#### Rodrigo A. Melo

## Free and Open Source Software for FPGA development

Virtual | Feb | 2021

$\bullet$

Joint ICTP-IAEA School on FPGA-based SoC and its Applications for Nuclear and Related Instrumentation | (smr 3562)

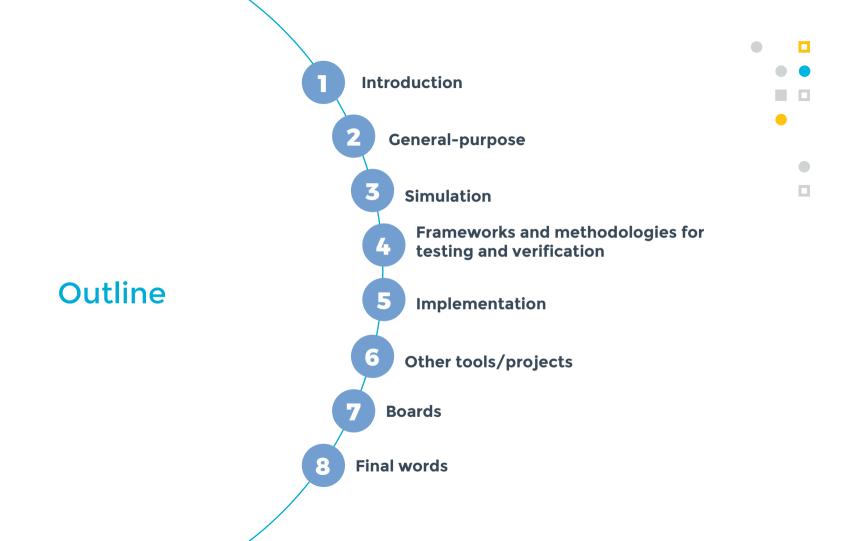

### Introduction

- Free (as freedom) and Open Source (you can access the source code)

Software (programs).

- Solves the disambiguation between free software and open-source software.

- Anyone is freely licensed to **use**, **copy**, **study**, and **change** the software.

creative

ns

#### General

- Personal control, customization and freedom

- Privacy and security

- Low or no costs (solutions and support)

- Quality, collaboration and efficiency

- High level of flexibility and open-standars adherence

- Innovation

#### **Particular for FPGA development**

- Vendor-independence

- Lightweight tools (size and speed)

## **General-purpose**

- Aka shell, terminal, console, bash, etc.

- Most projects provide one or more *Command-line interface* (CLI) tool/s.

- It is common for Linux distributions.

- You can use the Windows Subsytem for Linux (WSL), which is a compatibility layer for running Linux binary executables (probably with some limitations).

```

$ git init

Initialized empty Git repository in /tmp/tmp.IMBYSY7R8Y/.git/

$ cat > README << 'EOF'

> Git is a distributed revision control system.

> EOF

$ git add README

$ git commit

[master (root-commit) e4dcc69] You can edit locally and push

to any remote.

1 file changed, 1 insertion(+)

crate mode 100644 README

$ git remote add origin git@github.com:cdown/thats.git

$ git push -u origin master

```

- Is a distributed version control system.

- It was created in 2005 by Linus Torvalds, the Linux kernel creator, for development of the Linux kernel.

- Is the de facto standard for FOSS projects.

- Allows you to deal with a software repository (repo), managing versions and multiple users.

"Take Concurrent Versions System (CVS) as an example of what not to do; if in doubt, make the exact opposite decision" Linux Torvald, 2007

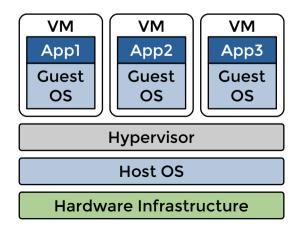

Docker uses OS-level virtualization to deliver software in packages called containers, which are isolated one from another and bundle their own software, libraries and configuration files.

All containers are run by a single OS Kernel and therefore uses fewer resources than VM.

#### Instituto Nacional de Tecnología Industrial Deployment (CI/CD)

- Is to automatically perform an action based on a repository event (push, merge, cron, etc).

- Continuous Integration: run linters, unit and/or integration tests, Hardware-in-the loop simulation.

- **Continuous Delivery:** build binaries, documentation, packages, etc.

- **Continuous Deployment:** build and install in production.

- Is a build automation tool.

- A Makefile contains a set of directives (targets, dependencies and rules) which are used by make to generate a target/goal.

- It works upon the principle that files only needs to be recreated if their dependencies are newer than the file being re/created.

- There are other newer tools such as CMake and Scons, but make is definitively the building tool, and sometimes part of the execution, in the FPGA ecosystem.

- Is an interpreted, high-level and general-purpose programming language (one of the most used in general, and the main in certain fields such as Machine/Deep Learning).

- A lot of its libraries are written in C (performance).

- Easy to read and learn.

- Most FOSS FPGA tools are written in Python, or C/C++ with a Python binding/wrapper.

- There are several HDL languages based on Python.

- Is also being used as verification language.

## Simulation

- Analyzer, compiler, simulator and (experimental) synthesizer for VHDL.

- Full support for the 1987, 1993, 2002 versions of the IEEE 1076 VHDL standard, and partial for the latest 2008 revision. Partial support of PSL (Property Specification Language).

- It generates binaries to perform a simulation.

- Can write waveforms to VCD or GHW (recommended for VHDL) files.

- Verilog (IEEE-1364) simulator.

- It generates an intermediate file format wich is after executed by a command.

• Verilog/SystemVerilog simulator.

- Compiles into multithreaded C++.

- Performs lint code-quality checks.

$\int \!\!\! \Lambda$

GTKWave is a fully featured wave viewer which reads LXT, LXT2, VZT, FST, and GHW files as well as standard Verilog VCD/EVCD files and allows their viewing

# Frameworks and methodologies for testing and verification

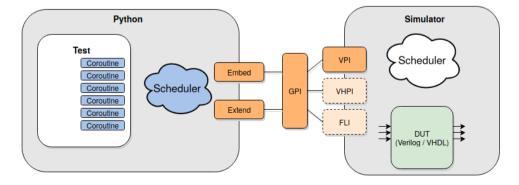

- OSVVM: Open Source VHDL Verification Methodology

- UVVM: Universal VHDL Verification Methodology

- VUnit: unit testing framework for VHDL/SystemVerilog

- SVUnit: unit testing framework for Verilog/SystemVerilog

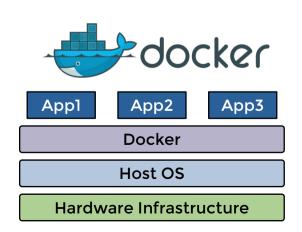

- cocotb: Coroutine Co-simulation Test Bench

- A coroutine based cosimulation library for writing VHDL and Verilog testbenches in Python

- Supported simulators: **ghdl**, **iverilog**, **verilator**, Synopsys VCS, Aldec Riviera-PRO, Aldec Active-HDL, Mentor Questa, Mentor ModelSim, Cadence Incisive, Cadence Xcelium, Tachyon DA CVC.

FPGA Methodologies and Testbench Base-Class Libraries

Source: The 2020 Wilson Research Group Functional Verification Study

- SymbiYosys (sby): front-end driver program for Yosys-based formal hardware verification flows.

- Formal Verification is the act of proving the correctness of intended algorithms underlying a system with respect to a certain formal specification or property, using formal methods of mathematics (assumptions and assertions).

- Supports Verilog (free), VHDL and SystemVerilog (through verific with a license).

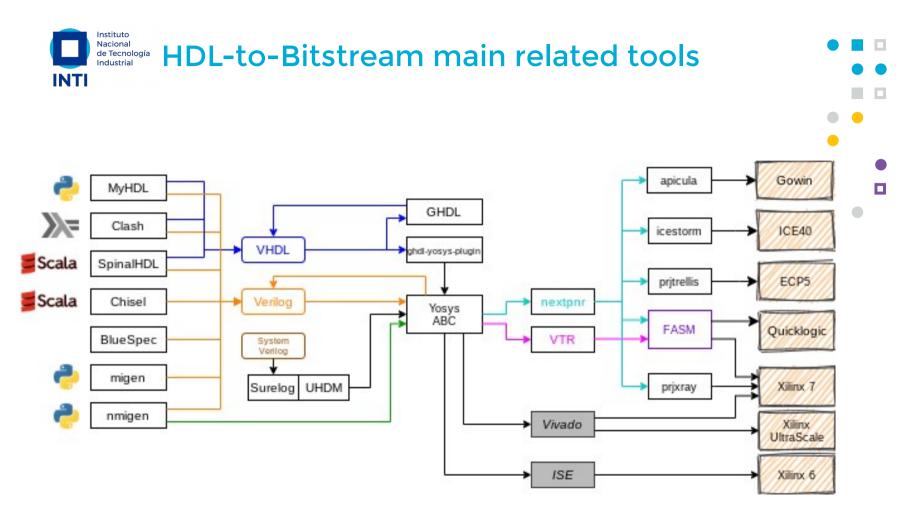

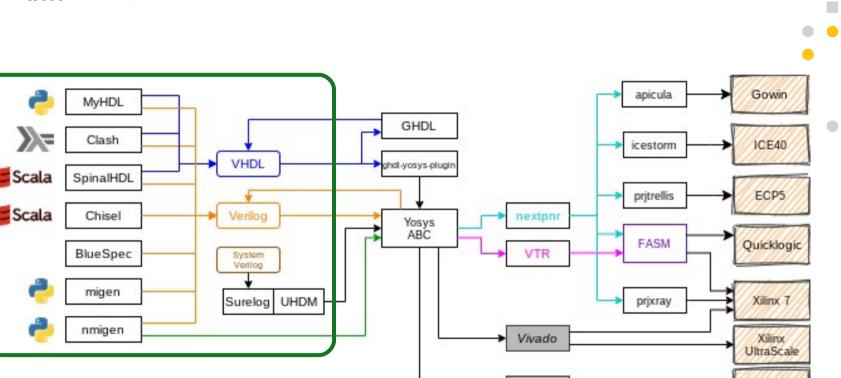

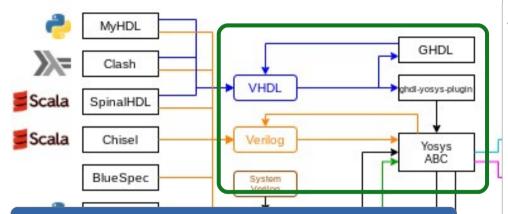

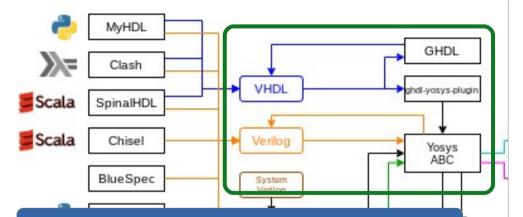

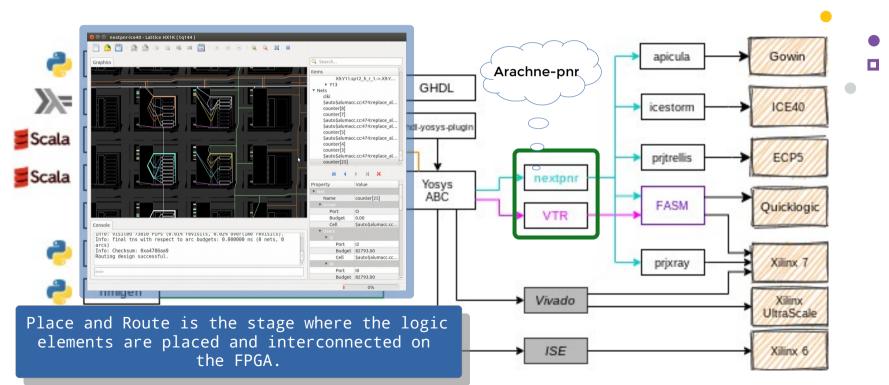

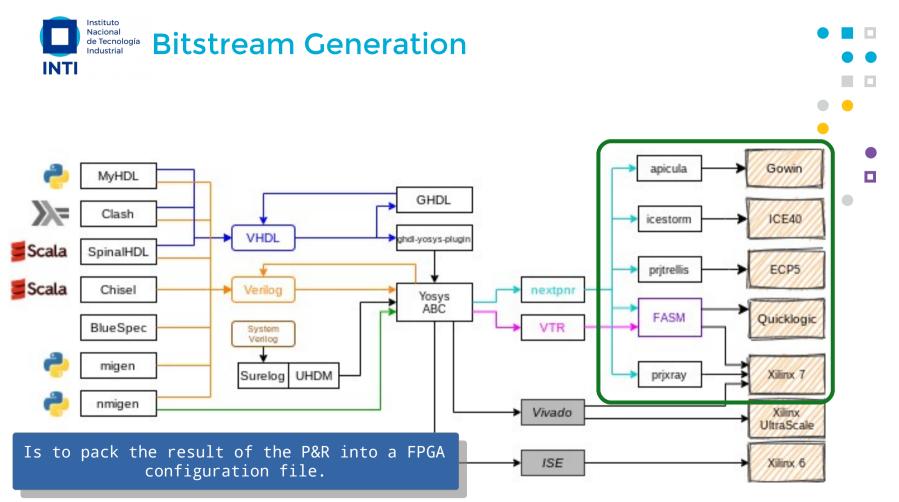

### Implementation (HDL-to-Bitstream)

The graphic is based on work from Unai Martinez-Corral

ISE

The graphic is based on work from Unai Martinez-Corral

Xilinx 6

Is to convert an abstract specification of a circuit (being an HDL a common input) into a design implementation in terms of the basic blocks supported by the chosen technology (being a netlist the output).

Yosys Open SYnthesis Suite

Is a framework for RTL synthesis tools. It currently has extensive Verilog-2005 support and provides a basic set of synthesis algorithms for various application domains. It was the first useful FOSS synthesizer. Supports devices from Lattice (iCE40 and ECP5), Xilinx (Series 7, Ultrascale, and others), Gowin, Achronix, Intel, Microsemi, etc.

The graphic is based on work from Unai Martinez-Corral

Is to convert an abstract specification of a circuit (being an HDL a common input) into a design implementation in terms of the basic blocks supported by the chosen technology (being a netlist the output).

**GHDL:** the open-source analyzer, compiler, simulator and (experimental, general purpose) synthesizer for VHDL.

ghdl-yosys-plugin: VHDL

synthesis, based on GHDL and

Yosys.

The graphic is based on work from Unai Martinez-Corral

The graphic is based on work from Unai Martinez-Corral

The graphic is based on work from Unai Martinez-Corral

- **OpenOCD:** Free and **Open On-Chip Debugging**, In-System Programming and Boundary-Scan Testing

- **UrJTAG:** universal JTAG library, server and tools.

- **iceprog:** programmer of the IceStorm project (FTDI-based programmers).

- **ecpprog:** programmer for the Lattice ECP5 series (FTDI-based programmers).

- **openFPGALoader:** universal utility for programming FPGA.

- **dfu-util:** Device Firmware Upgrade Utilities (intended to download/upload firmware to devices connected over USB).

# Others tools/projects

- **HDLmake:** tool for generating multi-purpose makefiles for FPGA projects.

- edalize: a Python Library for interacting with EDA tools (was part of FuseSoC, now its build backend).

- **PyFPGA:** A Python package to use FPGA development tools programmatically.

- Supports Synthesis, Implementation, Bitstream generation and Programming from Python.

- Supports ISE, Vivado, Quartus, Libero-SoC and open-source tools (Yosys, GHDL, ghdl-yosys-plugin, nextpnr, icestorm, trellis).

- Helpers: hdl2bit, prj2bit & bitprog.

- **PoC** (Pile of Cores Library): a library of free, open-source and platform independent IP cores.

- **FuseSoC:** package manager and build abstraction tool (edalize) for FPGA/ASIC development.

- Litex: a Migen/MiSoC based SoC builder that provides the infrastructure to easily create Cores/SoCs

- **OpenCores** and **LibreCores**: collections of IP-cores.

/ There are lot of FOSS projects at GitHub and GitLab.

- Leon 3 (Gaisler):

- Is a synthesisable VHDL model of a 32-bit processor compliant with the SPARC V8 architecture.

- GNU GPL license for research and education.

- Distributed as part of the GRLIB.

- OpenRISC:

- Specification OpenRISC 1000 (32/64 bits)

- The flagship implementation, the OR1200, is written in Verilog.

- Distributed as part of OpenRISC Reference Platform System-on-Chip (ORPSoC).

- Leon 3 (Gaisler):

- Is a synthesisable VHDL model of a 32-bit processor compliant with the SPARC V8 architecture.

- GNU GPL license for research and education.

- Distributed as part of the GRLIB.

- OpenRISC:

- Specification OpenRISC 1000 (32/64 bits)

- The flagship implementation, the OR1200, is written in Verilog.

- Distributed as part of OpenRISC Reference Platform System-on-Chip (ORPSoC).

| example who — Hossarque en plan                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

| tile tall Yew Selection find Packages Help TernetCL<br>TernesHDL ⊡ C I S The V ⇔ ► ■ O ⊂ La チ ⊡ ball ⊙ Ξ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                     |

| 41 v st next ≪ 57 52;<br>42 cnd 37;<br>43 v ten others⇒ v 57 53 ⇒<br>44 w st next ∞ 57 51;<br>45 end case;<br>46 and process p comb;<br>47                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                     |

| 40     process[iput], sput2, state_reg)-       51     begin       51     state_next ← state_reg;       52     case state_reg is       53     usion N = ∞       54     if uppet3 then if (input] = '81'   then       55     state_next ← x2;       56     clsif input-1 then if (input] = '81'   then       57     state_next ← x2;       58     else       59     state_next ← state_       50     state_next ← state_       50     state_next ← state_       58     end ff;       61     when S1 ⇒                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                     |

| State machine diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                     |

| s2<br>vertex = 10<br>vertex = 10<br>v |                     |

| + X conclude 0.54.000 431 (30.113)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | IF UTFS VHDL ΩGEHub |

TEROS technology

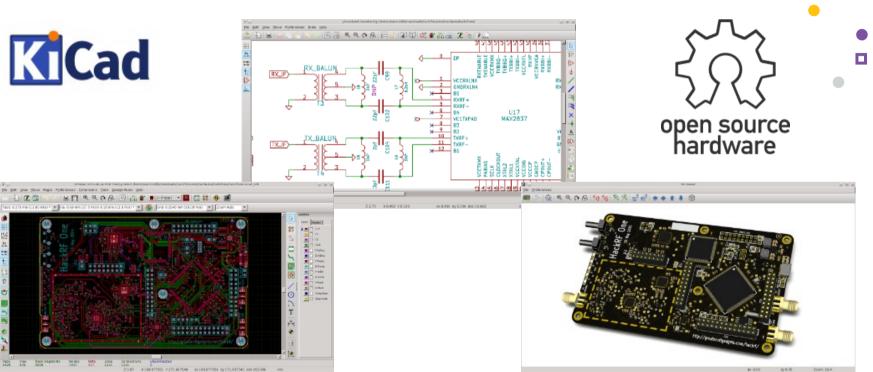

## Boards (Open Hardware)

Computadora Industrial Abierta Argentina Desarrollo colectivo

### 12 Layers!!! Based on a Zynq-7030

TinyFPGA BX

ULX3S

OrangeCrab

TinyFPGA EX

**QuickFeather – EOS S3**

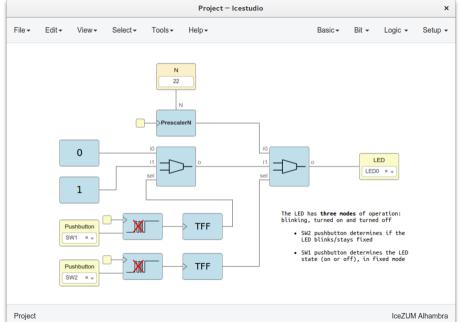

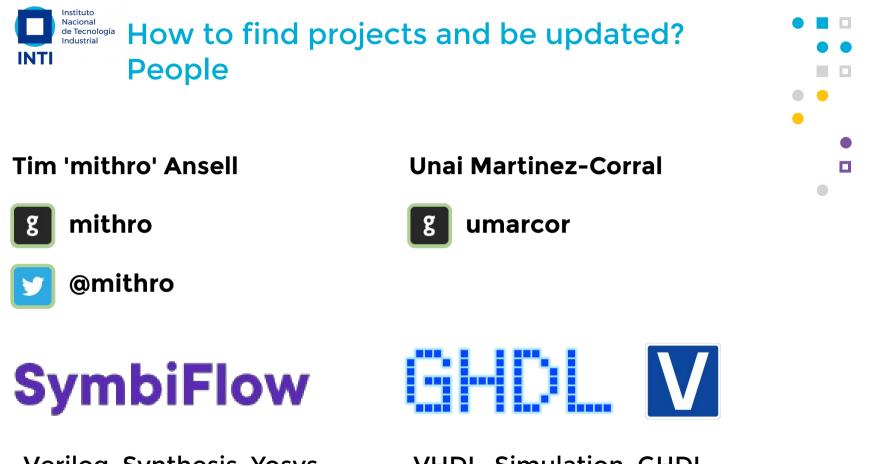

**SymbiFlow**

## **Final words**

Verilog, Synthesis, Yosys

VHDL, Simulation, GHDL

#### Instituto Nacional How to find projects and be updated? de Tecnología Industrial INTI hdl/awesome

Awesome resources for Hardware Description Tools, frameworks, IP cores, libraries and more!

Welcome to Awesome HDL, a community effort for maintaining a curated list of resources for Hardware Description, such as Tools, IP Core Libraries and Collections, Frameworks and more! Read all about it and see how to contribute.

#### **pyFPGA**

A Python package to use FPGA development tools programmatically

Maintained by: Rodrigo Alejandro Melo

PvFPGA is a Python Class for vendor-independent FPGA development. It allows using a single project file and programmatically executing synthesis, implementation, generation of bitstream

Categories

Curated midsized taxonomy

Tags Loose taxonomy

#### All items No filter

and/or transference to supported boards. The workflow is command-line centric.

• It's friendly with Version Control Systems and Continuous Integration (CI).

https://github.com/hdl/awesome https://hdl.github.io/awesome

- Several projects provide Dockerfiles or nighty builds to test its development.

- YosysHQ/fpga-toolchain: Multi-platform nightly builds of open source FPGA tools.

- hdl/MINGW-packages: Electronic design automation (EDA) package recipes for MinGW-w64 (MSYS2).

- hdl/containers: Building and deploying container images for open source electronic design automation (EDA).

- ghdl/docker: Scripts to build and use docker images including GHDL.

- Install Docker following the instructions for your OS.

- Run: \$DOCKER <CONTAINER> <TOOL> <OPTIONS> •

\$ DOCKER="docker run --rm -v \$HOME:\$HOME -w \$PWD"

\$ \$DOCKER ghdl/ghdl:buster-mcode ghdl --version GHDL 2.0.0-dev (v1.0.0-13-gad9906d3) [Dunoon edition] Compiled with GNAT Version: 8.3.0 mcode code generator Written by Tristan Gingold.

Copyright (C) 2003 - 2021 Tristan Gingold. GHDL is free software, covered by the GNU General Public License. There is NO warranty; not even for MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE.

\$ \$DOCKER hdlc/yosys yosys --version Yosys 0.9+3894 (git sha1 eff18a2b, clang 7.0.1-8+deb10u2 -fPIC -0s)

a tool, or when outdated, will produce the pull of a new image from Dockerhub.

🖾 rmelo@inti.gob.ar

rodrigoalejandromelo

@rodrigomelo9ok

rodrigomelo9

rodrigomelo9

# • H • Thank you

This work is licensed under CC BY 4.0 cc 👔

If you want to know more about INTI, we wait for you at

f INTIArg

@INTIargentina

in INTI

@ @intiargentina

canalinti

www.inti.gob.ar consulta@inti.gob.ar 0800 444 4004

Instituto Nacional de Tecnología Industrial

INT

Joint ICTP-IAEA School on FPGA-based SoC and its Applications for Nuclear and Related Instrumentation | (smr 3562)

Ministerio de Desarrollo Productivo **Argentina**