## Joint ICTP-IAEA School on FPGA-based SoC and its Applications for Nuclear and Related Instrumentation

#### **University of Sri Jayewardenepura**

#### My research Interest in

Embedded Systems

Design of Scientific Instrumentation

Sensor Network and IoT

#### Interested Topics in the workshop (To me)

- System on Chip Architecture and Design Methodology

- Design of Custom IPs

- C for Embedded Systems

- Hardware and Software Integration

- Use Machine Learning and Image Processing Algorithms in FPGA

# Personal improvement throught the Practical session

- IAEA Group 3 : Data Acquisition System

- Used board : CMOD-A7

**Exercise** 1

**Design an IP core**

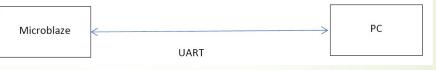

**Exercise-2**

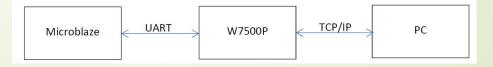

### Setup communication between MicroBlaze and PC using UART protocol

**Exercise-3**

Place the Wiznet W7500P in-between PC and SoC

controlling and monitoring of the IP cores through PC machine .

**Exercise** 4

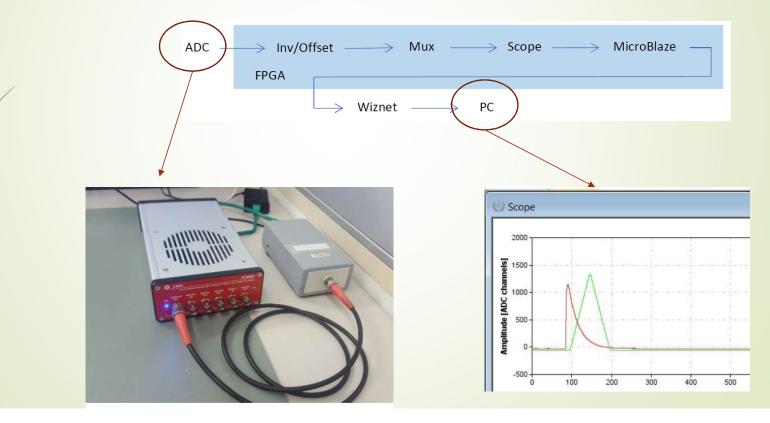

Implement simple data processing of the ADC data and two-channel oscilloscope inside the FPGA

**Exercise-5-7** Add different IP cores to the data processing system and improve the accuracy

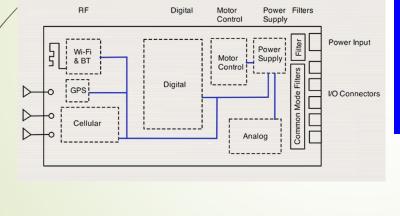

**Design Principles technique and Methodologies of Hardware Components**

Resolution 1280x1024 px Free Photoshop PSD file download www.psdgraphics.com