310/1780-10

ICTP-INFN Advanced Tranining Course on FPGA and VHDL for Hardware Simulation and Synthesis 27 November - 22 December 2006

VHDL & FPGA – Session 2

Nizar ABDALLH ACTEL Corp. 2061 Stierlin Court Mountain View, CA 94043-4655 U.S.A.

These lecture notes are intended only for distribution to participants

## Lectures: VHDL & FPGA Architectures

## Outline

- Introduction to FPGA & FPGA Design Flow

- Synthesis I Introduction

- Synthesis II Introduction to VHDL

- Synthesis III Advanced VHDL

- Design verification & timing concepts

- Programmable logic & FPGA architectures

- Actel ProASIC3 FPGA architecture

# Synthesis II – Introduction to VHDL

## Why HDL? Why VHDL?

#### HDL is a software solution due to limits in hardware solutions and to:

- Increasing design complexity

- Increasing cost in time and investment

- Increasing knowledge requirement

- Inadequacy of other existing languages

#### VHDL is a response to problems for system manufacturers in verifying their system fully

- Vendor dependency

- Different vendors with different incompatible HDLs

- Problems in design documentation exchange

#### A standard HDL from the System Manufacturer's Point of View: V H D L

#### **VHDL History**

- 1981: an Extensive Public Review (DOD): VHSIC Program for modeling digital systems

- 1983: a Request for Proposal (Intermetrics, IBM, and Texas Instruments)

- 1986: VHDL in the Public Domain

- 1987: Standard VHDL'87 (IEEE-1076-1987)

- 1993: New Standard VHDL'93 (IEEE-1076-1993)

- 1994: VITAL (VHDL Initiative Toward ASIC Libraries)

- Defines Standard Format for Gate Libraries, 1994

- Allows Specification of Common Timing Models

#### Revised Standard "VHDL-2001" in review now

VHDL & FPGA Architectures

© 2005 Nizar Abdallah

## **VHDL Advantages & Drawbacks**

Philosophy: readable, docs-based on a clear and predictable simulation behavior

#### Advantages

- Standard format for design exchange

- Technology independent

- Multiple vendor support

- Support for large as well as small designs

- Support for wide range of abstraction in modeling

- Simulation oriented (including for writing testbench)

- User defined value abstractions

- Timing constructs

#### Drawbacks

- Complex tools

- Slow tools

## **VHDL** Main Features

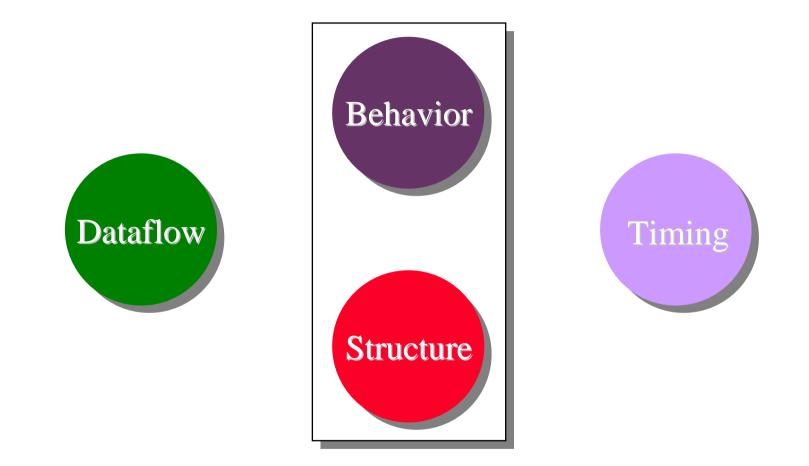

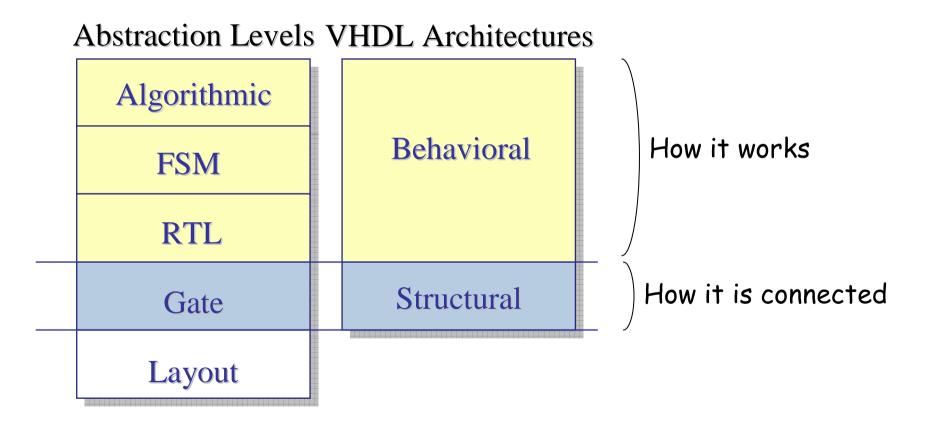

## **VHDL** Architectures

Does not allow a layout description

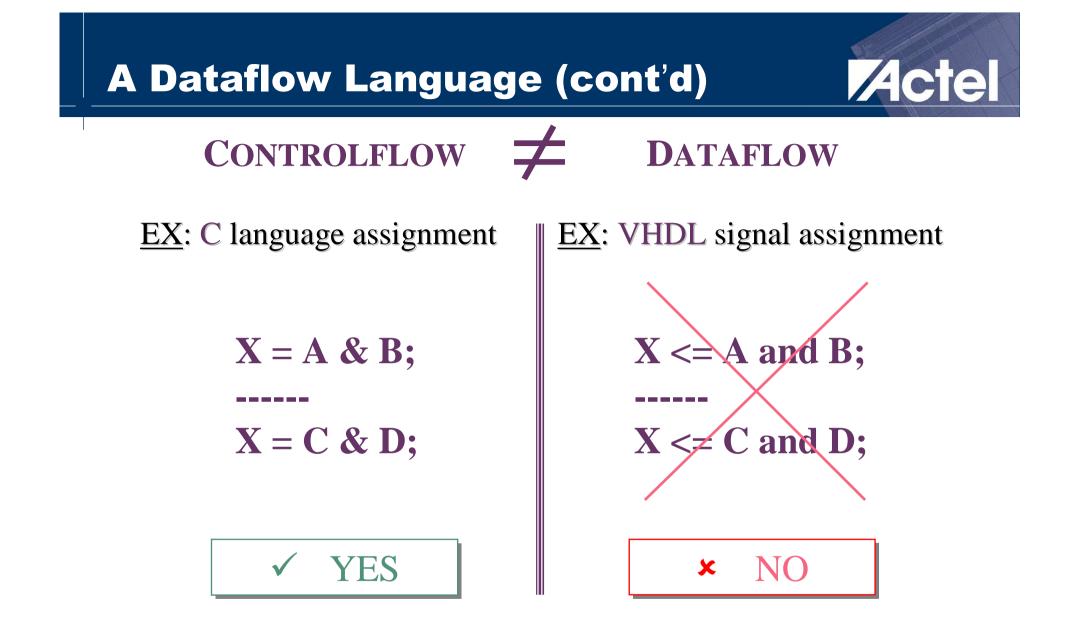

## Actel **A Dataflow Language CONTROLFLOW DATAFLOW** EX: C language assignment EX: VHDL signal assignment $X \le A$ and B; $\mathbf{X} = \mathbf{A} \ \& \ \mathbf{B};$

X is computed out of A and B <u>ONLY</u> each time this assignment is executed A <u>PERMANENT</u> link is created between A, B, and X

X is computed out of A and B <u>WHENEVER</u> A or B changes

#### **Behavioral vs. Structural**

**Behavioral**

#### D-FF with asynch low reset & pos-edge clock

```

process (CLK, RESET)

begin

if (RESET = '0') then

Q <= '0';

elsif (CLK'event and CLK='1') then

Q <= DATA;

end if ;

end if ;</pre>

```

```

-- component declaration Structural

component DFF

port ( D, CLR, CLK : in std_logic;

Q : out std_logic);

end component;

-- component instantiation

U1: DFF

port map (D => DATA, CLR => RESET, CLK => CLK, Q => OUT);

```

## **VHDL Building Blocks: Entity**

#### Entity

#### Architecture

#### Configuration

#### Package

#### Library

VHDL & FPGA Architectures

© 2005 Nizar Abdallah

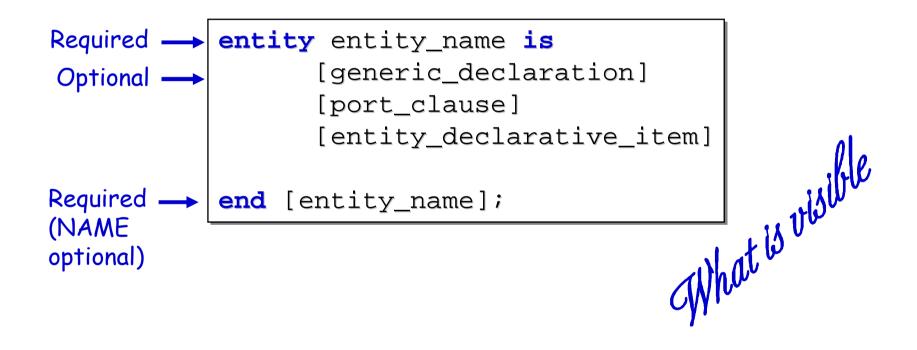

#### **Entity Overview**

The External Aspect of a Design Unit

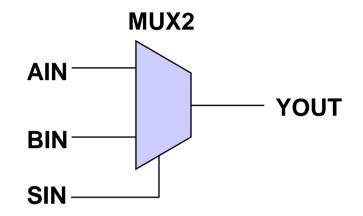

## **Entity Example: 2-to-1 Mux**

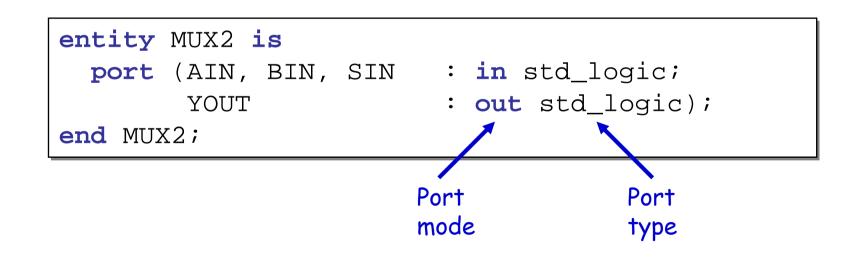

#### **Entity Example: Full Adder**

Actel

#### **Ports**

- Provide communication with other components

- Must have signal name, type and mode

#### Port Modes:

- in (data goes into entity only)

- out (data goes out of entity only and not used internally)

- inout (data is bi-directional)

- buffer (data goes out of entity and used internally)

## VHDL Building Blocks: Architecture Actel

#### Entity

#### Architecture

#### Configuration

#### Package

#### Library

VHDL & FPGA Architectures

© 2005 Nizar Abdallah

## **Architecture Overview**

- The Internal Aspect of a Design Unit

- Can be behavioral (RTL) or structural

- Always associated with single entity

- Single entity can have multiple architectures

```

architecture architecture_name of entity_name is

{architecture_declarative_part}

begin

{architecture_descriptive_part}

end [architecture_name];

```

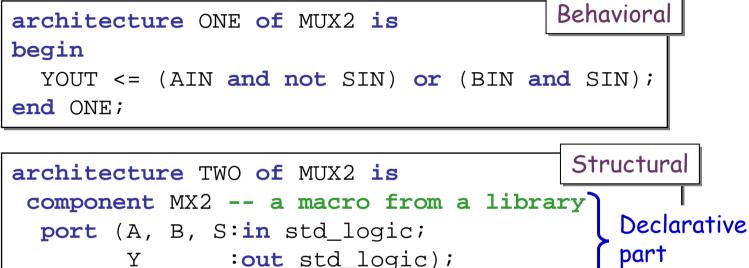

## Architecture Example: 2-to-1 Mux Acte

#### Two architecture flavors: Behavioral & Structural

end component; begin

-- instantiate MX2 U1: MX2 port map(A=>AIN, B=>BIN, S=>SIN, Y=>YOUT); end TWO;

Descriptive

part

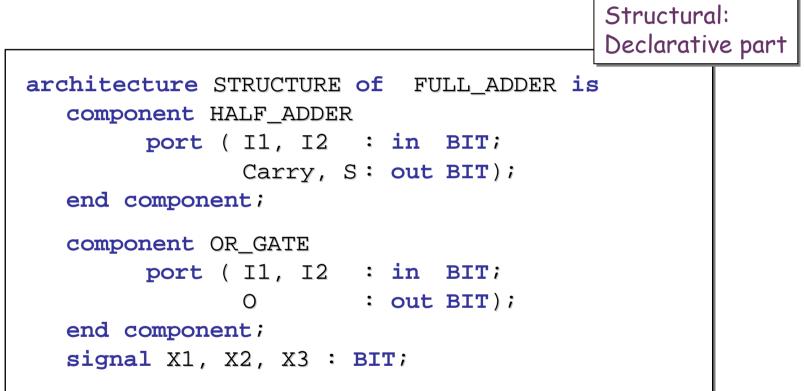

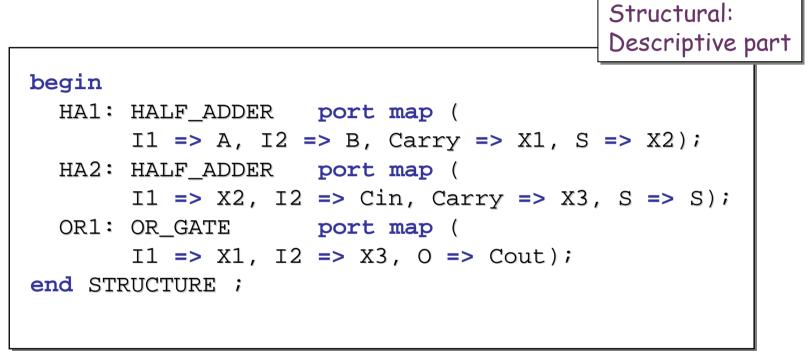

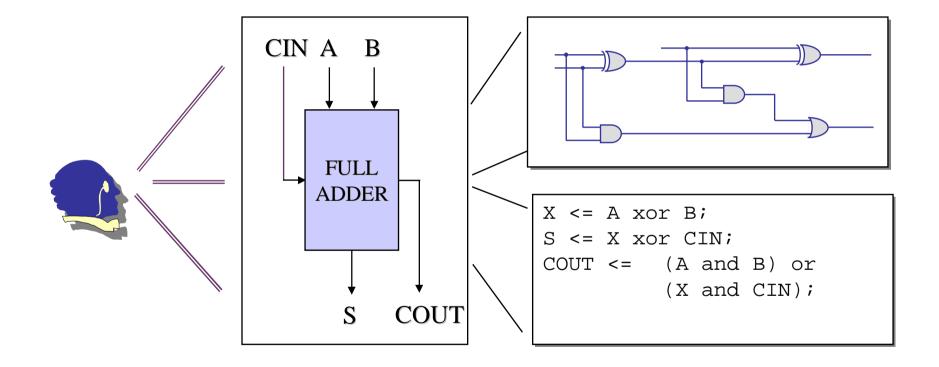

## **Architecture Example: Full Adder**

#### Two architecture flavors: Behavioral & Structural

```

entity FULL_ADDER is

port (A, B, Cin : in BIT;

S, Cout : out BIT);

end FULL_ADDER;

architecture DATAFLOW of FULL_ADDER is

signal X : BIT;

begin

X <= A xor B;

S <= X xor Cin after 10ns;

Cout <= (A and B) or (X and Cin) after 5ns;

end DATAFLOW;</pre>

```

Actel

## Architecture Example: Full Adder (condition

#### Two architecture flavors: Behavioral & Structural

## Architecture Example: Full Adder (condition

#### Two architecture flavors: Behavioral & Structural

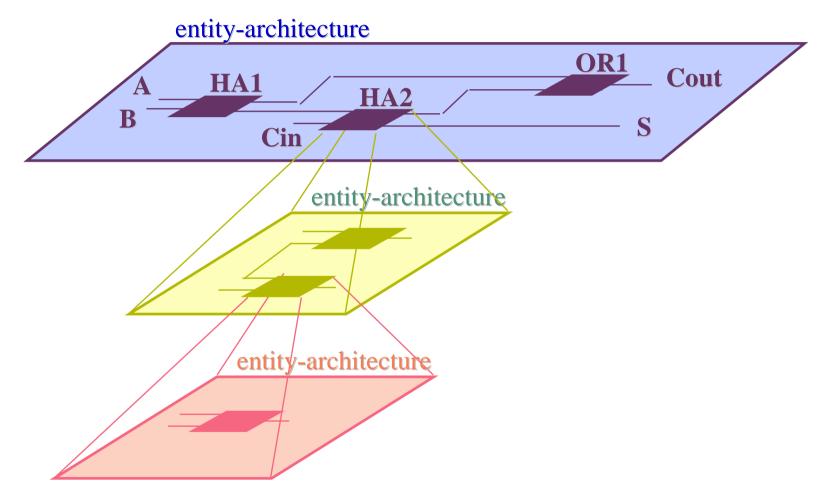

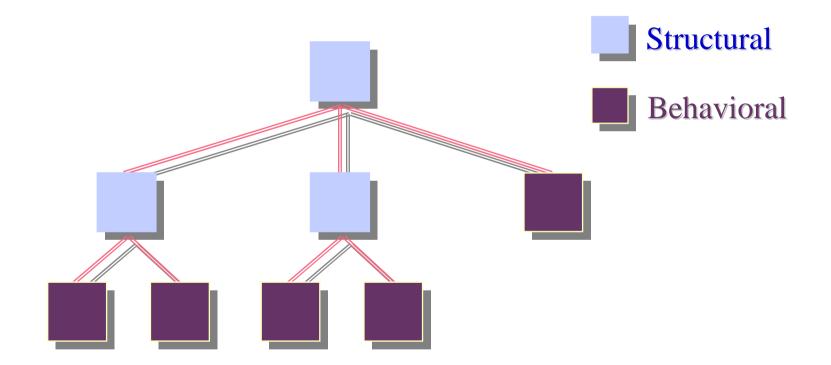

#### Structural Style to represent Hierarchy

#### **Architecture in a Design Tree**

#### Structure & Behavior in a Design Tree

#### **Entity/Architecture**

#### entity/architecture: a <u>One-to-Many</u> relationship

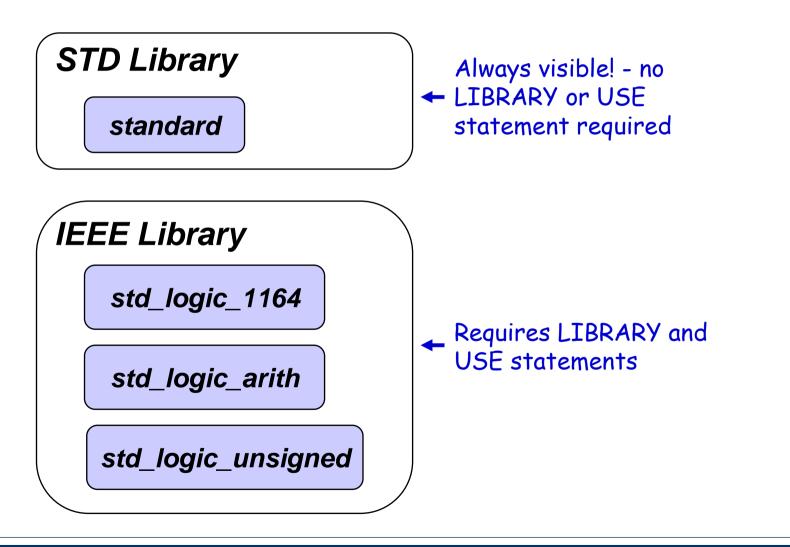

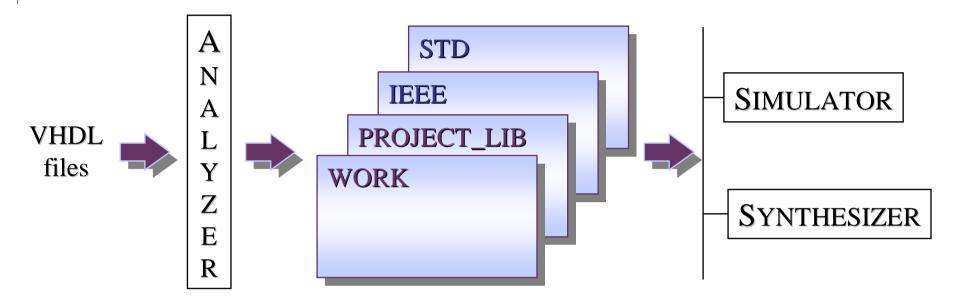

## VHDL Building Blocks: Packages & Libraries

#### Architecture

Configuration

#### Library

**VHDL & FPGA Architectures**

© 2005 Nizar Abdallah

Actel

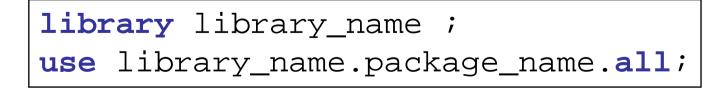

#### **Packages & Libraries**

- Libraries contain packages

- Packages contain commonly used types, operators, constants, functions, etc.

- Both must be "opened" before their contents can be used in an entity or architecture

library ieee;

use ieee.std\_logic\_1164.all;

## Commonly Used Libraries & Packag

#### **Design Libraries**

## Complete Design Example: Multiplie

#### Is this a structural or behavioral description?

#### **Data Objects**

#### Constants

#### Variables

- syntax: var:= expression

- can be declared in body (inside process) or subprogram (outside process)

- a body-declared variable is never reinitialized

- a sub-program declared variable is initialized for each call to the subprogram

- value assignment as immediate effect

#### Signals

- syntax: signal <= value</p>

- delayed value assignment

- optional propagation delay attribute

- no global variables to avoid synchronization problems

- value *resolution* for multiple assignments

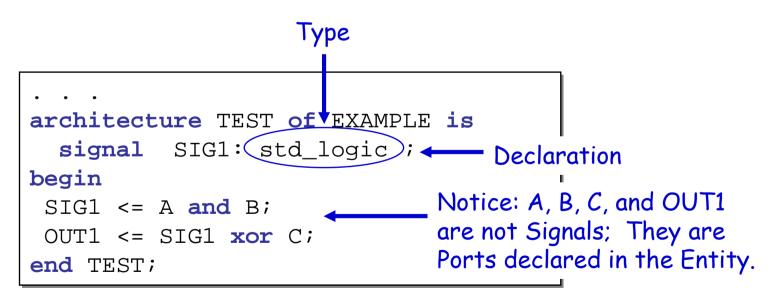

## Signals

OUT1

SIG1

Α

B

- Used for internal connections

- Must be declared before use

- Must have a type

- Assignment is done with <=</p>

## Bit order may be ascending (0 to 7) or descending (7 downto 0)

|                                    | Q is an 8-bit vector |  |  |  |

|------------------------------------|----------------------|--|--|--|

| entity COUNTER is                  |                      |  |  |  |

| <pre>port(CLK: in std_logic;</pre> |                      |  |  |  |

| RST: <b>in</b> std_logic;          |                      |  |  |  |

| Q : out std_logic_vector(7         | downto 0));          |  |  |  |

| end COUNTER;                       |                      |  |  |  |

|                     |            |                                   | S2 is a 3-bit vector | r |

|---------------------|------------|-----------------------------------|----------------------|---|

|                     | •••        |                                   |                      |   |

| architecture BEHAVE |            | BEHAVE of COUNTER is              |                      |   |

|                     | signal S1: | S1: std_logic_vector(7 downto 0); |                      |   |

|                     | signal S2: | 2: std_logic_vector(2 downto 0);  |                      |   |

|                     | signal S3: | <pre>std_logic;</pre>             |                      |   |

|                     |            |                                   |                      |   |

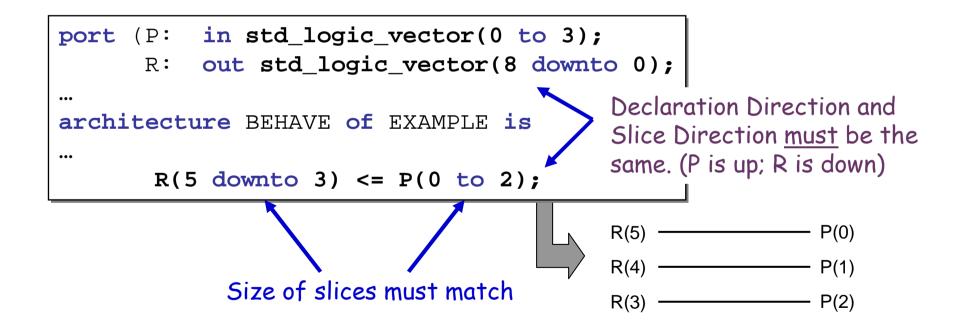

#### **Vector Slicing**

- Vector slicing can be used on either side of a signal or variable assignment statement

- Extracts subset of Vector for Reading or Writing

#### **Data Types**

#### All VHDL data objects must have a type

- Port types are declared in the entity

- Signal, variable, and constant types are declared in the architecture.

#### Types we will cover:

- STANDARD package types

- User-defined enumeration types

- IEEE std\_logic\_1164 package types

## IEEE 1076-1987 Standard Package

#### Predefined VHDL Data Types

- Is always visible

- No declaration is needed

#### Types available

- BOOLEAN : (false , true)

- BIT : ( '0', '1' )

- BIT\_VECTOR : array of BIT values

- INTEGER : range -2 147 483 647 to +2 147 483 647

- CHARACTER

- NATURAL : Subtype of INTEGER (Non Negative)

- **POSITIVE** : Subtype of INTEGER (positive)

- **STRING** : array of CHARACTERS

- **REAL** : range -1.0E+38 to +1.0E+38

- TIME : Physical type used for simulation

## IEEE 1076-1987: integer Type

- Allowed values are mathematical integers

- Minimum range: 231 to -231 (32 bits minimum) if no range is specified

- Useful as index holders for loops or generics

- Supported operations are add, subtract, multiply, and divide

```

architecture BEHAVE of COUNTER is

begin

process(clk)

variable cntr: integer range 0 to 63 := 0;

begin

```

# IEEE 1076-1987: bit / bit\_vector Type Actel

Allowed values are '0' and '1'

#### Default initialization to '0'

entity MUX is

port (A, B, S: in bit;

Y: out bit);

end MUX;

#### bit\_vector is an array of bits

```

architecture BEHAVE of MUX is

constant LOW: bit_vector(1 downto 0) := "00";

begin

```

## IEEE 1076-1987: boolean Type

- Allowed values are true and false

- Not a bit literal has no relationship to a bit

- Operations only allowed in IF-ELSE statements, in processes and always produce a Boolean result

```

library ieee;

use ieee.std_logic_1164.all;

entity CONTROLLER is

port (SEL : in boolean;

X, Y : in std_logic;

Z : out std_logic);

end CONTROLLER;

architecture BEHAVE of CONTROLLER is

begin

process (X, Y, SEL)

begin

if (SEL) then

```

```

Z <= X;

```

```

else

7 <= Y;

```

```

end if ;

```

```

end process;

```

```

end BEHAVE;

```

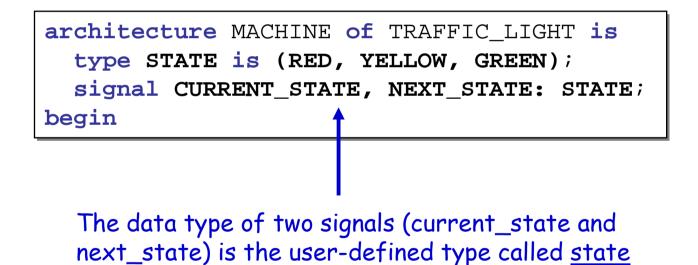

## **User-Defined Enumeration Types**

- Allow designers to specify exact values for operation

- Useful for state machine designs

Actel

# IEEE 1164-1993 Standard Logic Pack

std\_logic\_1164 must be declared

```

library ieee;

use ieee.std_logic_1164.all;

```

- Supported by most VHDL simulators and synthesis tools

- Includes a multi-value logic system

- Nine signal strengths defined

- Can resolve multiple signal drivers

#### Generally used instead of bit/bit\_vector

## std\_logic\_1164 Types

#### std\_ulogic, std\_ulogic\_vector

- Unresolved type

- Only one signal driver allowed

- std\_logic, std\_logic\_vector

- Resolved type multiple drivers allowed

- Used when tri-state logic required

#### std\_logic is best choice for behavioral

## "Legal" Values for std\_logic Type

#### Unresolved data type

#### type STD\_ULOGIC is (

| 'U'        |   | Uninitialized                                                   |

|------------|---|-----------------------------------------------------------------|

| 'X'        |   | Forcing Unknown                                                 |

| '0'        |   | Forcing Low (driven)                                            |

| '1'        | - | Forcing High (driven)                                           |

| 'Z'        |   | High Impedance                                                  |

|            |   |                                                                 |

| 'W'        |   | Weak Unknown Synthesizable                                      |

| 'W'<br>'L' |   | Weak Unknown<br>Weak Low (read)<br>Synthesizable<br>for<br>FPGA |

| 7 7        |   | for                                                             |

| <b>'L'</b> |   | Weak Unknown<br>Weak Low (read) for<br>FPGA                     |

Actel

## **Operators**

#### Six classes

| LOGIC OPERATOR         | and, or, nand, nor, xor |

|------------------------|-------------------------|

| RELATIONAL OPERATOR    | =, /=, <, <=, >, >=     |

| ADDING OPERATOR        | +,-,&                   |

| SIGN                   | +,-                     |

| MULTIPLYING OPERATOR   | * , / , mod , rem       |

| MISCELLANEOUS OPERATOR | ** , abs , not          |

|                        |                         |

| PRECEDENC              | <b>E ORDER</b>          |

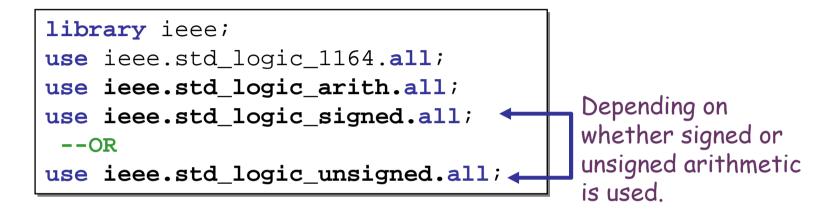

## **Arithmetic Operators**

#### Require opening the following packages:

# May be used on real, integer, bit or std\_logic types.

### **Operators: Example**

```

library ieee;

use ieee.std_logic_1164.all;

entity LOGIC is

port (A, B, C: in std_logic;

Y, Z : out std_logic);

end LOGIC;

architecture BEHAVE of LOGIC is

begin

Z <= A and B;

Y <= (A and B) or not C;

end BEHAVE;

```

() prevent ambiguity. Otherwise this could be: (A and B) or not C OR A and (B or not C)

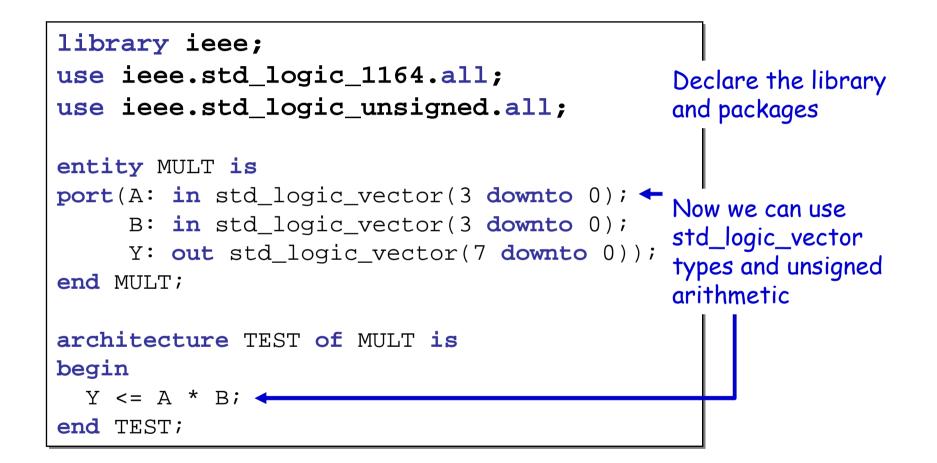

## **Arithmetic Operators: Example**

#### 4-bit multiplier

```

library ieee;

use ieee.std logic 1164.all;

use ieee.std_logic_unsigned.all;

entity MULT is

port(A: in std_logic_vector(3 downto 0);

*

B: in std logic vector(3 downto 0);

Y: out std logic vector(7 downto 0));

end MULT;

architecture BEHAVE of MULT is

begin

Y <= A * B;

end BEHAVE;

```

Α

Β

/ctel

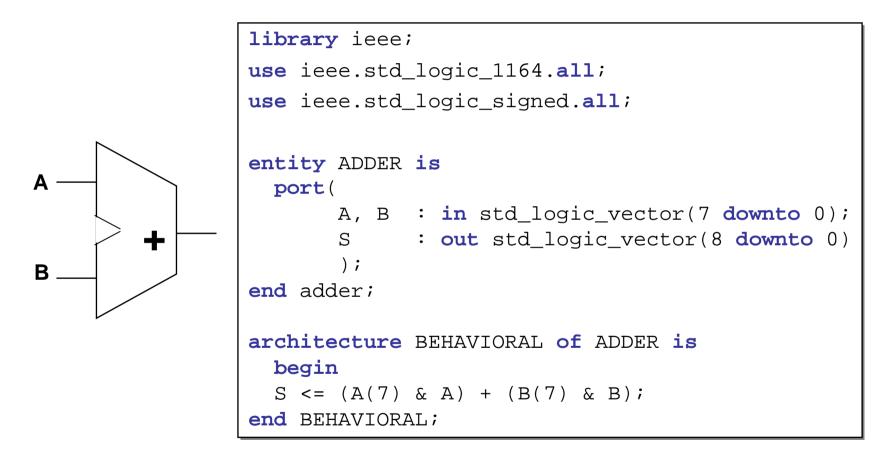

#### 8-bit adder with 9-bit result

#### A Data Attached to VHDL Objects

- S'LEFT : Index of the leftmost element of the data type

- S'RIGHT : Index of the rightmost element of the data type

- S'HIGH : Index of the highest element of the data type

- S'LOW : Index of the lowest element of the data type

- S'RANGE : Index range of the data type

- S'REVERSE\_RANGE : Reverse index range

- S'LENGTH : Number of elements of an array

- S'EVENT : A change value at the current simulation time

- S'STABLE : No change value at the current simulation time if (CK = 0 and not CK'STABLE)

• .....

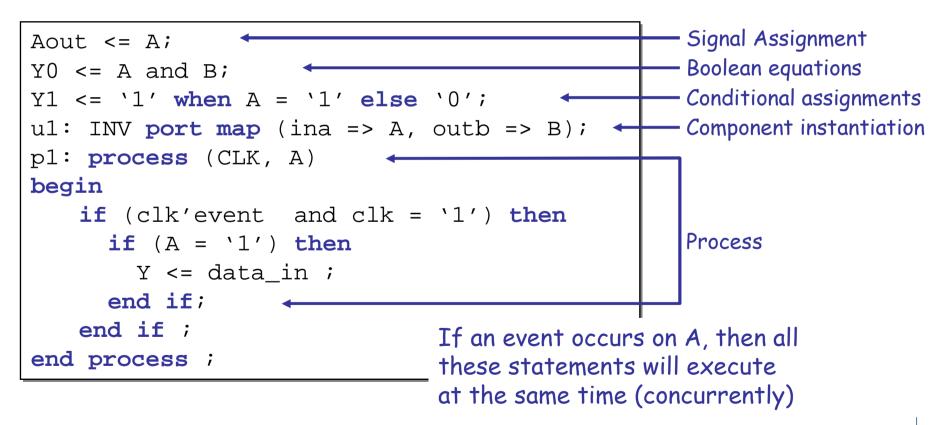

## **VHDL Statements**

#### Concurrent Statements

- Concurrent Signal Assignment

- Conditional Signal Assignment

- Selected Signal Assignment

- Block Statement

- Concurrent Assertion Statement

- Process Statement

## **Concurrent Statements**

#### Execute at the same time

# Signals impacted by an event are resolved in the same simulation time

## **Concurrent Signal Assignment**

- Always used within an architecture

- Change on the right-hand side causes <u>immediate</u> reassignment to the left-hand side

- Used in behavioral and structural descriptions

- Signals are associated with TIME

- With "after", the assignment is scheduled to a future simulation time

- Without "after", the assignment is scheduled at a DELTA TIME after the current simulation time

- Assignment operator is <=</p>

target <= expression [ after time\_expression ] ;</pre>

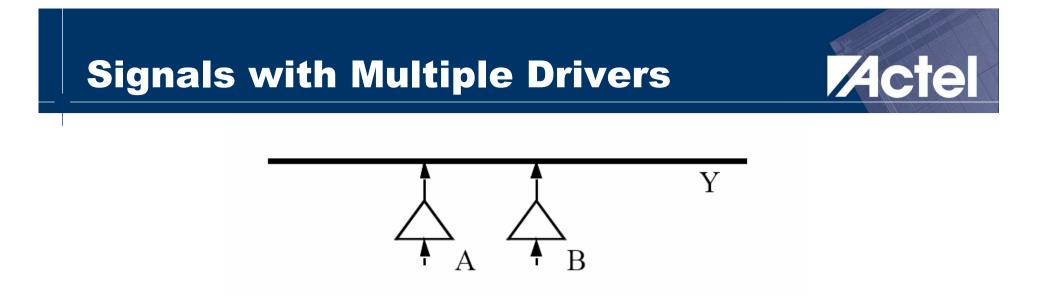

$Y \le A; -- in \ process1$ and,  $Y \le B; -- in \ process2$

#### What is the value of the signal in such a case?

Concept of a Resolution Function; attached to a signal or a type, and is called every time the value of signal needs to be determined -- that is every time a driver changes value

## **Conditional Signal Assignment**

- Concurrent Version of IF statement

- Condition/expression except for last expression

- One and only one of the expressions is used at a given time

- Syntax:

target <= first\_value when (condition1) else

second\_value when (condition1) else

third\_value;</pre>

Example:

Y <= IN1 when S = `0' else IN2 when S = `1' else `0';

Y <= ``00" when COUNT >= 8 else ``11";

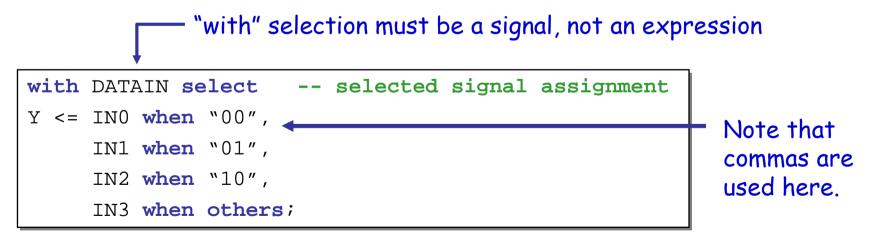

## **Selected Signal Assignment**

Concurrent Version of CASE Statement

#### Syntax:

with EXPRESSION

TARGET <= {expression when choices};</pre>

#### Example:

# When-Else Example: Tri-State Buffer Actel

```

library ieee;

use ieee.std logic 1164.all;

entity MY TRI is

A(0)-

·Y(0)

port(A: in std logic vector(3 downto 0);

EN-

EN: in std logic;

Y: out std logic vector(3 downto 0));

-Y(1)

A(1)-

end MY TRI;

EN-

A(2)-

·Y(2)

architecture BEHAVE of MY TRI is

begin

EN-

Y \leq A when EN = 1' else

·Y(3)

A(3)-

(others => `Z') ;

EN

end BEHAVE;

means Y <= "ZZZZ":

```

## With-Select Example: Truth Table

| Α | В | С | Y |

|---|---|---|---|

| 0 | 0 | 0 | 1 |

| 0 | 0 | 1 | 0 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | - |

| 1 | 1 | 1 | - |

'-' means don't care

```

library ieee;

use ieee.std logic 1164.all;

entity TRUTH TABLE is

port(A, B, C: in std logic;

Y: out std logic) ;

end TRUTH TABLE;

architecture BEHAVE of TRUTH TABLE is

signal S1: std_logic_vector(2 downto 0);

begin

S1 <= A & B & C; -- concatenate A, B, C

with S1 select

Y <= `1' when "000" | "010" | "100",

`0' when "001" | "011" | "101",

'-' when others;

end BEHAVE;

| means OR only when

used in "with" or "case"

```

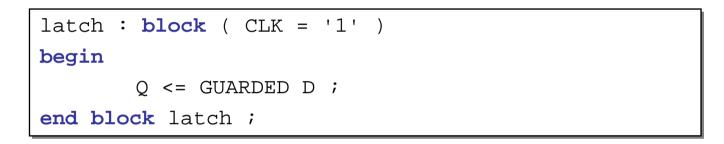

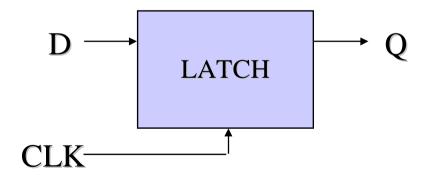

#### **Block Statement**

#### Used in synchronous descriptions

#### **Assertion Statement**

- If the condition is false, it reports a diagnostic message

- Useful for detecting condition violation during simulation

- Not used in synthesis

#### **Syntax:**

**assert** condition

[ **report** error\_message ]

[ severity\_level ] ;

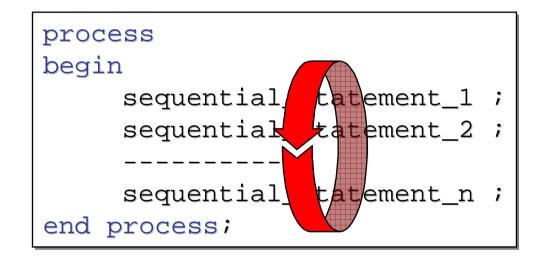

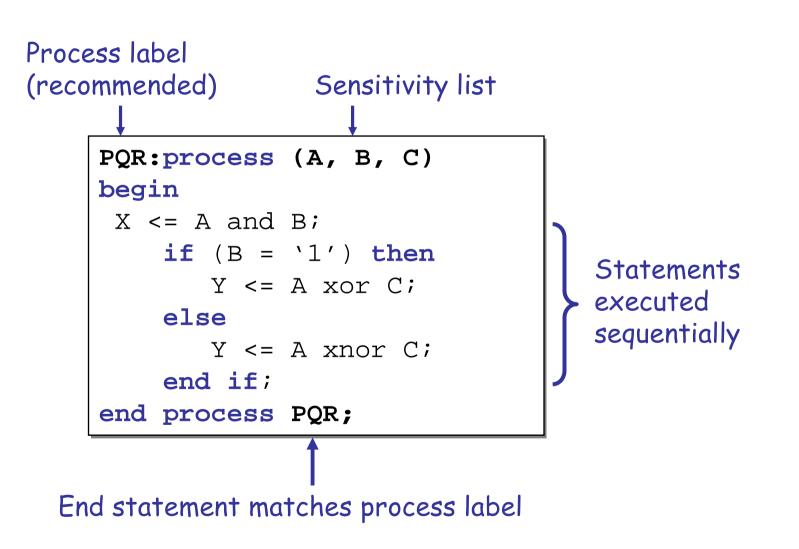

## **Process Statement**

- A Set of Sequential Statements

- All processes in a design executes CONCURRENTLY

- At a given time, ONLY ONE sequential statement executed within each process

- Communicates with the rest of a design through signals

```

[ label : ] process [ ( sensitivity_list ) ]

{ process_declarative_part }

begin

{ sequential_statements }

end process [ label ] ;

```

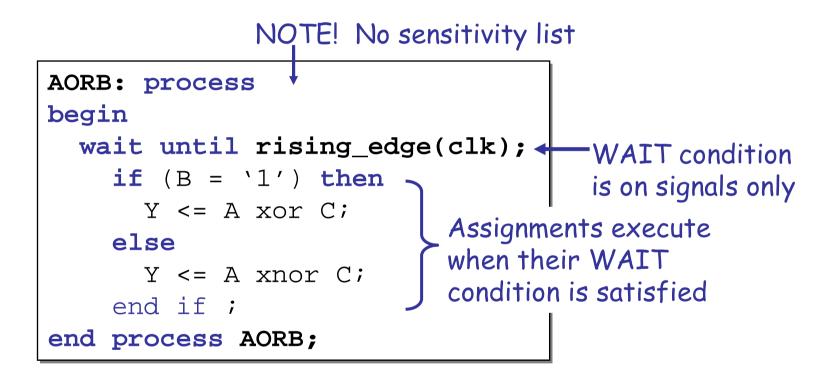

## **Process Statement (cont'd)**

#### A Pseudo Infinite Loop

• A Synchronization Mechanism is Needed

#### Sensitivity list or wait statement will be used

## **Process With Sensitivity List**

Actel

# Sequential Statements in Processes

- Executed line-by-line inside of a process or subprogram

- Typically include:

- WAIT statements

- Signal and variable assignments

- Conditionals like IF-THEN-ELSE, CASE, LOOP

#### Support other advanced statements

## **Variable Assignment Statement**

- Always executed in <u>Zero Simulation Time</u>

- Used as temporary storages

- Can not be seen by other concurrent statements

target\_variable := expression ;

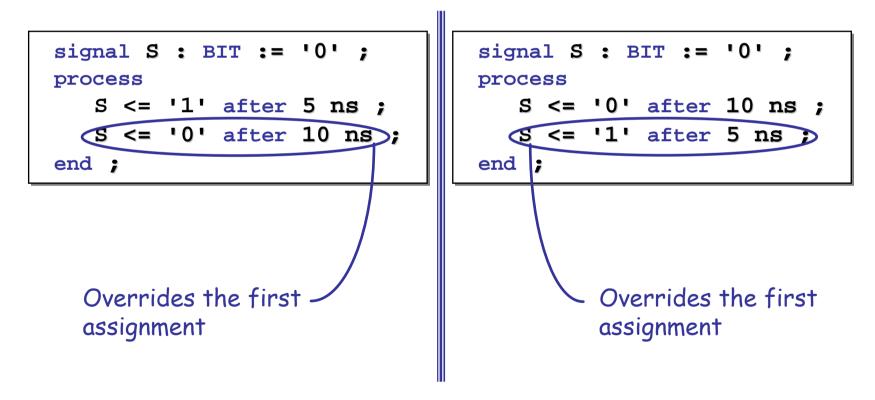

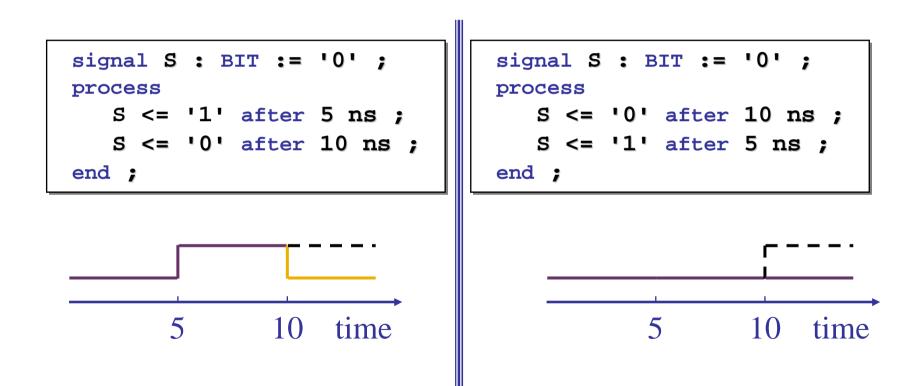

## **Signal Assignment Statement**

- Defines a <u>Driver</u> of the Signal

- Within a process, <u>Only One</u> driver for each signal

- When assigned in multiple processes, it has <u>Multiple Drivers</u>. A <u>Resolution Function</u> should be defined

target\_signal <= [ transport ] expression [ after time ] ;</pre>

## Inertial & Transport Delay Models

#### Default mode is Inertial

Inertial is useful in modeling devices that ignore spikes on the inputs

Actel

## **Inertial Delay Model**

- This is the default mode

- It is useful in modeling devices that ignore spikes on the inputs

## **Transport Delay Model**

Signals are propagated without filtering

© 2005 Nizar Abdallah

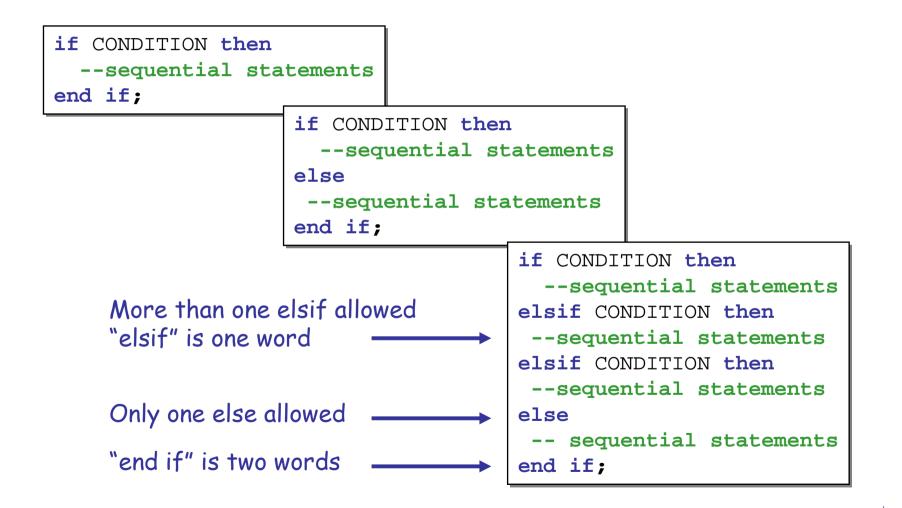

## **If-Then-Else Statement**

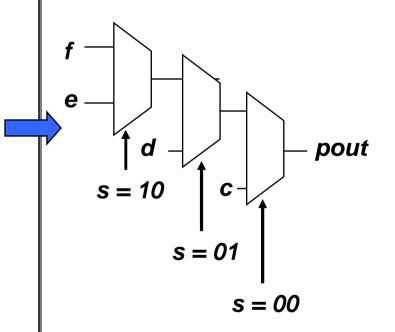

## **If-Then-Else Example**

```

library ieee;

use ieee.std logic 1164.all;

entity IF MUX is

port (C, D, E, F : in std logic;

S : in std logic vector(1 downto 0);

POUT : out std logic);

end IF MUX;

architecture BEHAVE of IF MUX is

begin

ONE: process (S, C, D, E, F)

begin

if (S = "00") then

POUT \leq C_i

elsif (S = "01") then

POUT \leq D_i

elsif (S = "10") then

POUT \leq E_i

else POUT \leq F_i

end if ;

end process ONE;

end BEHAVE;

```

#### IF implies Priority

Actel

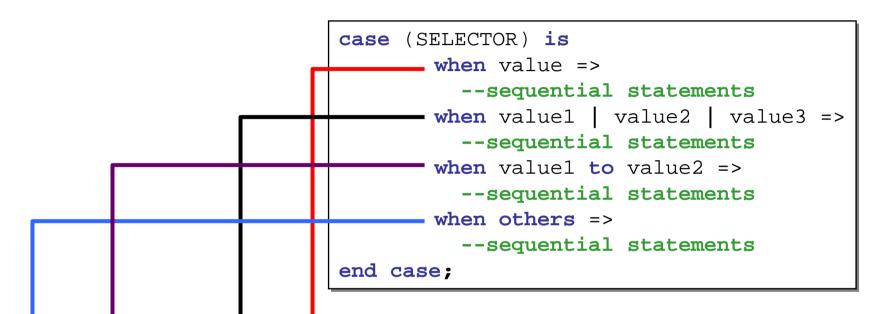

'when SELECTOR = value, then ...'

'when SELECTOR = value1 OR value2 OR value 3, then ..."

'when SELECTOR falls within the range from value1 to value2, then ..."

'when SELECTOR = any other value, then ...'

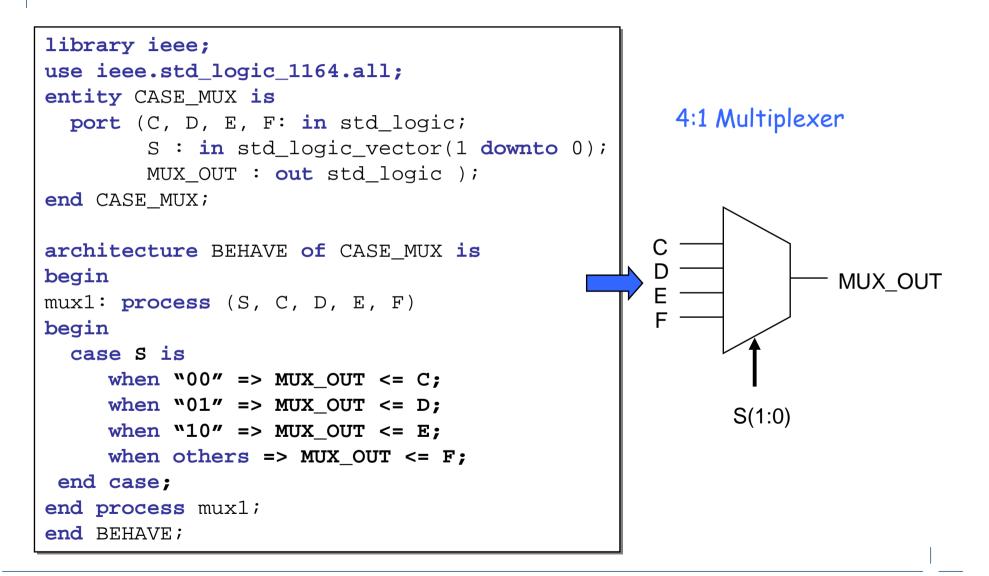

#### **Case Example: 4-to-1 Mux**

VHDL & FPGA Architectures

## Case Example: Bi-Directional Buffers Actel

```

library ieee;

use ieee.std logic 1164.all;

entity BIBUF is

port (A, E: in std_logic;

Y : inout std logic;

B : out std logic );

end BIBUF ;

architecture BEHAVE of BIBUF is

begin

ONE: process (A,E)

begin

case E is

when 1' => Y <= A;

when 0' => Y <= Z';

when others => Y <= 'X';

end case;

end process ONE;

B \leq Y;

end BEHAVE;

```

## **Questions ?**

VHDL & FPGA Architectures

© 2005 Nizar Abdallah