1977-5

#### First ICTP Regional Microelectronics Workshop and Training on VHDL for Hardware Synthesis and FPGA Design in Asia-Pacific

16 June - 11 July, 2008

Scaling.

Paulo Moreira PH ESE ME Division C E R N CH-1211 Geneva 23 SWITZERLAND

## Outline

- Introduction

- Transistors

- The CMOS inverter

- Technology

- Scaling

- Scaling objectives

- Scaling variables

- Scaling consequences

- Gates

- Sequential circuits

- Storage elements

- Phase-Locked Loops

- Example

# Technology scaling

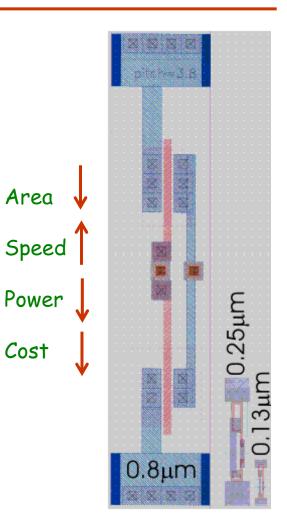

- Technology scaling has a <u>threefold</u> <u>objective</u>:

- Increase the transistor density

- Reduce the gate delay

- Reduce the power consumption

- At present, between two technology generations, the objectives are:

- Doubling of the transistor density;

- Reduction of the gate delay by 30% (43% increase in frequency);

- Reduction of the power by 50% (at 43% increase in frequency);

## Technology scaling

- How is scaling achieved?

- All the device dimensions (lateral and vertical) are reduced by  $1/\alpha$

- Concentration densities are increased by  $\boldsymbol{\alpha}$

- Device voltages reduced by  $1/\alpha$  (not in all scaling methods)

- Typically  $1/\alpha = 0.7$  (30% reduction in the dimensions)

# Technology scaling

#### The scaling variables are:

- Supply voltage:  $V_{dd} \rightarrow V_{dd} / \alpha$  $L \rightarrow L/\alpha$ - Gate length:

- $\begin{array}{cccc} W & \rightarrow & W \,/\,\alpha \\ t_{ox} & \rightarrow & t_{ox} \,/\,\alpha \\ X_{j} & \rightarrow & X_{j} \,/\,\alpha \end{array}$ - Gate width:

- Gate-oxide thickness:

- Junction depth:

- Substrate doping:  $N_A \rightarrow N_A \times \alpha$

This is called **constant field** scaling because the electric field across the gate-oxide does not change when the technology is scaled

If the power supply voltage is maintained constant the scaling is called **constant voltage**. In this case, the electric field across the gate-oxide increases as the technology is scaled down.

Due to gate-oxide breakdown, below  $0.8\mu m$  only "constant" field" scaling is used.

#### Scaling consequences

Some consequences of 30% scaling in the constant field regime ( $\alpha = 1.43$ ,  $1/\alpha = 0.7$ ):

• Device/die area:

$W \times L \rightarrow (1/\alpha)^2 = 0.49$

- In practice, microprocessor <u>die size grows</u> about 25% per technology generation! This is a result of added functionality.

- Transistor density:

(unit area) /(W  $\times$  L)  $\rightarrow$   $\alpha^2$  = 2.04

- In practice, <u>memory density</u> has been scaling as expected.

#### Scaling consequences

• Gate capacitance:

W × L /

$$t_{ox} \rightarrow 1/\alpha = 0.7$$

• Drain current:

$$(W/L) \times (V^2/t_{ox}) \rightarrow 1/\alpha = 0.7$$

• Gate delay:

$(C \times V) / I \rightarrow 1/\alpha = 0.7$ Frequency  $\rightarrow \alpha = 1.43$

In practice, microprocessor frequency has doubled every technology generation (2 to 3 years)! This faster increase rate is due to super-pipelined architectures ("less gates per clock cycle")

#### Scaling consequences

• Power:

$$C \times V^2 \times f \rightarrow (1/\alpha)^2 = 0.49$$

• Power density:

$$1/t_{ox} \times V^2 \times f \rightarrow 1$$

- In practice, the power density has been increasing faster than foreseen by the simple scaling theory. This is due to the faster them foreseen increase in frequency

## Interconnects scaling

- Interconnects scaling:

- Higher densities are only possible if the interconnects also scale.

- Reduced width  $\rightarrow$  increased resistance

- Denser interconnects  $\rightarrow$  <u>higher capacitance</u>

- To account for <u>increased parasitics</u> and <u>integration</u> <u>complexity</u> **more interconnection layers** are added:

- thinner and tighter layers  $\rightarrow$  local interconnections

- thicker and sparser layers  $\rightarrow$  global interconnections and power

## Scaling table

| Parameter                               | Constant Field           | Constant Voltage   |                      |  |  |

|-----------------------------------------|--------------------------|--------------------|----------------------|--|--|

| Supply voltage (V <sub>dd</sub> )       | 1/α                      | 1                  | <b>↑</b>             |  |  |

| Length (L)                              | 1/α                      | 1/α                |                      |  |  |

| Width (W)                               | 1/α                      | 1/α                | Scaling<br>Variables |  |  |

| Gate-oxide thickness (t <sub>ox</sub> ) | 1/α                      | 1/α                |                      |  |  |

| Junction depth (X <sub>i</sub> )        | 1/α                      | 1/α                |                      |  |  |

| Substrate doping $(N_A)$                | α                        | α                  |                      |  |  |

| Electric field across gate oxide (E)    | 1                        | α                  | Ť                    |  |  |

| Depletion layer thickness               | 1/α                      | 1/α                |                      |  |  |

| Gate area (Die area)                    | $1/\alpha^2$             | <b>1/</b> α²       | Device               |  |  |

| Gate capacitance (load) (C)             | 1/α                      | 1/α                | Repercussion         |  |  |

| Drain-current (I <sub>dss</sub> )       | 1/α                      | α                  |                      |  |  |

| Transconductance (g <sub>m</sub> )      | 1                        | α                  | Ļ                    |  |  |

| Gate delay                              | 1/α                      | <b>1/</b> \alpha^2 | Î                    |  |  |

| Current density                         | α                        | $\alpha^3$         |                      |  |  |

| DC & Dynamic power dissipation          | $1/\alpha^2$             | α                  | Circuit              |  |  |

| Power density                           | 1                        | $\alpha^3$         | Repercussion         |  |  |

| Power-Delay product                     | <b>1/</b> α <sup>3</sup> | 1/α                | Ļ                    |  |  |

| Paulo Moreira                           | Technology scaling       |                    |                      |  |  |

|                                         |                          |                    |                      |  |  |

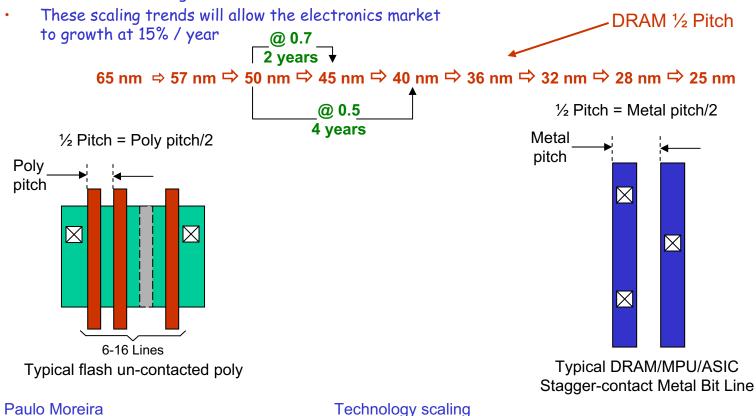

## 2004 and beyond ...

- International Technology Roadmap For Semiconductors (ITRS 2007)

- Forecast from the semiconductor industry with a 15 year perspective:

- Near-term: 2007 2015

- Long-term: 2016 2022.

- The forecast is done in terms of 1<sup>st</sup> year of production:

- Product shipment first exceeds 10K units/month (using production tooling)

- A near-term scaling ratio of @ 0.7 is assumed

## 2008 and beyond ...

| ITRS Road Map, 2007 edition:                     | 2008   | 2010           | 2012   | <b>2022</b> (year of first production) |

|--------------------------------------------------|--------|----------------|--------|----------------------------------------|

| DRAM ½ pitch (nm)                                | 57     | 45             | 36     | 11                                     |

| μP M1 ½ pitch (nm)                               | 59     | 45             | 36     | 11                                     |

| Flash Poly ½ pitch (nm)                          | 45     | 36             | 28     | 9 <i>IEEE Spectrum, July</i> 1999      |

| Gate length, printed (nm)                        | 38     | 30             | 24     | 7.5 Special report: "The 100-          |

| Gate length, physical (nm)                       | 23     | 18             | 14     | 4.5 <b>million transistor IC</b> "     |

| DRAM:                                            |        |                |        |                                        |

| Bits/chip (Gbits)                                | 2.15   | 4.2            | 4.29   | 68.72                                  |

| Chip size (mm²)                                  | 74     | 93             | 59     | 93                                     |

| Gbits/cm <sup>2</sup>                            | 2.9    | 4.62           | 7.33   | 73.85                                  |

| Flash:                                           |        |                |        |                                        |

| Bits/chip (Gbits) SLC                            | 8.59   | 17.18          | 17.18  | 274.88                                 |

| Chip size (mm²)                                  | 101.80 | 128.26         | 128.26 | 128.26                                 |

| Gbits/cm <sup>2</sup>                            | 8.44   | 13.40          | 21.30  | 214.0                                  |

| Bits/chip (Gbits) MLC [2 bits/cell]              | 17.18  | 34.36          | 34.36  | 549.76                                 |

| Chip size (mm²)                                  | 101.80 | 128.26         | 80.80  | 128.26                                 |

| Gbits/cm <sup>2</sup>                            | 16.90  | 26.80          | 42.50  | 429.0                                  |

| Bits/chip (Gbits) MLC [4 bits/cell]              | 34.36  | 68.72          | 68.72  | 1099.51                                |

| Chip size (mm²)                                  | 101.80 | 128.26         | 80.80  | 128.26                                 |

| Gbits/cm <sup>2</sup>                            | 33.8   | 53.6           | 85.1   | 857.0                                  |

| μP (high performance):                           |        |                |        |                                        |

| Transistors/chip (Millions)                      | 1106   | 2212           | 2212   | 35391                                  |

| Chip size (mm²)                                  | 246    | 310            | 195    | 310                                    |

| Transistors/cm <sup>2</sup> (M/cm <sup>2</sup> ) | 449    | 714            | 1133   | 11416                                  |

| Total pads                                       | 3072   | 3072           | 3072   | 3072 (66.7% allocated for power        |

| Paulo Moreira                                    | Tech   | nology scaling | 3      | and ground)<br>11                      |

## 2008 and beyond ...

| ITRS Road Map, 2007 edition:                       | 2008 | 2010 | 2012    | 2022 (year of first production) |

|----------------------------------------------------|------|------|---------|---------------------------------|

| Performance:                                       |      |      |         |                                 |

| On-Chip clock (GHz)<br>Chip-to-board (GHz)         | 5.0  | 5.9  | 6.8     | 14                              |

| Wiring levels (maximum)<br>Wiring levels (minimum) | 12   | 12   | 12      | 15                              |

| Power supply:                                      |      |      |         |                                 |

| Vdd (V):                                           | 1.0  | 1.0  | 0.9     | 0.65                            |

| Maximum allowable power (W)                        | 198  | 198  | 198     | 198 (With heat sink)            |

| Lithography:                                       |      |      |         |                                 |

| Field size - area (mm²)                            | 858  | 858  | 858     | 858                             |

| Wafer diameter (mm)                                | 300  | 300  | 300/450 | 450                             |