1977-7

#### First ICTP Regional Microelectronics Workshop and Training on VHDL for Hardware Synthesis and FPGA Design in Asia-Pacific

16 June - 11 July, 2008

Sequential circuits.

Paulo Moreira

PH ESE ME Division

CERN

CH-1211 Geneva 23

SWITZERLAND

## Outline

- Introduction

- Transistors

- The CMOS inverter

- Technology

- Scaling

- Gates

- Sequential circuits

- Time in logic circuits

- D flip-flop

- State machine timing

- Interconnects

- Clock distribution

- Storage elements

- Phase-Locked Loops

- Example

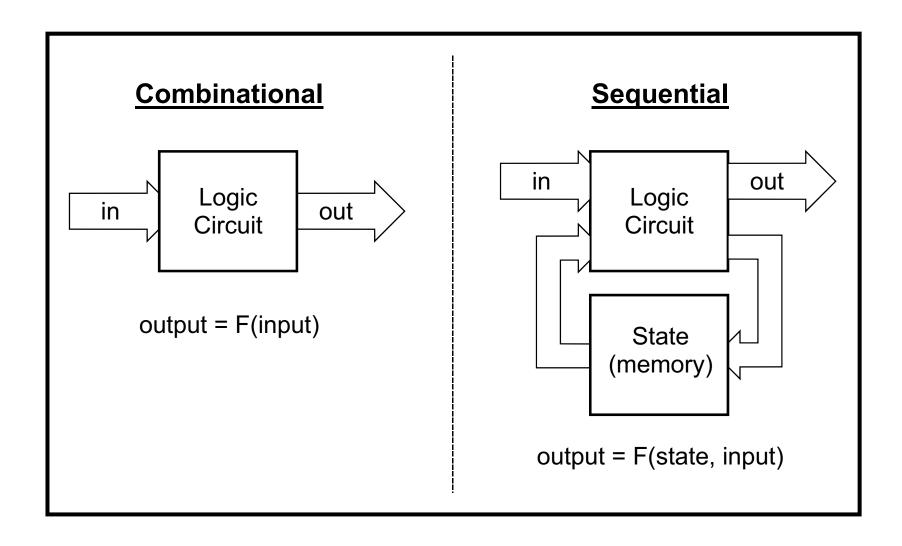

## "Time also counts"

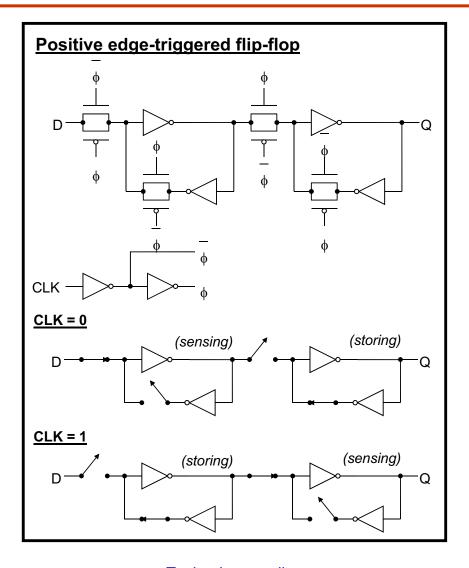

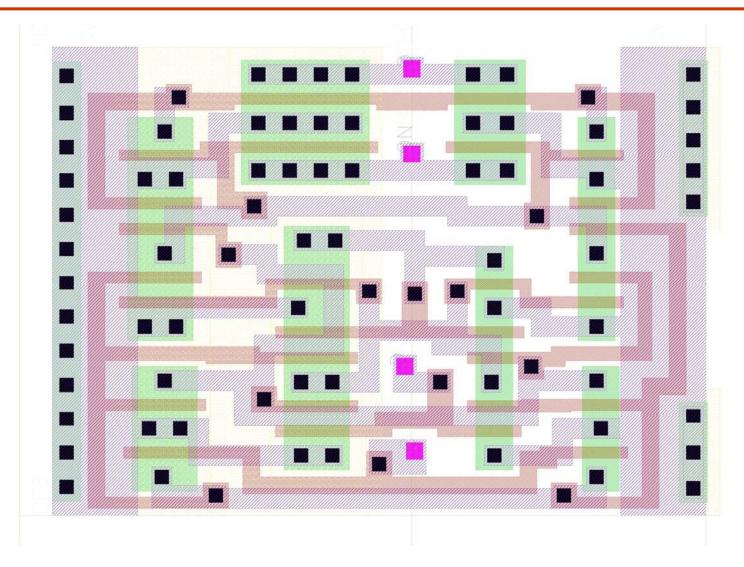

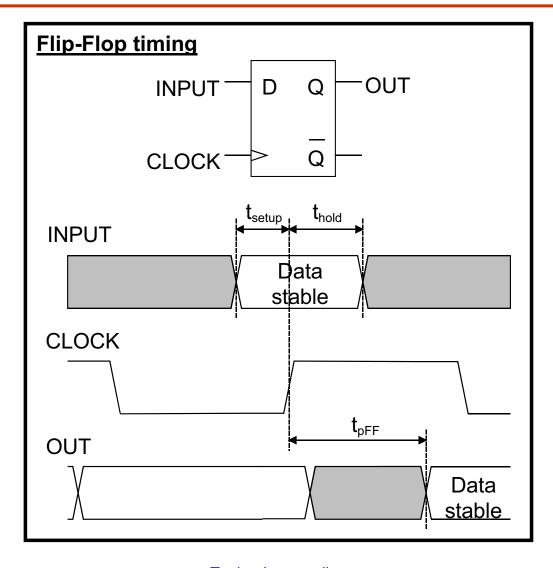

# D Flip-Flop

# D Flip-Flop

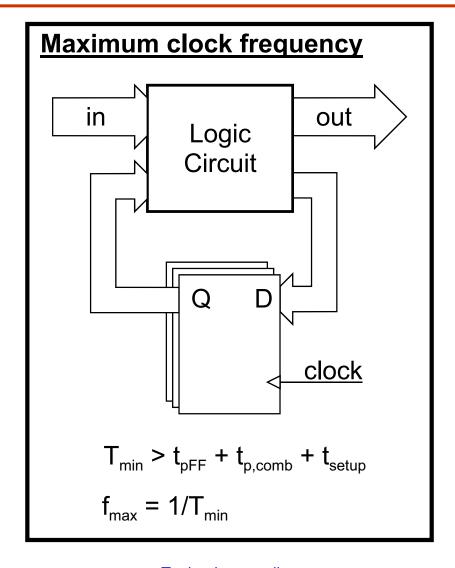

# State machine timing

# State machine timing

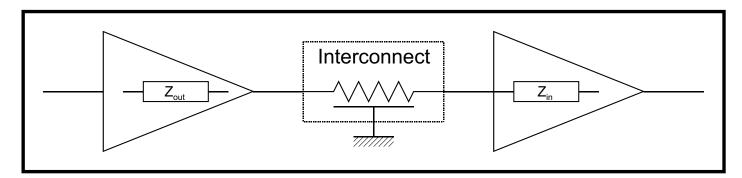

- The previous result assumes that signals can propagate instantaneously across interconnects

- In reality interconnects are metal or polysilicon structures with associated resistance and capacitance.

- That, introduces signal propagation delay that has to be taken into account for reliable operation of the circuit

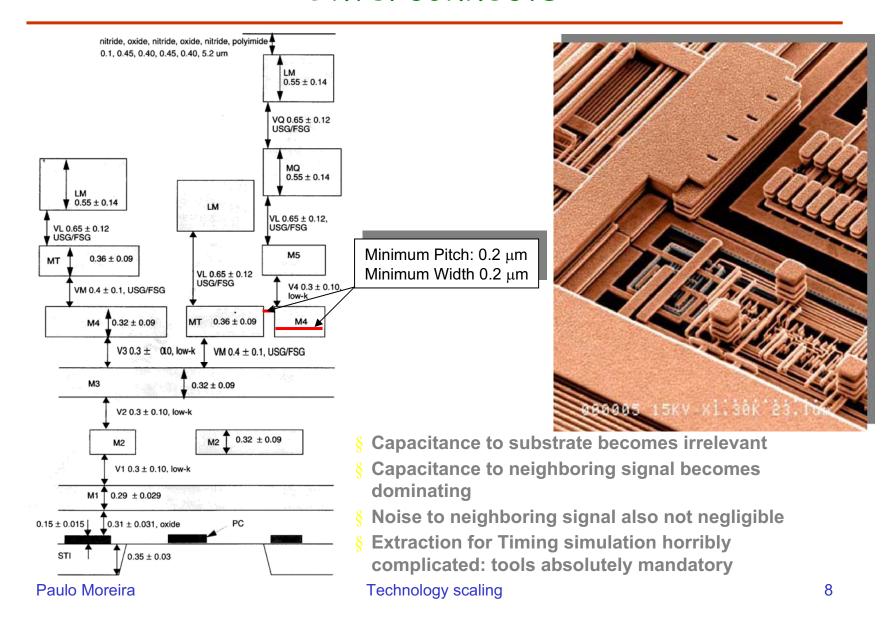

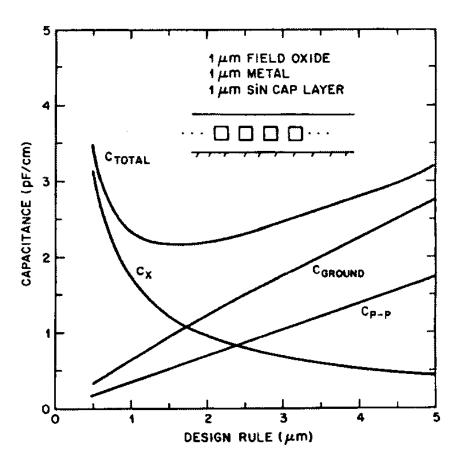

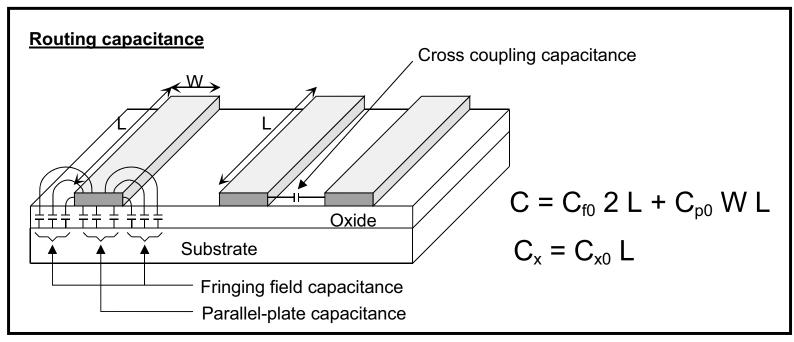

Figure 3.10: Interconnect capacitance including wire-to-wire capacitance [Schaper83]. (© 1983 IEEE)

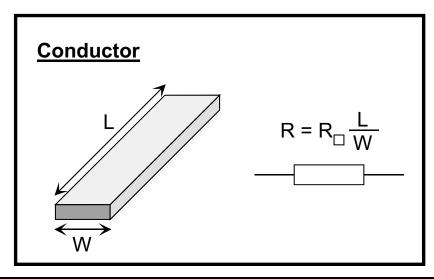

| Film                         | Sheet resistance ( $\Omega$ /square)     |  |

|------------------------------|------------------------------------------|--|

| n-well                       | 310                                      |  |

| p+, n+ diffusion (salicided) | 4                                        |  |

| polysilicon (salicided)      | 4                                        |  |

| Metal 1                      | 0.12                                     |  |

| Metal 2, 3 and 4             | 0.09                                     |  |

| Metal 5                      | 0.05                                     |  |

|                              |                                          |  |

|                              | (Typical values for an advanced process) |  |

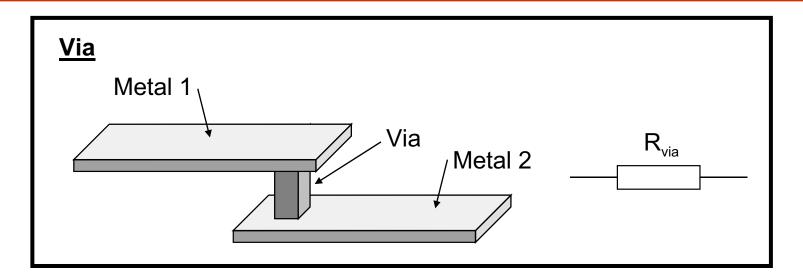

- Via or contact resistance depends on:

- The contacted materials

- The contact area

| Via/contact       | Resistance ( $\Omega$ ) |

|-------------------|-------------------------|

| M1 to n+ or p+    | 10                      |

| M1 to Polysilicon | 10                      |

| V1, 2, 3 and 4    | 7                       |

| Interconnect layer  | Parallel-plate (fF/μm²) | Fringing (fF/μm) |

|---------------------|-------------------------|------------------|

| Polysilicon to sub. | 0.058                   | 0.043            |

| Metal 1 to sub.     | 0.031                   | 0.044            |

| Metal 2 to sub.     | 0.015                   | 0.035            |

| Metal 3 to sub.     | 0.010                   | 0.033            |

|                     |                         |                  |

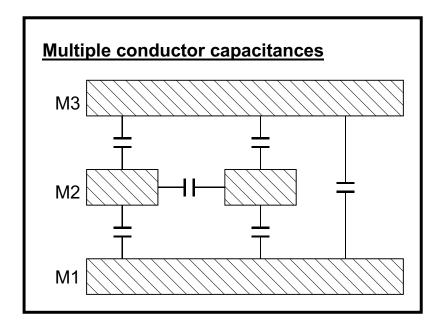

Three dimensional field simulators are required to accurately compute the capacitance of a multi-wire structure

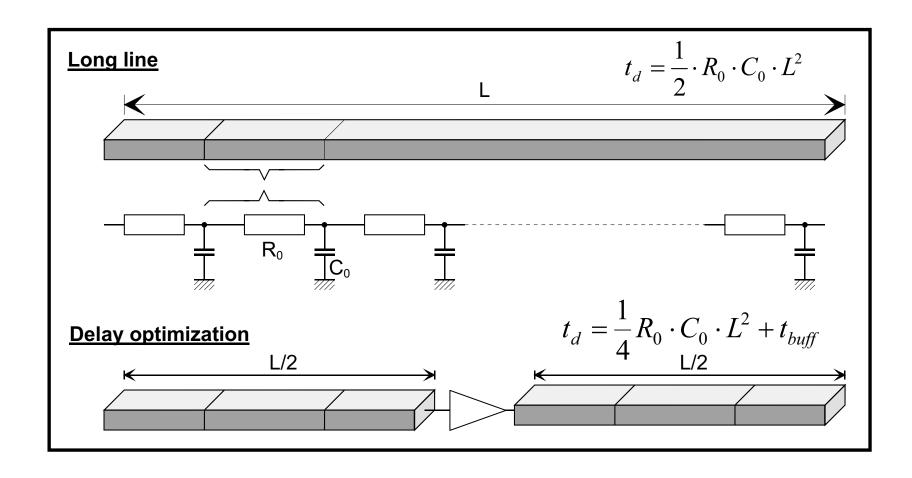

- Delay depends on:

- Impedance of the driving source

- Distributed resistance/capacitance of the wire

- Load impedance

- Distributed RC delay:

- Can be dominant in long wires

- Important in polysilicon wires (relatively high resistance)

- Important in salicided wires

- Important in heavily loaded wires

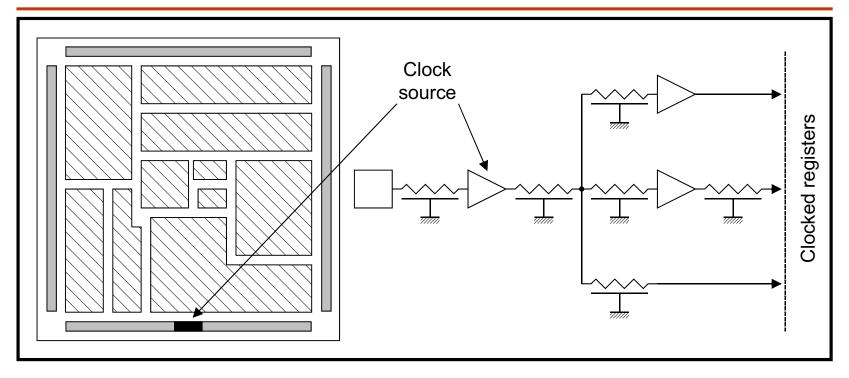

- Clock signals are "special signals"

- Every data movement in a synchronous system is referenced to the clock signal

- Clock signals:

- Are typically loaded with high fanout

- Travel over the longest distances in the IC

- Operate at the highest frequencies

- "Equipotential" clocking:

- In a synchronous system all clock signals are derived from a single clock source ("clock reference")

- Ideally: clocking events should occur at all registers  $\frac{\text{simultaneously}}{\text{simultaneously}}$  ... =  $\frac{\text{t}(\text{clk}_{i-1})}{\text{t}(\text{clk}_{i})} = \frac{\text{t}(\text{clk}_{i+1})}{\text{t}(\text{clk}_{i+1})} = \dots$

- In practice: clocking events will occur at slightly different instants among the different registers in the data path

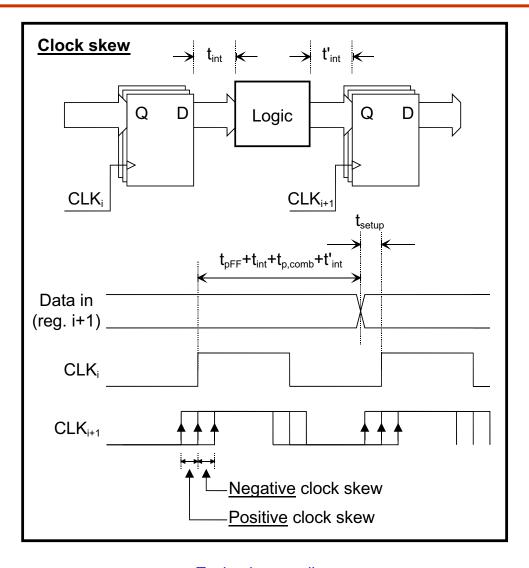

Skew: difference between the clocking instants of two "sequential" registers:

Skew =

$$t(CLK_i)$$

-  $t(CLK_{i+1})$

Maximum operation frequency:

$$T_{\min} = \frac{1}{f_{\max}} = t_{dFF} + t_{\inf} + t_{p,comb} + t_{\inf}' + t_{setup} + t_{skew}$$

- Skew > 0, decreases the operation frequency

- Skew < 0, can be used to compensate a critical data path <u>BUT</u> this results in more positive skew for the next data path!

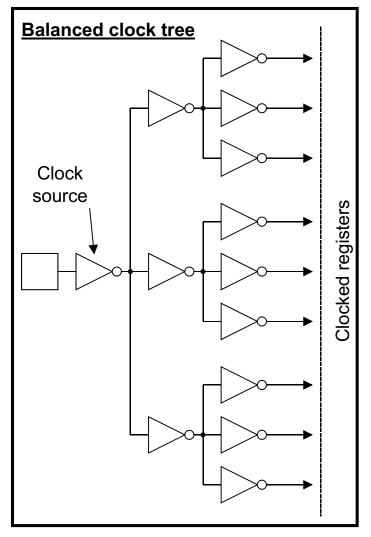

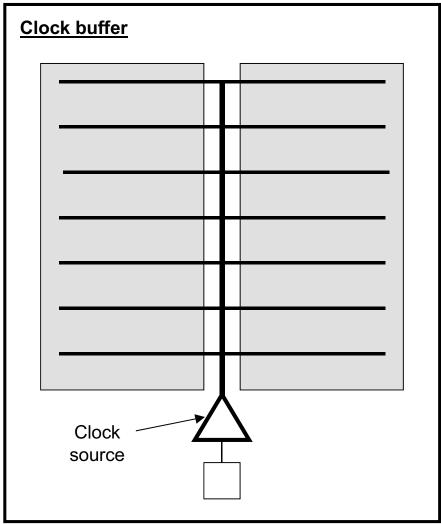

- Different clock paths can have different delays due to:

- Differences in line lengths from clock source to the clocked registers

- Differences in passive interconnect parameters (line resistance/capacitance, line dimensions, ...)

- Differences in delays in the active buffers within the clock distribution network:

- Differences in active device parameters (threshold voltages, channel mobility)

- In a well designed and balanced clock distribution network, the distributed clock buffers should be the principal source of clock skew

#### Clock buffers:

- Amplify the clock signal degraded by the interconnect impedance

- Isolate the local clock lines from upstream load impedances