2065-19

#### Advanced Training Course on FPGA Design and VHDL for Hardware Simulation and Synthesis

26 October - 20 November, 2009

FPGA Design & VHDL Fundamentals of FPGAs

Nizar Abdallah ACTEL Corp. 2061 Stierlin Court Mountain View CA 94043-4655 U.S.A.

## **FPGA Design & VHDL**

Nizar Abdallah nizar@ieee.org

October 2009

## **Fundamentals of FPGAs**

#### Agenda

- FPGA Fundamentals

- Mixed-Signal FPGAs

- Actel Fusion Architecture

- FPGA Design Considerations

- Trends

- Choosing an FPGA

- Development Tools

- Summary

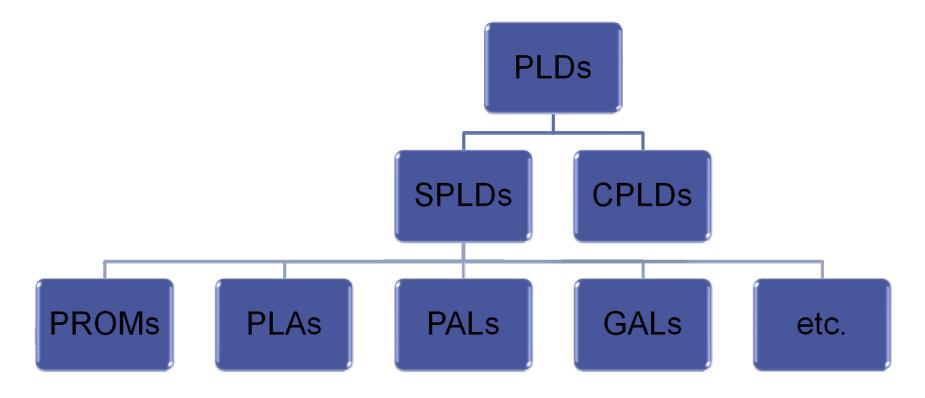

#### Before FPGAs

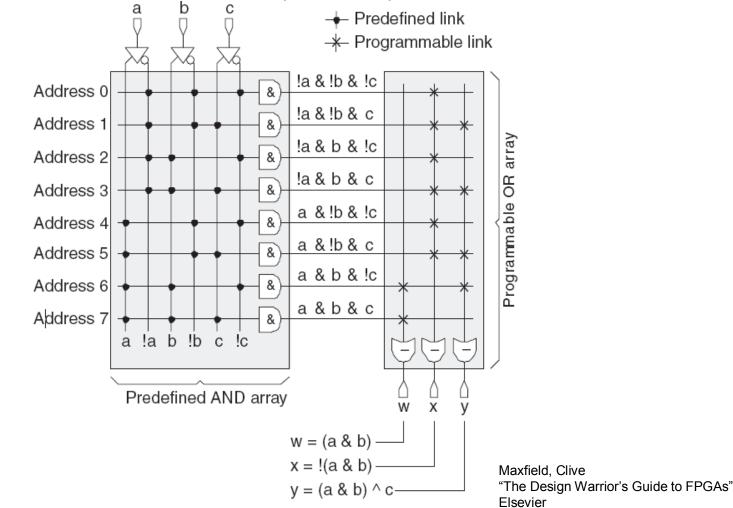

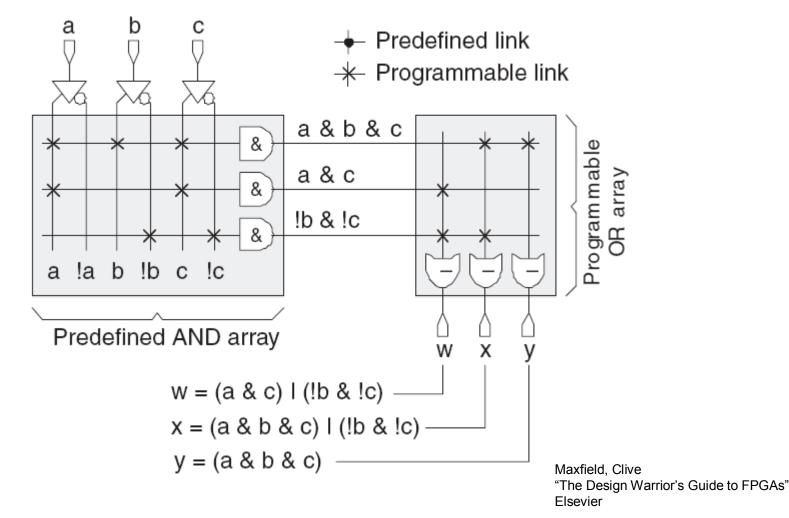

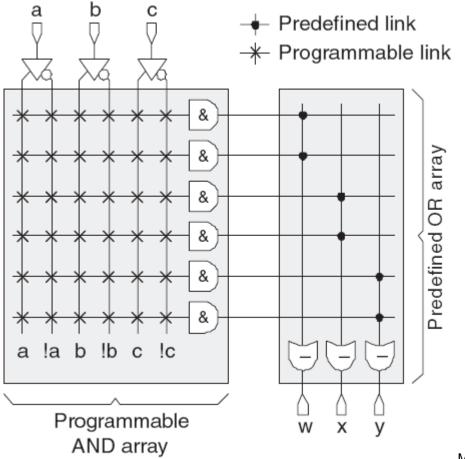

Before FPGAs: Simple PLDs (SPLDs)–PROMs

Before FPGAs: Simple PLDs (SPLDs)–PLAs

Before FPGAs: Simple PLDs (SPLDs)–PALs

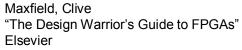

Before FPGAs: Complex PLDs (CPLDs)

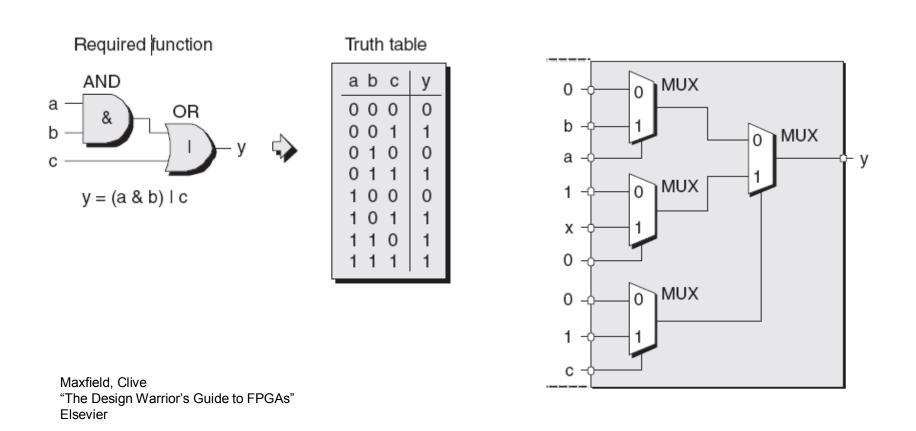

Maxfield, Clive "The Design Warrior's Guide to FPGAs" Elsevier

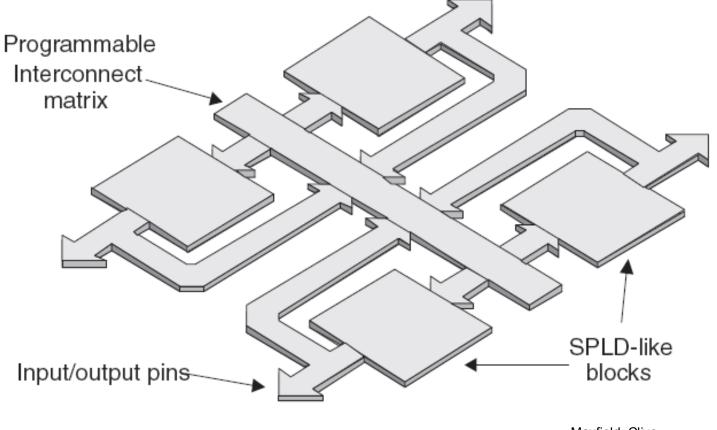

#### The GAP

**FPGA Fundamentals: Definition**

Field Programmable Gate Array

A large number of logic gates in an IC array that can be connected (configured) electrically

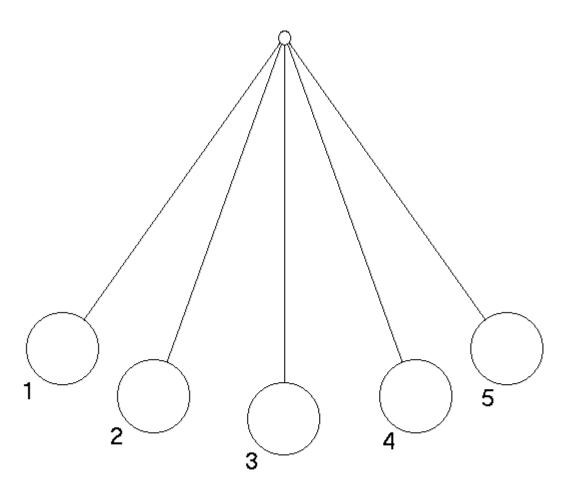

#### The Four Components of FPGAs

- The Configuration Element

- The Logic Module

- The Memory

- Control Circuits/Special Features

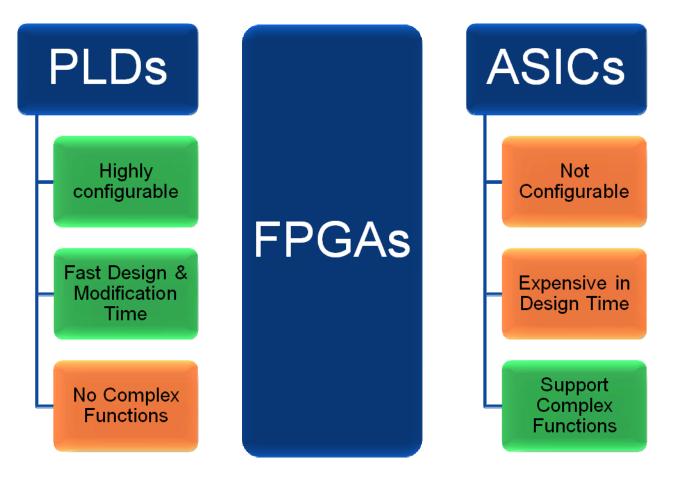

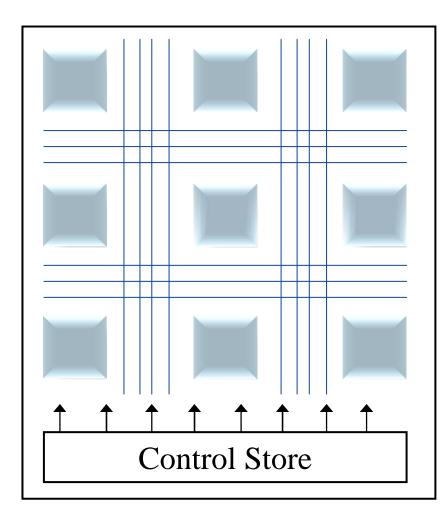

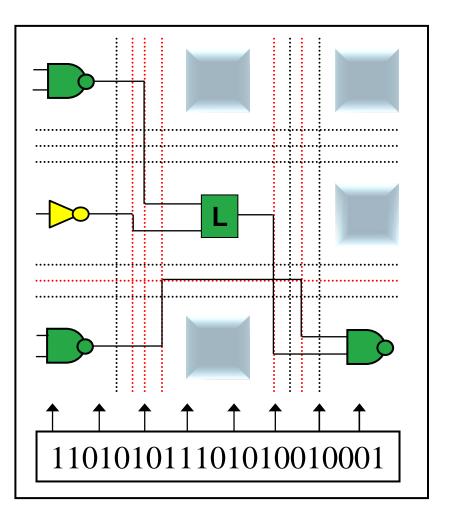

#### FPGA Fundamentals: Basic Architecture

#### Generic FPGA Architecture

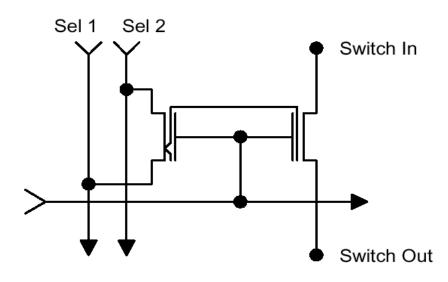

The Interconnect Switch

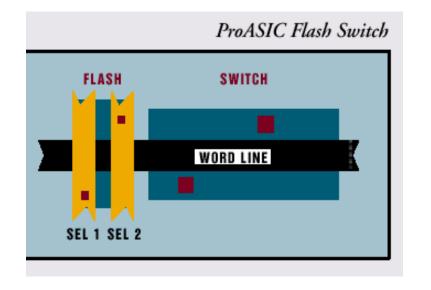

#### **ProASIC**, **ProASIC**<sup>Plus</sup>, **ProASIC3** Routing Switch

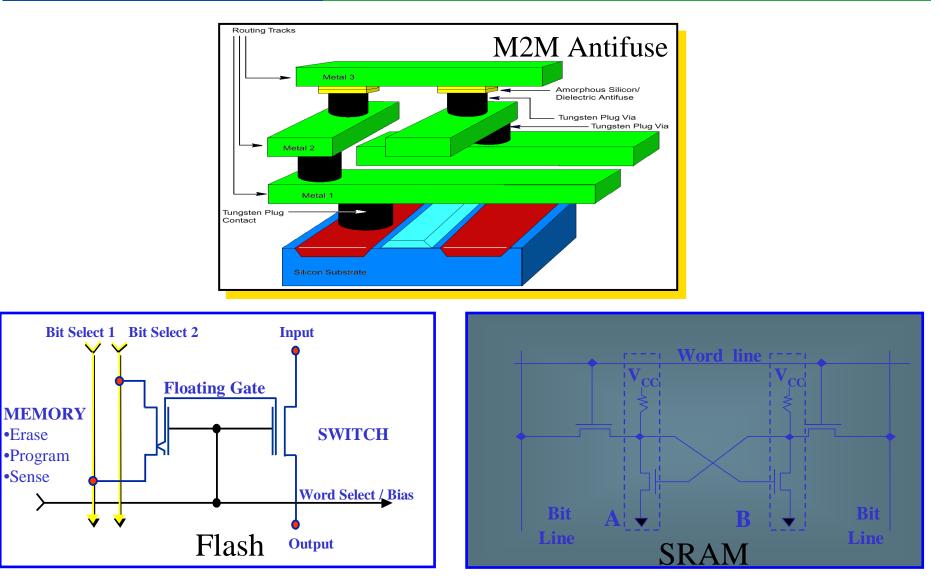

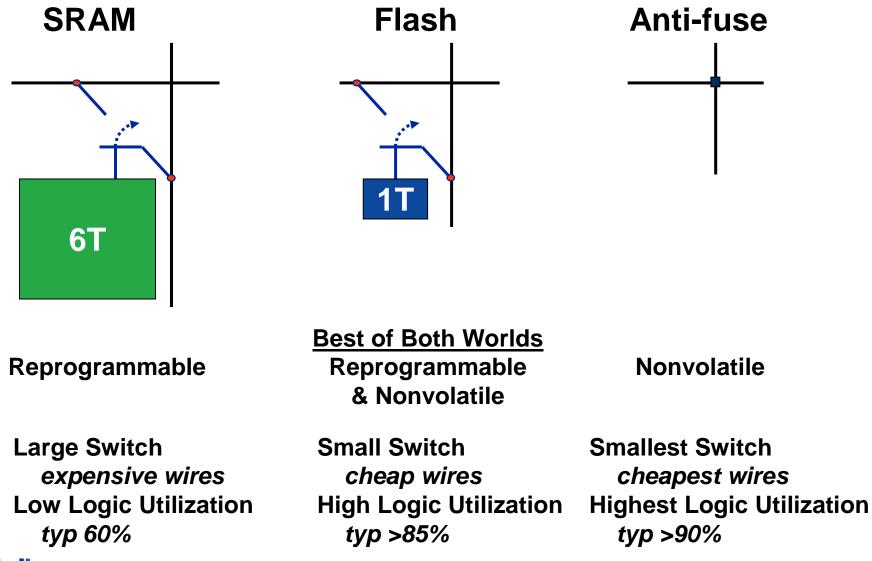

#### Programming Technologies

| Feature                              | SRAM             | Anti-fuse                 | Flash                     |

|--------------------------------------|------------------|---------------------------|---------------------------|

| Technology node                      | State of the art | Behind by 1-2 generations | Behind by 1-2 generations |

| Reprogrammable                       | Yes              | No                        | Yes                       |

| Preserves configuration when off     | No               | Yes                       | Yes                       |

| Requires external configuration file | Yes              | No                        | No                        |

| Instantly on                         | No               | Yes                       | Yes                       |

| IP security                          | Acceptable       | Excellent                 | Excellent                 |

| Power consumption                    | Medium           | Low                       | Low                       |

#### **FPGA Fundamentals: Logic Elements**

#### LUT based vs. MUX based

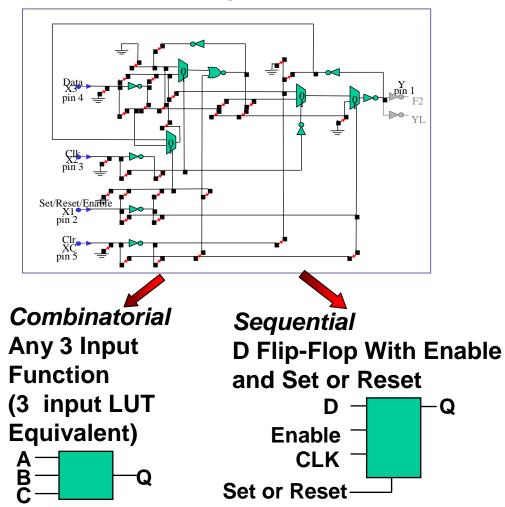

#### **FPGA Fundamentals: Logic Elements**

Actel's Flash MUX based Logic Module

#### FPGA Fundamentals: An Example

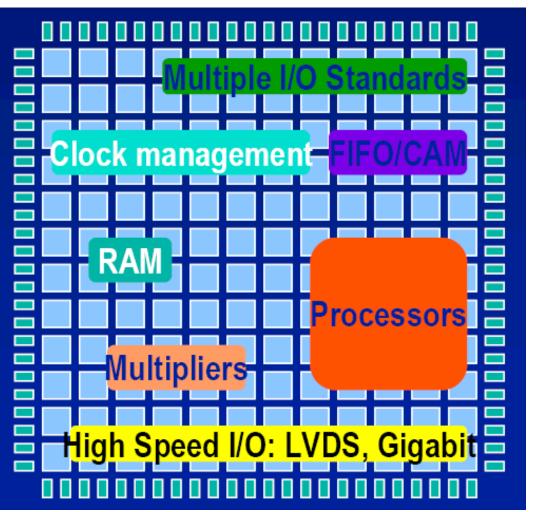

#### FPGA Fundamentals: Complex Architecture

A Plethora of IPs...

# Fundamentals of Mixed-Signal FPGAs

## Actel Fusion® FPGA

FUSION

Analog Signal

Digital Signal

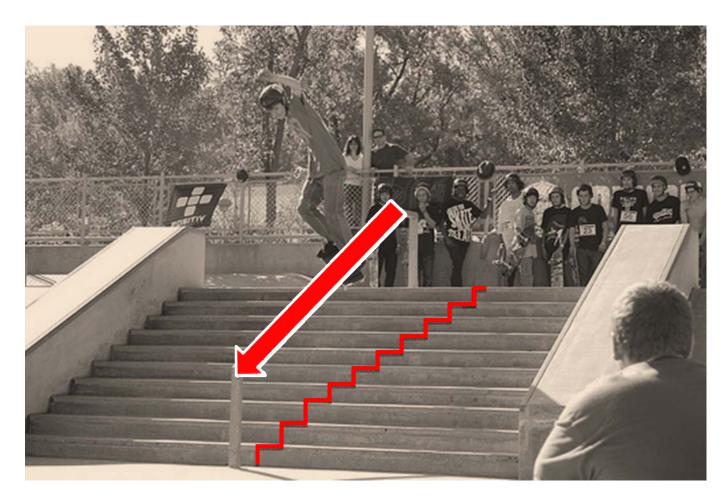

#### Quanta

Pendulum Tracking

Pendulum Tracking-5 Quanta-

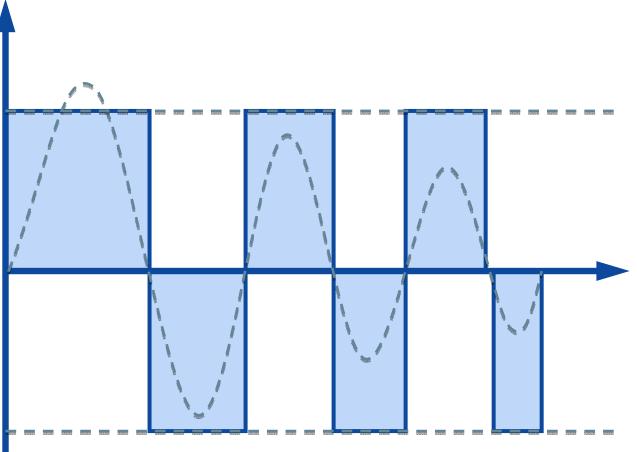

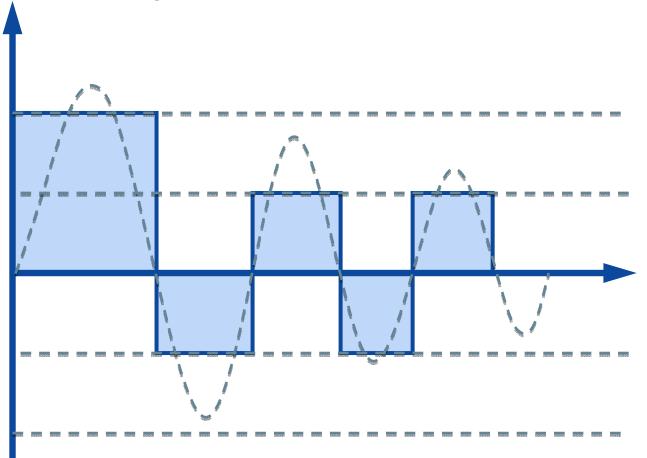

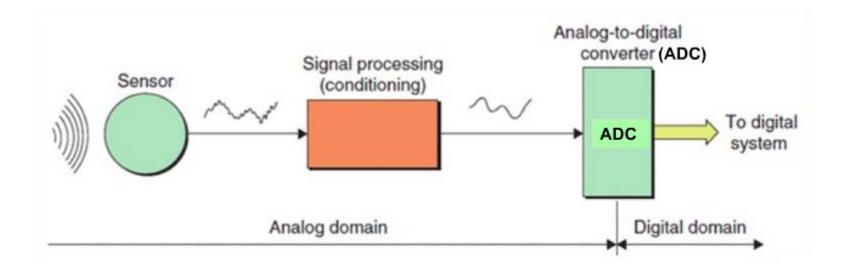

Sampling and Quantization

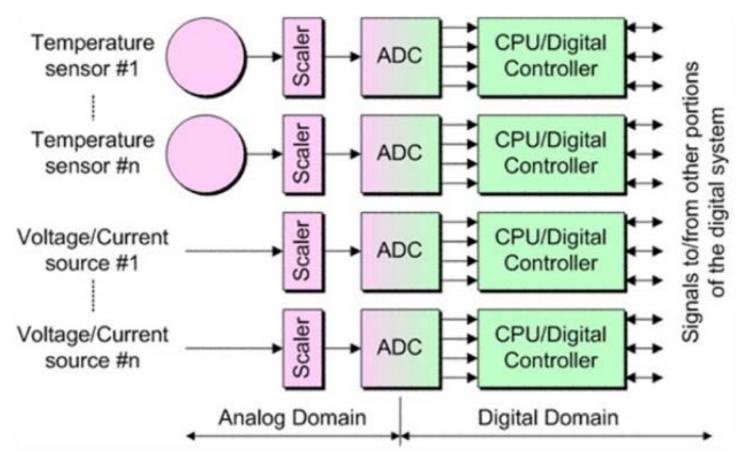

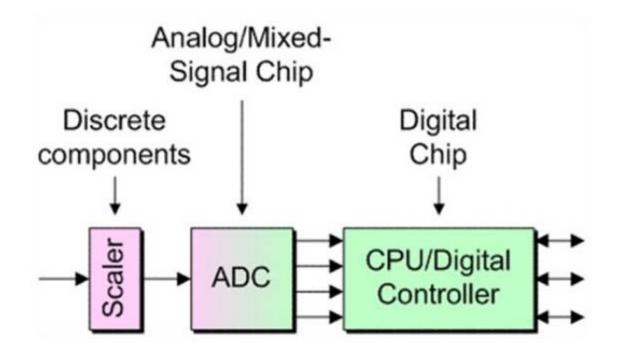

#### System Monitoring

Separate Analog and Digital

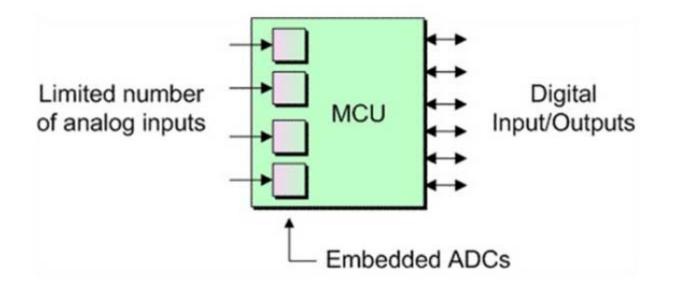

#### Microcontrollers

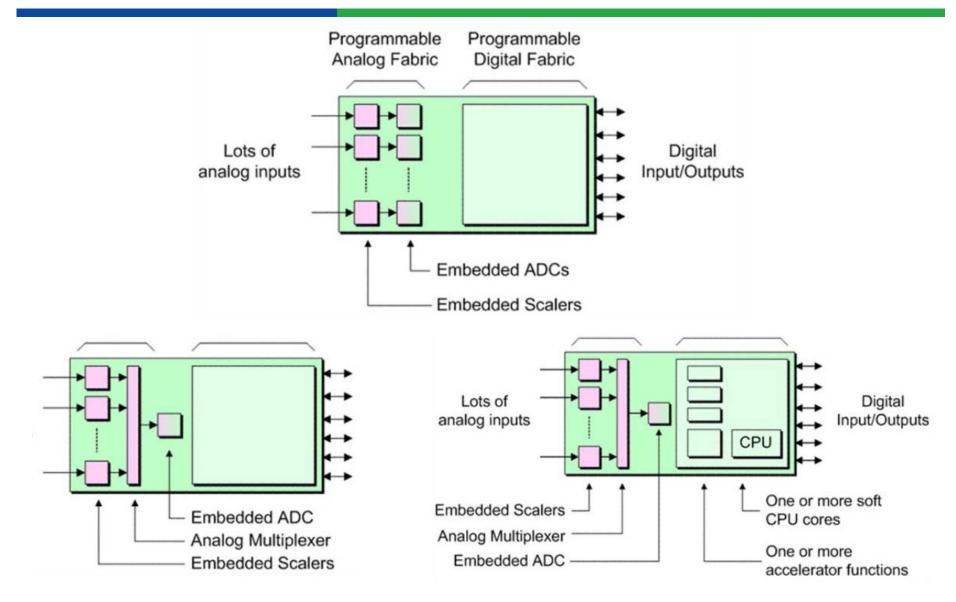

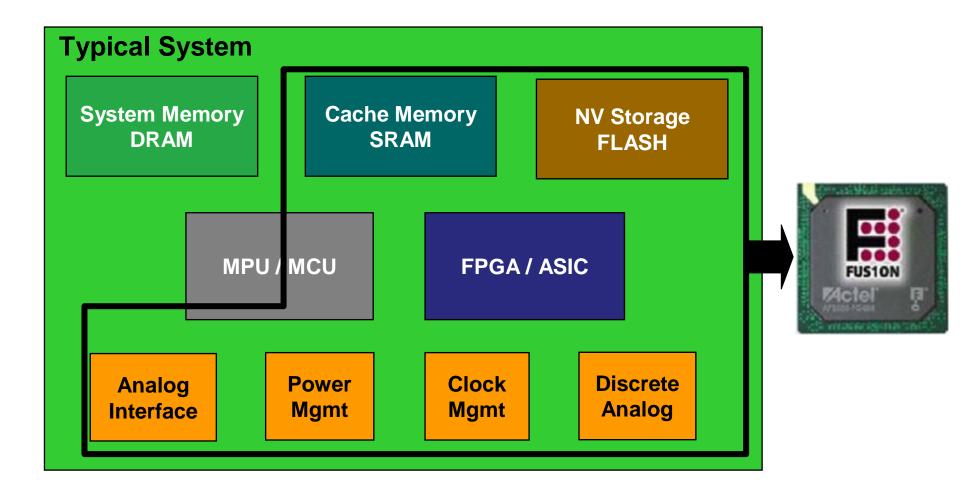

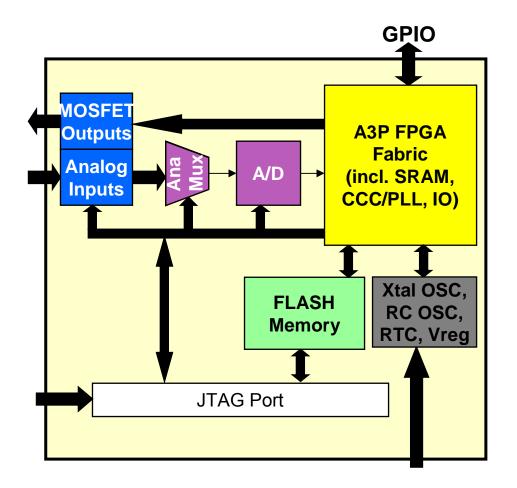

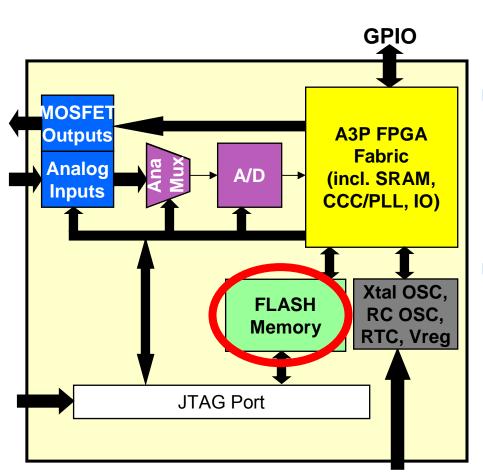

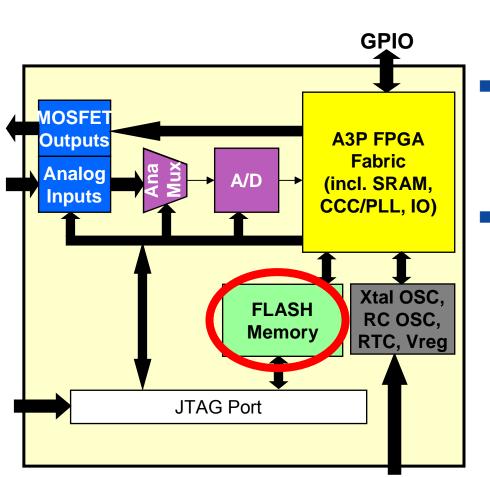

## Mixed-Signal FPGAs: All in one

## Actel's Fusion Mixed-Signal FPGA

## Actel's Fusion Mixed-Signal FPGA

- Flash based

- Up to 30 analog inputs

- ADC (12 bits, 600 ksps)

- Up to 1.5M system gates

- Advanced I/O support

- SRAM / FIFO blocks

- Embedded Flash Memory

- ... and much more...

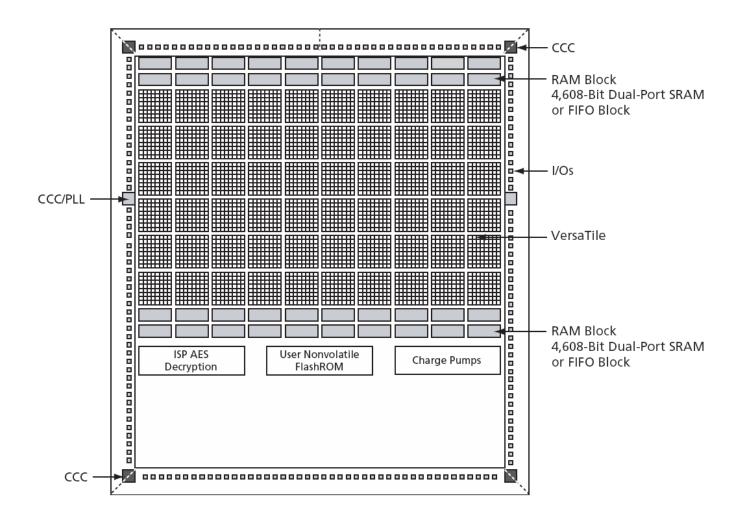

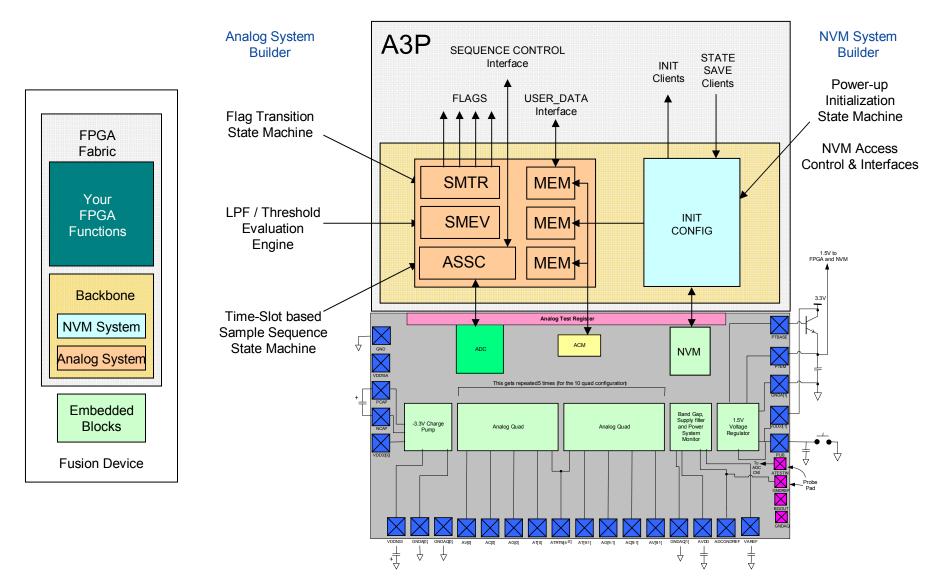

#### **Fusion Architecture**

Fusion starts with ProASIC3...

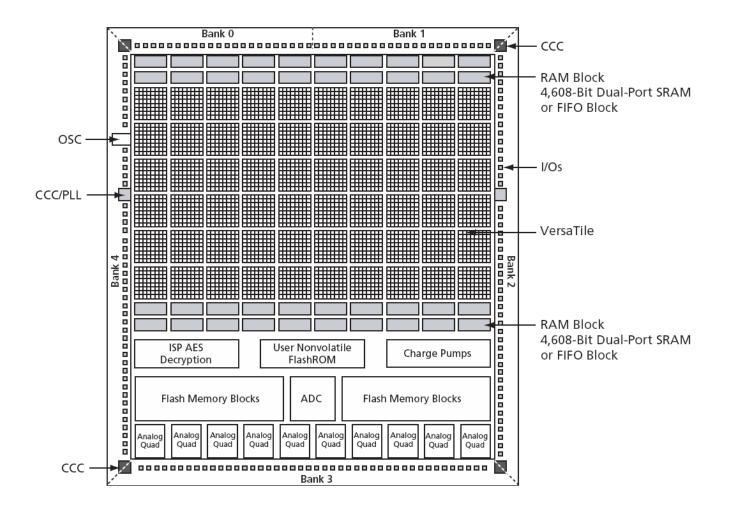

### **Fusion Architecture**

And adds Flash Memory Blocks and Analog Peripherals...

## **Fusion PSC: Target Applications**

- Power and Temperature Management

- Power sequencing with tracking control

- Smart battery charging

- Voltage, current, temperature monitors and alarms

- Fan and heat-element control and monitoring

- Intelligent Platform Management Interface (IPMI)

- Motor and Motion Control

- Motor control stepper, 3-phase and solenoid control

- Anti-lock brakes

- System initialization and configuration

- Context save and restore

- Context switching

- System boot codes

- Storage

- Program code storage

- EEPROM emulation

- Data acquisition and logging

- Low Power and Clocking

- Control for sleep mode and wake-up

- Live at power-up clock generation, conditioning, and distribution

## **Fusion Family**

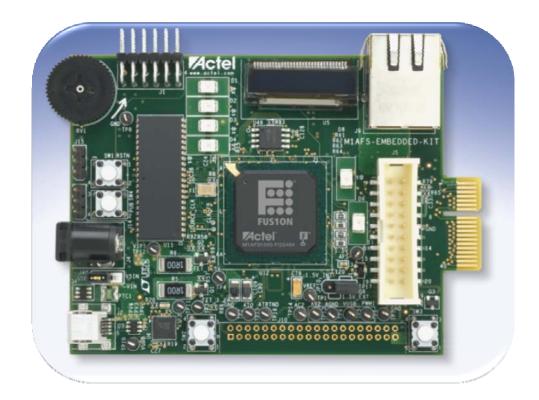

|                                           | Part #              | AFS090               | AFS250               | AFS600              | AFS1500             |

|-------------------------------------------|---------------------|----------------------|----------------------|---------------------|---------------------|

|                                           | ARM enabled         | -                    | -                    | M7AFS600            | -                   |

|                                           | Cortex M1 enabled   |                      |                      | M1AFS600            | M1AFS1500           |

|                                           | System Gates        | 90K                  | 250K                 | 600K                | 1,500K              |

| ส                                         | Tiles (D-FF)        | 2,304                | 6,144                | 13,824              | 38,400              |

| General                                   | Secure (AES) ISP    | Yes                  | Yes                  | Yes                 | Yes                 |

| ő                                         | PLLs                | 1                    | 1                    | 2                   | 2                   |

|                                           | Globals             | 18                   | 18                   | 18                  | 18                  |

|                                           | RAM blocks (512x9)  | 6                    | 8                    | 24                  | 60                  |

| >                                         | Total RAM           | 27 Kbits             | 36 Kbits             | 108 Kbits           | 270 Kbits           |

| Jor                                       | FlashROM bits       | 1Kbits               | 1Kbits               | 1Kbits              | 1Kbits              |

| Memory                                    | Flash Memory Blocks | 1                    | 1                    | 2                   | 4                   |

|                                           | Total Flash Memory  | 2 Mbits              | 2 Mbits              | 4 Mbits             | 8 Mbits             |

| bo                                        | Analog Quads        | 5                    | 6                    | 10                  | 10                  |

| Analog                                    | Analog Inputs       | 15                   | 18                   | 30                  | 30                  |

| Ā                                         | Output Gate Drivers | 5                    | 6                    | 10                  | 10                  |

|                                           | I/O Types           | Analog / LVDS / Std+ | Analog / LVDS / Std+ | Analog / LVDS / Pro | Analog / LVDS / Pro |

| <u>Q</u>                                  | I/O Banks (+ JTAG)  | 4                    | 4                    | 5                   | 5                   |

| ≦ _                                       | Max Digital I/O     | 75                   | 114                  | 172                 | 252                 |

|                                           | Analog I/O          | 20                   | 24                   | 40                  | 40                  |

| g ,                                       | QN108               | 37/9 (16)            |                      |                     |                     |

| le /<br>de                                | QN180               | 60/16 (20)           | 65/15 (24)           |                     |                     |

| Single /<br>ble ende<br>nalog)            | PQ208               |                      | 93/26 (24)           | 95/46 (40)          |                     |

| D: Single<br>uble enc<br>(analog)         | FG256               | 75/22 (20)           | 114/37 (24)          | 119/58 (40)         | 119/58 (40)         |

| I/O: Single /<br>Double ended<br>(analog) | FG484               |                      |                      | 172/86 (40)         | 228/86 (40)         |

|                                           | FG676               |                      |                      |                     | 252/126 (40)        |

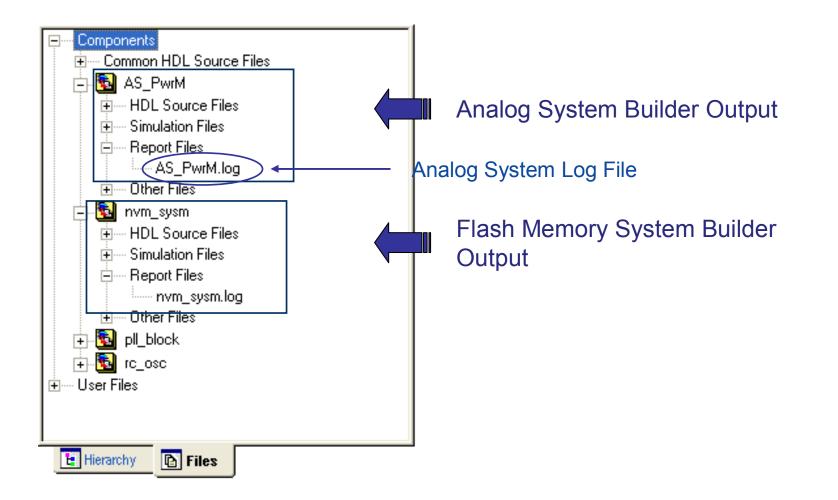

- Creates Complete Analog System Including

- AB Hard-Macro

- Analog System Soft-IPs (RTL)

- Analog System data storage RAMs

- Memory files for simulation

- Configuration file for import into NVM System

### Analog System Builder: Supported Peripherals

- Voltage Monitor

- Current Monitor

- Differential Voltage Monitor

- Temperature Monitor

- Direct Digital Input

- Output Gate Driver

- Internal Temperature Monitor

- Internal Voltage Monitor

- RTC (Real Time Counter)

| ADC Configuration                                                                           | MHz      | ADC Clock:          | Re <u>s</u> oluti | on: 10 | ▼ bits                   | 4                       | Advanced Options |

|---------------------------------------------------------------------------------------------|----------|---------------------|-------------------|--------|--------------------------|-------------------------|------------------|

| Available p <u>e</u> ripherals:                                                             | Peripher | als used in system: |                   |        |                          |                         | _0               |

| Voltage Monitor<br>Current Monitor<br>Temperature Monitor                                   |          | Peripheral          | Signal            | Туре   | Acquisition<br>time (us) | Sampling Rate<br>(ksps) | Package Pin      |

| Gate Driver<br>Real Time Counter<br>Internal Temperature Monito<br>Internal Voltage Monitor |          |                     |                   |        |                          |                         |                  |

|                                                                                             |          | y Sampling Seguence | -1                |        |                          |                         | Generate         |

| Modify Analog System Buil                                 | der - [analog_sys]           |                |                  |                          |                         |                   |

|-----------------------------------------------------------|------------------------------|----------------|------------------|--------------------------|-------------------------|-------------------|

| ADC Configuration                                         |                              |                | <b>↓</b>         |                          |                         |                   |

| System Clock: 40.000                                      | MHz ADC Clock:               | 10.000 MHz Re: | solution: 12     | ▼ bits                   |                         | Advanced Options. |

| For recommended clock scher                               | _                            |                | - , ,            |                          | _                       |                   |

| For recommended clock scher                               | me piease click <u>nere.</u> |                |                  |                          |                         |                   |

| Available p <u>e</u> ripherals:                           | Peripherals used in system:  |                |                  |                          |                         | =                 |

| Voltage Monitor<br>Current Monitor<br>Temperature Monitor | Peripheral                   | Signal         | Туре             | Acquisition<br>time (us) | Sampling Rate<br>(ksps) | Package Pin       |

| Differential Voltage Monitor                              | 1 Input Voltage              |                | Voltage          | 10.000                   | 32.154                  | Unassigned        |

| Direct Digital Input                                      | 2 Input Voltage              | V1P8           | Voltage          | 1.000                    |                         | Unassigned        |

| Gate Driver<br>Real Time Counter                          | 3 Temperature                | Temp           | Temperature      | 10.000                   |                         | Unassigned        |

| Internal Temperature Monito                               | 4 Gate Driver                | V2P5bad        | Gate Driver      |                          |                         | Unassigned        |

| Internal Voltage Monitor                                  | 5 Gate Driver                | V1P8bad        | Gate Driver      |                          |                         | Unassigned        |

| T                                                         | 6 Gate Driver                | over_temp      | Gate Driver      |                          |                         | Unassigned        |

|                                                           | -                            | channe         | ng rate fo<br>:I |                          | Assign                  | <br>pins for      |

|                                                           |                              |                |                  |                          | analoa                  | channels          |

| <b>.</b>                                                  | h Nafina                     | ADC complian   |                  |                          | analog                  | chumers           |

| Select periphero                                          | als Define /                 | ADC sampling   |                  |                          |                         |                   |

|                                                           | sequence                     |                |                  |                          |                         |                   |

|                                                           | · · ·                        |                |                  |                          |                         |                   |

|                                                           |                              |                |                  |                          |                         |                   |

|                                                           |                              |                |                  |                          |                         |                   |

|                                                           | ¥                            |                |                  |                          |                         |                   |

|                                                           | Mandalia Consultana Consulta | ce             |                  |                          |                         | <u>G</u> enerate  |

|                                                           | Modify Sampling Seguen       |                |                  |                          |                         |                   |

**POWER MATTERS**

To Configure a Voltage Monitor

| Configure Volt                        | tage Mo             | nitor Periphe | ral                |              |                                                      |                   |                     |         | × |

|---------------------------------------|---------------------|---------------|--------------------|--------------|------------------------------------------------------|-------------------|---------------------|---------|---|

| :                                     | AV pad Signal name: |               |                    | 1            | Prescaler                                            |                   |                     |         |   |

| Digital fil<br>Filtering<br>Initial v | g factor:           | None          | ▼<br>V<br>Comparis | on Flag Spec | Acguisition ti<br>M <u>a</u> ximum volt<br>ification | ····· )           | 10.000<br>12.000000 | us<br>V |   |

|                                       | Fla                 | g Name        | Flag               | д Туре       | Threshold<br>(V)                                     | Assert<br>Samples | De-asse<br>Sample   |         |   |

| 2<br>3<br>4                           |                     |               |                    |              |                                                      |                   |                     |         |   |

| Help                                  |                     |               |                    |              | [                                                    | ОК                |                     | ancel   |   |

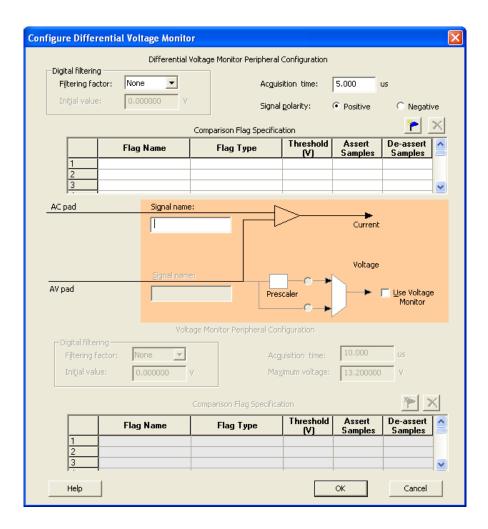

#### To Configure Differential Voltage Monitor

| ngure Differentia                      | al Voltage Monitor |                               |                        |                   |                        |

|----------------------------------------|--------------------|-------------------------------|------------------------|-------------------|------------------------|

|                                        | Differential Vo    | oltage Monitor Peripheral     | Configuration          |                   |                        |

| Digital filtering<br>Filtering factor: | None               | Acgui                         | sition time:           | 5.000             | JS                     |

| Ini <u>t</u> ial value:                | 0.000000 V         | Signal                        | polarity:              | Positive          | C Negative             |

|                                        |                    | Comparison Flag Specifica     | ation                  |                   | <b>*</b> ×             |

|                                        | Flag Name          | Flag Type                     | Threshold<br>(V)       | Assert<br>Samples | De-assert              |

| 1 2                                    |                    |                               |                        | Jampies           |                        |

| 3                                      |                    |                               |                        |                   | <u> </u>               |

| AC pad                                 | Signal name:       | r                             | _                      | _                 |                        |

|                                        |                    |                               | <u> </u>               | Current           |                        |

| AV pad                                 | Signal name:       |                               | scaler                 | Voltage           | Use Voltage<br>Monitor |

| – Digital filtering —                  | Volta              | ge Monitor Peripheral Cor     | figuration             |                   |                        |

| Filtering factor:                      | None               | Acc                           | juisition time:        | 10.000            | us                     |

| Ini <u>t</u> ial value;                | 0.000000 V         | Maj                           | <u>k</u> imum voltage: | 13.200000         | A                      |

|                                        | c                  | <br>Comparison Flag Specifica | ition                  |                   | * ×                    |

|                                        | Flag Name          | Flag Type                     | Threshold<br>(V)       | Assert<br>Samples | De-assert A            |

| 1 2 3                                  |                    |                               |                        |                   |                        |

|                                        |                    |                               |                        |                   |                        |

| 3                                      |                    |                               |                        |                   | <b></b>                |

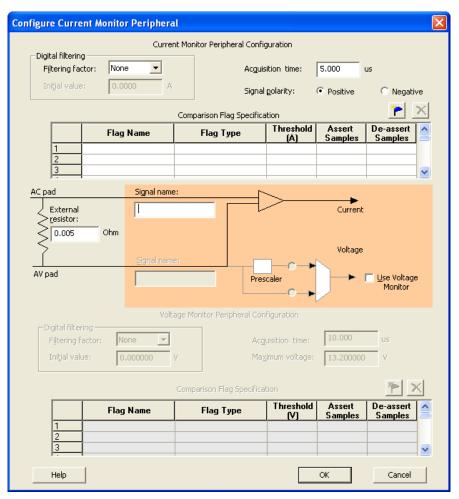

#### To Configure Current Monitor

| Configure Current A                                                  | Aonitor Periphera | d                            |                                  |                    | ×           |

|----------------------------------------------------------------------|-------------------|------------------------------|----------------------------------|--------------------|-------------|

|                                                                      | Curre             | nt Monitor Peripheral Config | guration                         |                    |             |

| Digital filtering<br>Filtering factor:<br>Initial value:             | None 💌            |                              | sition time:<br>polarity:        | • Positive         | us          |

| L                                                                    |                   | Comparison Flag Specifica    | ation                            |                    | <u>*</u> ×  |

|                                                                      | Flag Name         | Flag Type                    | Threshold<br>(A)                 | Assert<br>Samples  | De-assert A |

| 1<br>2<br>3                                                          |                   |                              |                                  |                    |             |

| AC pad                                                               | Signal name       | ;<br>;; [~                   | _                                |                    |             |

| External<br>resistor:<br>0.005<br>AV pad                             | Ohm Signal nam    |                              | - C - +                          | Current<br>Voltage | Use Voltage |

|                                                                      | Volt              | age Monitor Peripheral Con   | •                                |                    | Monitor     |

| – Digital filtering –<br>Filtering factor<br>Ini <u>t</u> ial value: |                   |                              | uisition time:<br>gimum voltage: | 10.000             | us<br>V     |

|                                                                      |                   | Comparison Flag Specifica    | tion                             |                    | <b>⊁</b> ×  |

| 1<br>2<br>3                                                          | Flag Name         | Flag Type                    | Threshold<br>(V)                 | Assert<br>Samples  | De-assert A |

| Help                                                                 |                   |                              |                                  | ок                 | Cancel      |

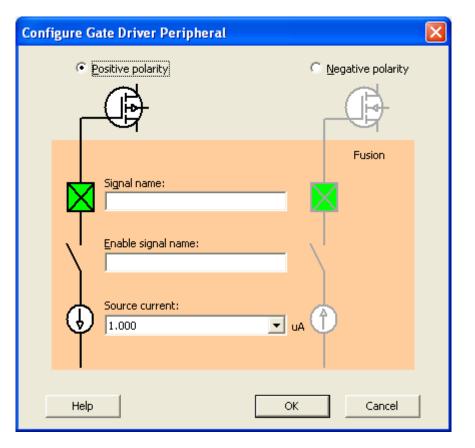

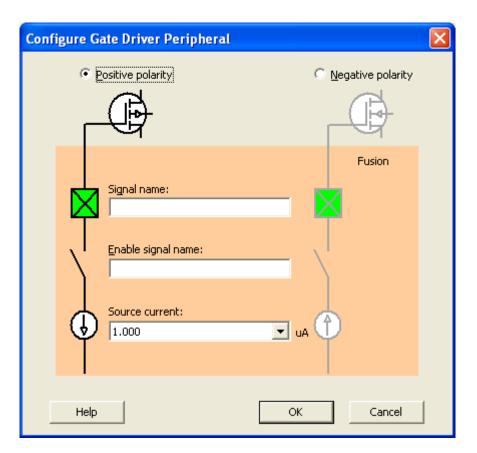

To Configure Gate Driver Outputs

Displaying Flags for Different Voltage Thresholds

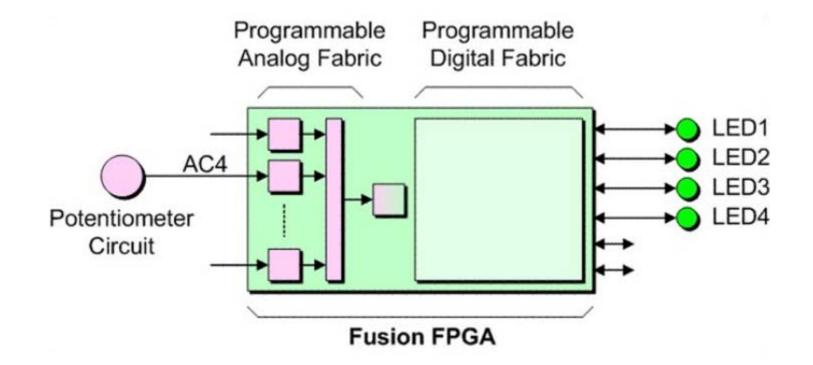

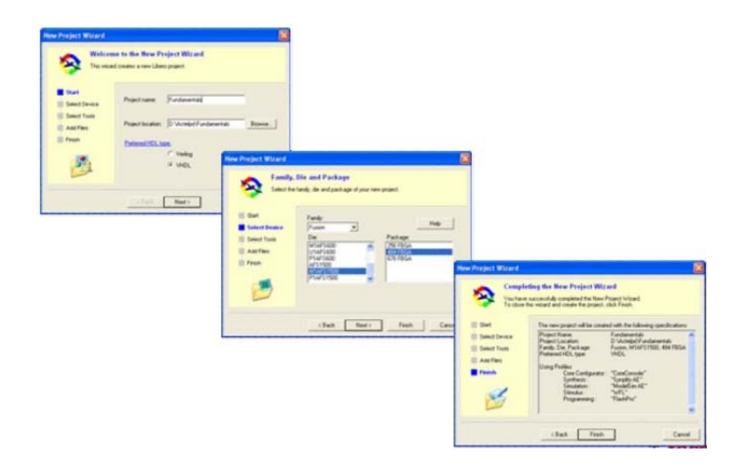

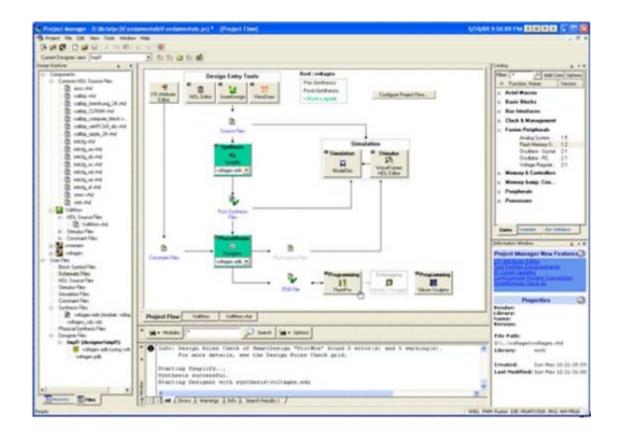

Creating a Libero Project

Use SmartDesign to Connect Various Analog & Digital Blocks on a Virtual Canvas

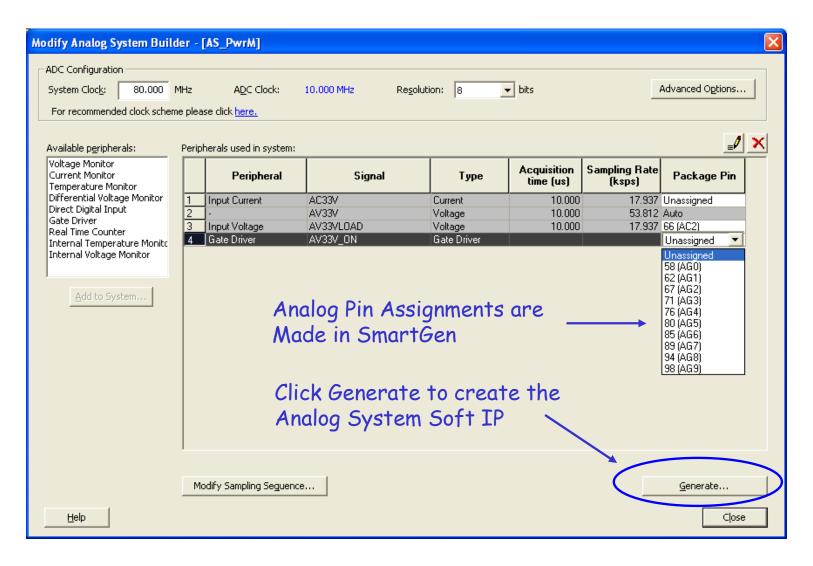

Within SmartDesign, use the Analog System Builder to Create the Voltage Monitor – Max from Potentiometer=3.3V

| tage Hordus<br>met Hordus Palat                                              | aland Signal     | 1,000    | Sampletion Sample                 |                       | 12         |                                |              |                    |

|------------------------------------------------------------------------------|------------------|----------|-----------------------------------|-----------------------|------------|--------------------------------|--------------|--------------------|

| ngan aliure Manifur<br>Weeksal Yakaga Manifur<br>eci Dagha Dapad<br>In Dhina |                  | 1        |                                   |                       |            |                                |              |                    |

| e Trea Capitar<br>et Trea Capitar<br>Ind Tange stude Nords                   |                  |          |                                   |                       |            |                                |              |                    |

|                                                                              |                  |          |                                   |                       |            |                                |              |                    |

| and the second                                                               |                  | Configur | re Vellage Mon                    | iter Periol           | recal      |                                |              |                    |

|                                                                              |                  |          |                                   |                       |            |                                |              |                    |

|                                                                              |                  |          | - poly                            | Signal name:<br>Volt3 |            |                                | -            | 2                  |

|                                                                              |                  |          |                                   | 1.000                 |            | Prescaler                      |              |                    |

|                                                                              |                  |          |                                   |                       |            |                                |              |                    |

|                                                                              |                  |          | Ngtal filtering                   |                       |            |                                |              |                    |

| and classes                                                                  | Constraint of    |          | rikeng faitari                    | None                  | •          | Acquisition to                 | - 1          | 0.000 uii          |

|                                                                              | a traperta de la |          |                                   | None                  |            | Acquisition to<br>Maximum volt | - 1 <u>1</u> | 0.000 uii<br>1.3 V |

|                                                                              | a (anaise)       |          | FilterngFactors                   |                       | - <u>*</u> | Hannun vol                     | - 1 <u>1</u> | v v                |

|                                                                              |                  |          | Pitering Factors<br>(Piter value) |                       |            | Hannun vol                     | - 1 <u>1</u> |                    |

Assigning to a Voltage Channel (ex. AC4)

| alog System Duilder: Cr                                                                                                                     | eate core*                 |        |          |                          |                         | SUR                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Þ  |

|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|--------|----------|--------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| ADC Configuration<br>System Cluck:                                                                                                          | MHE ADC Clock:             | Resck  | tors [10 | • bits                   | 19                      | Advanced Options                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | .] |

| Available peripherals:                                                                                                                      | Pergherals used in system: |        |          |                          |                         | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2  |

| Vokage Monitor<br>Current Honitor<br>Temperature Monitor                                                                                    | Peripheral                 | Signal | Type     | Acquisition<br>time (us) | Sampling Rate<br>(Raps) | Package Pin                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Γ  |

| Differential Voltage Hunder<br>Dent Digital Ispat<br>Gate Drive<br>Red Tane Counter<br>Deternal Toporature Hondu<br>Deternal Voltage Hondur | 1 Provid Violitage V       | at .   | Voltage  | 10.000                   |                         | Charangewell  All14 (Al17) All14 (Al17) All15 (Al17) All15 (Al17) All17 (Al19) T12 (Al19 |    |

|                                                                                                                                             | Hodify Sanpling Sequence   | L      |          |                          |                         | Generate                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

| Help                                                                                                                                        |                            |        |          |                          |                         | Obse                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | -  |

#### Synthesis -> P&R -> Programming

### **Fusion Peripherals**

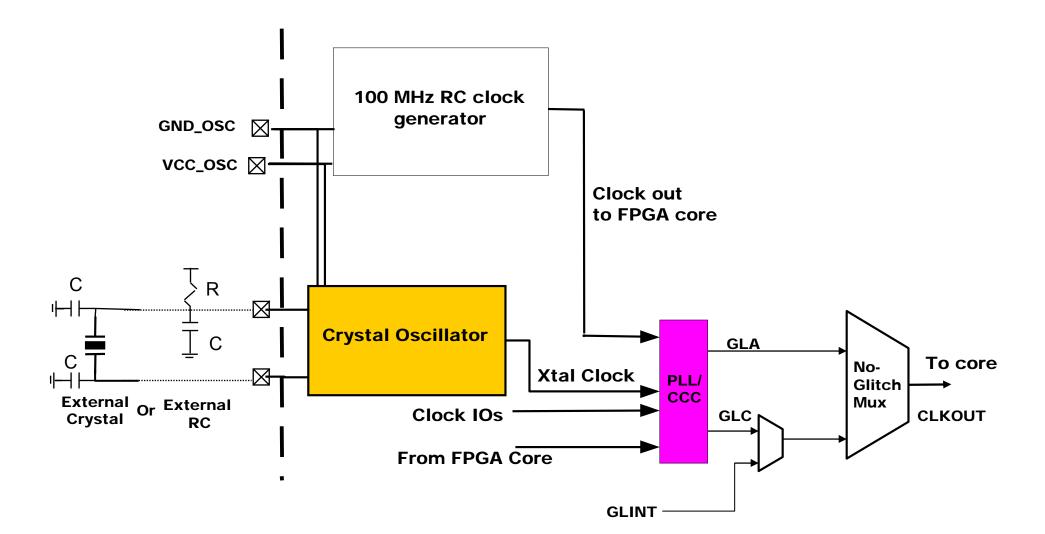

- Clocking

- RC and Crystal Oscillators

- Clock Conditioning Circuitry

- No-Glitch MUX

- Embedded Memory

- Analog Block

### **Fusion Clock Resources**

- Fusion Provides Multiple Clocking Resources:

- On chip clock sources:

- RC oscillator @ 100MHz

- Crystal Oscillator Circuit

- Six CCC Blocks / PLLs (1 or 2)

- No-Glitch MUX

- Real Time Counter (RTC)

- Use Models

- Internal 100MHz RC oscillator

- Crystal OSC circuit

- 32 KHz 20 MHz

- CCC/PLLs can multiply, divide, and phase shift clock signals for user applications

- Sources include: crystal Osc, RC Osc, or external clock

- RTC enables low power sleep mode

### Fusion Clock Resources System Block Diagram

### **RC & Crystal Oscillators**

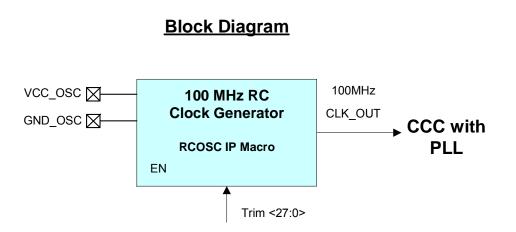

### Fusion RC Oscillator Features

- Summary

- Clock frequency: 100 MHz

- +/-1%: 0 to 70 C

- Duty cycle 40% 60%

- Requires no external components

- Can be used to drive either a PLL or Output Pad

- Provides an integrated, accurate on-chip clock source

- Additional Features

- Factory trim capability for high precision

Note\*: Crystal oscillator and RC oscillator physically share the same VCC and GND power pads.

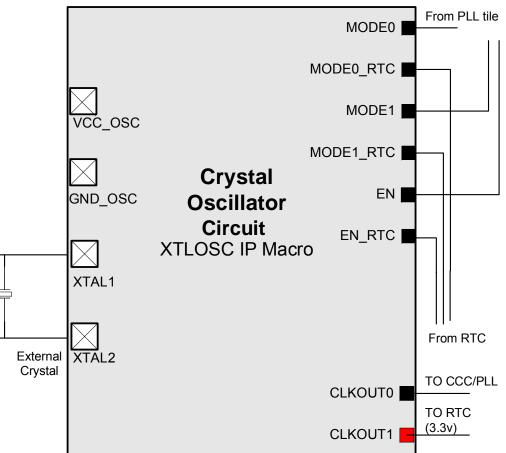

# Fusion Crystal Oscillator

#### Features

- High-precision Clock Source

Up to 100ppm (0.01%) precision

Supports Both On-chip and Off-chip Resources

Source for PLL/CCC

- Modes

- External Crystal:

- High gain: 2 20 MHz

- Med gain: 0.2 2 MHz

- Low gain: 32 200 KHz

- RC Network: 32kHz 4MHz

- Specifications

- Maximum output jitter 50pS RMS

- 10 MHz crystal (0.05%)

- Duty cycle: 40% 60%

Note: Crystal oscillator and RC oscillator physically shared the same VCC and GND power pads.

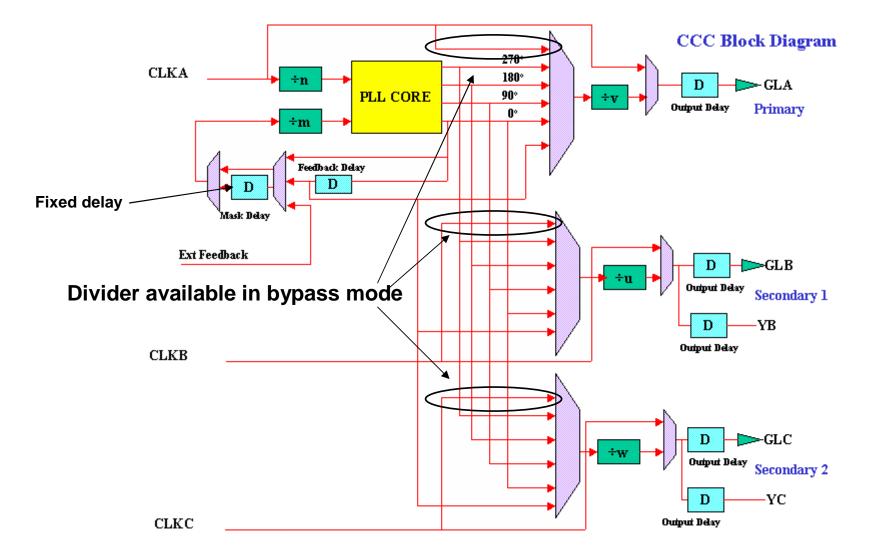

#### **Fusion**

#### Clock Conditioning Circuitry (CCC)

- All Devices Have 6 Clock Conditioning Circuitry (CCC) Blocks, BUT ...

- ... Some CCC Blocks do not contain PLLs

- AFS090 / AFS250 1 PLL

- AFS 600 / AFS1500 2 PLLs

- ... Non-PLL Functionality Still Available

- Divider and Delay Elements

- Global Access from I/O or Internal Signal

- 3 Global MUX Blocks

- Steer Signals from Global Pads and FPGA Fabric into Global Networks

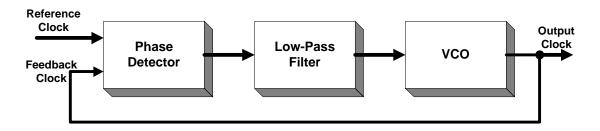

## **Fusion PLL**

- Functions

- Clock Phase Adjustment

- Clock Delay Minimization

- Clock Frequency Synthesis

- Allows Access From Global Pads To Global Network and PLL

- Allows Access From PLL To FPGA Core

- Input Sources:

- Single Ended I/O, Differential I/O, FPGA Core, RC Osc, XTAL Osc

### Fusion PLL *Features*

- Delay Blocks (6 Programmable and 1 Fixed)

- Programmable Delay/Advance up to 5.56 ns in 160 ps increments for Clock Skew Minimization

- 5 Frequency Divider Blocks

- Provide Frequency Multiplication/Division

- Clock Phase Adjustment

- 0°, 90°, 180°, and 270°

- Dynamic Shift Register

- Provides Dynamic Reconfiguration Capability

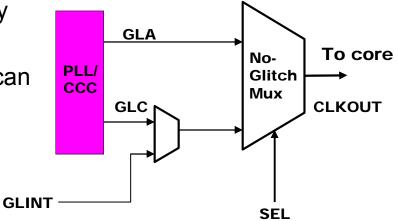

### No-Glitch MUX (NGMUX)

### Fusion No-Glitch MUX (NGMUX)

- Provides Special Switching Sequence

Between Two Asynchronous Clock Domains

- User-configurable to select between 2 of 3 possible clock sources – GLA, GLC, or other internal signal

- Time-out circuitry included in case one of the clocks stops or runs at very low frequency

- Advantage

- Eliminates narrow pulses/glitches which can cause clocking errors

- Especially critical in hi-rel apps

- Uses

- Clock domain control

- Power reduction by transitioning to lower frequency

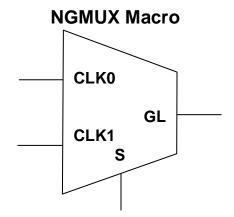

### Fusion No-Glitch MUX Usage

- NGMUX is Implemented as a 2:1 Mux in the Software

- Instantiate NGMUX in VHDL or Verilog Description

| Signal Name | Direction | Function     |

|-------------|-----------|--------------|

| CLK0        | Input     | Clock Input  |

| CLK1        | Input     | Clock Input  |

|             |           | Mux Select   |

| S           | Input     | 0 -> 1 CLK1  |

|             |           | 1 -> 0 CLK0  |

| CLKOUT      | Output    | Clock Output |

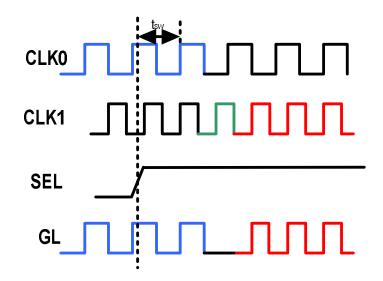

#### Fusion No-Glitch MUX Operation

- Switching from CLK0 to CLK1:

- GL will drive one last complete CLK0 positive pulse (i.e. one rising edge followed by one falling edge).

- From that point GL stays low until the second rising edge of CLK1 occurs.

- At the second CLK1 rising edge, GL will continuously deliver CLK1 signals.

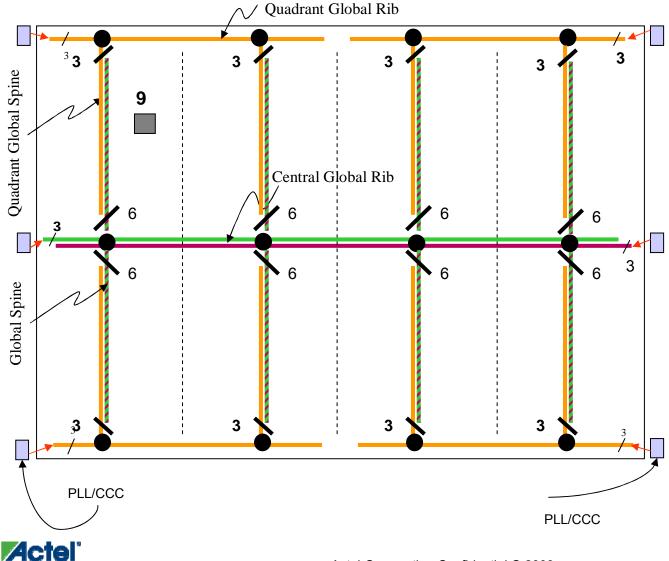

### **Fusion: Global Distribution Network**

- Left and Right CCCs Provide 6 Chip-wide **Global Networks** (Access from I/Os in Middle of Left and Right Sides)

- 12 Quadrant Global Networks (3 per Quadrant – Access from I/Os in 4 Corners)

- Each VersaTile Has Access to 9 Global Resources

- Access from PLLs and Internal Signals

### **Fusion Peripherals**

- Clocking

- Embedded Memory

- Flash Memory Block

- FlashROM

- SRAM and FIFO

- Analog Block

### Fusion Only FPGA with Flash Memory

### **Fusion Flash Features**

- Flash Memory 2 Mb Density

- 1 4 blocks/device

- Each 2 Mb array has independent controller

- Independent JTAG access

- Flexible Operation

- x8, x16, and/or x32 FPGA

- Each supports multiple partitions

- Small page size (1kb)

- Can be accessed by either on-chip or off chip resources

- High Performance

- 60 ns random access

- Pipelined 10 ns access of sequential memory addresses

### Fusion Flash Features (cont.)

- Flash Memory Level:

- FPGA access

- Password security

- JTAG access for programming

- Page Level:

- JTAG read / write protection

- Program/erase

- Partition on page boundaries

- Block Level Error Detect:

- Single error correct

- Double error detect

## **Fusion Peripherals**

- Clocking

- Embedded Memory

- Flash Memory Block

- FlashROM

- SRAM and FIFO

- Analog Block

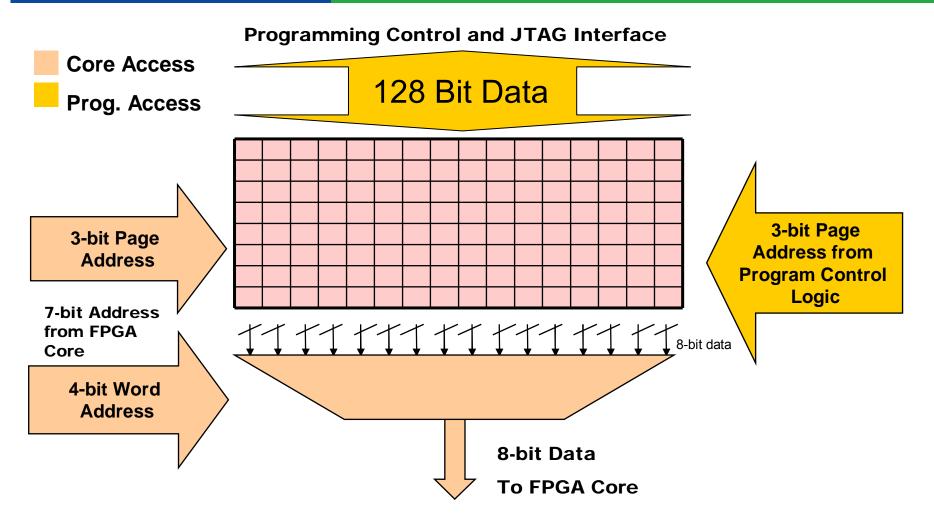

### FlashROM (FROM) Memory

- 8 pages of 128 bits (8x128)

- Same as ProASIC3\E FROM

- FPGA Core and FlashROM Memory Can Be Programmed Separately

- Allows Changing FROM without Erasing Core

- Core Powered Down during FROM Programming

- Example Applications

- IP Addressing

- User/System Preference Storage

- Device Serialization

- Inventory Control

- Subscription Models (Set-top Boxes)

- Secure Key Storage

- Presets

- Date Stamping

- Version Management

#### FlashROM Logical View

Every 128-bit Page Can Be Reprogrammed Independently

## **Fusion Peripherals**

- Clocking

- Embedded Memory

- Flash Memory Block

- FlashROM

- SRAM and FIFO

- Analog Block

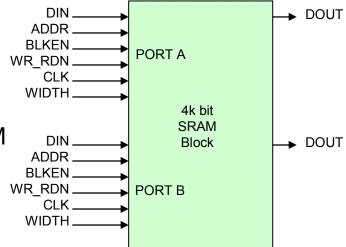

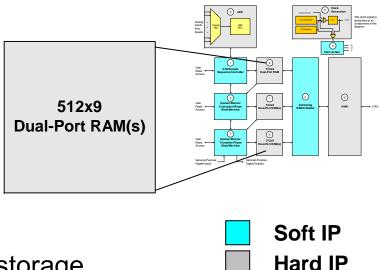

#### **Dual-Port SRAM Blocks**

- Multiple 4K bit Embedded Memory Blocks:

- 2 Write/Read ports OR independent 2-port

- Synchronous operation up to 250 MHz

- Fully programmable

- Scalable aspect ratio from 256x18 to 4Kx1

- Cascadable wide and deep

- SmartGen tool automates memory generation

- FIFO Capability

- Decoder, FIFO control and flag logic built into RAM block

- Programmable FIFO depth and flag threshold

## **Fusion SRAM Implementation**

#### True Dual-port RAM:

- Variable Aspect Ratios 4096x1, 2048x2, 1024x4 or 512x9

- Independent Read and Write Port Widths

- Dual-port Options Both Read, Both Write, One Read & One Write; Same Clock Frequency or Two Different Clock Frequencies

- Pass-through of Write Data or Hold Old Data on Output

- Two-port RAM:

- Variable Aspect Ratios 512x9 or 256x18

- Independent Read and Write Widths

- Dedicated Read and Write Ports

- Both Macros Have

- Synchronous Write

- Synchronous Read Pipelined or Non-Pipelined

- Asynchronous Output Reset

#### Fusion RAM *FIFO*

Fusion Has One FIFO Macro:

- Variable Aspect Ratios 4096x1, 2048x2, 1024x4, 512x9, or 256X18

- Independent Read and Write Port Widths

- Four FIFO Flags Empty, Full, Almost-empty, Almost-full

- FIFO Empty/Full Flags Synchronized to Read Clock and Write Clock, Respectively

- Programmable Threshold Values of 'Almost' Flags

- Asynchronous Reset

- Active-low Block Enable

- Active-low Write Enable and Active-high Read Enable

- FSTOP and ESTOP FIFO Counters Can Count after FIFO Is Full or Empty

- Allows Writing to FIFO Once and Repeatedly Reading Same Contents without Rewriting Contents

### **Fusion Peripherals**

- Clocking

- Embedded Memory

- Flash Memory Block

- FlashROM

- SRAM and FIFO

- Analog Block

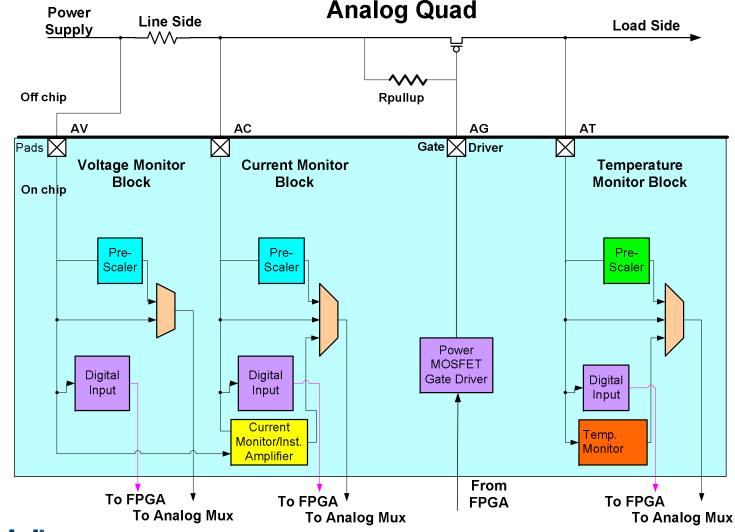

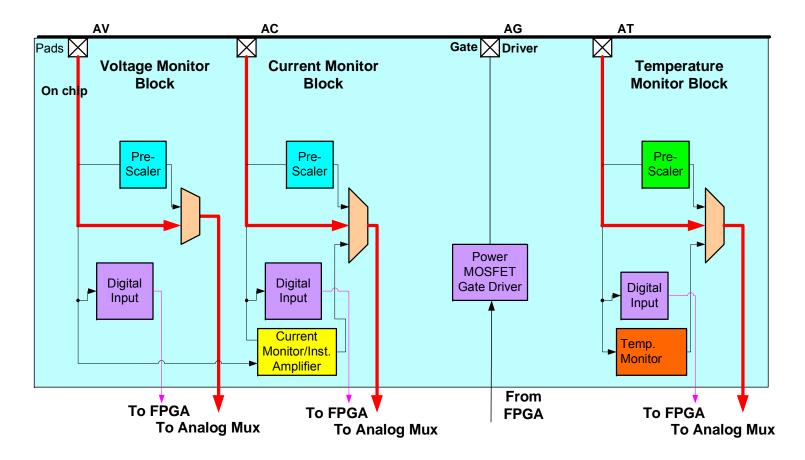

## Fusion Analog Block

- 1.5V Voltage regulator

- -3.3V Voltage converter (for internal use only)

- Bandgap voltage reference

- Power System Monitor (Generates Flash and ADC Reference)

- Real Time Counter System (RTC)

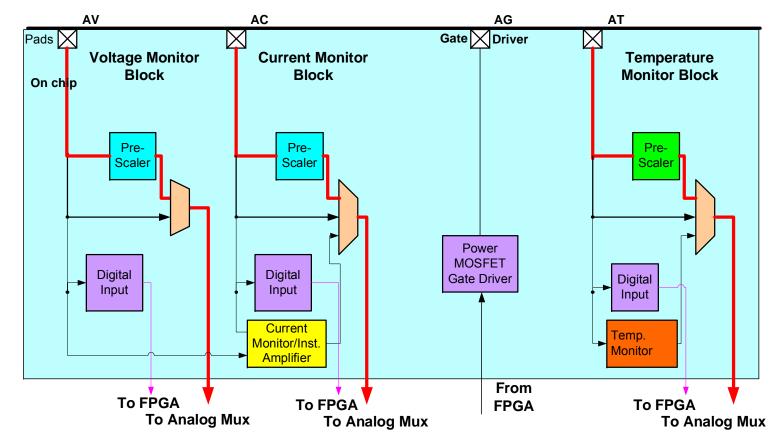

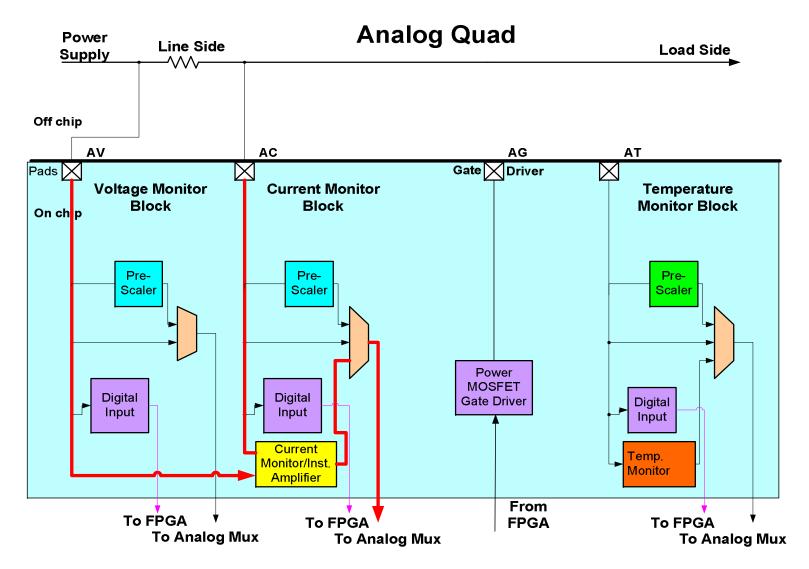

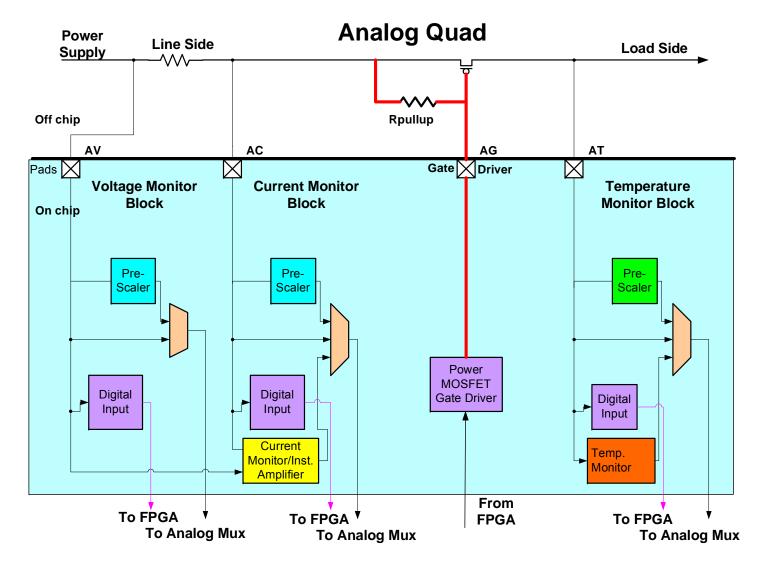

- Analog Quad (up to 10 Analog Quads)

- Voltage monitor block

- Current Monitor block

- Temperature monitor block

- Gate control/driver block

- Analog MUX

- ADC

- Selectable 8/10/12 bit resolution

- 32 input channels

- Up to 600K samples per second

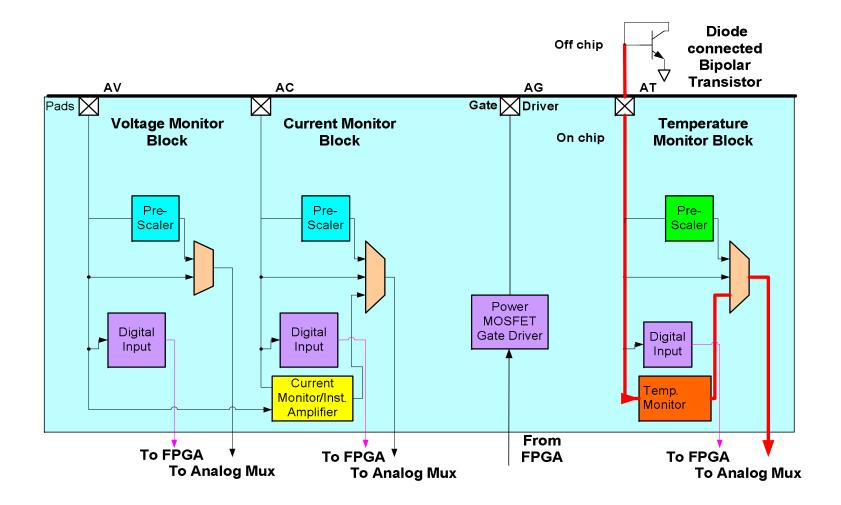

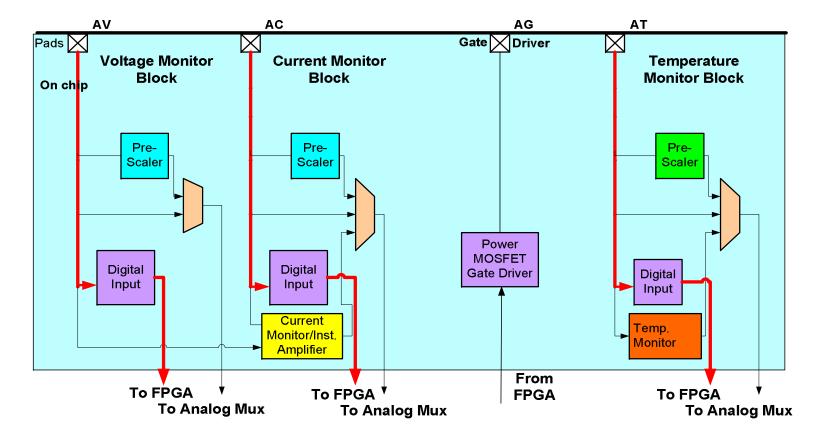

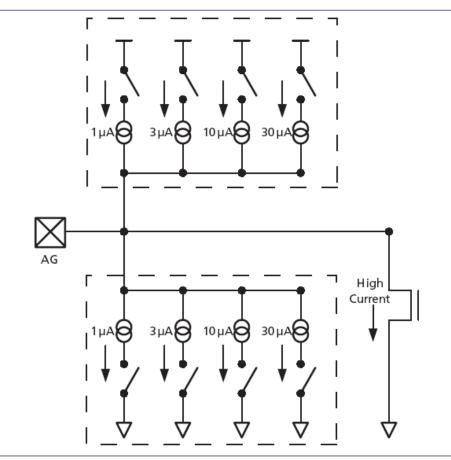

## Analog Quad (AQ)

Analog Quad is the Basic Analog I/O Structure *Power* Line Side

#### **Fusion Analog Quad**

- Features

- Includes 4 analog interface pins

- AV pin Input: direct and prescaler voltage monitor

- AC pin Input: direct and prescaler voltage monitor, current monitor

- AT pin Input: direct and prescaler voltage monitor, temp monitor

- AG pin Output Power FET gate control or high voltage, high drive output

- Input voltage range for AV and AC pads: 10.5V to 0 V or 0V to 12V +/- 10%

- Input voltage range for AT pad: 0V to 16V +/- 10%

- AV, AC, AT pads can be used as low speed digital inputs (Tr, Tf > 20nS)

- Modular building block used on all Fusion family members

- AFS090: 5 Quads

- AFS250: 6 Quads

- AFS600, AFS1500: 10 Quads

## Analog Quad: Direct Input

#### **Analog Quad**

Direct Input used when Maximum Input Voltage is between 2V and  $V_{REF}$

#### Analog Quad: Direct Input

- AV, AC, and AT pads can be Routed Directly to the Analog Mux by Configuring the Analog Quad

- Features

- Best accuracy, lowest offset

- No Buffers or Amplifiers between Input pin and ADC

- No DC input current; capacitive load only (~20pF)

- Resistive connection to ADC: ~4k ohm

- One Input range: 0V to ADC reference level

- Full scale level for internal reference is 2.56V

- Decimal value of 8 most significant bits is input level in 'centiVolts' (i.e., ADC count of 207 = 2.07V at input)

- Equivalent function to micro-controller style ADC

- Limitations

- Positive input only

- Single range

- Needs low impedance input source for full bandwidth

- Input capacitance varies greatly as input selection MUX is changed and Sample/Hold cycles

#### Analog Quad: Pre-scaler Input

#### **Analog Quad**

Pre-scaler Input used when Input Voltage is not between 2V and  $V_{REF}$

#### Analog Quad: Pre-scaler Input

- Features

- Input voltage ranges for AV and AC pads

- Pre-Scaler input from -10.5V to 0V or 0V to 12V

- Full scale ranges for ADC: ±16V, ±8V, ± 4V, ± 2V, ± 1V, ± 0.5V, ± 0.25V and ±0.125V

- Input voltage ranges for AT pads

- Pre-Scaler input from 0V to 16V

- Full scale ranges for ADC: +16V and +4V

- All ranges indicate input level in mV with a simple left or right shift of the binary value

- On 4V range with 12 bit ADC setting, LSB = 1mV at input pin

- Constant input impedance; ~1M ohm, 5pF

- Limitations

- Pre-scale circuits add offset and gain error

- Dynamic range changes are discouraged (will cause transient measurement errors on all channels)

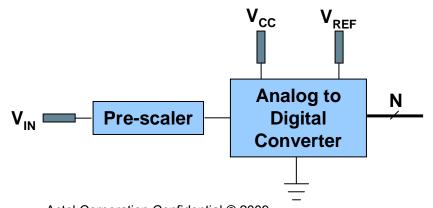

# **Pre-Scaling**

- Overdriving the ADC Input Can Result in:

- Erroneous Conversions

- Input Latch Up

- Permanent Damage To Device Is Possible

- To Avoid Overdriving, The Input Can Be Pre-scaled To Ensure Maximum Voltage To ADC Does Not Exceed VREF

- "Scale Down" Voltages That Are Greater Than VREF

- "Scale Up" Voltages That Are Less Than VREF

- Invert If Input Voltage Is Negative

## Pre-Scaling (Cont.)

- Pre-scaler Value (Gain) is Chosen to Ensure (Max V<sub>IN</sub> \* G) ≤ V<sub>REF</sub>

- Gain May Be Chosen Such That the LSB of the Converter Output is a Convenient Number

- Example:

- For V<sub>REF</sub> = 2.56V and V<sub>IN</sub> = 6V, G = 0.4267 Ensures Input to ADC  $\leq$  V<sub>REF</sub> But . . .

- LSB of ADC equals the following:

- 8 bit: 23.44 mV

- 10 bit: 5.86 mV

- 12 bit: 1.47 mV

- Using A Different Gain Value Can Result In Simpler Calculations

- Limitations

- Pre-scale Circuits Add Offset and Gain Error

## Analog Quad: Pre-scaling Factors

|                                  |                    | Full Scale Voltage | LSB 8-bit conversion | LSB 10-bit conversion | LSB 12-bit conversion |            |

|----------------------------------|--------------------|--------------------|----------------------|-----------------------|-----------------------|------------|

| V <sub>IN</sub>                  | Scaling Factor (G) | (VREF / G)         | (mV)                 | (mV)                  | (mV)                  | Range Name |

| $12V \ge V_{IN} > 8V$            | 0.15625            | 16.368 V           | 64                   | 16                    | 4                     | 16V        |

| $8V \ge V_{IN} > 4V$             | 0.3125             | 8.184 V            | 32                   | 8                     | 2                     | 8V         |

| $4V \ge V_{IN} > 2V$             | 0.625              | 4.092 V            | 16                   | 4                     | 1                     | 4V         |

| $2V \ge V_{IN} > 1V$             | 1.25               | 2.046 V            | 8                    | 2                     | 0.5                   | 2V         |

| 1V ≥ V <sub>IN</sub> > 0.5V      | 2.5                | 1.023 V            | 4                    | 1                     | 0.25                  | 1V         |

| 0.5V ≥ V <sub>IN</sub> > 0.25V   | 5.0                | 0.5115 V           | 2                    | 0.5                   | 0.125                 | 0.5V       |

| 0.25V ≥ V <sub>IN</sub> > 0.125V | 10.0               | 0.25575 V          | 1                    | 0.25                  | 0.0625                | 0.25V      |

| V <sub>IN</sub> ≤ 0.125V         | 20.0               | 0.127875 V         | 0.5                  | 0.125                 | 0.03125               | 0.125V     |

- Fusion Scaling Factors Give Convenient LSB Values For All ADC Resolutions

- All Ranges Indicate Input Level in mV with Simple Left or Right Shift of Binary Value

- Maximum Allowable Input Voltage:

- -10.5V or +12V for AV and AC pads

- +16V for AT pad

- Pre-scaling Offset and Gain Error

- Gain error

- Positive DC inputs: 1% typ

- Negative DC inputs: 2% typ

- Offset error

- 2 ± 0.2% of range

#### Analog Quad: Pre-scaler Input Examples

- Example 1

- 8V Is Applied to AV Pad

- Scaling Factor Is Set to 0.3125

- Output of Pre-scaler (Input to ADC) is (8 \* 0.3125) = 2.5V

- For 12-bit Resolution, ADC output = 2<sup>12</sup> \* (2.5 / 2.56) = 4000

- LSB = (2.56 / 0.3125) / 2<sup>12</sup> = 2 mV

- Example 2

- 12V Is Applied to AV Pad

- Scaling Factor Is Set to 0.15626

- Output of Pre-scaler (Input to ADC) is (12 \* 0.15625) = 1.875V

- For 12-bit Resolution, ADC output  $= 2^{12} * (1.875 / 2.56) = 3000$

- LSB = (2.56 / 0.15626) / 2<sup>12</sup> = 4 mV

- Example 3

- –0.2V Is Applied to AV Pad

- Scaling Factor Is Set to 10

- Output of Pre-scaler (Input to ADC) is (0.2 \* 10) = 2.0V

- Input signal is inverted to make ADC input positive

- For 12-bit Resolution, ADC output =  $2^{12} * (2.0 / 2.56) = 3200$

- LSB = (2.56 / 10) / 2<sup>12</sup> = 0.0625 mV

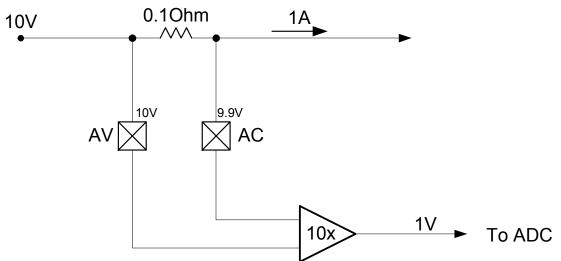

## Analog Quad: Current Monitor

#### Analog Quad: Current Monitor

Can sense Current by Measuring Voltage Drop Across an External Resistor

- If the Polarity bit is set to '0' (positive):

- Current monitor output will be = 10 \* (AV-AC)

- If the Polarity bit is set to '1' (negative):

- Current monitor output will be = 10 \* (mag(AV)-mag(AC))

- Note: ADC input should be positive only

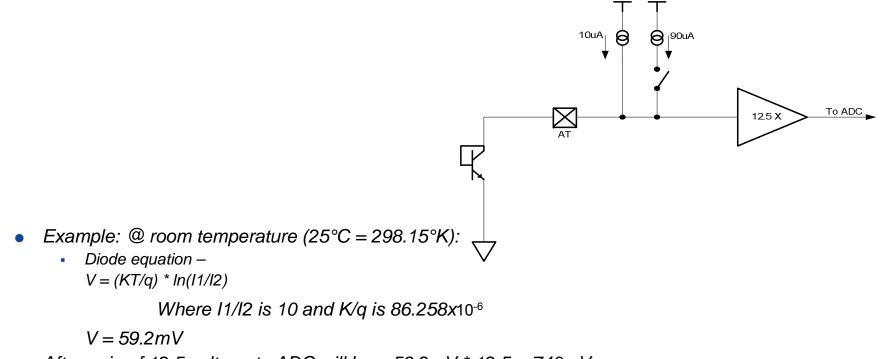

#### Analog Quad: Temperature Monitor

#### Analog Quad: Temperature Monitor

- Can Monitor Temperature of External Transistor Connected as Diode

- Basic accuracy of 5 degrees C

- Output count of ADC reads directly as absolute temperature (K)

• After gain of 12.5 voltage to ADC will be = 59.2mV \* 12.5 = 740mV

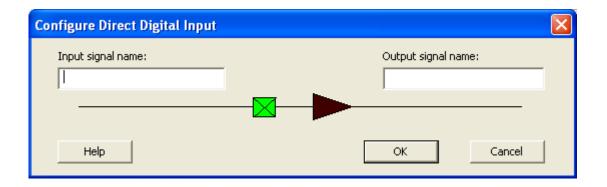

## Analog Quad: Direct Digital Input

#### **Analog Quad**

#### Analog Quad: Direct Digital Input

- AV, AC, and AT pads can be used as low speed Digital Inputs (LVTTL)

- Operating speed 10MHz (Max)

- (Tr, Tf > 20nS)

- Delay 10nS (Typ)

- The Digital Buffers can be Disabled if not used

#### Analog Quad: Gate Driver

#### Analog Quad: Gate Driver

#### Features

- Controls turn on of external Power FET by pulling the gate towards ground

- FET Vgs limited to Ig \* Rpullup

- Slew rate of load controlled by Ig/Cgd = dV/dt

- Works for positive supplies (with P-FET) and negative supplies (with N-FET)

- High drive mode can sink/source 25mA

- Limitations

- Requires external pullup resistor

- Open drain style output. Does not output a voltage level

#### Analog Quad: Gate Driver

- Gate Driver has two Modes:

- High current drive 25mA @ 1V

- Low current drive choose between 1, 3, 10 and 30uA

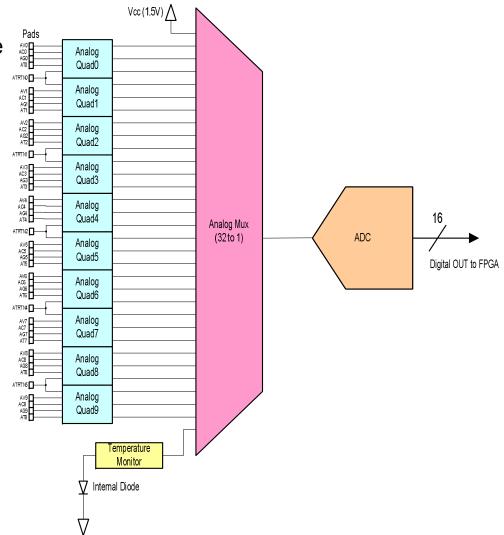

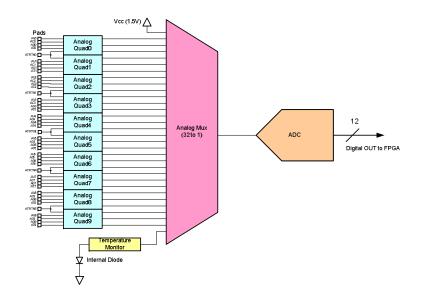

## Fusion Analog MUX

- Input to the Fusion ADC is a 32:1 Analog MUX

- 30 Input Channels are User Definable

- Connected to Analog Quad AV. AC and AT inputs

- Two Channels are Hardwired Internally

- Channel 0 is wired to the FPGA's 1.5 V supply

- Fusion device can monitor its own power supply

- Channel 31 connects to an internal temperature diode

- Monitor temperature of the Fusion device

- Analog Block Input CHNUMBER [4:0]

Selects Channel for Conversion

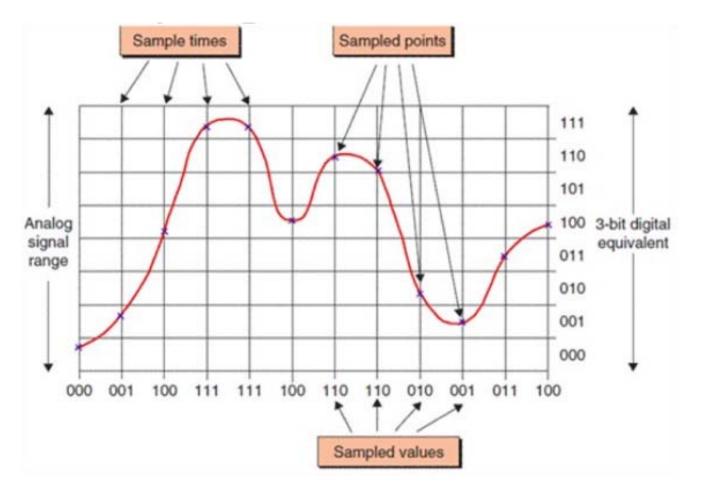

# Fusion ADC

- 8/10/12 bit Selectable Resolution

- 32 Input Channels

- Up to 600K samples/sec

- TUE (Total Unadjusted Error)

- +/- 2 LSB in 8 bit mode

- +/- 4 LSB in 10 bit mode

- +/- 6 LSB in 12 bit mode

- Clock

- ADC interface clock max frequency 100MHz

- Selectable clock divider (divide by 4 to 1024) to generate ADC internal clock

- ADC internal clock frequency range 1 10MHz

- Sample and Hold

- Selectable sample time 2 257 \* ADC internal clock period

- Self Calibration

- Automatic full calibration on powerup

- Optional incremental calibration after each conversion

- Status Signals:

- Conversion in progress

- Sampling in progress

- Calibration in progress

- Data valid

- Power Requirements

- 3.3V for Analog, 1.5V for Digital, and reference voltage (2.56V to 3.3V)

## **Analog Block Summary**

- Up to 10 Analog Quads per Device

- Pre-scaler input range:

- -10.5 V to 0V or 0V to 12V for AV and AC inputs

- 0 to 16V for AT input

- Voltage Monitor

- Current Monitor

- Temperature Monitor

- Gate Driver For controlling Power MOSFETs

- 32 Input Channel ADC with Selectable Resolution (8/10/12 bit)

- Selectable Internal/External Voltage Reference

- 1.5V Voltage Regulator

- Real Time Counter (RTC)

#### Fusion: I/O Overview

- Fusion I/Os Are Organized in Banks Supporting Multiple Standards

- 1.5 V, 1.8 V, 2.5 V and 3.3 V

- Common I/O Features

- Programmable Slew Rate

- Programmable Drive Strength

- Weak Pull-up / Pull-down

- I/Os Power Up in Known State

- No special power up sequencing is required

## Fusion: I/O Functions

#### Regular I/Os

- Input, Output, Tristate and Bidirectional Buffers

- Registered I/Os

- Built-in Input, Output and Output-Enable Registers

- Each Register Equivalent to 1-tile Core Flip-flop

- DDR I/Os

- Built-in Input and Output DDR Registers

# Fusion I/O Bank Types

- Hot Swap Bank

- Support for Single-ended I/O Standards

- LVTTL, LVCMOS

- Hot Swappable

- 3 Drive Strengths, Weak Pull-up / Pull-down Circuits

- DDR Transmit / Receive

- LVDS Bank

- Support for Single-ended and Differential I/O Standards

- Single-ended

- LVTTL, LVCMOS

- PCI, PCI-X

- Differential

- High-Speed 700Mb/s LVDS with External Resistors

- LVPECL I/O

- 2 Programmable Slew Rates, 6 Drive Strengths, Weak Pull-up / Pull-down Circuits

- DDR Transmit / Receive

- No Hot-swap Capability

## Fusion I/O Bank Types (cont.)

#### Pro I/O Bank

- LVDS Bank I/O Standards Support PLUS ...

- ... Voltage-Referenced I/O Standards

- HSTL1

- SSTL2/3

- GTL+

- 2 Programmable Slew Rates, 6 Drive Strengths, Weak Pull-up / Pulldown Circuits

- DDR Transmit / Receive

- Hot-Swappable

- Analog I/O Bank

- Analog Quad I/O Structure

- Can be used for low speed digital input signals

## Fusion I/O: I/O Bank Type Summary

| I/O Bank | Single-Ended I/O Standard                                                                | Differential I/O<br>Standard | Voltage-Referenced                                                                                        | Hot-Swap |

|----------|------------------------------------------------------------------------------------------|------------------------------|-----------------------------------------------------------------------------------------------------------|----------|

| Hot-Swap | LVTTL/LVCMOS 3.3 V, LVCMOS 2.5 V/1.8 V/<br>1.5 V, LVCMOS2.5/5.0 V                        | _                            | _                                                                                                         | Yes      |

| LVDS     | LVTTL/LVCMOS 3.3 V, LVCMOS 2.5 V/1.8 V/<br>1.5 V, LVCMOS2.5/5.0 V, 3.3 V PCI/3.3 V PCI-X | LVPECL and LVDS              | _                                                                                                         | _        |

| Pro I/O  | LVTTL/LVCMOS 3.3 V, LVCMOS 2.5 V/1.8 V/<br>1.5 V, LVCMOS2.5/5.0 V, 3.3 V PCI/3.3 V PCI-X |                              | GTL+ 2.5 V / 3.3 V, GTL 2.5 V / 3.3 V,<br>HSTL Class 1 and 2, SSTL2 Class 1<br>and 2, SSTL3 Class 1 and 2 | Yes      |

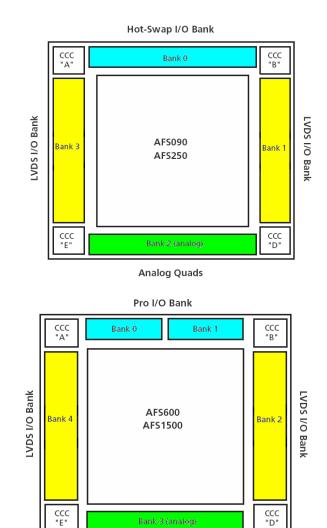

# Fusion: I/O Banks per Device

- AFS090 / AFS250

- Four I/O Banks:

- 1 Hot-swap Bank North side of chip

- 2 LVDS Banks East, West sides

- 1 Analog Bank South side

- AFS600 / AFS1500

- Five I/O Banks:

- 2 Pro I/O Banks North side of chip

- 2 LVDS Banks East, West sides

- 1 Analog Bank South side

Bank 3 (analog)

Analog Quads

#### LVDS / Pro I/O Banks: Output Drive and Slew Rate

#### LVDS Bank

|                    | OUT_DRIVE (mA) |   |   |   |    |    |      |     |

|--------------------|----------------|---|---|---|----|----|------|-----|

| I/O Standards      | 2              | 4 | 6 | 8 | 12 | 16 | Slew |     |

| LVTTL/LVCMOS 3.3 V | ✓              | ~ | ~ | 1 | ~  | ~  | High | Low |

| LVCMOS 2.5 V       | ✓              | ~ | ~ | ~ | ~  | -  | High | Low |

| LVCMOS 1.8 V       | $\checkmark$   | ~ | ~ | 1 | _  | _  | High | Low |

| LVCMOS 1.5 V       | $\checkmark$   | 1 | _ | _ | _  | _  | High | Low |

#### Pro I/O Bank

|                    | OUT_DRIVE (mA) |   |   |   |    |    |    |      |     |

|--------------------|----------------|---|---|---|----|----|----|------|-----|

| I/O Standards      | 2              | 4 | 6 | 8 | 12 | 16 | 24 | Slew |     |

| LVTTL/LVCMOS 3.3 V | 1              | ~ | ~ | ~ | ~  | ~  | ~  | High | Low |

| LVCMOS 2.5 V       | 1              | ~ | 1 | 1 | ~  | ~  | ~  | High | Low |

| LVCMOS 2.5 V/5.0 V | 1              | ~ | 1 | 1 | ~  | ~  | 1  | High | Low |

| LVCMOS 1.8 V       | 1              | ~ | 1 | 1 | ~  | 1  | _  | High | Low |

| LVCMOS 1.5 V       | 1              | 1 | 1 | 1 | 1  | _  | _  | High | Low |

# Fusion: I/O Banks and User I/O Counts

| $\mathbf{i}$           | Part #             | AFS090               | AFS250               | AFS600              | AFS1500             |

|------------------------|--------------------|----------------------|----------------------|---------------------|---------------------|

|                        | I/O Types          | Analog / LVDS / Std+ | Analog / LVDS / Std+ | Analog / LVDS / Pro | Analog / LVDS / Pro |

| 0/                     | I/O Banks (+ JTAG) | 4                    | 4                    | 5                   | 5                   |

| 1                      | Max Digital I/O    | 73                   | 114                  | 172                 | 278                 |

|                        | Analog I/O         | 20                   | 24                   | 40                  | 40                  |

|                        | QN108              | 36/14                |                      |                     |                     |

| al /                   | QN180              | 48/20                | 62/24                |                     |                     |

| D: digital ,<br>analog | PQ208              |                      | 93/24                | 95/40               |                     |

| ): d<br>ana            | FG256              | 73/20                | 114/24               | 119/40              | 119/40              |

| I/О:<br>а              | FG484              |                      |                      | 172/40              | 228/40              |

|                        | FG676              |                      |                      |                     | 278/40              |

#### Agenda

- Fusion Overview

- Fusion Architecture

- Fusion Design Flow

- Development Support

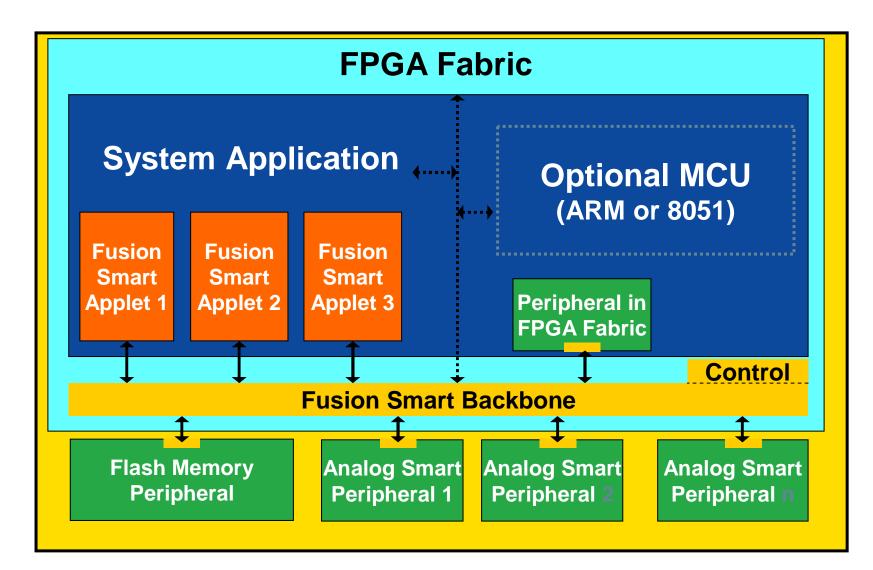

# **Fusion Design Flow**

- Fusion Smart Backbone

- Libero Flow

- SmartGen

- Simulation

- Programming and Security

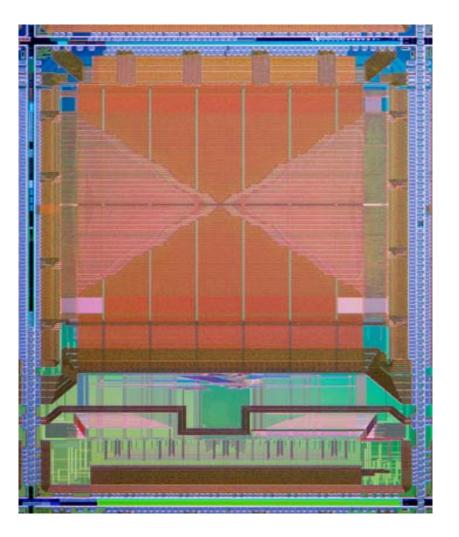

# Actel Fusion Silicon: Physical View

# The Fusion Backbone

#### System Overview

- Soft IP Role in System

- "Glue" That Binds System Components Together

- Main Control for Analog System

- Sampling

- Digital low-pass filtering

- Threshold comparisons

- State filtering

- GPI/GPO

- Makes microcontroller dependency unnecessary (self-sustained)

- Soft IP Configuration

- All configuration within the Analog I/F Soft IP is controlled via setting toplevel Generics/Parameters and propagating these values through hierarchy

- Allow user read access to RAMs, RAM address space size, enable DLPF, control Current/Temperature monitoring functions, Declare number of GPI/GPO signals, etc.

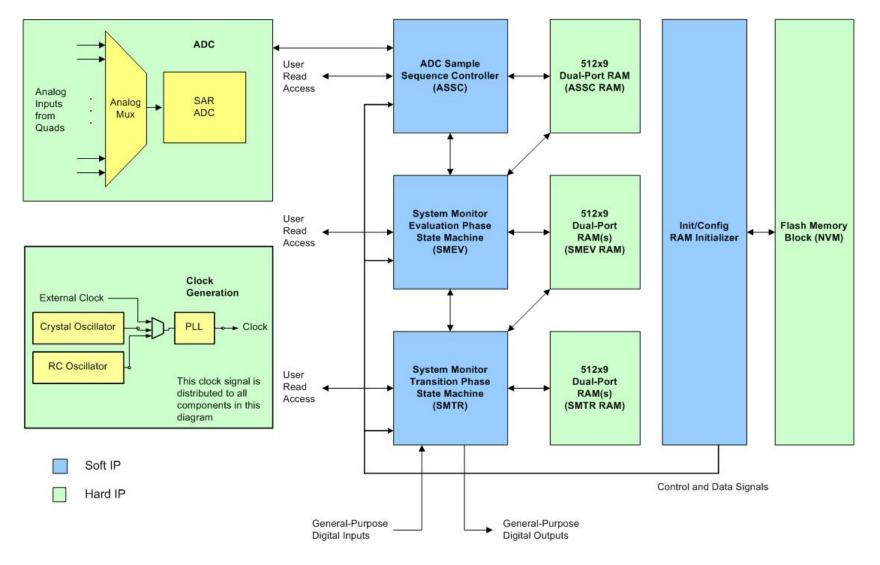

#### System Overview Hard/Soft IP Blocks

# System Overview

- Non-Volatile Memory (NVM)

- System configuration storage

- Including Analog system configuration parameters

- User-define storage

- On-chip/off-chip microcontroller(s)

- User data storage

- etc.

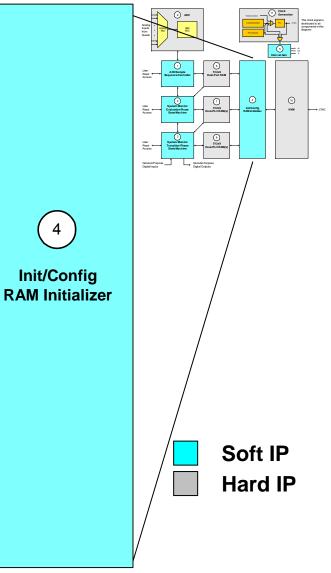

#### System Overview Init/Confia Block

- Init/Config Soft IP Block

- Reads configuration information from NVM

- Initializes (writes) all "clients"

- Analog Quads, analog I/F soft IP, user IP

- When init/config is done, the analog I/F soft IP commences operation

#### System Overview Dual-Port RAM Blocks

#### 512x9 Dual-port RAM Blocks

- Heart of Analog I/F system

- Initialized by Init/Config

- ASSC block Configuration

- Parameter storage

- ADC sample storage for each analog channel

- Digitally low-pass filtered ADC sample storage

- Application sequence storage for SMEV and SMTR blocks

- Threshold comparison results for SMEV block

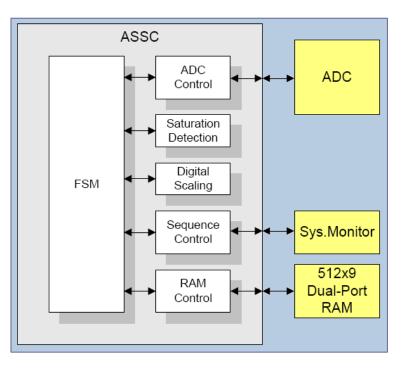

#### System Overview ASSC Soft IP Block

- ADC Sample

Sequence Controller (ASSC)

- Controls ADC

- Calibration

- Power-down

- Sampling

- 8/10/12-bit Resolution

- Detects Saturation of Channels

- Digital post-scaling of ADC Samples

- Controls Current Monitor and Temperature Monitor Strobes

- RAM Stores Sequence Information for ASSC

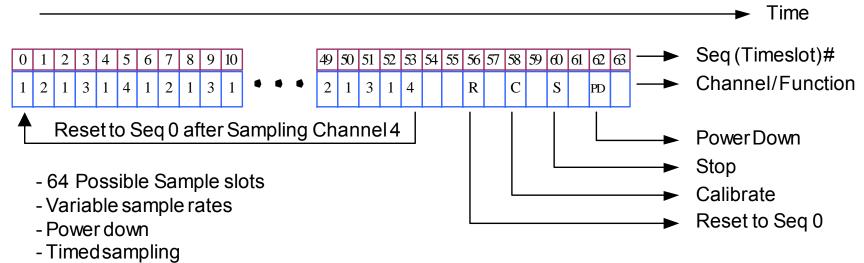

# **Sampling Sequence Specification**

- Why do we need to Sequence the Samples???

- 32 analog signals; 1 ADC

- TDM Sequencing

- 64 Time Slots

- More time slots for a Channel; more ADC Mindshare; Higher Throughput

- Each channel Added to Analog System Gets Added to Sequencer Automatically

- Sequence can be Optionally Modified for More/Less Samples

- Out of Sequence Jumps for Special Sampling During Runtime

- One time jump; return to regular operating sequence

- No automatic sequence, manual jump requests only

- Main Operating Sequence

- Automatically computed based on target rate

- Manual specification for customized applications

#### Main Feature Description ASSC Time Slots

Programmable Sequencer

- Automatic or external triggering

- External controlled 'jump to Seq #'

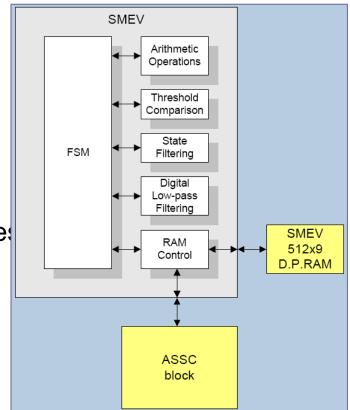

#### System Overview SMEV Soft IP Block

- System Monitor Evaluation Phase State Machine

- Compares ADC Samples with user-defined Thresholds

- Simple 12-bit, Unsigned Arithmetic Operations

- A[11:0], B[11:0]

- Digital Low-Pass Filtering of ADC Samples

- Average ADC sampled data

- Requires only current ADC sample and previous averaged data

- State Filtering (Digital Correlation)

- Look for 0->1 or 1->0 Transitions

- RAM Stores Application Sequences for SMEV

- Sequences controlled by Op-codes

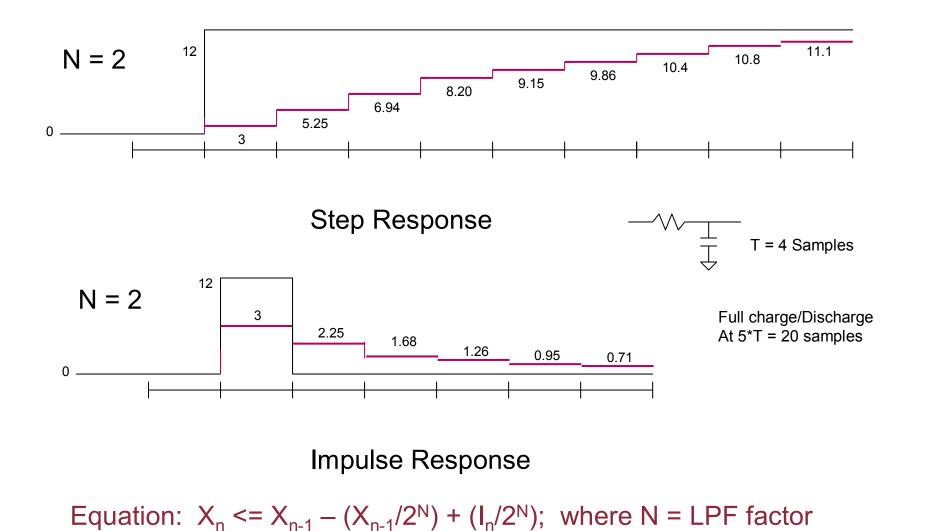

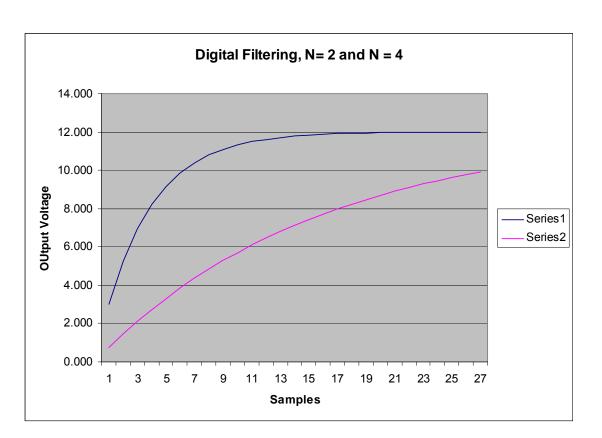

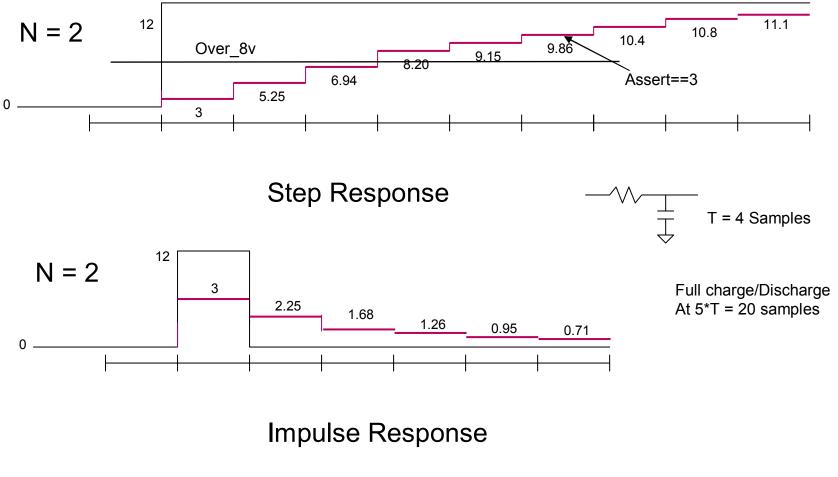

# **Digital Low Pass Filtering**

Equation:

$$X_n \le X_{n-1} - (X_{n-1}/2^N) + (I_n/2^N)$$

; where N = LPF factor

#### Digital Filtering - Step Response

| N =             | 2      | 4     |

|-----------------|--------|-------|

| ln =            | 12     | 12    |

| Initial Value = | 0      | 0     |

|                 |        |       |

| Хо              | 3.000  | 0.750 |

| X1              | 5.250  | 1.453 |

| X2              | 6.938  | 2.112 |

| X3              | 8.203  | 2.730 |

| X4              | 9.152  | 3.310 |

| X5              | 9.864  | 3.853 |

| X6              | 10.398 | 4.362 |

| X7              | 10.799 | 4.839 |

| X8              | 11.099 | 5.287 |

| X9              | 11.324 | 5.706 |

| X10             | 11.493 | 6.100 |

| X11             | 11.620 | 6.469 |

| X12             | 11.715 | 6.814 |

| X13             | 11.786 | 7.138 |

| X14             | 11.840 | 7.442 |

| X15             | 11.880 | 7.727 |

# **State Filtering**

Equation:  $X_n \le X_{n-1} - (X_{n-1}/2^N) + (I_n/2^N)$ ; where N = LPF factor

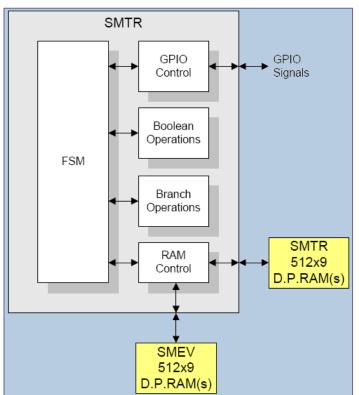

#### System Overview SMTR Soft IP Block

- System Monitor Transition

Phase State Machine

- User-defined Digital Inputs and Digital Outputs (flags)

- Boolean Operations on Digital Inputs

and Internal Temporary Registers

- Branching Operations (if-then-else conditional jumps, looping)

- "Microcontroller-like"

- Reads and Processes SMEV Comparisons

- RAM Stores Application Sequences for SMTR

- Sequences Controlled by Op-codes

# **Data Processing Order**

- Acquire Analog Signal

- Convert to Digital Data

- Average the Resulting Data to Smooth the Samples

- Compare the Result With the Threshold to Detect Overflow or Underflow

- Wait for Multiple Compare Results to Remove Glitches

- Raise the Over/Under Flow Flag

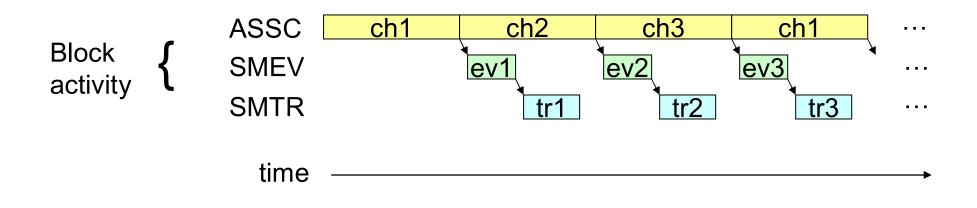

#### Main Feature Description Analog I/F Operation Flow

- ASSC -> SMEV -> SMTR

- Pipelined, TDM operation: ADC samples first, Evaluation of samples second, Transition decisions based on Evaluation third, repeat ...

# Soft IP Summary

- Soft IP Main Control for Analog System

- Configurable via Setting Generics/Parameters at toplevel

- Pipelined Operation

- Complex Sequencing, Branching, and Looping Operations Possible With Limited Hardware Resources

- Completely Self-sustained System (no Micro Required)

# **Fusion Design Flow**

- Fusion Smart Backbone

- Libero Flow

- SmartGen

- Simulation

- Programming and Security

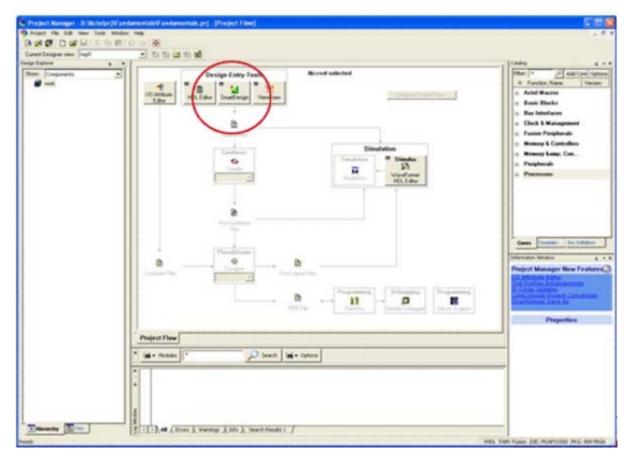

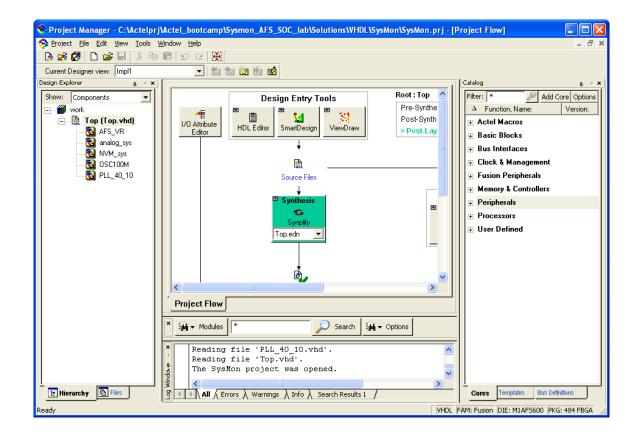

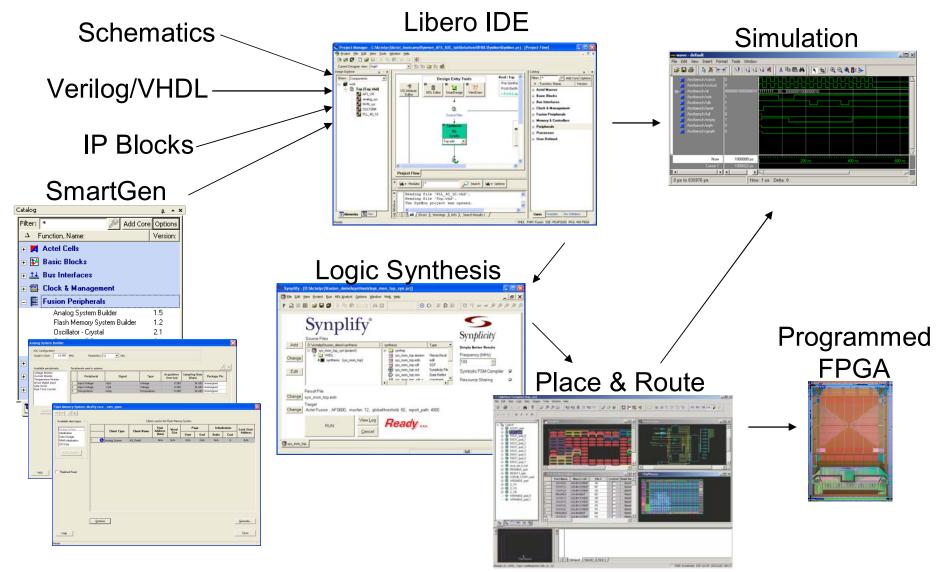

# Libero IDE

- Integrated Development Environment

- Schematic Editor

- HDL entry tools

- SmartGen Wizard

- Actel IP Cores

- Logic Synthesis

- Logic Simulator

- I/O Editor

- Place & Route tools

- Timing Analysis

- Device Programming

# Familiar FPGA Design Flow

# **Fusion Design Flow**

- Fusion Smart Backbone

- Libero Flow

- SmartGen

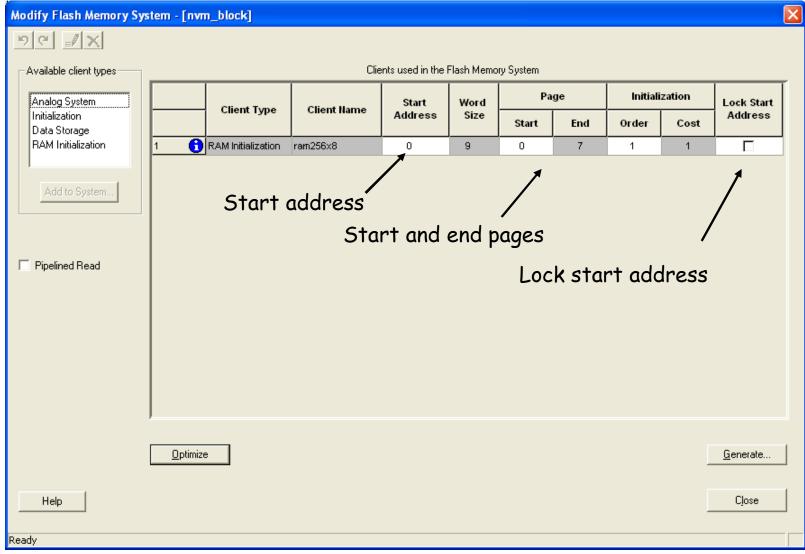

- Flash Memory System Builder

- Analog System Builder

- Other SmartGen Cores

- Simulation

- Programming and Security

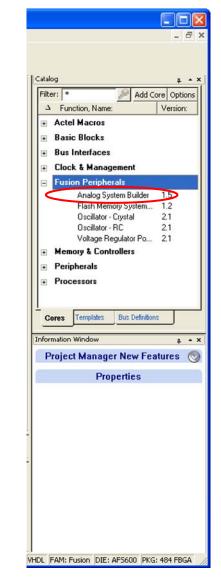

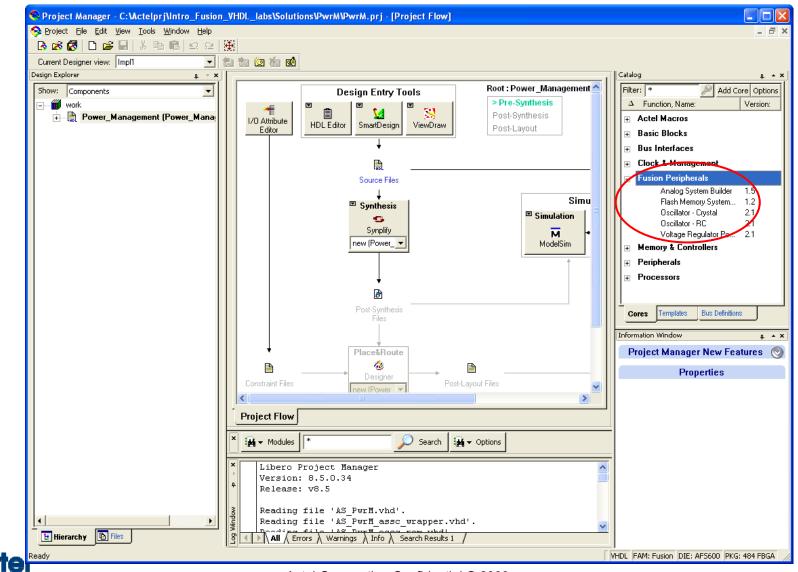

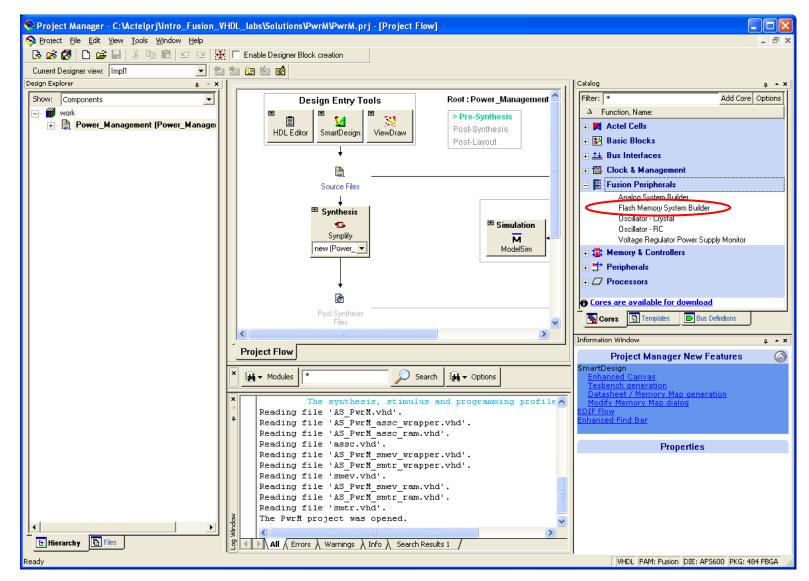

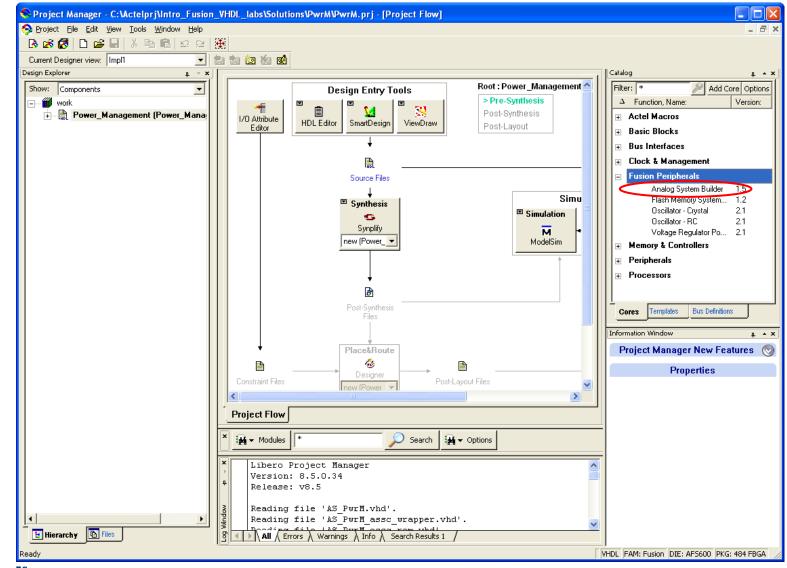

#### Libero with SmartGen

POWER

# **SmartGen Cores for Fusion**

- New System Builders

- Analog System Builder

- Flash Memory System Builder

- New Silicon Cores

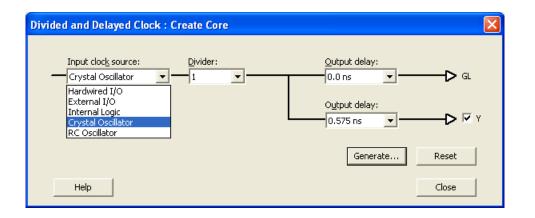

- Divided and Delayed Clock

- Crystal Oscillator

- VRPSM

- NGMUX

- RC Oscillator

- Dynamic CCC

- Enhanced Cores from ProASIC3/E

- Static PLL

- Delayed Clock

- RAM

- Initialization from Flash Memory

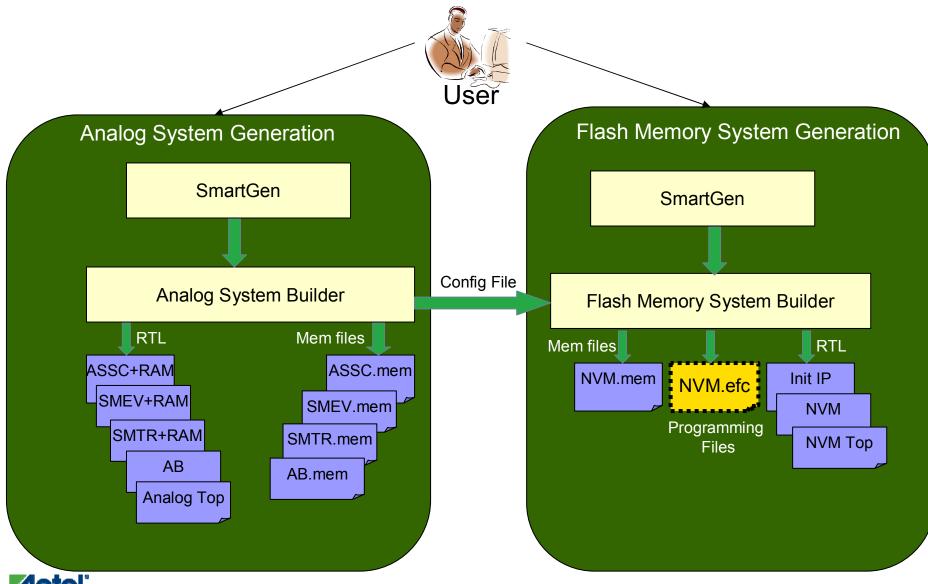

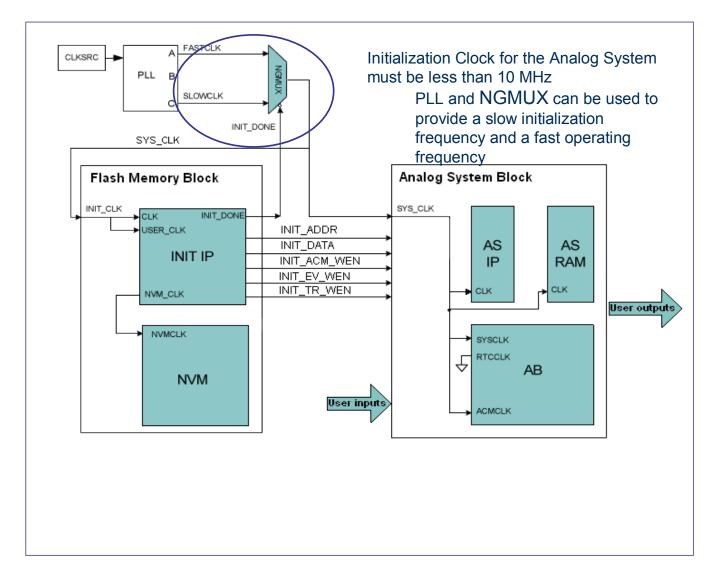

#### Analog & NVM System Generation

# **Fusion Design Flow**

- Fusion Smart Backbone

- Libero Flow

- SmartGen

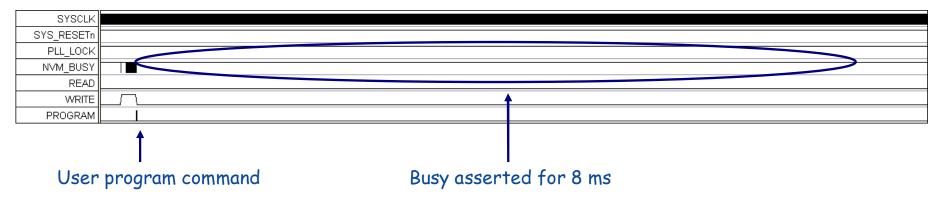

- Flash Memory System Builder