2065-20

#### Advanced Training Course on FPGA Design and VHDL for Hardware Simulation and Synthesis

26 October - 20 November, 2009

Introduction to SoC Design

Nizar Abdallah ACTEL Corp. 2061 Stierlin Court Mountain View CA 94043-4655 U.S.A.

# Introduction to SoC Design

Actel Corporation © 2009

# Agenda

- Overview

- ARM Cortex-M1 Architecture

- Cortex-M1 Instruction Set

- Actel's Cortex-M1

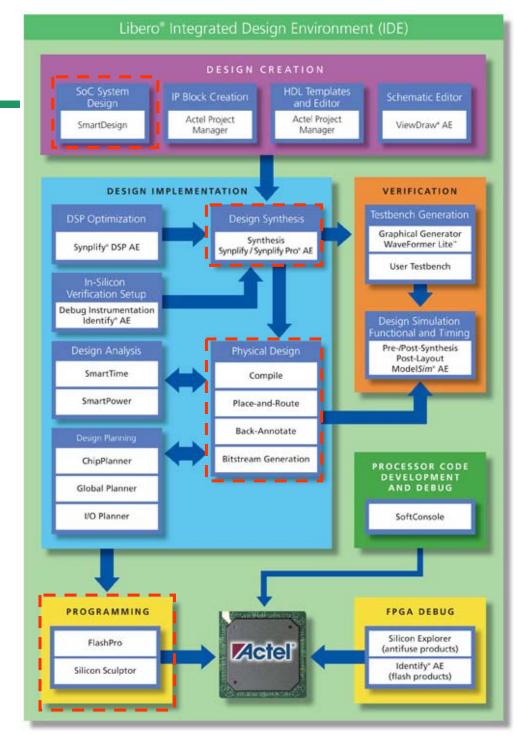

- System-on-Chip and SmartDesign

- Testing

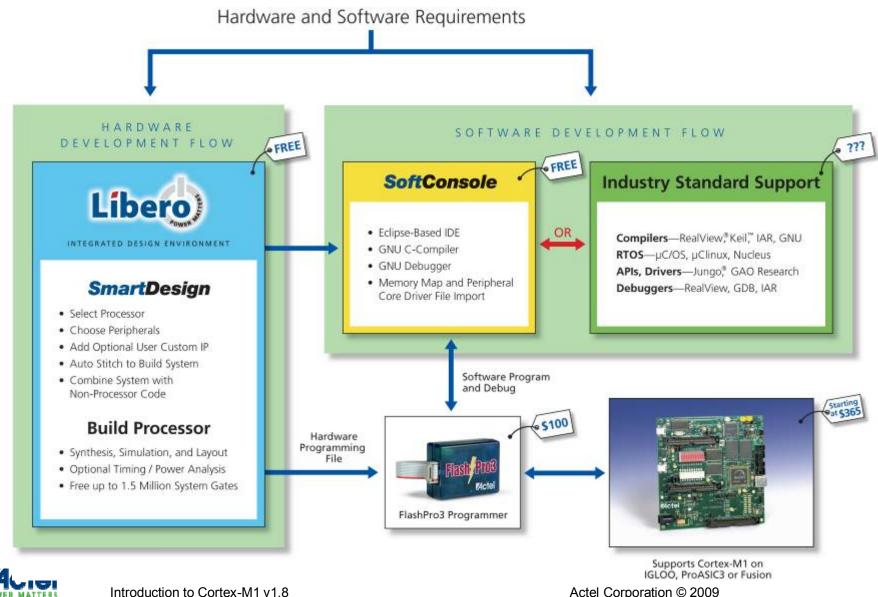

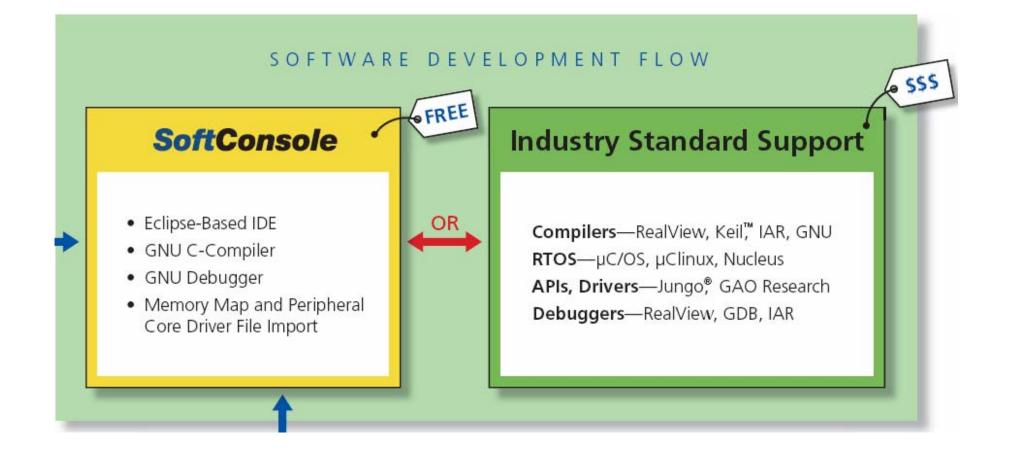

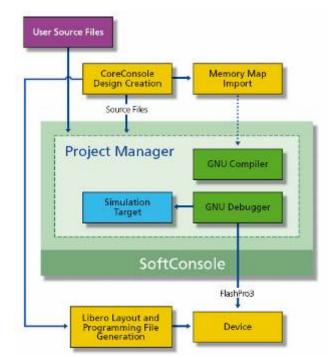

- Cortex-M1 Development Tools

- Reference

## Overview

Actel Corporation © 2009

# **SoC Definition**

- What exactly is SoC?

- Entire system built on a single piece of silicon

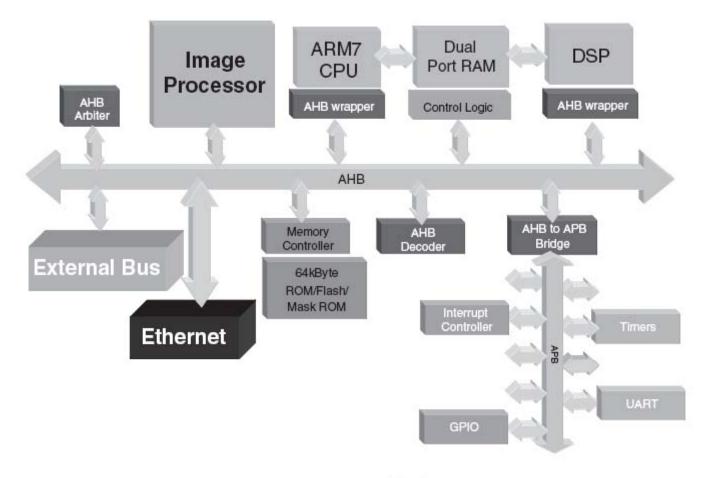

- Includes a processor, memory, DSP Cores, IO devices, interfaces to external circuitry, and custom IPs as Verilog or VHDL modules

- SoC designs primarily used in embedded applications

- SoC design brings a new level of complexity to IC design

- Cost to develop is very high

- Large and complex IP from many diverse sources

- "Black box" view of IP (cannot change or "see" details)

- Lack of existing interface standards

- Fairly complex SW running on an on-chip CPU

- Integration, performance, and power are crucial

- Mixed signal (analog & digital) circuitry

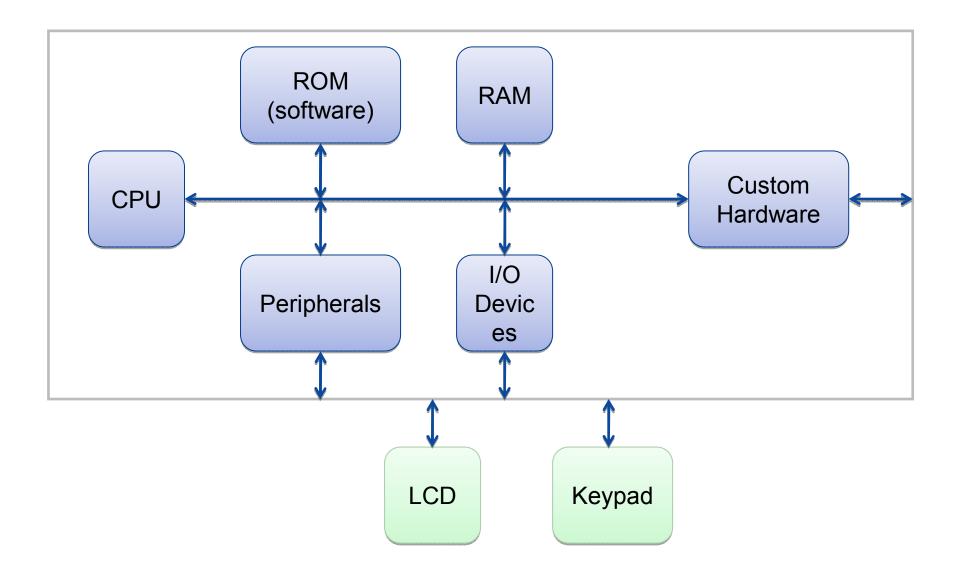

# **Embedded System Definition**

- A dedicated computer hardware with software designed to solve a specific problem

- Uses "hidden" microprocessors from 8bit MC to 64-bit MP

- Some RAM or ROM is required; Flash commonly used

- ...and a mix of Timers, Interrupt controller, UARTs, GPIO, DMA controllers, Real time clock, LCD controller...

- Embedded system software divided into operating software and application software

# **Embedded System Diagram**

# **Embedded System Design Constraints**

- Cost

- Memory

- Power

- Real-time Response

- Performance

- System Size

- Reliability

- Time-to-Market

# **Embedded System Classification**

- Little or no custom hardware design

- Time-to-market requirement

- Use high integration microprocessor or off the shelf boards

- A lot of custom hardware SoB design

- High performance requirements

- High performance microprocessor (PowerPC, MIPS chips)

- Large custom logic on boards (FPGA, ASIC)

- Even maybe multiple boards...

- A lot of custom hardware SoB design

- Small size and low-power requirements

- One or more microprocessors on a chip

- IPs such as ARM or MIPS

- Cost to develop is very high

- Consumer electronics: MP3, digital cameras...

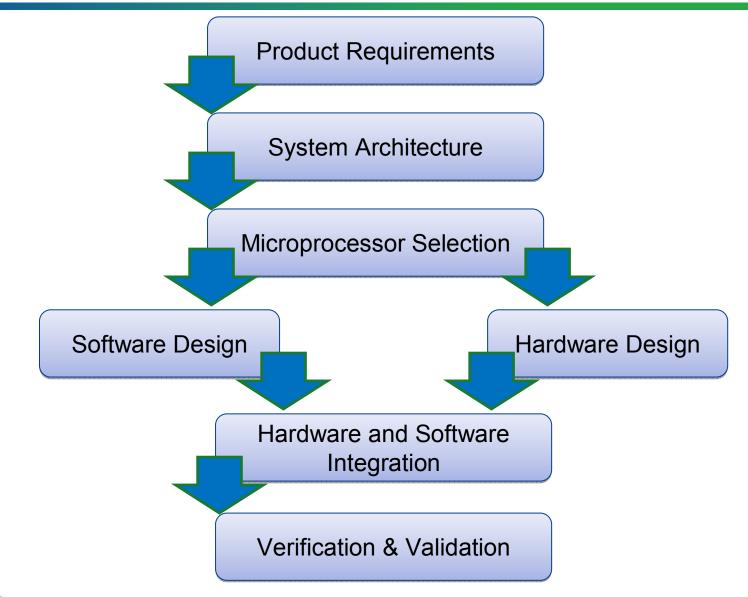

# **Embedded System Design Process**

# Embedded System Design Process

## Requirements

- Product specifications

- Required features and functionalities

- System Architecture

- Defines major blocs and functions

- Interfaces, bus structure, HW & SW functionalities

- Simulation, SW, and Spreadsheet to define best architecture

- How many packet/sec can this router handle?

- Microprocessor selection

- One of the most difficult tasks

- Perf, cost, power, SW dev. Tools, legacy SW, RTOS, Sim models...

# Embedded System Design Process

- Hardware Design

- Important data to the SW team

- CPU address map, Register definition for all SW programmable registers

- Software Design

- Boot code

- Hardware diagnostics, device drivers, Application software

- RTOS

- Hardware & Software integration

- Verification and Validation

# Example1: Embedded System

- In order to test the hardware, a Cordic algorithm is to be implemented. This algorithm calculates the sine and cosine functions of a given number. Such a number is to be entered over the UART interface through a Hyper-Terminal or some similar program on a PC.

- The first action of the main program will initialize the UART. Then some text is to be output over the UART, following which the program would wait for input from the user. Such input would first be checked for any errors, before being formatted as a fixed point number, with 8 bits before and 24 bits after the decimal point, and passed on to the function that implemented the Cordic algorithm.

- The result of the calculation are to be transformed back into strings and output over the UART.

## Introduction to Cortex-M1

Actel Corporation © 2009

# Agenda

- Overview

- ARM Cortex-M1 Architecture

- Cortex-M1 Instruction Set

- Actel's Cortex-M1

- System-on-Chip and SmartDesign

- Testing

- Cortex-M1 Development Tools

- Reference

## Overview

Actel Corporation © 2009

# **ARM History**

- First ARM Processor Developed in Mid-eighties

- Acorn Computers, Limited in Cambridge, England

- Originally, ARM Stood for Acorn RISC Machine

- Later Changed to Advanced RISC Machine

- All Major Chip Manufacturers Have Licenses to One or More ARM Cores, more than 100...

- Analog Devices, Atmel, Cirrus, Fujitsu, IBM, Infineon, Intel, Mitsubishi, Motorola, National Semiconductor, NEC, Philips, Sharp, ST Microelectronics, Texas Instruments, Toshiba ...

- ARM7TDMI Most Popular ARM Core in Embedded Systems

- Business Model

- License fees for microprocessors and other IP blocks

- Per-chip royalties on shipments of chips using ARM IP

- Tools & boards to support development and debugging

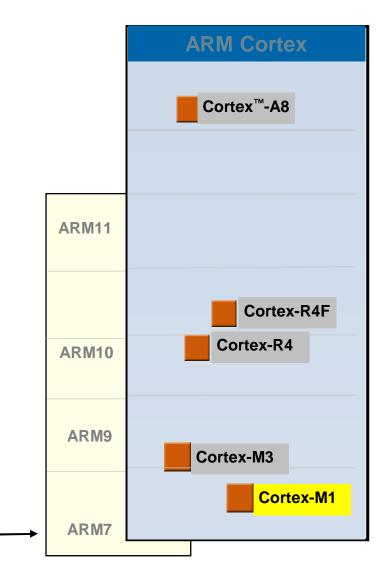

# **ARM Processors**

- Established Processors

- ARM7 (e.g., Actel's CoreMP7), ARM9, ARM11, and Others

- RISC principles: Simplicity and High Instruction Throughput

- New Cortex Processors from ARM

- Range of Processors which Target Different Markets/Applications

- Three Cortex Variants:

| Series | Market Segment                                                                           | Instruction Sets<br>Supported |

|--------|------------------------------------------------------------------------------------------|-------------------------------|

| A      | Applications – Complex Operating Systems and User Applications                           | ARM, Thumb and Thumb-2        |

| R      | Real-time Systems                                                                        | ARM, Thumb and Thumb-2        |

| М      | Microcontroller – Deeply-embedded<br>Processors for Cost/Power-sensitive<br>Applications | Thumb-2 Only                  |

## **RISC Processors**

## World Domination

| thru          | 1994   | 1995   | 1996   | 1997   | 1998    | 1999    | 2000    | 2001    |

|---------------|--------|--------|--------|--------|---------|---------|---------|---------|

| ARM/StrongARM | 2,170  | 2,100  | 4,200  | 9,800  | 50,400  | 152,000 | 414,000 | 402,000 |

| MIPS          | 3,254  | 5,500  | 19,200 | 48,000 | 53,200  | 57,000  | 62,800  | 62,000  |

| Hitachi SH    | 2,800  | 14,000 | 18,300 | 23,800 | 2,600   | 33,000  | 50,000  | 45,000  |

| PowerPC       | 2,090  | 3,300  | 4,300  | 3,800  | 6,800   | 8,300   | 18,800  | 23,000  |

| Total         | 30,499 | 33,830 | 58,480 | 98,220 | 149,080 | 262,820 | 556,800 | 538,860 |

#### Merchant RISC Microprocessor Shipments (1000s)

Source: Andrew Allison

# ARM's New Processor Family

- Common Architecture across All Cores

- Thumb®-2 Blended 16/32-bit ISA

- Three ARM Cortex Series

- Applications (A Series)

- Real-time (R Series)

- Microcontroller (M Series)

- Cortex-M1 Processor

- Designed for FPGA Implementation

- Upward-compatible with Cortex Range

**ARM7TDMI (CoreMP7)**

• Easy Path to ASIC

# **ARM Cores**

- Hard Macro form

- Provided as a layout object

- High performance and small die area

- Limited portability between different silicon processes

- Soft Macro form

- Verilog RTL format

- More flexibility

- Less performance

- Most common form today!

## Cortex-M1 Next Member of the M Series

- Intended for FPGA Implementation

- Soft Processor (Implemented in FPGA Fabric)

- Small, Powerful, Highly-optimized, and Configurable

- ARMv6-M Architecture

- Subset of Thumb-2: All 16-bit Thumb Instructions and Some 32-bit Thumb-2 Instructions

- Delivered as Black Box via SmartDesign

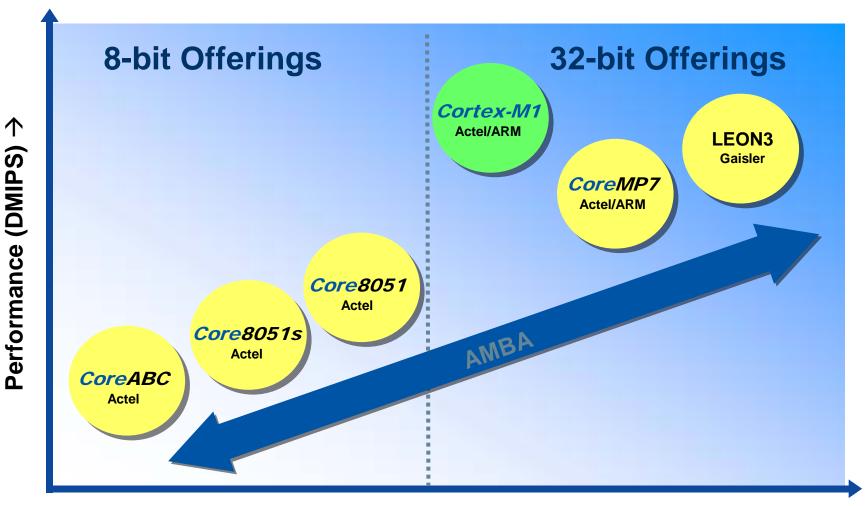

# **Actel Processor Offerings**

#### Core Size (Tiles) $\rightarrow$

AMBA: Advanced Microcontoller Bus Architecture

DMIPS: Dhrystone MIPS (Million Instructions Per Second)

## Cortex-M1 Overview of Features

- Soft 32-bit IP Core for FPGAs

- High-frequency, Low-area Design

- Executes All Existing Thumb® Code

- ARMv6-M Instruction Set (Thumb2)

- Nested Vectored Interrupt Controller (NVIC)

- Balance between Size and Speed

- Operates at up to 62MHz

- Implemented in as few as 4300 Tiles (A3P / Fusion)

- Uses Three-stage Pipeline

- Interfaces

- ARM AMBA® AHB-Lite<sup>™</sup> Interface (Single Master)

- Separate Data & Instruction Memory Interfaces

- Debug via JTAG Interface

# Cortex-M1 <u>Nested Vectored Interrupt Controller (NVIC)</u>

| Name of register                 | Туре | Address    |

|----------------------------------|------|------------|

| Interrupt Set Enable Register    | R/W  | 0XE000E100 |

| Interrupt Clear Enable Register  | R/W  | 0XE000E180 |

| Interrupt Set Pending Register   | R/W  | 0XE000E200 |

| Interrupt Clear Pending Register | R/W  | 0XE000E280 |

| Priority 0 Register              | R/W  | 0XE000E400 |

| Priority 1 Register              | R/W  | 0XE000E404 |

| Priority 2 Register              | R/W  | 0XE000E408 |

| Priority 3 Register              | R/W  | 0XE000E40C |

| Priority 4 Register              | R/W  | 0XE000E410 |

| Priority 5 Register              | R/W  | 0XE000E414 |

| Priority 6 Register              | R/W  | 0XE000E418 |

| Priority 7 Register              | R/W  | 0XE000E41C |

Source: ARM Inc.

## **Cortex-M1** Architecture

Actel Corporation © 2009

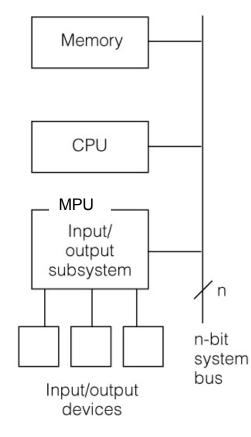

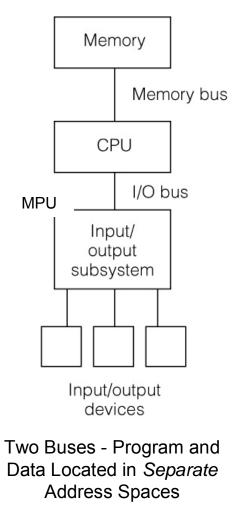

## **Processor Architectures**

#### von Neumann

One Bus - Program and Data Located in Same Address Space

## Harvard

# Cortex-M1

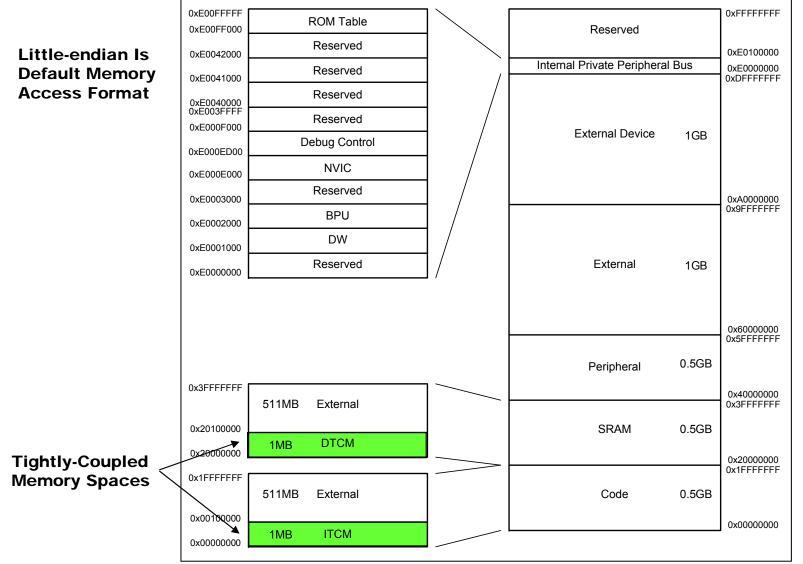

## Architecture and Memory Organization

- Cortex-M1 is von Neumann Architecture …

- Linear 32-bit Address Space (4 GB)

- Only Load, Store, and Swap Instructions Can Access Data from Memory

- Separate Tightly-Coupled Memories Make It 'Slightly Harvard'

- Separate Instruction and Data TCMs

- Limited to 1MB (Maximum) Each

- Cortex-M1 Processor Supports Three Data Types

- Word (32-bit)

- Half-word (16-bit)

- Byte (8-bit)

- Data Alignment

- Words Must Be Aligned to Four-byte Boundaries

- Half-words Must Be Aligned to Two-byte Boundaries

- Bytes Can Be Placed on any Byte Boundary

- Supports Both Big- and Little-endian Formats

## Cortex-M1

## Architecture and Memory Organization

- Historically, Intel uses Little-endian and RISC Big-endian

- ARM allows the user to choose the byte order

| DATA[31:0] | Address 3 | Address 2 | Address 1 | Address 0 |

|------------|-----------|-----------|-----------|-----------|

| 3          | 1 24      | 23 16     | 15 8      | 7 0       |

Little endian byte order

| DATA[31:0] | Address 0 | Address 1 | Address 2 | Address 3 |

|------------|-----------|-----------|-----------|-----------|

| 3          | 1 24      | 23 16     | 15 8      | 7 0       |

Big endian byte order

## Cortex-M1

#### Architecture and Memory Organization

- When data transfers are a full word, the data on the bus is identical for both big-endian and little-endian byte order

- Endianness becomes important for both master and slave when data transfers on the bus are for 1 or 2 bytes

- One of the first questions to always ask for a new design is, "What is the byte order of the design, big or little endian?"

Architecture and Memory Organization

- RISC 32-bit architecture gives best performance to operate on 32-bit data

- Drawback: amount of memory required to hold 32bit instructions, especially in embedded systems

- Code Density in Embedded Systems

- ARM allows running 16-bit instructions called Thumb: 30% less memory for 30% less performance

## Cortex-M1 Memory Map

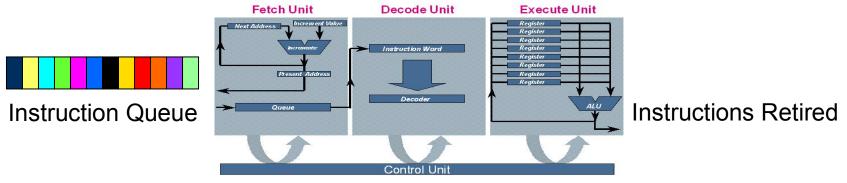

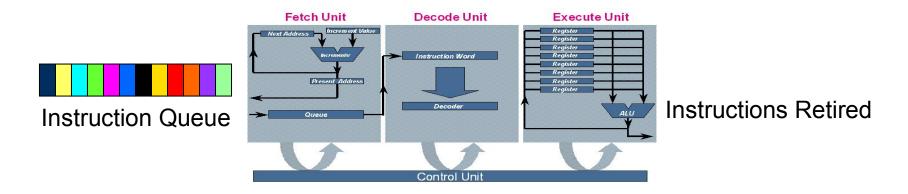

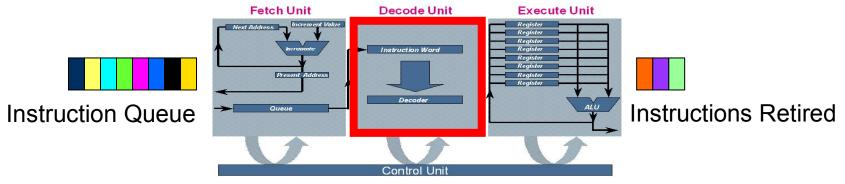

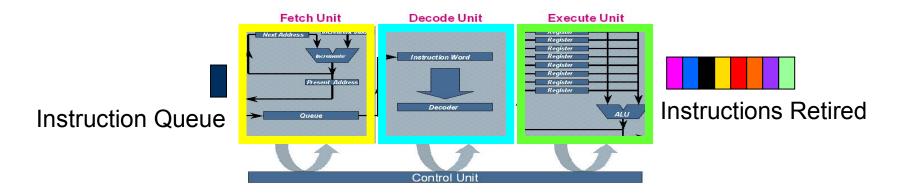

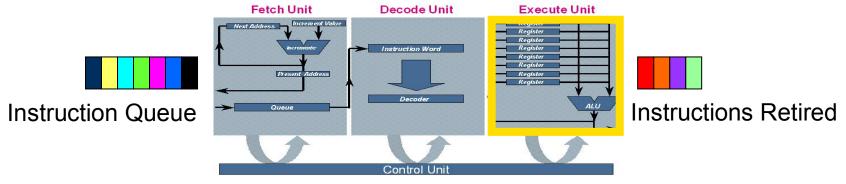

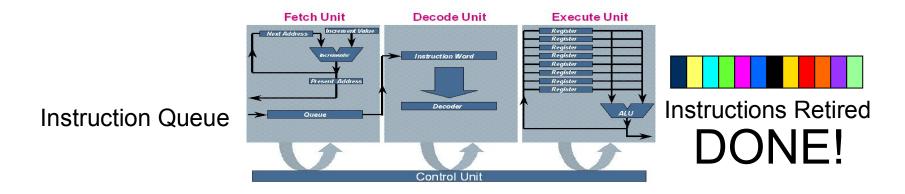

# M1's 3-Stage Instruction Pipeline

- Three Stages Are:

- Fetch Fetching an Instruction from Memory Containing Code

- Decode Decoding Instruction and Preparing Datapath Control Signals for Next Cycle

- Execute Reading Source Registers, Performing Shift or ALU Operations, and Writing Back Result to Destination Register

- One Instruction is Executed Every Cycle when Pipeline is Full

- 3 cycles Needed to Completely Process One Instruction

- 3 cycles Needed to Reload Pipeline Branch Instructions

- Pipeline Halted for One Cycle if Multiple Memory Accesses Needed to Execute Instruction

|               | cycle 1 | cycle 2 | cycle 3 | cycle4  | cycle5  |

|---------------|---------|---------|---------|---------|---------|

| instruction 1 | Fetch   | Decode  | Execute |         |         |

| instruction 2 |         | Fetch   | Decode  | Execute |         |

| instruction 3 |         |         | Fetch   | Decode  | Execute |

## Increasing Processor Performance **Pipelining**

## **Sequential Processor**

#### **Pipelined Processor**

## Increasing Processor Performance *Pipelining*

## **Sequential Processor**

## **Pipelined Processor**

## Increasing Processor Performance **Pipelining**

## Sequential Processor

#### **Pipelined Processor**

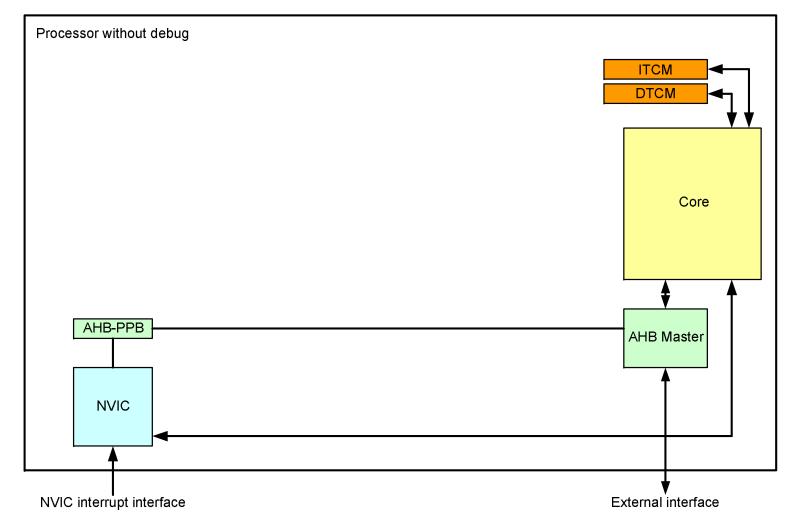

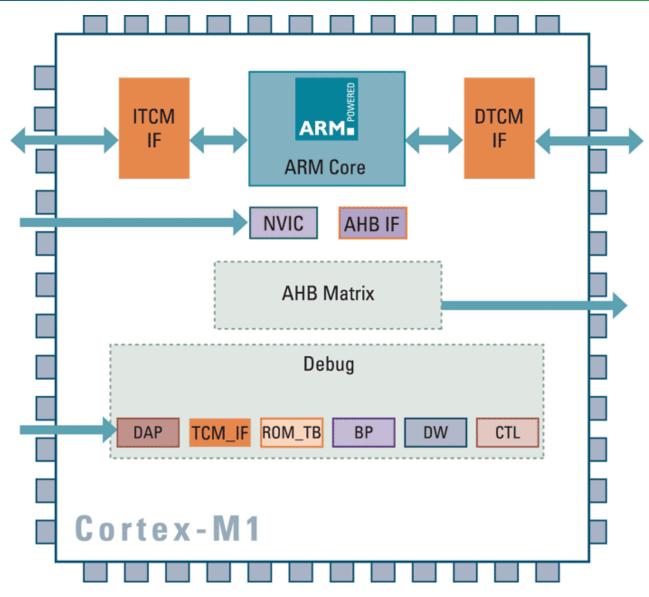

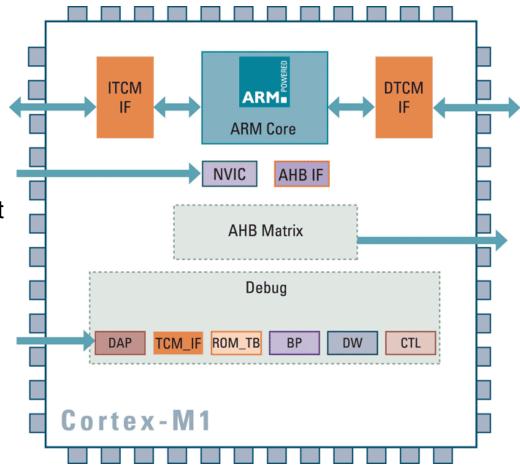

#### Cortex-M1 Without Debug Block Diagram

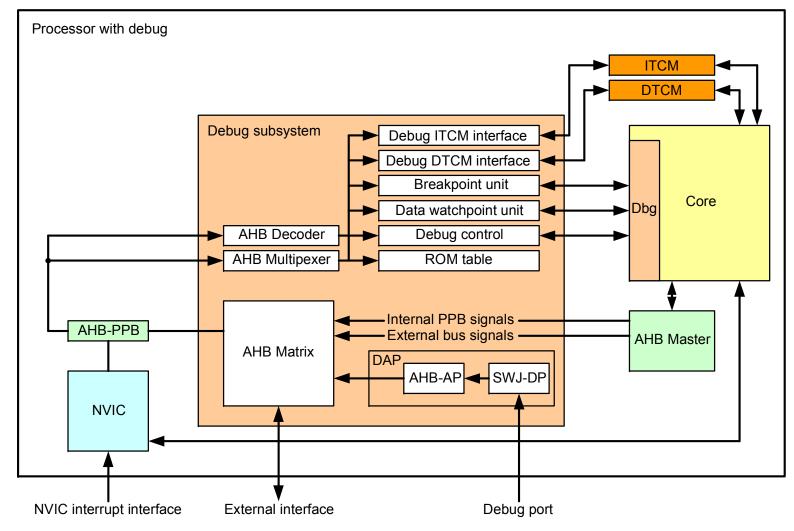

#### Cortex-M1 with Debug Block Diagram

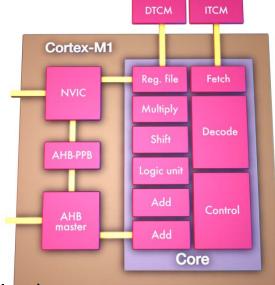

#### Cortex-M1 Architectural Diagram Block by Block

## Cortex-M1 Architectural Diagram Acronyms

- TCM

- Tightly-Coupled Memories

- NVIC

- Nested Vectored Interrupt Controller

- AHB IF

- AMBA AHB Bus Interface

- DAP

- Debug Access Port (See Next Slide)

- ROM\_TB

- ROM Table

- BP

- Breakpoint Unit

- DW

- Data Watchpoint Unit

## **Debug Control Registers**

| Name      | Description                        |

|-----------|------------------------------------|

| ABORT     | Access Port Abort Register         |

| IDCODE    | ID Code Register                   |

| CTRL/STAT | Debug Port Control/Status Register |

| SELECT    | Access Port Select Register        |

| RDBUFF    | Read Buffer                        |

- Access to Debug and AHB Access Control Registers is via Debug Port

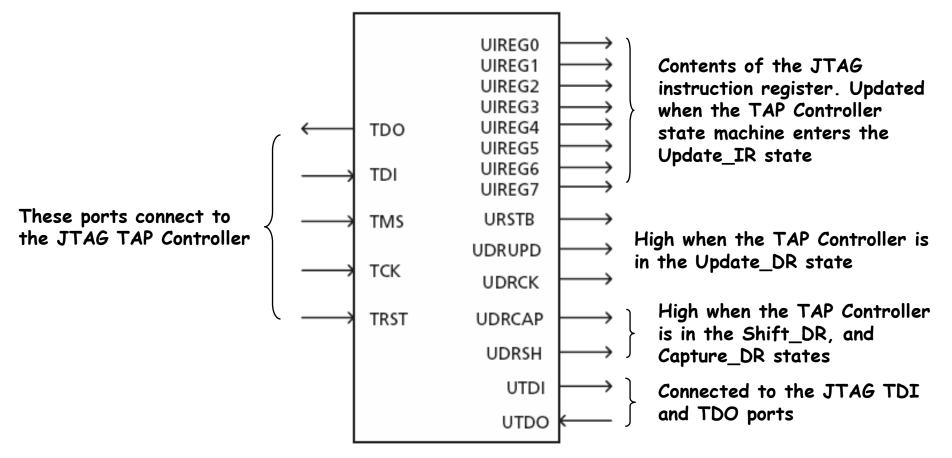

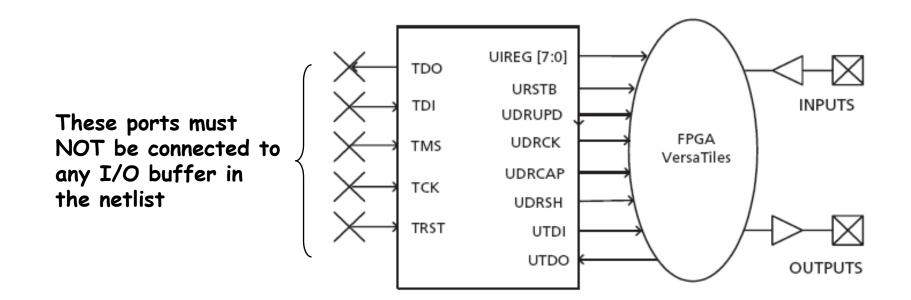

- UJTAG Macro Is Included in Debug Port Logic

## **Debug Control Registers**

- Two configurations for debug:

- The full debug configuration has four breakpoint comparators and two watchpoint comparators. Default configuration.

- The reduced debug configuration has two breakpoint comparators and one watchpoint comparator.

#### Debug facilitates:

- core halt

- core stepping

- core register access while halted

- read/write to: TCMs, AHB address space, internal Private Peripheral Bus (PPB)

- Breakpoints

- watchpoints

#### Main debug components

- Debug control registers to access and control debugging of the core

- BreakPoint Unit (BPU) to implement breakpoints

- Data Watchpoint (DW) unit to implement watchpoints

- debug memory interfaces to access ITCM and DTCM

- ROM table.

## **UJTAG Macro Symbol**

#### UJTAG Macro Is Already Instantiated in Cortex-M1 Debug Unit!

## **UJTAG Interconnection**

#### Cortex-M1 Technical Overview

- Core

- Three-stage Pipeline

- ARMv6-M Instruction Set Architecture

- All 16-bit Thumb Instructions and Some Thumb-2 32-bit Instructions

- Datapath Optimized for Thumb and for FPGA Implementation

- Multiplier, Adder, Shifter and Logic Unit, All in Parallel

- Tightly-coupled Interface to Interrupt Controller

- Supports Tightly-Coupled Memory (TCM) for Instructions and Data

- Registers

- 13 General-purpose 32-bit Registers

- Link Register (LR), Program Counter (PC), Program Status Register (xPSR), Stack Pointer (SP)

#### Cortex-M1 Technical Overview (cont.)

- Debug

- Debug via JTAG or 2-pin Serial-wire Interface

- Provides Access to All Registers and Memory

- Includes Break-point Unit (BP) and Data-watchpoint (DW) Unit

- 4 Breakpoints and 2 Watchpoints

- Nested Vectored Interrupt Controller (NVIC)

- NVIC Is Tightly Coupled to Processor Core

- Low-latency Exception Processing

- Level and Pulse Interrupts Supported

- Processor State Automatically Saved and Restored when Switching to Interrupt Service Routine (ISR)

## AMBA Bus Interface Signals

#### AHB-Lite Bus

| Signal       | Function                                    |

|--------------|---------------------------------------------|

| HCLK         | Bus Clock                                   |

| HRESETn      | ACTIVE-LOW Bus Reset                        |

| HADDR(31:0)  | System Address Bus                          |

| HTRANS(1:0)  | Transfer Type                               |

| HWRITE       | Transfer Direction (1=Write, 0=Read)        |

| HSIZE(2:0)   | Transfer Size                               |

| HBURST(2:0)  | Indicates if Transfer Forms Part of a Burst |

| HPROT        | Protection Control                          |

| HWDATA(31:0) | 32-bit Write Data (from Master)             |

| HRDATA(31:0) | 32-bit Read Data (to Master)                |

| HREADY       | Transfer Complete                           |

| HRESP(1:0)   | Transfer Response                           |

| HMASTLOCK    | Master Signal                               |

## Cortex-M1

#### Debug Interfaces

• Note: Debug Interface Signals Are ALWAYS Present!

| Name        | Туре   | Description            |

|-------------|--------|------------------------|

| RV_TCK      | Input  | RealView JTAG          |

| RV_nTRST    | Input  | RealView JTAG          |

| RV_TMS      | Input  | RealView JTAG          |

| RV_TDI      | Input  | RealView JTAG          |

| RV_nSRST_IN | Input  | RealView JTAG          |

| RV_TRCK     | Input  | RealView JTAG          |

| RV_TDOUT    | Output | RealView JTAG          |

| RV_nTDOEN   | Output | RealView JTAG          |

| UJTAG_TCK   | Input  | FlashPro3 JTAG         |

| UJTAG_TDI   | Input  | FlashPro3 JTAG         |

| UJTAG_TMS   | Input  | FlashPro3 JTAG         |

| UJTAG_TRSTB | Input  | FlashPro3 JTAG         |

| UJTAG_TDO   | Output | FlashPro3 JTAG         |

| EDBGRQ      | Input  | External debug request |

#### Cortex-M1 Miscellaneous Signals

| Name      | Туре   | Description                                |

|-----------|--------|--------------------------------------------|

| HCLK      | Input  | Main processor clock                       |

| NSYSRESET | Input  | External push-button/power-<br>up reset    |

| WDOGRES   | Input  | Watchdog reset to Cortex-<br>M1            |

| WDOGRESn  | Output | Reset of watchdog timer                    |

| HRESETn   | Output | Reset to other components<br>in AHB system |

| IRQ[31:0] | Input  | External Interrupts                        |

| ΝΜΙ       | Input  | Non-maskable Interrupt                     |

| nTRST     | Input  | JTAG reset                                 |

| JTAGTOP   | Output | State Controller Indicator                 |

| nTDOEN    | Output | JTAG data out enable                       |

| LOCKUP    | Output | Core is locked up                          |

| HALTED    | Output | Core is in Halt debug state                |

## Cortex-M1

#### Processor Operating States and Modes

#### States

- Thumb

- Normal Execution

- Runs 16-bit Halfword-aligned Thumb and Thumb-2 Instructions plus 32bit BL, MRS, MSR, ISB, DSB, and DMB Instructions

- Data Types Supported 32-bit Words, 16-bit Halfwords, 8-bit Bytes

- Debug State

- Used for Halting Debug

- Modes

- Thread Mode

- Entered on Reset

- Can Be Re-entered after Exception Return

- Handler Mode

- Used for Handling Exceptions

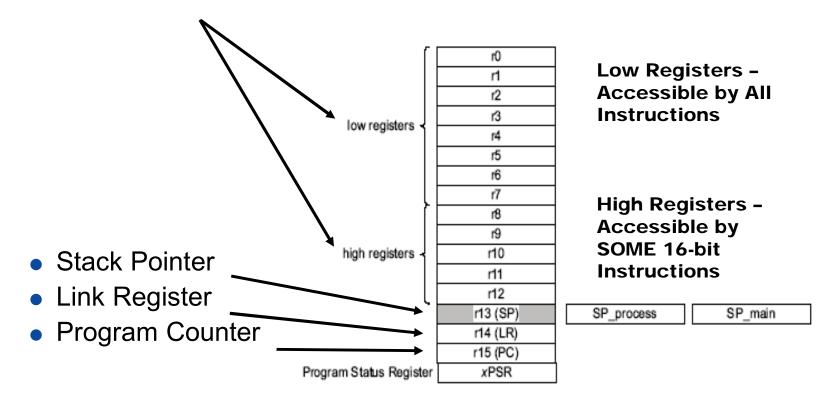

#### Cortex-M1 Reaisters

- 17 Registers

- 13 General-Purpose Registers

#### Cortex-M1 SP. LR and PC Registers

- Stack Pointer

- Auto-aligned to Word Boundary

- Has Banked Register Aliases SP\_process and SP\_main

- Handler Mode Always Uses SP\_main, but You Can Configure Thread Mode to Use Either SP\_main or SP\_process

- Link Register

- Receives Subroutine Return Address from PC when *Branch and Link* (BL) Instruction Is Executed

- LR Is also Used for Exception Return

- At All Other Times, Treat R14 as General-purpose Register

- Program Counter

- Auto-aligned to Halfword Boundaries

#### Cortex-M1

#### Special-Purpose Program StatusRegisters (xPSR)

- Processor Status at System Level is Broken into Three Categories

- Registers Can Be Accessed Individually or Two or Three at a Time Using MRS and MSR Instructions

- Application PSR

- Contains Condition-code Flags

- Before Entering Exception, Processor Saves Condition-code Flags on the Stack

- Accessed with MSR and MRS Instructions

- Interrupt PSR

- Contains Interrupt Service Routine (ISR) Number Current Exception

- Execution PSR (EPSR)

- Contains the Thumb state bit (T-bit)

- Not Directly Accessible except in Debug State

- All Fields Read as Zero using an MRS Instruction

- MSR Instruction Writes Are ignored

- On Entering an Exception, the Processor Saves Combined Information from the Three Status Registers on the Stack

#### Cortex-M1 Exception Types and Priorities

| Position | Exception type            | Priority     | Description                                                                                                                                                                                 | Activated                   |

|----------|---------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| -        | -                         | -            | Stack top is loaded from first entry of vector table on reset.                                                                                                                              | -                           |

| 1        | Reset                     | -3 (highest) | Invoked on power up and warm reset. On first instruction, drops to lowest priority, Thread mode.                                                                                            | Asynchronous                |

| 2        | Non-maskable<br>Interrupt | -2           | <ul> <li>This exception type cannot be:</li> <li>masked or prevented from activation by<br/>any other exception</li> <li>pre-empted by any other exception other<br/>than Reset.</li> </ul> | Asynchronous                |

| 3        | Hard Fault                | -1           | All classes of Fault.                                                                                                                                                                       | Synchronous or asynchronous |

| 4-10     | -                         | -            | Reserved.                                                                                                                                                                                   | -                           |

| 11       | SVC                       | Configurable | System service call using the SVC instruction.                                                                                                                                              | Synchronous                 |

| 12-13    | -                         |              | Reserved.                                                                                                                                                                                   | -                           |

| 14       | PendSV                    | Configurable | Pendable request for system service. This is only pended by software.                                                                                                                       | Asynchronous                |

| 15       | SysTick                   | Configurable | System tick timer has fired.                                                                                                                                                                | Asynchronous                |

| 16-47    | External Interrupt        | Configurable | Asserted from outside the processor or pended by software.                                                                                                                                  | Asynchronous                |

#### Servicing an Exception

- Push 8 Registers (xPSR, ReturnAddress(), R0, R1, R2, R3, R12, and LR) on Selected Stack

- Read Vector from Appropriate Vector Table Entry

- Example: (0x0) + (exception\_number \*4)

- Only after ALL EIGHT Registers in Previous Step Are Pushed onto Stack

- On Reset Only, Update SP\_main from First Entry in the Vector Table

- Other Exceptions Do Not Modify SP\_main this Way

- Update PC with Vector Table Read Location

- No Other Late-arriving Exceptions Can Be Processed until the First Instruction of This Exception Starts to Execute

- Set LR to EXC\_RETURN to Exit from Exception

#### **Cortex-M1 Instruction Set**

Actel Corporation © 2009

## **ARM Instructions**

- 32-bit Instruction Length

- 36 Instruction Formats

- ALL ARM Instructions Can Be Conditional!

| Cond | 0 | 0 | J. | C | )pc | od  | le | S |     | Rn  |   |     | Ro   | I   |      |     |      |     | Op  | ber | an  | d 2 |        | Data Processing /<br>PSR Transfer           |

|------|---|---|----|---|-----|-----|----|---|-----|-----|---|-----|------|-----|------|-----|------|-----|-----|-----|-----|-----|--------|---------------------------------------------|

| Cond | D | 0 | 0  | 0 | 0   | 0   | A  | s |     | Rd  |   |     | Rr   | i i | 1    | 1   | Rs   |     | 1   | 0   | 0   | 1   | Rm     | Multiply                                    |

| Cond | Q | 0 | 0  | 0 | 1   | υ   | A  | s | F   | dHi | 2 |     | RdL  | .0  |      | ł   | Rn   |     | 1   | 0   | 0   | 1   | Rm     | Multiply Long                               |

| Cond | 0 | 0 | 0  | 1 | 0   | в   | 0  | 0 |     | Rn  |   |     | Ro   | 1   | 0    | 0   | 0    | 0   | 1   | 0   | 0   | 1   | Rm     | Single Data Swap                            |

| Cond | 0 | 0 | 0  | 1 | 0   | 0   | 1  | 0 | 1 1 | 1   | 1 | 1   | 1    | 1 1 | 1    | 1   | 1    | 1   | 0   | 0   | 0   | 1   | Rn     | Branch and Exchange                         |

| Cond | 0 | 0 | 0  | Ρ | U   | 0   | w  | L |     | Rn  |   |     | Ro   | 1   | 0    | 0   | 0    | 0   | 1   | s   | н   | 1   | Rm     | Halfword Data Transfer.<br>register offset  |

| Cond | 0 | þ | 0  | Ρ | U   | 1   | w  | L |     | Rn  |   | 0   | Ro   | 1   |      | (   | Offs | et  | 1   | S   | Н   | 1   | Offset | Halfword Data Transfer.<br>immediate offset |

| Cond | 0 | 1 | 1  | Ρ | U   | в   | w  | L |     | Rn  |   |     | Ro   | 1   |      |     |      |     | -   | Of  | fse | t   |        | Single Data Transfer                        |

| Cond | 0 | 1 | 1  |   |     |     |    |   |     |     |   |     |      |     |      |     |      |     |     |     |     | 1   |        | Undefined                                   |

| Cond | 1 | Ó | 0  | Ρ | U   | s   | w  | L |     | Rn  |   |     |      |     |      |     | Re   | gis | ter | Lis | st  |     |        | Block Data Transfer                         |

| Cond | 1 | 0 | 1  | L |     |     |    |   |     |     |   | C.  |      | 0   | ffse | t   |      |     |     |     |     |     |        | Branch                                      |

| Cond | 1 | 1 | 0  | Ρ | U   | N   | W  | L |     | Rn  |   |     | CR   | d   |      | C   | P#   |     |     |     | ß   | Off | set    | Coprocessor Data<br>Transfer                |

| Cond | 1 | 1 | 1  | 0 | C   | ;P  | Op | c | 0   | Rn  | l | ĉ   | CR   | d   | 0    | C   | ;P#  |     |     | CF  | ,   | 0   | CRm    | Coprocessor Data<br>Operation               |

| Cond | t | 1 | 1  | 0 | CF  | • C | pc | L | 0   | Rn  | ŝ |     | Ro   | 1   |      | C   | P#   |     | t   | CF  | •   | 1   | CRm    | Coprocessor Register<br>Transfer            |

| Cond | 1 | 1 | 1  | 1 |     | -   | 3  |   | 2   |     | _ | Igi | nore | d b | y pi | TO( | es   | sor | -   | -   | _   | 2   |        | Software Interrupt                          |

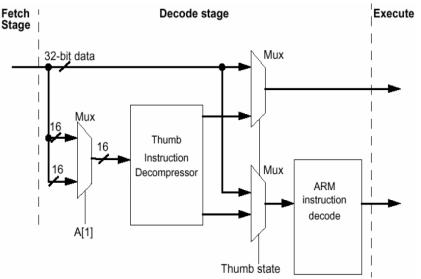

#### **Thumb Instructions**

- 16-bit Instruction Length

- Maps 32-bit Instructions into 16-bit Instructions

- Thumb Instructions Are Most-often-used 32-bit Instructions

- Thumb Instructions Transparently Expand in Real Time to Full 32-bit ARM Instructions

Fetch Decode stage

- Thumb-instruction Decoder Placed in Pipeline

- Change to Thumb Mode Effected by Changing State of Multiplexers Feeding Instruction Decoders and Data Bus

## **Thumb Instruction Set**

- Instruction Word Length Shrunk to 16-bits

- Some Functionality Is Not Available

- 19 Different Thumb Instruction Formats

- Instructions Have their Own Syntax

- Each Instruction Has Native ARM Instruction Counterpart

- Only ONE Conditional Instruction!

| •          |    | 15 | 14 | 13 | 12 | 11 | 10 | 9  | 8    | 7    | 6 5  | 543      | 2 1 0 |                                            |

|------------|----|----|----|----|----|----|----|----|------|------|------|----------|-------|--------------------------------------------|

|            | 1  | 0  | 0  | 0  | C  | )p |    | 0  | ffse | t5   |      | Rs       | Rd    | Move shifted register                      |

| ot         | 2  | 0  | 0  | 0  | 1  | 1  | Ι  | Op | Rn   | offs | set3 | Rs       | Rd    | Add/subtract                               |

|            | 3  | 0  | 0  | 1  | C  | )p |    | Rd |      |      |      | Offset8  |       | Move/compare/add<br>/subtract immediate    |

| uction     | 4  | 0  | 1  | 0  | 0  | 0  | 0  |    | 0    | р    |      | Rs       | Rd    | ALU operations                             |

|            | 5  | 0  | 1  | 0  | 0  | 0  | 1  | o  | р    | H1   | H2   | Rs/Hs    | Rd/Hd | Hi register operations<br>/branch exchange |

|            | 6  | 0  | 1  | 0  | 0  | 1  |    | Rd |      |      |      | Word8    |       | PC-relative load                           |

| Dwn        | 7  | 0  | 1  | 0  | 1  | L  | в  | 0  |      | Ro   |      | Rb       | Rd    | Load/store with register<br>offset         |

|            | 8  | 0  | 1  | 0  | 1  | н  | s  | 1  |      | Ro   |      | Rb       | Rd    | Load/store sign-extended<br>byte/halfword  |

| ive        | 9  | 0  | 1  | 1  | в  | L  |    | 0  | ffse | t5   |      | Rb       | Rd    | Load/store with immediate<br>offset        |

| part       | 10 | 1  | 0  | 0  | 0  | L  |    | 0  | ffse | t5   |      | Rb       | Rd    | Load/store halfword                        |

|            | 11 | 1  | 0  | 0  | 1  | L  |    | Rd |      |      |      | Word8    |       | SP-relative load/store                     |

|            | 12 | 1  | 0  | 1  | 0  | SP |    | Rd |      |      |      | Word8    |       | Load address                               |

|            | 13 | 1  | 0  | 1  | 1  | 0  | 0  | 0  | 0    | s    |      | SWord    | d7    | Add offset to stack pointer                |

|            | 14 | 1  | 0  | 1  | 1  | L  | 1  | 0  | R    |      |      | Rlist    |       | Push/pop registers                         |

|            | 15 | 1  | 1  | 0  | 0  | L  |    | Rh |      |      |      | Rlist    |       | Multiple load/store                        |

| <b>→</b> < | 16 | 1  | 1  | 0  | 1  |    | Со | nd |      |      |      | Soffset8 | 1     | Conditional branch                         |

|            | 17 | 1  | 1  | 0  | 1  | 1  | 1  | 1  | 1    |      |      | Value8   |       | Software Interrupt                         |

|            | 18 | 1  | 1  | 1  | 0  | 0  |    |    |      |      | Of   | fset11   |       | Unconditional branch                       |

|            | 19 | 1  | 1  | 1  | 1  | н  |    |    |      |      | C    | )ffset   |       | Long branch with link                      |

|            |    |    |    | _  |    |    |    |    |      |      |      |          |       |                                            |

Actel Corporation © 2009

7 6 5 4

8

14 13 12 11

## ARM Code vs. Thumb Code Comparison

#### Performance

- 32-bit Memory

- ARM Code Is 40% Faster than Thumb Code

- 16-bit Memory

- Thumb Code Is 45% Faster than ARM Code

- Code

- Thumb Code Requires 65% 70% of the Space of ARM Code

- Thumb Code Uses 40% More Instructions than ARM Code

- Thumb Code Has Higher Density and Better Performance with 16-bit Memory

- ARM Code Has Better Performance with 32-bit Memory

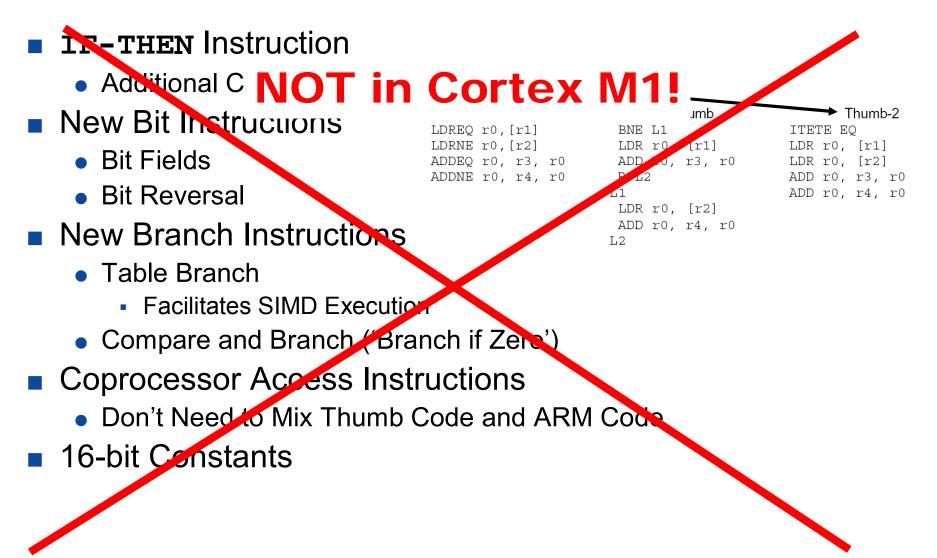

## What's Thumb-2?

- Remember 16-bit Thumb Instructions Are Mapped into 32bit ARM Instructions for Execution

- Some ARM Special Features Were NOT Supported in Thumb

- ARM Wanted to Eliminate ...

- ... Tradeoff of Size vs. Speed

- ... Confusion about Which Instruction Set to Select

- Thumb-2 Combines 16- and 32-bit Instructions in a Single Instruction Set

- Allows Mixing of Instructions without Mode Switching

- Halfword Pairs of Instructions Are Inserted in Thumb Instruction Stream

- Thumb-2 Features

- Mostly 16-bit Instructions

- 5% Better Code Density than Existing Thumb Code

- 2-3% Faster than Thumb Code

- Code Density 74% of ARM Code Density

- Code Performance 98% of ARM Code Performance

Introduction to Cortex-M1 v1.8

## **Thumb-2 Instruction Set**

Changes vis-à-vis Thumb

# Thumb-2 32-bit Instructions

#### ARM-like

- Data Proce: Most Not Supported in

- DSP and M

- Cortex-M1!

- Load and Store menuctions

- Branch Instructions

- System Control BYJ, RFE, SRS, etc

- Coprocessor (VFP, MOVE<sup>™</sup>, etc.)

- New

- Bit-field Insert/Extract/Clear BFL, {S|U}BFX, BFC

- Bit Reverse RBIT

- 16-bit Immediate instructions MOVW, MOVH

- Table Branch TB{B|H} [Rbase, Rinder

- Additional Memory System Hints PLD

# Cortex-M1 Instruction Set

- Branch instructions (6)

- B Conditional Branch, Unconditional, with Link...

- BX Branch and Exchange instruction set.

- Data processing instructions

- ADD, CMP, MOV, MULT, SUB...

- Load and store register instructions

- Load and store multiple instructions

- Two instructions, LDMIA & STMIA, to support block copy

- Exception generating instructions

- Software Interrupt (SWI) instruction used to cause a SWI exception to occur

- Main mechanism in the Thumb instruction set by which User mode code can make calls to privileged Operating System code

## **Cortex-M1 Instruction Set**

#### 16-bit Instructions

- CPS Change Processor State

- Enables/Disables Interrupts

- **NOP** No Operation

- Certain New Thumb-2 Instructions Are Ignored (IF-THEN)

- SEV Send Event

- Event Signaled to All CPUs in Multiprocessor System

- WFE Wait for Event

- Suspend Execution until Reset, Exception, etc. Occurs

- wfi Wait for Interrupt

- Suspend Execution until Interrupt Occurs

- YIELD Yield (Multithreaded Systems)

- Software Can Indicate that Task Can Be Swapped Out

#### Actel's Cortex-M1

Actel Corporation © 2009

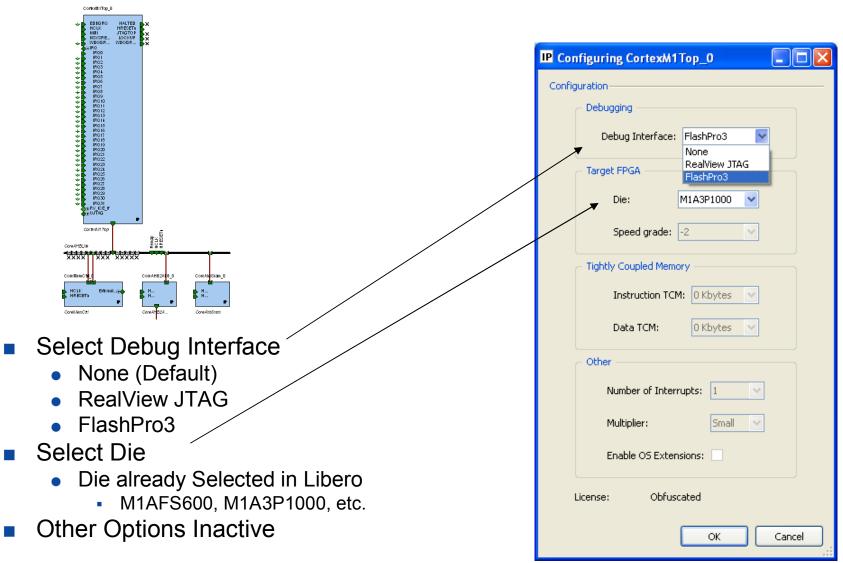

#### Cortex-M1 Configurable Options

#### • Full Range of Configurable Options Will Be Available ...

| Feature         | Configurable Option                                       |

|-----------------|-----------------------------------------------------------|

| Debug           | Debug Functionality Can Be Included or Excluded           |

| Interrupts      | 1, 4, 8, 16 or 32 Interrupts (0 Interrupts Not Supported) |

| Instruction TCM | 0KB (None), 1KB, 2KB, and Powers of 2 to 1MB              |

| Data TCM        | 0KB (None), 1KB, 2KB, and Powers of 2 to 1MB              |

| Multiplier      | Normal (3-cycle Execution) or Small (33 Cycles)           |

| OS Extensions   | Present or Absent                                         |

| Endianness      | Little-endian or Big-endian (BE8)                         |

- Actel Will Deliver Restricted Range of Configurations

- Fixed, Black-box Implementations with Predefined Configurations (Similar to CoreMP7)

## **Cortex-M1 Configurations**

#### Current Release – v2.6

| Variant                                                                                                                 | Configuration                                                                                                                  |

|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| M1AFSxxxxDebug<br>M1A3PxxxxDebug<br>M1A3PExxxxDebug<br>M1A3PLxxxxDebug<br>M1AGLxxxxDebug<br>M1AGLExxxxDebug             | Debug Support (2 breakpoints, 1 watchpoint)<br>No TCMs, Small Multiplier, 1 Interrupt, No OS Extensions,<br>Little-endian Only |

| M1AFSxxxxNodebug<br>M1A3PxxxxNodebug<br>M1A3PExxxxNodebug<br>M1A3PLxxxxNodebug<br>M1AGLxxxxNodebug<br>M1AGLExxxxNodebug | No Debug Capability<br>No TCMs, Small Multiplier, 1 Interrupt, No OS extensions,<br>Little-endian Only                         |

#### Future Releases

• More Variants, More Devices

## Supported Devices and Availability

| M1-enabled Devices | 250          | 400     | 600          | 1000         | E1500        | E3000        |

|--------------------|--------------|---------|--------------|--------------|--------------|--------------|

| M1 IGLOO           | $\checkmark$ |         | $\checkmark$ | $\checkmark$ |              | $\checkmark$ |

| M1 ProASIC3        | $\checkmark$ | Planned | $\checkmark$ | $\checkmark$ | $\checkmark$ | $\checkmark$ |

| M1 ProASIC3L       |              |         | $\checkmark$ | $\checkmark$ |              | Planned      |

| M1 Fusion          | $\checkmark$ |         | $\checkmark$ |              | $\checkmark$ |              |

Information updated March 2009

- ARM Cortex-M1 processor Actel M1 devices

- One user selectable option: with or without debug.

- Pre-configured settings

- 0K ITCM, 0K DTCM, small multiplier, little-endian,

- No OS extensions, and 1 interrupt

- Fully Configured M1AFS1500 2009

- 8kB ITCM, 4kB DTCM, 16 interrupts, OS extensions, fast multiplier, little-endian.

- Contains upgraded BFM

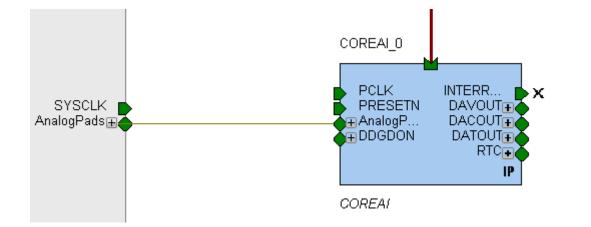

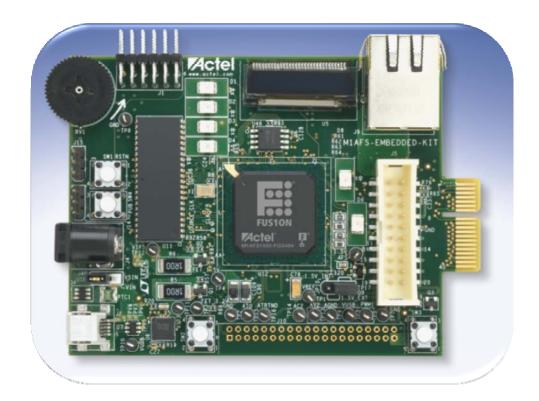

## **Optimized Cortex-M1 in M1 Fusion**

- Optimized Firm-macro Implementation

- Optimized for M1 Fusion Devices

- Porous Implementation Placed in FPGA Fabric by Actel

- Simplified Routing of Useradded IP

- Enables Rapid Design Development

- Cortex-M1 Black Box

- M1 Functionality

- User Can Add IP and Program into M1 Fusion

- Timing Shell and BFM Included

#### Cortex-M1 Utilization and Performance

| Device       | Variant  |                 | v2.6 |             |

|--------------|----------|-----------------|------|-------------|

| Device       | variant  | Frequency (MHz) | Area | Utilization |

| M1AFS250-2   | No-debug | 62.26           | 4353 | 70.85%      |

| M1AFS600-2   | No-debug | 60.96           | 4353 | 31.49%      |

| MIAF5600-2   | Debug    | 55.14           | 7090 | \$1 6006    |

| M1AFS1500-2  | No-debug | 62.69           | 4353 | 11.34%      |

| MIAF51500-2  | Debug    | 56.39           | 7282 | 18.96%      |

| M1AGL250V2   | No-debug | 25.56           | 4353 | 70.85%      |

| M1AGL250V5   | No-debug | 43.04           | 4353 | 70.85%      |

| M1AGL600V2   | No-debug | 25.46           | 4353 | 31.49%      |

| MIAGL600V2   | Debug    | 24.40           | 7282 | 52.68%      |

| M1AGL600V5   | No-debug | 40.23           | 4353 | 31.49%      |

| MIAGL600V5   | Debug    | 39.90           | 7282 | 52.68%      |

| M1AGL1000V2  | No-debug | 24.74           | 4353 | 17.71%      |

| MIAGE1000v2  | Debug    | 23.53           | 7282 | 29.63%      |

| M1AGL1000V5  | No-debug | 40.87           | 4353 | 17.71%      |

| MIAGL1000V5  | Debug    | 40.57           | 7282 | 29.63%      |

| M1AGLE3000V2 | No-debug | 24.89           | 4353 | 5.78%       |

| WIAGLE3000v2 | Debug    | 24.54           | 7282 | 9.68%       |

| M1AGLE3000V5 | No-debug | 36.89           | 4353 | 5.78%       |

| MIAGLE3000V5 | Debug    | 38.05           | 7282 | 9.68%       |

| M1A3P250-2   | No-debug | 62.46           | 4353 | 70.85%      |

| M1A3P600-2   | No-debug | 62.63           | 4353 | 31.49%      |

| MIASP000-2   | Debug    | 59.24           | 7282 | 52.68%      |

| M1A3P1000-2  | No-debug | 62.18           | 4353 | 17.71%      |

# Cortex-M1 Summary

- New FPGA-targeted Processor from ARM

- Small and Fast

- 4300 Tiles, 62 MHz without Debug

- Some Nice Features

- Thumb-2 Instruction Set

- Mostly 16-bit Instructions Good Code Density)

- Good Interrupt Support (Closely-coupled NVIC)

- Easier to Program than CoreMP7

- Porting CoreMP7 Software Fairly Straightforward

- V2.6 Available Now

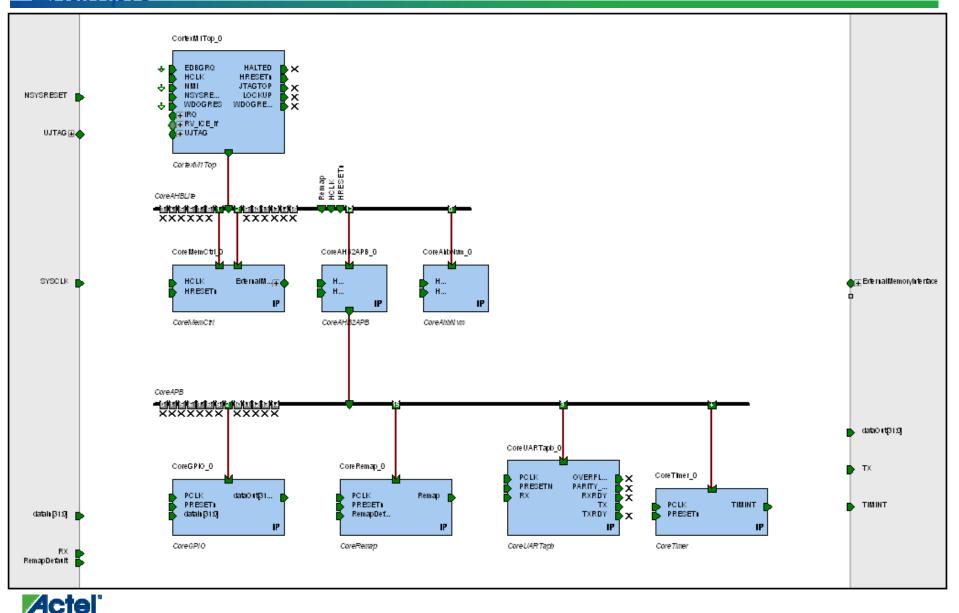

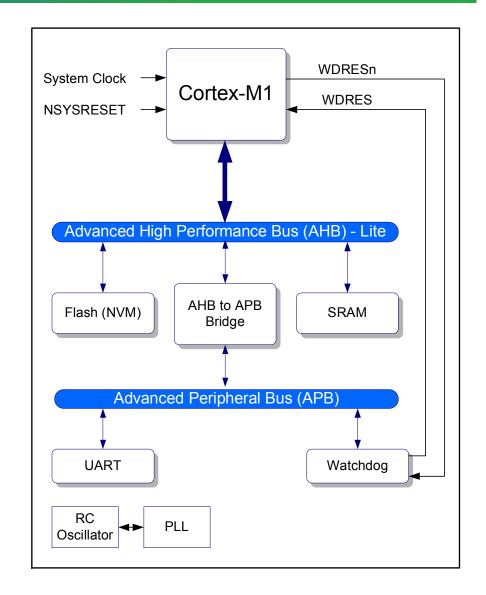

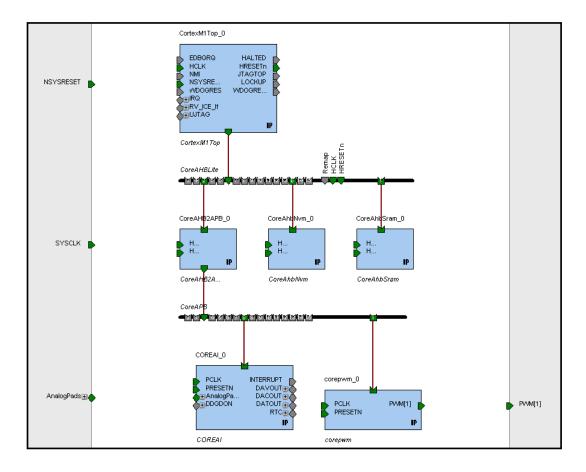

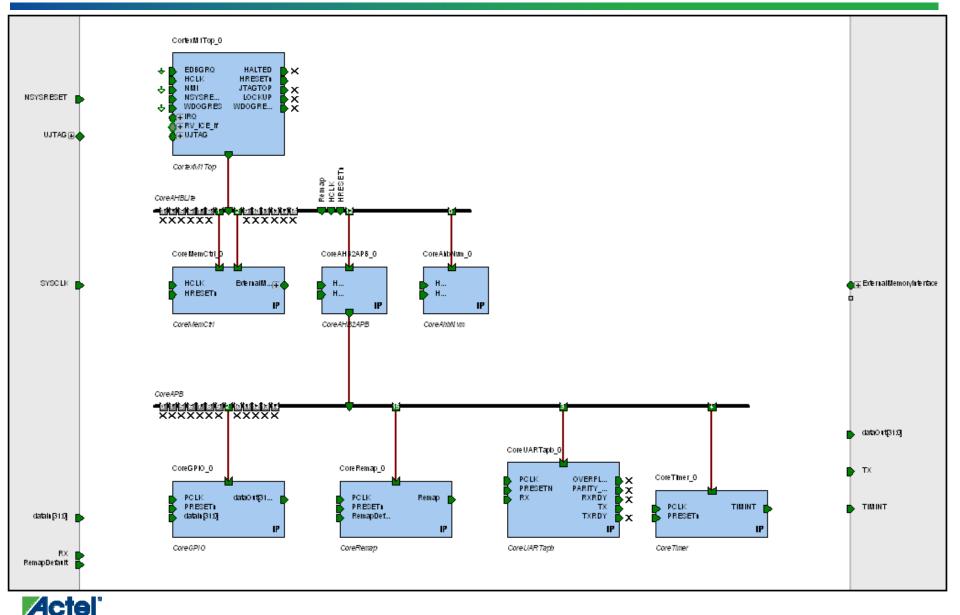

# System-on-Chip and SmartDesign Introduction to AMBA

# System-on-Chip and SmartDesign

- AMBA Bus Architectures

- SmartDesign and IP Cores

- Using SmartDesign

- IP Database

- Testing

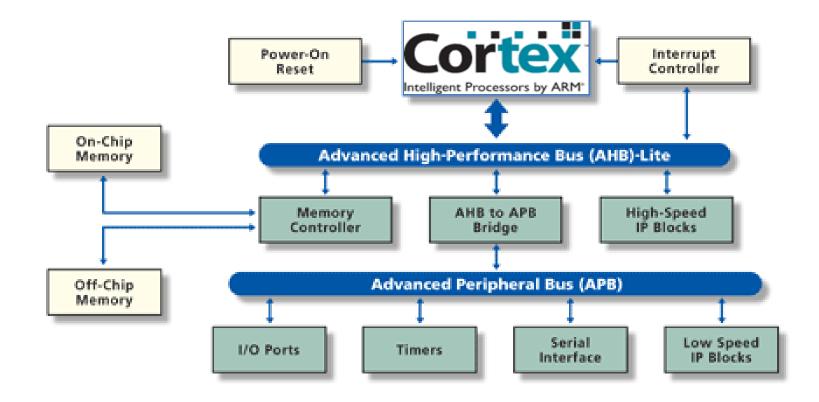

## **AMBA Bus Architectures**

Actel Corporation © 2009

# **Bus: definition**

- Set of wires connected to many bus actors

- Wires are grouped in functional groups:

- Address: bus actor identifiers

- Data

- Control: physical support for the protocol

- Wires are shared

- Access protocols are required

- Control logic + control wires embody the protocol

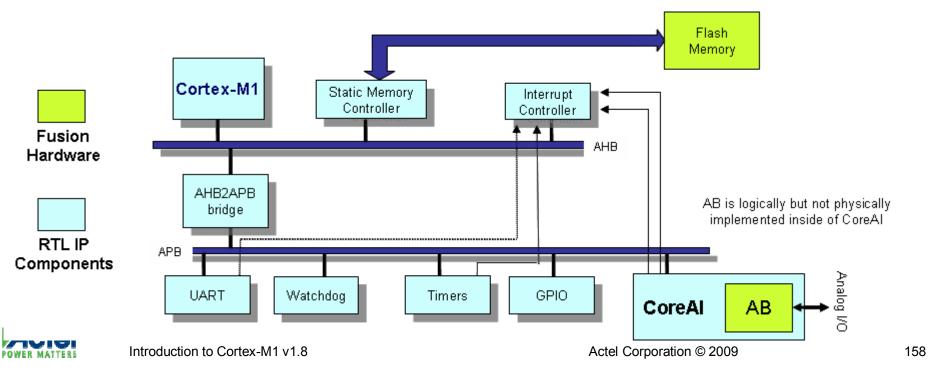

# What Is AMBA?

- Open-standard, On-chip Bus Specification

- Interconnection & Management of SoC Functional Blocks

- Widely-adopted Protocol and Standard with ARM Processors

- Three distinct buses

- AHB (the Advanced High-performance Bus).

- High-performance system backbone bus.

- Multi-Master, Split Transactions, Burst Transfers and Other Modes

- Example Components Cortex-M1, CoreMP7, and Memory Controllers

- ASB (the Advanced System Bus).

- An alternative system bus.

- APB (the Advanced Peripheral Bus).

- Minimal power consumption.

- Reduced interface complexity.

- Example Components Watchdog and UART

- AHB & APB AMBA Protocols Supported by SmartDesign

- When Both AHB and APB Are Used in System, They Must Be Bridged (AHB2APB Bridge Provided)

# What Is AMBA?

- Three distinct buses

- AHB (the Advanced High-performance Bus).

- High-performance system backbone bus.

- ASB (the Advanced System Bus).

- An alternative system bus.

- APB (the Advanced Peripheral Bus).

- Minimal power consumption. Reduced interface complexity.

## AMBA Subsystem Block Diagram

"typical" AMBA system

## AMBA Subsystem Block Diagram

- First-generation system bus that evolved from ARM7TDMI bus protocol

- Supports pipelining, bursts, and multiple bus masters

- The four bus agents in ASB are:

- Arbiter: Implements a simple request/grant structure to support multiple bus masters

- Decoder: Centralized address decoder to determine which slave is responsible for servicing a bus transaction

- Master: Initiates reads and writes on the bus

- Slave: Responds to master initiated reads and writes

- Drawbacks

- Use of double-edging clock

- Bi-directional data bus

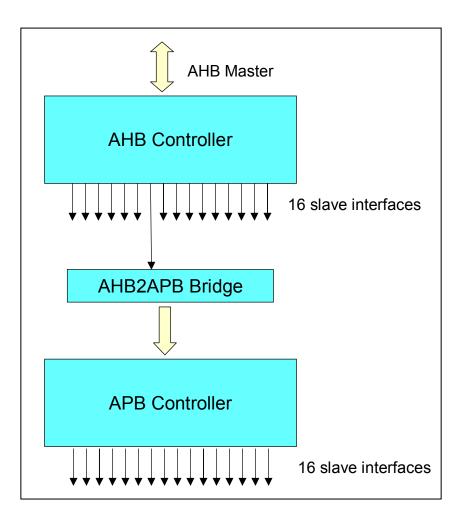

# AMBA Bus Fabric

- Bus Fabric Components

- AHB Controller

- AHB to APB Bridge

- APB Controller

- AHB and APB Controllers Incorporate All Bus Switching and Decoding Logic

- Two AHB Controller Configurations

- Single Master (AHB-Lite)

- Multi-Master (3 Masters)

- Supports Full AHB Slaves

# AHB Bus

#### Features

- High Bandwidth

- No Maximum Clock Frequency Specified

- Designs up to 2 GHz!

- Burst Transfers

- Split Transactions

- Single-cycle Bus Master Handover

- Single-clock-edge Operation

- Non-tristate Implementation

- Support for Multiple Masters

- Bridging to APB Bus

# AHB Bus

#### Burst vs. Split

- Burst transaction

- Slave to increment (or decrement) address

- No need of sending many sequential addresses through bus

- Reduces power (computations at the slave)

- Split transaction

- When a master transaction can potentially take a long time (i.e. communicating with APB peripherals).

- To avoid holding the bus for many cycles

- Masters issues a request, then releases the bus, and waits for notification, which can come many cycles after.

#### AMBA Bus Interface Signals AHB Single-Master and AHB-Lite Buses

| Name                         | Source           | Description                                                                                                                                                                                                     |

|------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HCLK<br>Bus clock            | Clock source     | This clock times all bus transfers. All signal timings are related to the rising edge of <b>HCLK</b> .                                                                                                          |

| HRESETn<br>Reset             | Reset controller | The bus reset signal is active LOW and is used to reset the system and the bus. This is the only active LOW signal.                                                                                             |

| HADDR[31:0]<br>Address bus   | Master           | The 32-bit system address bus.                                                                                                                                                                                  |

| HTRANS[1:0]<br>Transfer type | Master           | Indicates the type of the current transfer, which can<br>be NONSEQUENTIAL, SEQUENTIAL, IDLE or<br>BUSY.                                                                                                         |

| HWRITE<br>Transfer direction | Master           | When HIGH this signal indicates a write transfer<br>and when LOW a read transfer.                                                                                                                               |

| HSIZE[2:0]<br>Transfer size  | Master           | Indicates the size of the transfer, which is typically<br>byte (8-bit), halfword (16-bit) or word (32-bit). The<br>protocol allows for larger transfer sizes up to a<br>maximum of 1024 bits.<br>Source: ARM In |

### AMBA Bus Interface Signals AHB Single-Master and AHB-Lite Buses

| HBURST[2:0]<br>Burst type        | Master | Indicates if the transfer forms part of a burst. Four,<br>eight and sixteen beat bursts are supported and the<br>burst may be either incrementing or wrapping.                                                                                                                                                                                                                                                                                                                                       |

|----------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HPROT[3:0]<br>Protection control | Master | The protection control signals provide additional<br>information about a bus access and are primarily<br>intended for use by any module that wishes to<br>implement some level of protection.<br>The signals indicate if the transfer is an opcode<br>fetch or data access, as well as if the transfer is a<br>privileged mode access or user mode access. For<br>bus masters with a memory management unit these<br>signals also indicate whether the current access is<br>cacheable or bufferable. |

## AMBA Bus Interface Signals AHB Single-Master and AHB-Lite Buses

| Name                            | Source  | Description                                                                                                                                                                                                                                          |

|---------------------------------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HWDATA[31:0]<br>Write data bus  | Master  | The write data bus is used to transfer data from the<br>master to the bus slaves during write operations. A<br>minimum data bus width of 32 bits is<br>recommended. However, this may easily be<br>extended to allow for higher bandwidth operation. |

| HSELx<br>Slave select           | Decoder | Each AHB slave has its own slave select signal and<br>this signal indicates that the current transfer is<br>intended for the selected slave. This signal is<br>simply a combinatorial decode of the address bus.                                     |

| HRDATA[31:0]<br>Read data bus   | Slave   | The read data bus is used to transfer data from bus<br>slaves to the bus master during read operations. A<br>minimum data bus width of 32 bits is<br>recommended. However, this may easily be<br>extended to allow for higher bandwidth operation.   |

| HREADY<br>Transfer done         | Slave   | When HIGH the <b>HREADY</b> signal indicates that a<br>transfer has finished on the bus. This signal may be<br>driven LOW to extend a transfer.<br>Note: Slaves on the bus require <b>HREADY</b> as both<br>an input and an output signal.           |

| HRESP[1:0]<br>Transfer response | Slave   | The transfer response provides additional<br>information on the status of a transfer.<br>Four different responses are provided, OKAY,<br>ERROR, RETRY and SPLIT.                                                                                     |

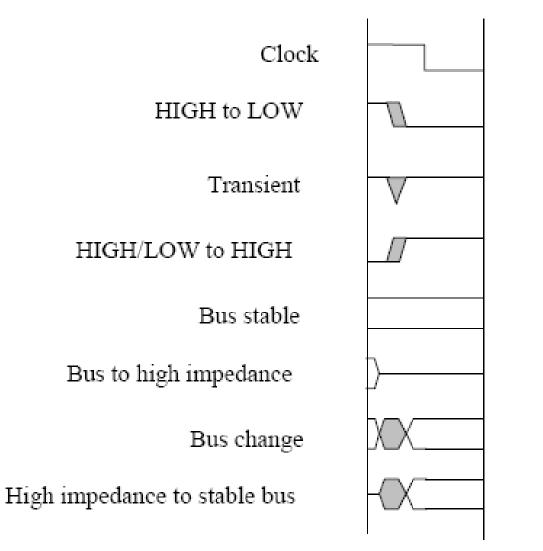

# **Timing Diagram Conventions**

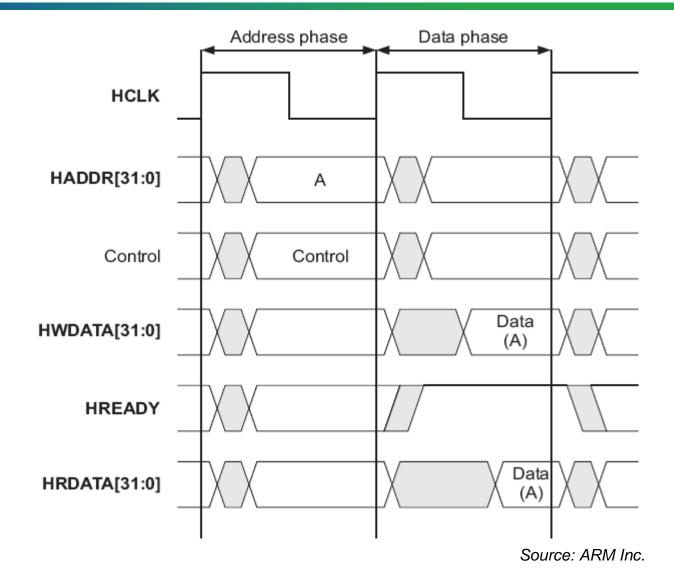

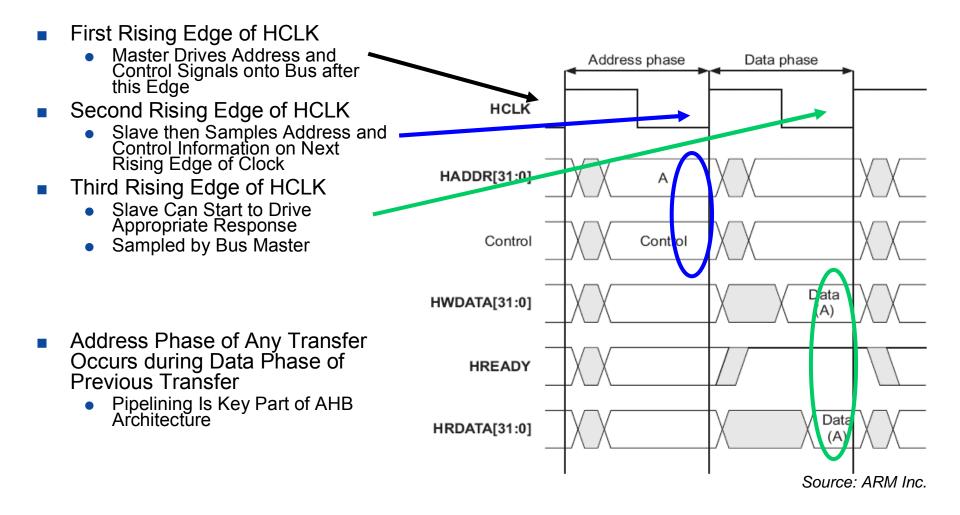

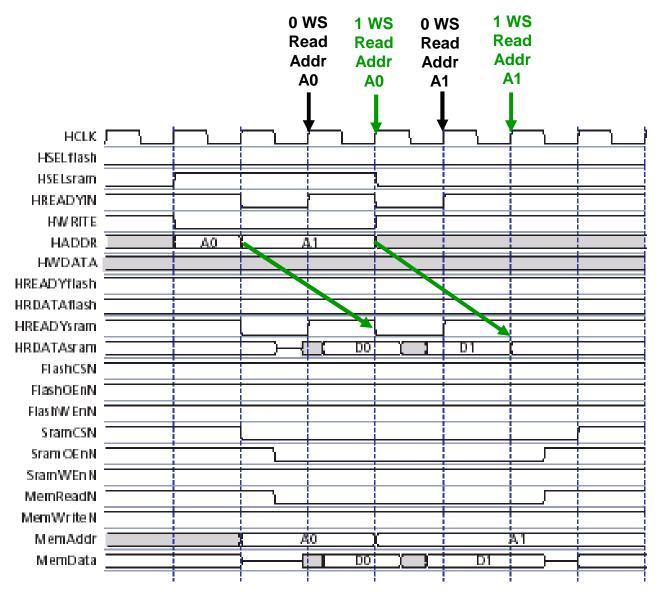

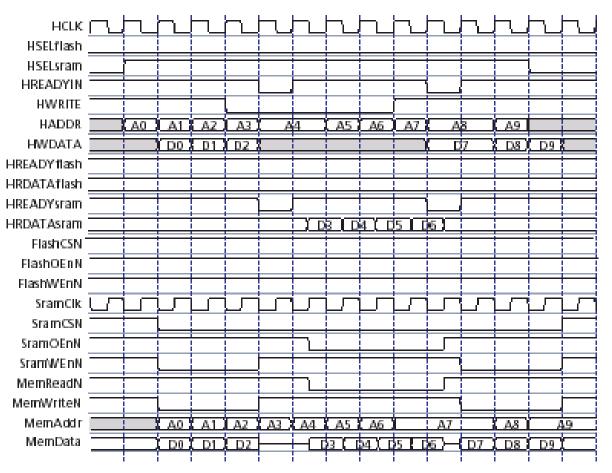

# Simple AHB Transfer

# **AHB** Transfer

#### No Wait States

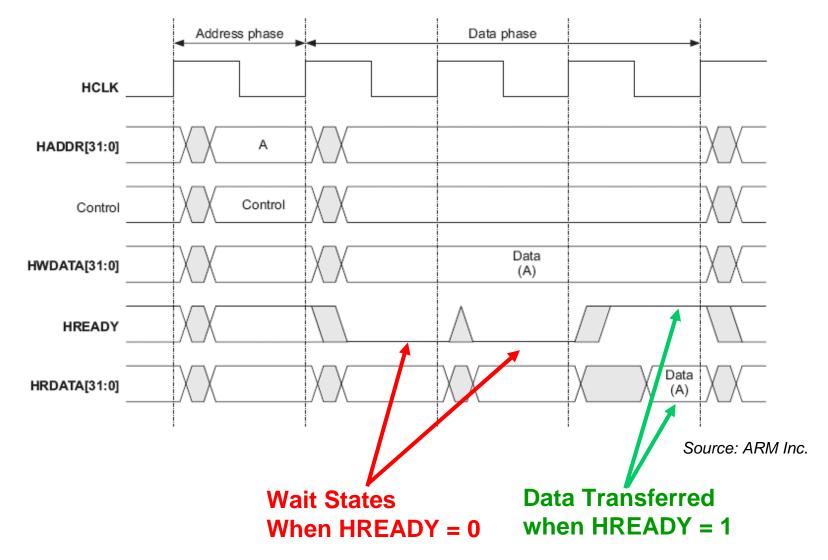

## AHB Transfer Wait States

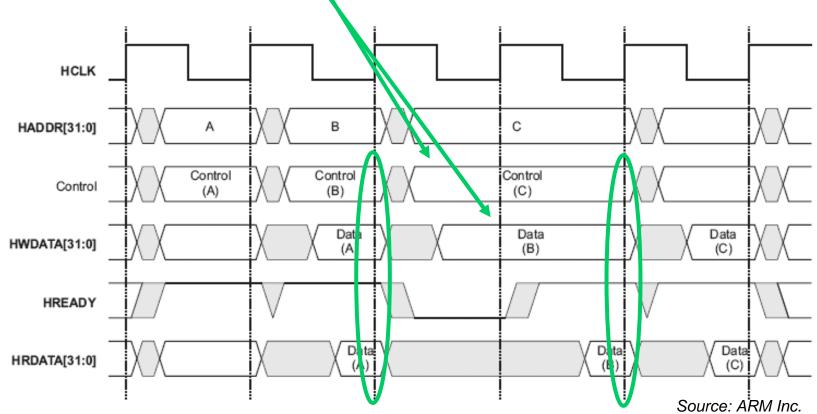

# AHB Transfer

**Pipelined Operations**

Control of Next Transfer Overlaps Data from Previous Transfer

## AHB Bus Burst Signal Encoding

| HBURST[2:0] | Туре   | Description                              |

|-------------|--------|------------------------------------------|

| 000         | SINGLE | Single transfer                          |

| 001         | INCR   | Incrementing burst of unspecified length |

| 010         | WRAP4  | 4-beat wrapping burst                    |

| 011         | INCR4  | 4-beat incrementing burst                |

| 100         | WRAP8  | 8-beat wrapping burst                    |

| 101         | INCR8  | 8-beat incrementing burst                |

| 110         | WRAP16 | 16-beat wrapping burst                   |

| 111         | INCR16 | 16-beat incrementing burst               |

- Note that Transfer Size Can Be Larger than 16

- Source: ARM Inc.

• INCR Indicates Unspecified Length

## AHB Bus Transfer Type Encoding

| HTRANS[1:0]                                        | Туре          | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| oo<br>Granted & u                                  | IDLE<br>nused | Indicates that no data transfer is required. The IDLE transfer type is used when a bus master is granted the bus, but does not wish to perform a data transfer. Slaves must always provide a zero wait state OKAY response to IDLE transfers and the transfer should be ignored by the slave.                                                                                                                                                                                                                                                               |

| 01<br>Locks the bu<br>but no trans<br>within a bur | fer           | The BUSY transfer type allows bus masters to insert IDLE cycles in the middle of bursts<br>of transfers. This transfer type indicates that the bus master is continuing with a burst of<br>transfers, but the next transfer cannot take place immediately. When a master uses the<br>BUSY transfer type the address and control signals must reflect the next transfer in the<br>burst.<br>The transfer should be ignored by the slave. Slaves must always provide a zero wait state<br>OKAY response, in the same way that they respond to IDLE transfers. |

| 10<br>Starts a Burs<br>single transf               |               | Indicates the first transfer of a burst or a single transfer. The address and control signals<br>are unrelated to the previous transfer.<br>Single transfers on the bus are treated as bursts of one and therefore the transfer type is<br>NONSEQUENTIAL.                                                                                                                                                                                                                                                                                                   |

| 11<br>Continues a                                  | seq<br>burst  | The remaining transfers in a burst are SEQUENTIAL and the address is related to the previous transfer. The control information is identical to the previous transfer. The address is equal to the address of the previous transfer plus the size (in bytes). In the case of a wrapping burst the address of the transfer wraps at the address boundary equal to the size (in bytes) multiplied by the number of beats in the transfer (either 4, 8 or 16).                                                                                                  |

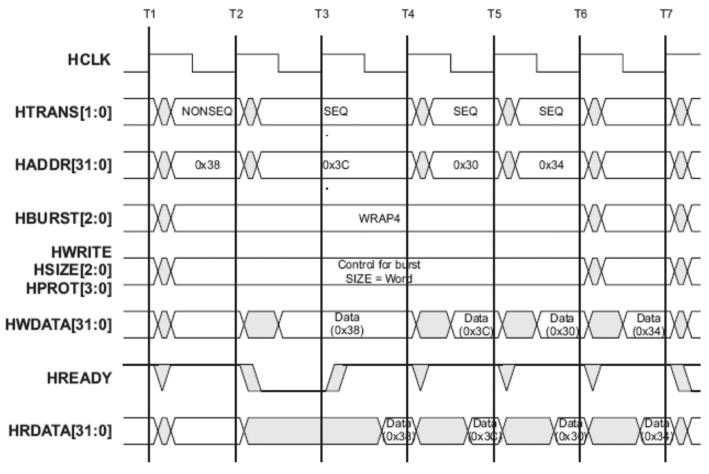

#### AHB Bus Four-beat Wrapping Burst

Sequential Addresses 38, 3C, 30, 34

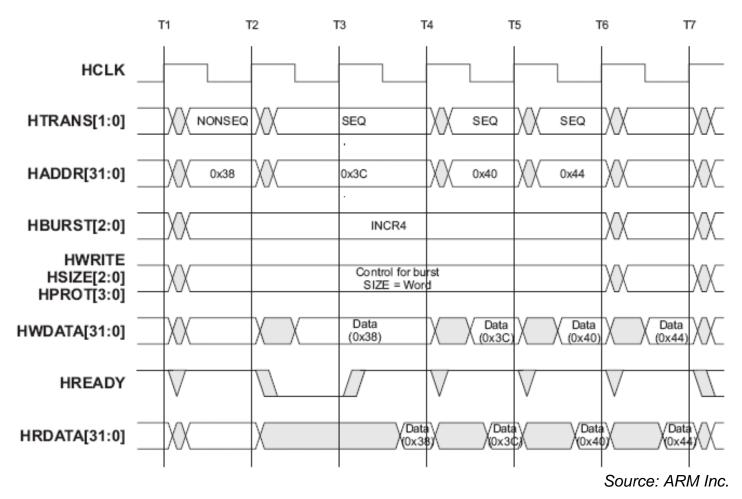

#### AHB Bus Four-beat Incrementing Burst

Sequential Addresses 38, 3C, 40, 44

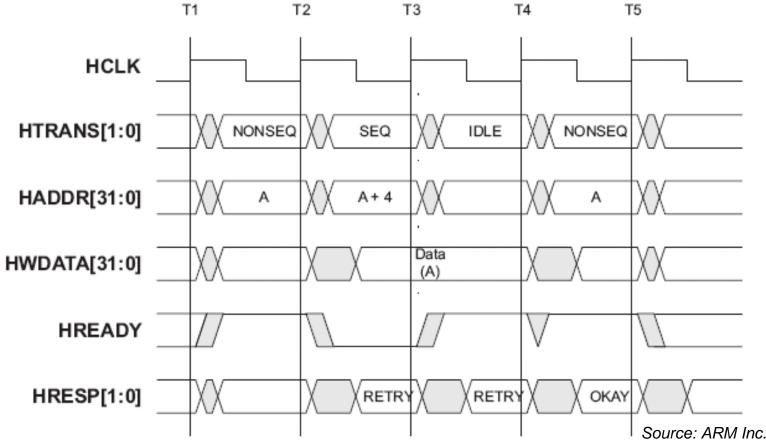

## AHB Bus

#### Transfer with Slave Retry Response

- Slave Indicates Response on HRESP(1:0)

- Can Be OK, ERROR, RETRY, or SPLIT

## AHB Bus

#### SPLIT vs. RETRY Responses

- SPLIT and RETRY Responses BOTH Allow ...

- ... Slaves to Release Bus when They Cannot Immediately Supply Data for Transfer

- ... Transfer to Finish on Bus and therefore Higher-priority Master Can Access Bus

- Difference between SPLIT and RETRY ... How Arbiter Allocates Bus after SPLIT or RETRY Has Occurred

- RETRY

- Arbiter Continues to Use Normal Priority Scheme

- Only Masters with Higher Priority Get Bus Access

- SPLIT

- Arbiter Adjusts Priority Scheme so that Any Other Master Requesting Bus Gets Access, even if Lower Priority

- Transfer Completion Requires Informing Arbiter when Slave Has Data Available

- Requires Extra Complexity in Both Slave and Arbiter, but Completely Frees Bus for Use by Other Masters

- Master Should Treat SPLIT and RETRY the SAME WAY

- Should Continue to Request Bus and Attempt the Transfer until Successful Completion or ERROR Response Termination

# **AMBA Bus Interface Signals**

#### AHB Multi-Master Bus

| Signal        | Function                                                                            |

|---------------|-------------------------------------------------------------------------------------|

| HBUSREQx      | Request from Master x to Use Bus                                                    |

| HLOCKx        | Indicates that Master Requires Locked Access to Bus                                 |

| HGRANTx       | Grant to Master x to Use Bus                                                        |

| HMASTx        | Indication from Arbiter that Master x Is Using Bus                                  |

| HSPLITx(15:0) | Indication from Slave x as to which Bus Masters May Re-Attempt<br>Split Transaction |

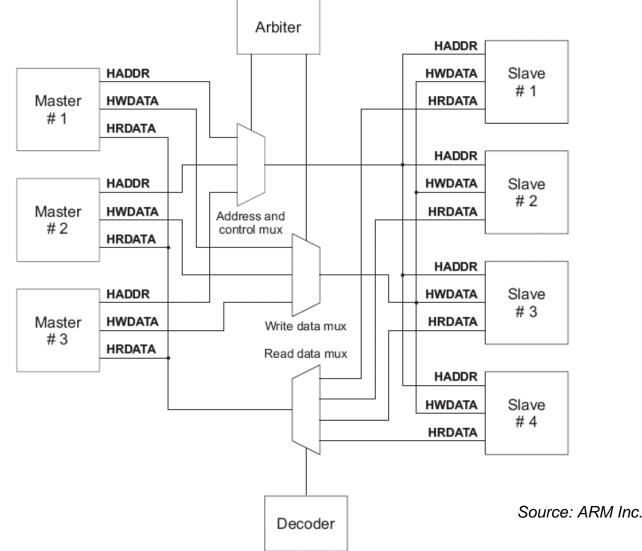

# AHB Multi-Master Subsystem

Three Masters, Four Slaves

- CoreAHB Uses Simple Priority Arbitration Scheme

- Master 3 Has Highest Priority

- Master 0 which Is Internal 'Dummy' Master Is Next-highest

- Master 2 Is Next

- Master 1 (Default) Is Lowest Priority

- This Is Normally Processor Master

- Master 0 Handles Several Situations

- Example Breaks Deadlock when Multiple Masters Are Locked in SPLIT Transactions

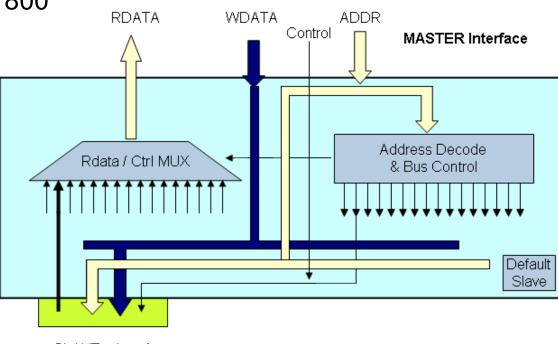

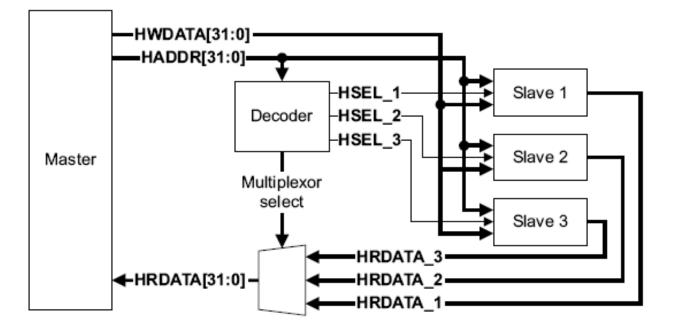

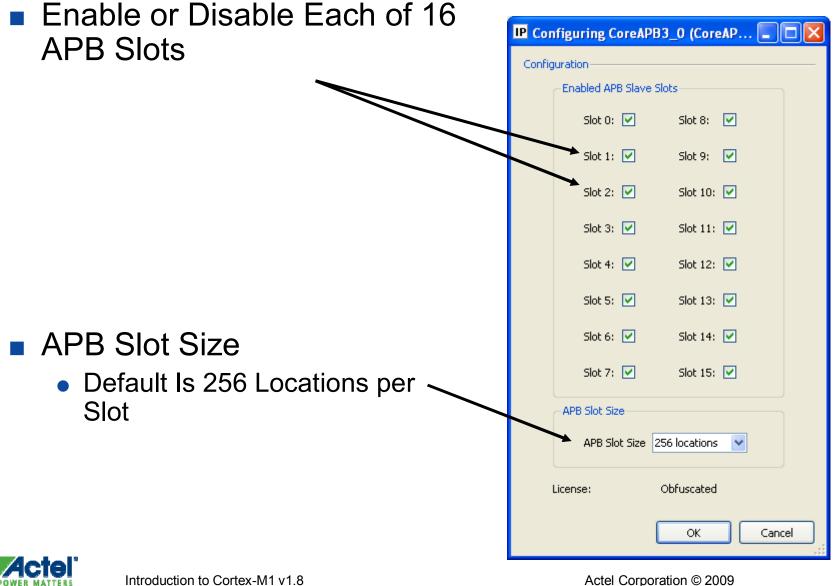

# CoreAHBLite

#### Single Master

- Single AHB Master Interface

- Default Interface for Cortex-M1

- 16 AHB Slave Interfaces

- Each Is Allocated Fixed Memory Location

- Two 'Standard' Locations

- Mem at 0

- Interrupt at Top of Memory

- Tile Count: 800

### AHB-Lite System Single Master, Three Slaves

CoreAHBLite Works Fine Here …

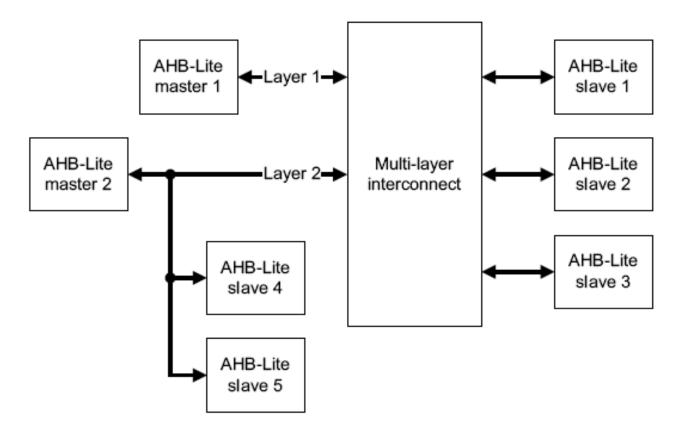

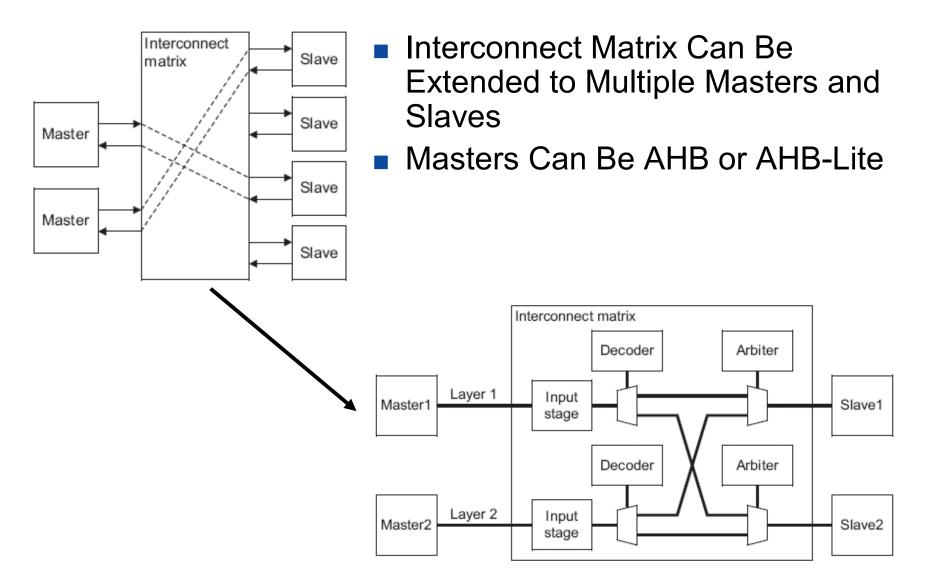

## AHB-Lite System TWO Masters, Multiple Slaves

BUT ... How Do We Implement THIS?

# AHB or AHB-Lite

#### Multi-Layer Interconnect Scheme

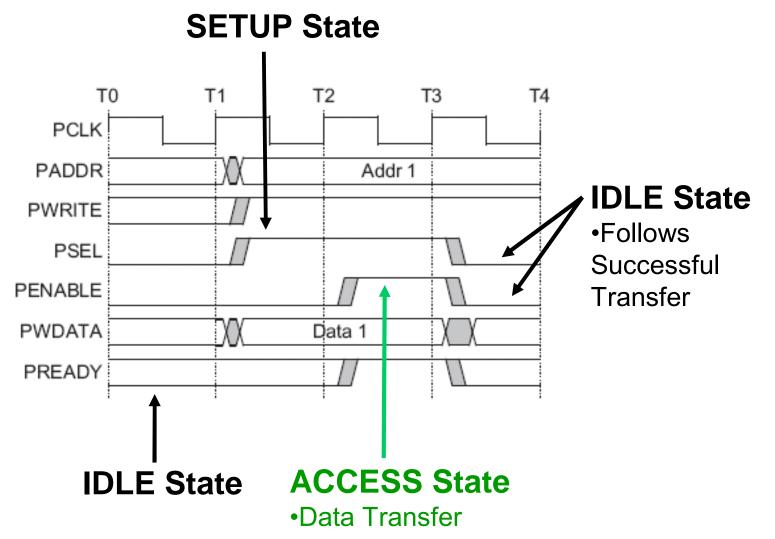

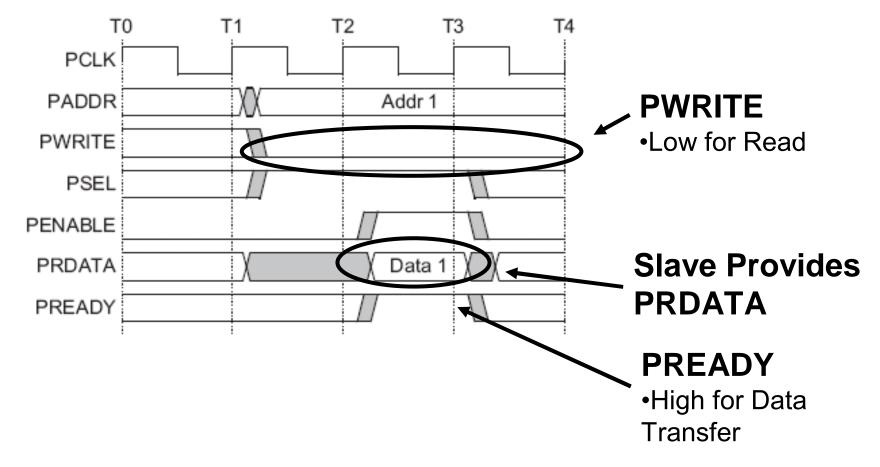

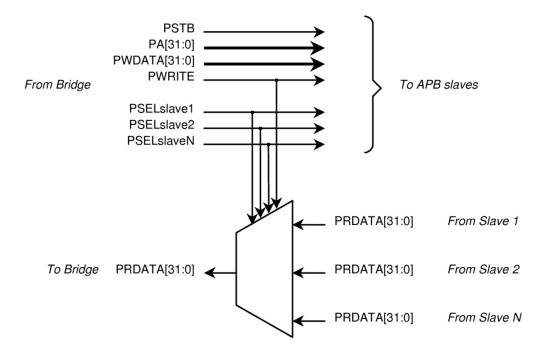

# AMBA Bus Interface Signals

| Signal      | Function                                                |

|-------------|---------------------------------------------------------|

| PCLK        | Bus Clock                                               |

| PRESETn     | ACTIVE-LOW Bus Reset                                    |

| PADDR(31:0) | System Address Bus (up to 32 Bits Wide)                 |

| PSELx       | Select Signal for APB Slave                             |

| PENABLE     | Indicates Second and Subsequent APB Transfer Cycles     |

| PWRITE      | Transfer Direction (1=Write, 0=Read)                    |

| PWDATA      | Write Data (up to 32 Bits from Master)                  |

| PRDATA      | Read Data (up to 32 Bits from Slave)                    |

| PREADY      | Transfer Complete (Used by Slave to Insert Wait States) |

| PSLVERR     | Indicates APB Transfer Failure (OPTIONAL)               |

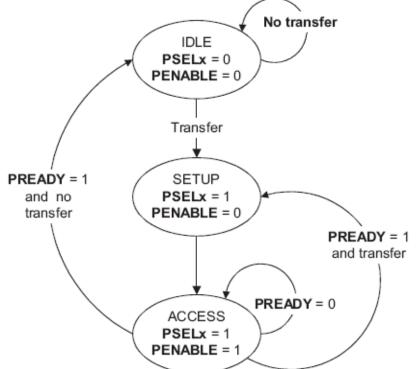

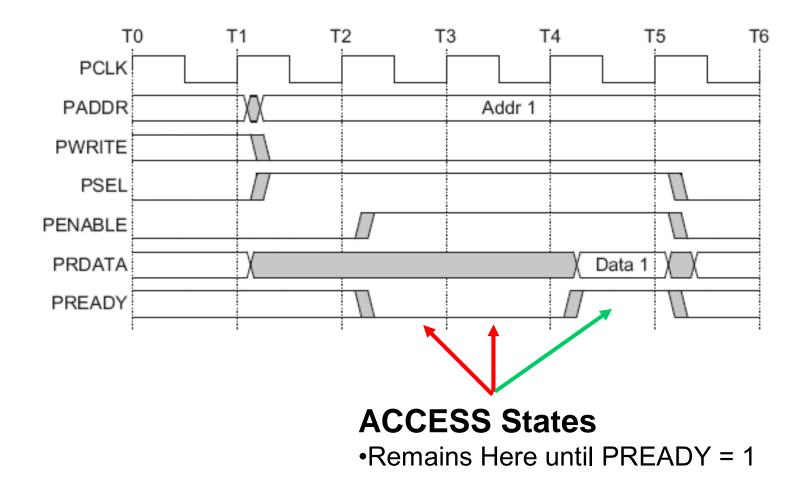

# **APB Bus**

#### State Machine

- IDLE

- Default APB State

#### SETUP

- Bus Moves Here when Transfer Is Required

- Select PSELx for Targeted Slave

Asserted

- Bus Remains Here Only One Clock Cycl

- Moves to Access State on Next Clock Rising Edge

#### ACCESS

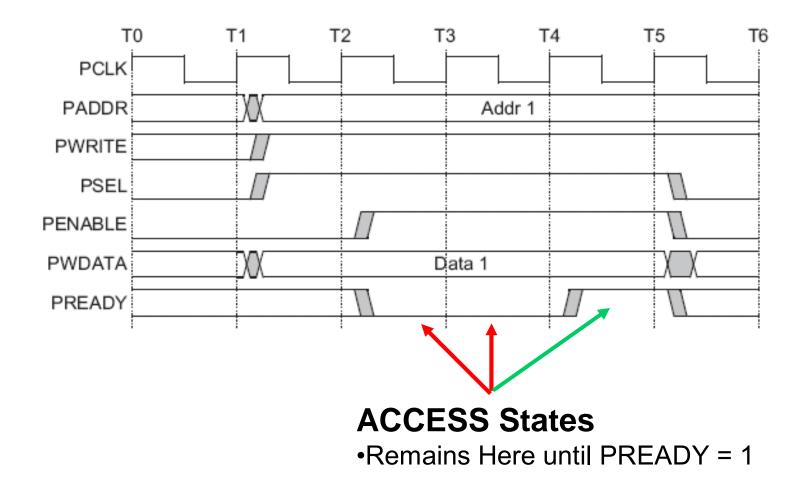

- Enable PENABLE Asserted

- PADDR, PWRITE, PSELx, and PWRITE Must Remain Stable during Transition from SETUP to ACCESS State

- Exit from ACCESS State Controlled by PREADY from Slave

- PREADY HIGH Successful Transfer

- PREADY LOW State Machine Remains in ACCESS State

### APB Write Transfer No Wait States

### APB Write Transfer With Wait States

### APB Read Transfer No Wait States

### APB Read Transfer With Wait States

# AHB to APB Transactions

Introduction to Cortex-M1 v1.8

**POWER MATTERS**

### BFM Simulation ModelSim Wave Window

| <b>i wave - default</b><br>ile Edit View Add Format Iools Window                                                                                                                                     |                                                                                              |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                      |                                                                                              |

| D 🗃 🖬 🍯 👗 🖻 🛍 😂 😂 🛛 🖊 🖁                                                                                                                                                                              |                                                                                              |

|                                                                                                                                                                                                      | 0 0 <del>0</del>                                                                             |

| Messages                                                                                                                                                                                             | Address                                                                                      |

| <ul> <li>/testbench/sysclk</li> <li>/testbench/nsysreset</li> <li>Timer Signals</li> <li>coretimer_00/pclk</li> <li>1</li> </ul>                                                                     | SETUP     Data       State     ACCESS       State     State                                  |

| coretimer_00/psel     coretimer_00/penable     coretimer_00/penable     coretimer_00/pwrite     f     f     coretimer_00/paddr     4                                                                 |                                                                                              |

|                                                                                                                                                                                                      | 000000000<br>00000000 0000000000000000000                                                    |

| cortexm1_00/hclk         1           cortexm1_00/htrans         00           cortexm1_00/hddr         00000000           cortexm1_00/haddr         00000000           cortexm1_00/hburst         001 | 00 10 10 10 10 10 10 10 10 10 10 10 10 1                                                     |

| cortexm1_00/hwrite         X           cortexm1_00/hsize         0XX           cortexm1_00/hprot         0000           cortexm1_00/hwdata         XXXXXXXX                                          | 000     0xx     010     000     0001     0001       0000     0001     0001     0001     0001 |

| cortexm1_00/hready 1<br>cortexm1_00/hrdata 00000000<br>cortexm1_00/hrdata 00000000                                                                                                                   |                                                                                              |

| cortexm1_00/nmi     C                                                                                                                                                                                | 1400 ns 1600 ns 1800 ns 2000 ns 2200 ns 2400 r                                               |

|                                                                                                                                                                                                      |                                                                                              |

| 1206800 ps to 2413600 ps Now: 213,                                                                                                                                                                   | '19,225 ps Delta: 1                                                                          |

APB write cycle (yellow) – write 0x00000100 to CoreTimer TimerLoad register Note that paddr = 0x000 – CoreAHB2APB strips off the upper 8 address bits and drives the appropriate PSEL

#### AMBA Bus Architecture Summary

- AHB is a High-performance Bus

- Supports Bursting and Split Transfers

- APB is a Simple, Low-performance Bus

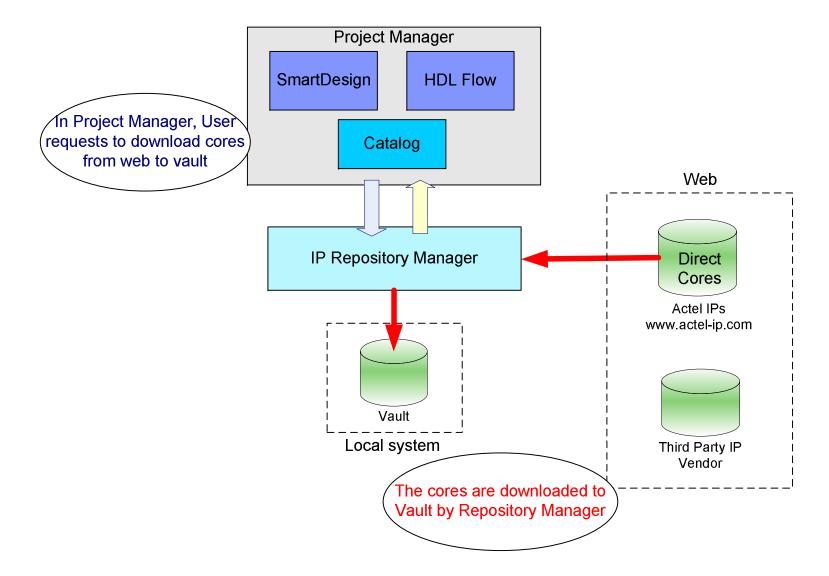

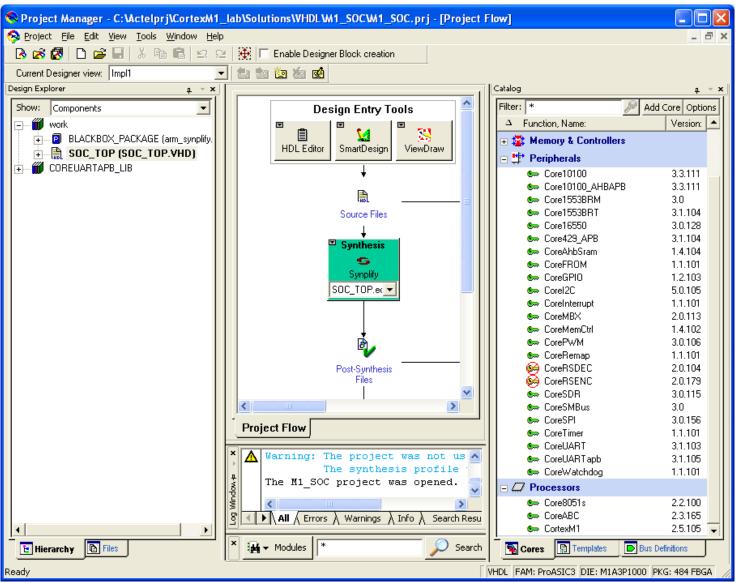

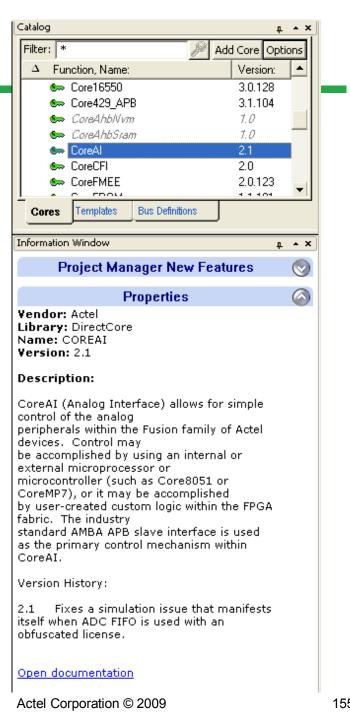

# **SmartDesign and IP Cores**

Actel Corporation © 2009

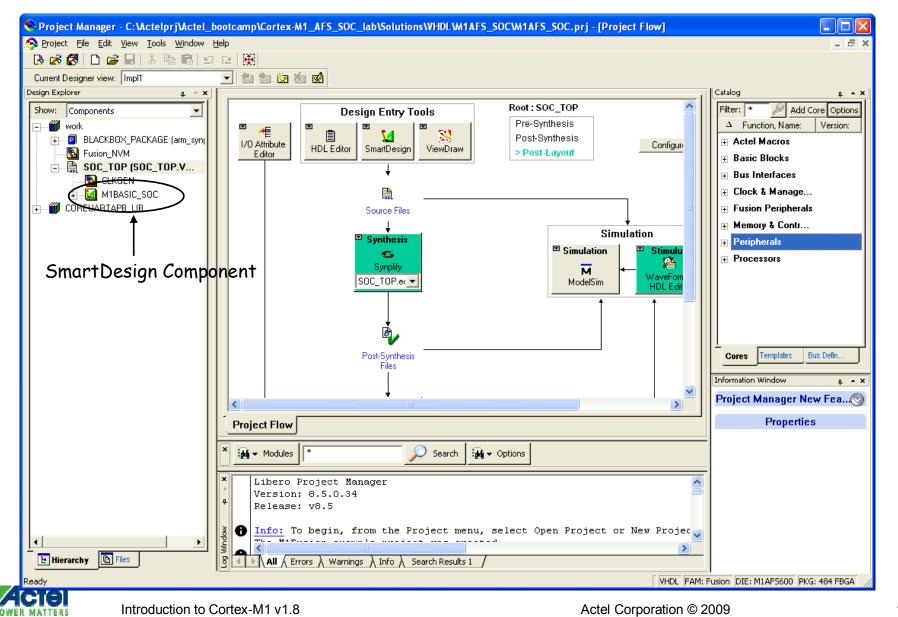

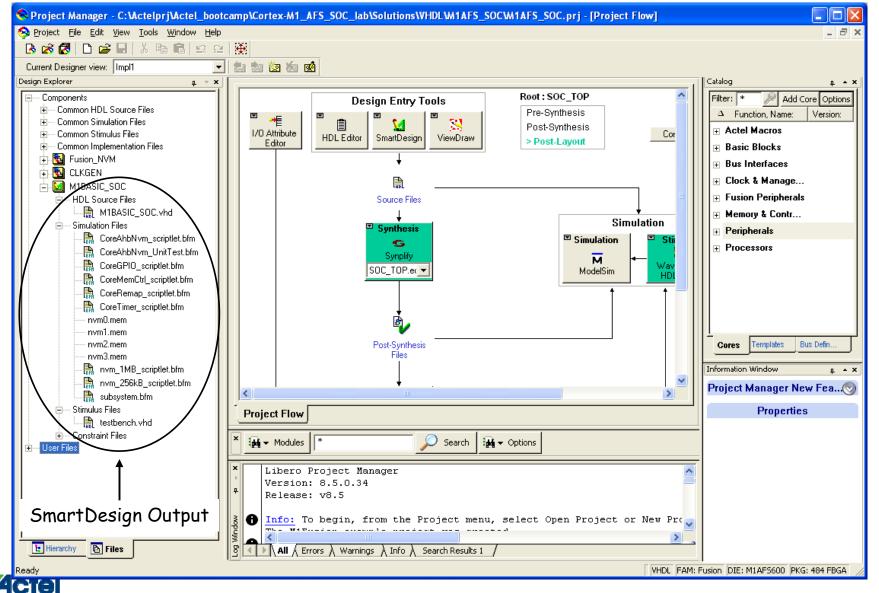

### Using SmartDesign

Actel Corporation © 2009

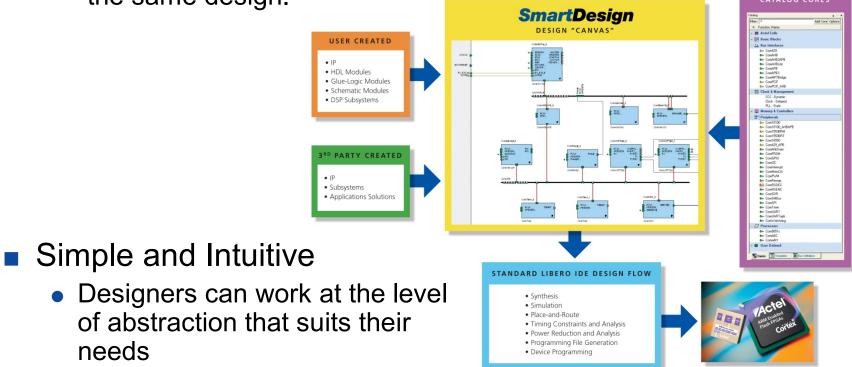

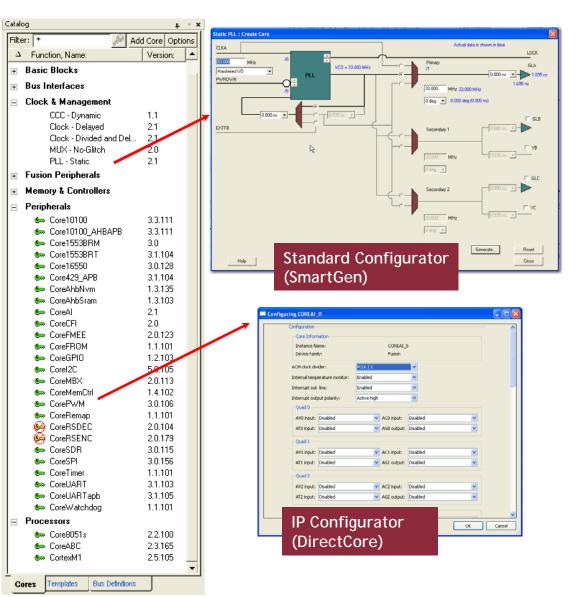

### SmartDesign Vision

Next Generation Design Entry Tool

• First tool in the industry that can be used for designing System on a Chip designs, custom FPGA designs or a mixture of both types in the same design. CATALOG CORES

needs

### What is SmartDesign?

- Powerful Block-based Visual Design Creation Tool

- Instantiate blocks from a variety of sources

- DirectCore IP, SmartGen, User HDL, Companion Cores, Actel library cells, and the list goes on.

- Supported for all platforms

- Simple and Intuitive Design Creation

- Auto Connect

- Fast manual connectivity between blocks

- Hierarchical design support

- DRC

- Checks rules to guarantee correct by construction design

- Connectivity errors

- Configuration errors

- Special silicon rules

- SOC Features

- Auto Connect

- clocks and resets for processors and peripherals

- Other known DirectCore connections

- Memory Map Configuration Dialog

- Testbench and Bus Functional Model (BFM) script generation

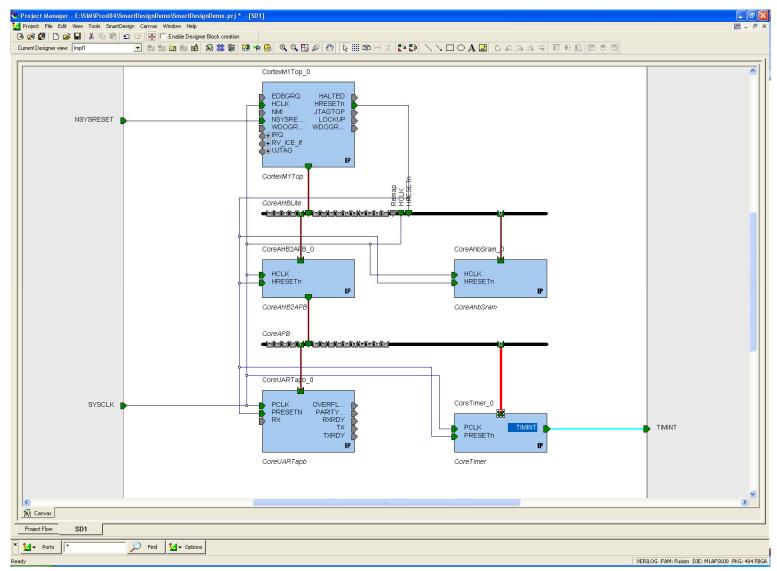

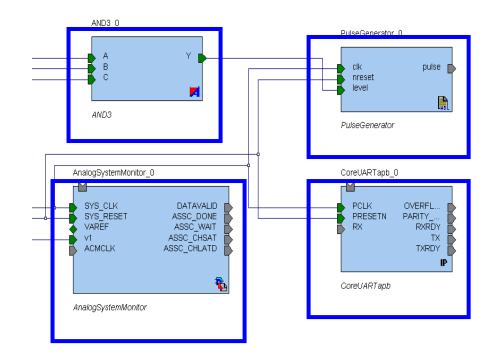

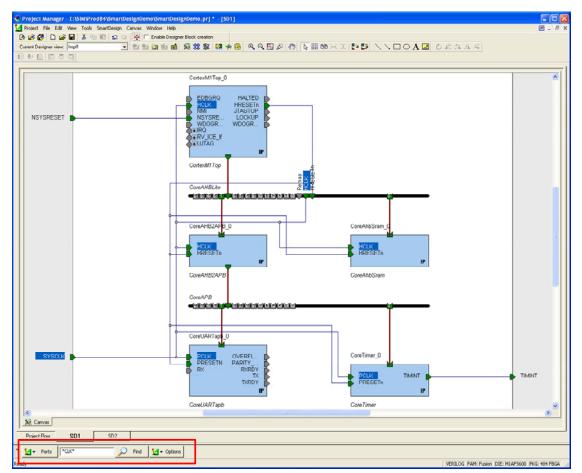

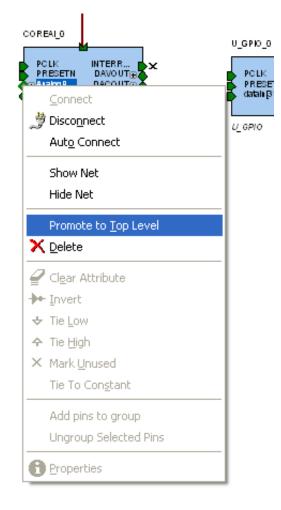

### SmartDesign Canvas

- SmartDesign Canvas

- Instance pins are displayed on canvas

- Connections are shown using nets

- Displaying of Nets is optional

- Selective enabling / disabling of showing nets

- Drag and Drop directly from the Catalog into the Canvas

- All Design Operations Available in the Canvas

- Connect / Disconnect

- Promote To Top

- Tie Low / Tie High / Tie Constant / Inversion

- Float

- Split ( if bus )

- Group

### SmartDesign Canvas

### Design with any Block Types

#### One Tool to Connect Your Design

- DirectCore IP

- SmartGen Cores

- User HDL

- Actel Macros (And, Or, I/Os, etc)

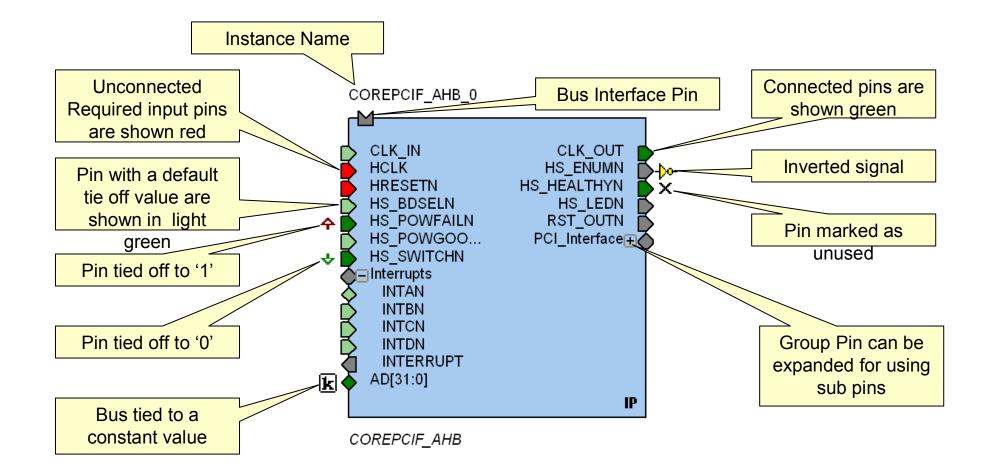

### **Canvas Instance**

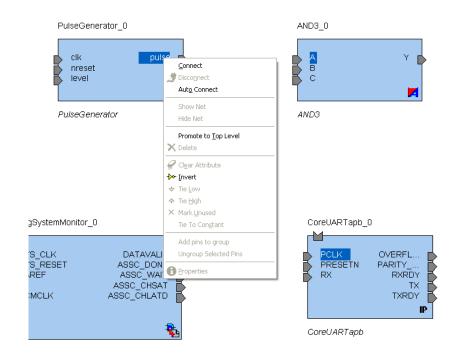

### **Making Connections**

- Right-click on a pin for Available Operations

- Select 2 or More Pins With the CTRL key, Right-click and Connect

### Modifying Memory Map

- Easy and Intuitive Method to Connect Peripherals at Particular Addresses on the Bus

- Interactive and Immediate Updating of Base Addresses

| ∃- CoreAHBLite_0 | Address    | Deriphoral             |

|------------------|------------|------------------------|

| CoreAPB_0        | 0x10000000 | CoreTimer_0:APBslave   |

| COLEMPD_0        |            | Cole Timei_0.AFBsiave  |

|                  | 0x11000000 |                        |

|                  | 0x12000000 |                        |

|                  | 0x13000000 |                        |

|                  | 0x14000000 |                        |

|                  | 0x15000000 |                        |

|                  | 0x16000000 |                        |

|                  | 0x17000000 |                        |

|                  | 0x18000000 |                        |

|                  | 0x19000000 | CoreUARTapb_0:APBslave |

|                  | 0x1a000000 |                        |

|                  | 0x1b000000 |                        |

|                  | 0x1c000000 |                        |

|                  | 0x1d000000 |                        |

|                  | 0x1e000000 |                        |

|                  | 0x1f000000 |                        |

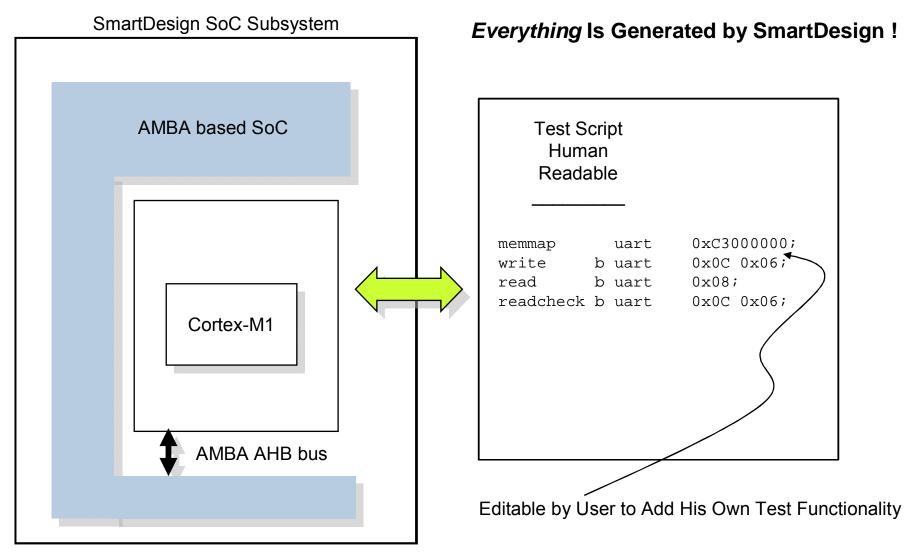

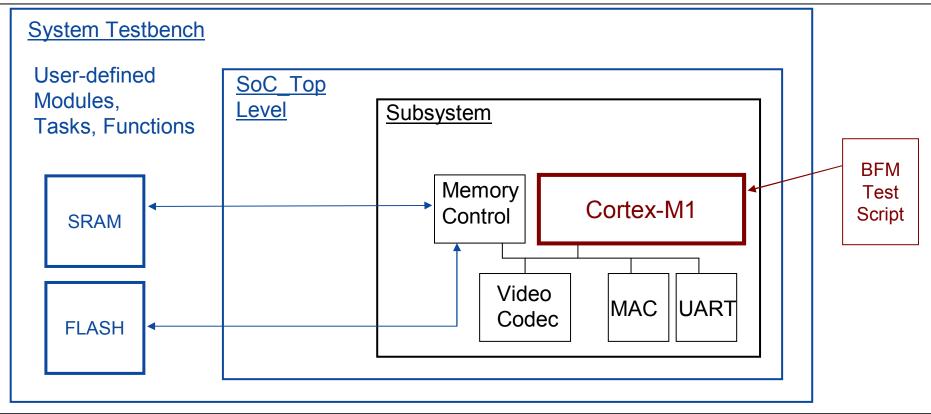

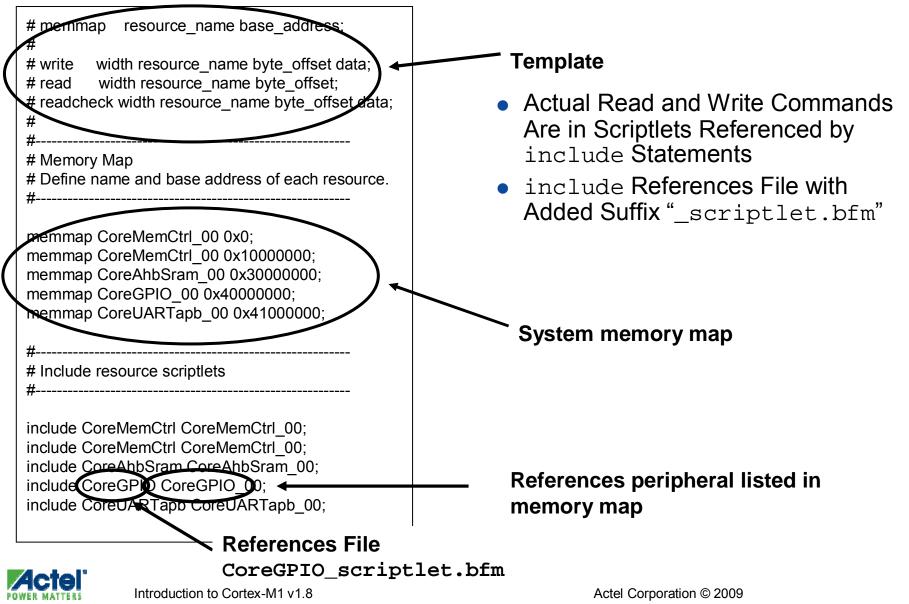

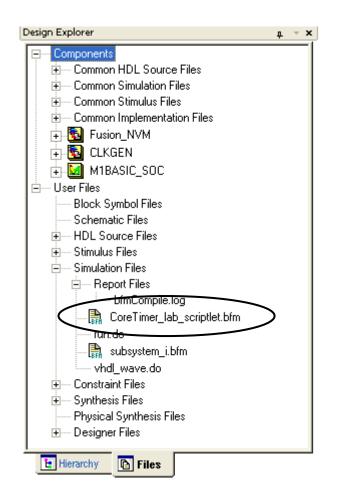

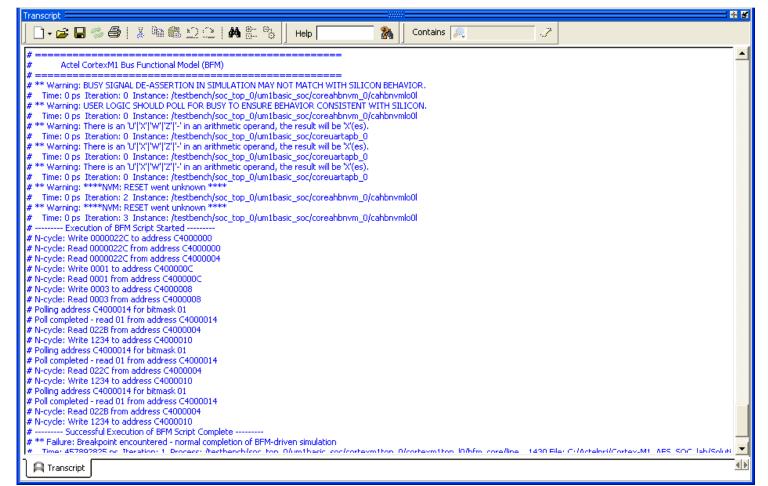

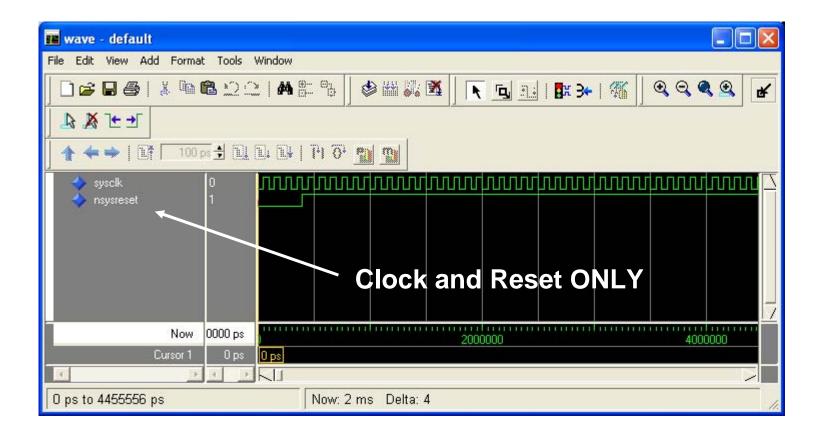

### **Testbench Generation**

- Design Testbench

- Generates a top level testbench

- Clock and Reset drivers automatically generated and connected

- Bus Functional Model Script Generation

- Generates BFM script file for processor based designs

- Based on your peripheral connectivity in your designs

- Look at Processor Core Handbooks (ex: CortexM1) for more details on BFMs and usage

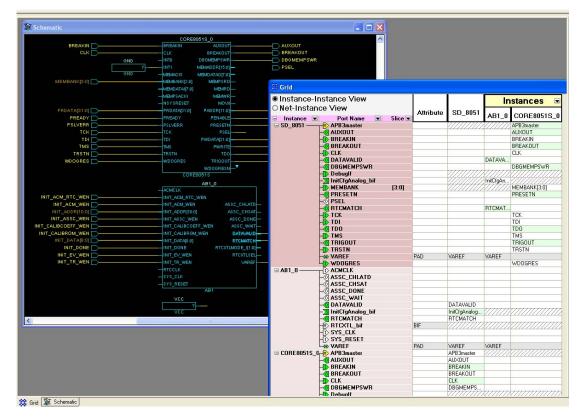

### **Design Rule Checker**

- Checks your Design for Errors

- Invoke with Checker icon (see picture)

- Connectivity

- Unconnected/Required input pins

- Floating output pins

- Silicon required connection

- Example: RTC must be driven by Crystal Oscillator

- Configuration

- Check consistency between configurations

- Example: CoreMP7 and CoreMP7Bridge debug configuration

- Errors Reported in a Connectivity Grid

- Directly fix your connectivity mistakes

- Enables fast sorting / filtering

|          | Message            | ▼ .          | Instance    | V         | Port Name | V | Slice 🝸 | Attribute        | SD1 |

|----------|--------------------|--------------|-------------|-----------|-----------|---|---------|------------------|-----|

| 🕀 Floati | ng Driver <u>A</u> |              |             |           |           |   |         |                  | 0   |

|          | nnected Bus Interf | ace <u>e</u> |             | _         |           |   |         |                  | 0   |

| 🗆 Undri  | ven Pin 覅 ———      |              | CoreAHBLite | <u>0_</u> | ᡗ Remap   |   |         |                  |     |

|          |                    | - E          | CoreUARTa   |           | I) BX     |   |         |                  |     |

|          |                    | L.           | CortexM1To  | p_0       |           |   |         | Polnvert         | 0   |

|          |                    |              |             |           |           |   |         | Tie Low Tie High |     |

### **Datasheet Generation**

- Design Datasheet

- Pin outs of the design

- Cores used and their description

- Memory Map

| AM: Fusion<br>Die: M1AF<br>Package: 484 F | <u>CoreUARTapb_0</u><br><u>CortexM1Top_0</u>                             |                                   | C                                                   | oreTimer_0      | : RegisterMa                   | ) Memor        | у Мар          |                             |                         |                            |             |

|-------------------------------------------|--------------------------------------------------------------------------|-----------------------------------|-----------------------------------------------------|-----------------|--------------------------------|----------------|----------------|-----------------------------|-------------------------|----------------------------|-------------|

| IDL: Verilo<br>.ocation: E:/SIN           | top of page                                                              | CortexM1Top_                      | _0 Subs <sup>rai</sup>                              | inge: 0×0100000 | 10                             |                |                |                             |                         |                            |             |

| itate: SAVE                               | Instance Name:                                                           | Master(s) on this bus:            |                                                     |                 | Address                        |                | Туре           | Width                       | Reset Value             | Name                       | Description |

|                                           | Type:                                                                    | <ul> <li>CortexM1Top_0</li> </ul> |                                                     |                 | base addres                    | s + 0x00       | read-write     | 32                          | 0x00000000              | <u>TimerLoad</u>           |             |

| 's                                        | Vendor:                                                                  |                                   |                                                     |                 | base addres                    | s + 0x04       | read-only      | 32                          | 0xFFFFFFFF              | <u>TimerValue</u>          |             |

| <u>'s</u><br>pres<br>emory Map            | Library:                                                                 |                                   |                                                     |                 | base addres                    | s + 0x08       | read-write     | 32                          | 0x00                    | TimerControl               |             |

|                                           | Core Name:                                                               |                                   |                                                     | -               | base addres:                   | s + 0x0C       | write-only     | 32                          | 0x0                     | <u>TimerPrescale</u>       |             |

|                                           | Version:                                                                 |                                   |                                                     |                 | base addres                    | s + 0x10       | write-only     | 32                          | 0x0                     | TimerIntClr                |             |

|                                           | Description:                                                             |                                   | CoreAh                                              |                 | base addres                    | s + 0x14       | read-only      | 32                          | 0x0                     | TimerRIS                   |             |

|                                           |                                                                          |                                   |                                                     |                 | base addres                    | s + 0x18       | read-only      | 32                          | 0x0                     | TimerMIS                   |             |

|                                           | instance list, top of page                                               |                                   |                                                     |                 |                                |                |                |                             |                         |                            |             |

|                                           | moranee not, top or page                                                 |                                   | CoreMe                                              |                 |                                |                | back to        | <u>CortexM1T</u>            | op_0 Memory Map         |                            |             |

|                                           | Instance Name:                                                           |                                   | <u>CoreMer</u>                                      | TimerLoad r     | egister details:               |                | <u>back to</u> | <u>CortexM1T</u>            | <u>op_0 Memory Map</u>  |                            |             |