2065-2

#### Advanced Training Course on FPGA Design and VHDL for Hardware Simulation and Synthesis

26 October - 20 November, 2009

**Digital CMOS Design**

Pirouz Bazargan-Sabet

LP6-Department ASIM

University of Pierre and Marie Curie VI

4, place Jussieu, 75252 Paris Cedex 06

France

## Outline

- Digital CMOS design

- ─ Boolean algebra

- ─ Basic digital CMOS gates

- Combinational and sequential circuits

- Coding Representation of numbers

How to implement Boolean functions in CMOS technology?

Which functionalities are available

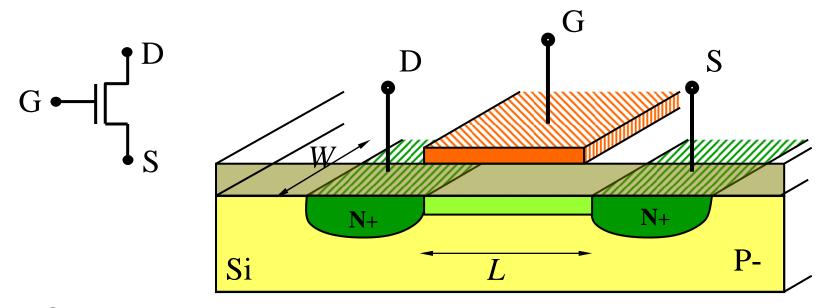

N-MOS transistor

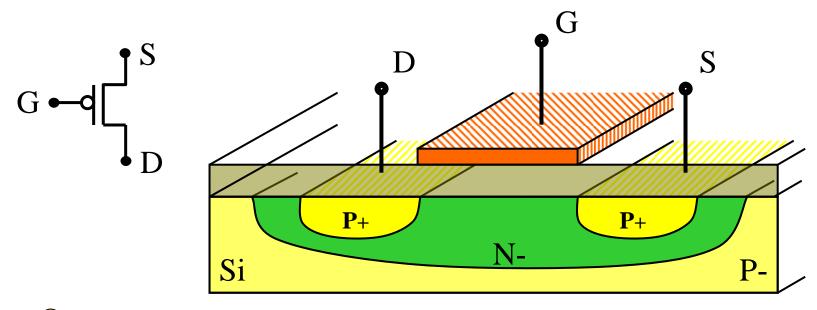

P-MOS transistor

The electrical behavior of a MOS transistor is very complex

Design of a multi-million transistor circuit?

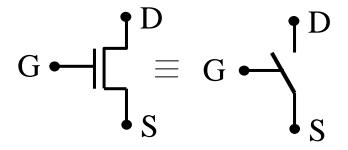

# In a digital circuit a MOS transistor can be seen as a Switch

*N-MOS*

$$D = S$$

when  $G = 1$

P-MOS

$$G \leftarrow G = G = G$$

$D = G = G$

$D = G = G$

$$D = S$$

when  $G = 0$

When driving, a MOS transistor can be seen as a Resistor

$$R \propto rac{L}{W}$$

For the same size, a P-MOS is twice more resistive than an N-MOS

The N-MOS and P-MOS are not exactly symmetrical

A N-MOS is a good transmitter of 0

A P-MOS is a good transmitter of 1

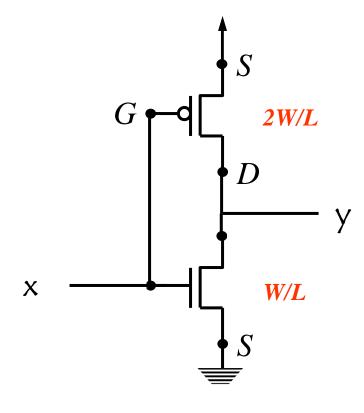

$$y = Not x$$

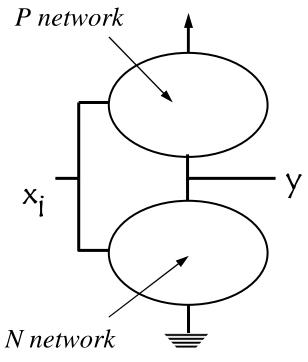

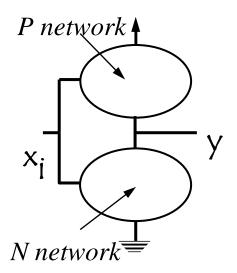

Dual CMOS gate

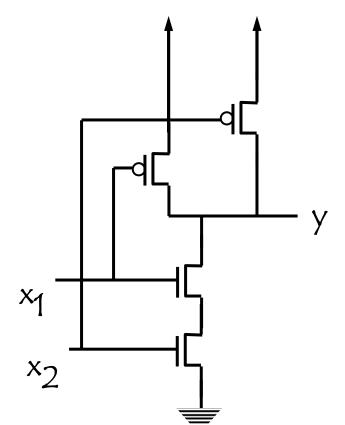

$$y = \overline{x_1 \cdot x_2}$$

Design of a dual gate

The P-network must be the dual of the N-network

Series — Parallel Parallel — Series

Take care of the size of transistors

- To set the output to 0 a path has to be created through the N network

- A series of N-transistor must be conducting

$$\prod x_i = 1$$

Only negative (inverting) functions can be created

Implementing a Boolean function with a CMOS gate?

- The function must be inverting in regard of all the variables

- Put the function in the form of  $f = \overline{g}$

- Design the N-network of g

#### Implementing a Boolean function with a CMOS gate?

- In the expression of g each '.' are two paths in series

- In the expression of g each '+' are two paths in parallel

- The P-network is the dual network of the N-network

- Avoid putting more than 3 transistors in series

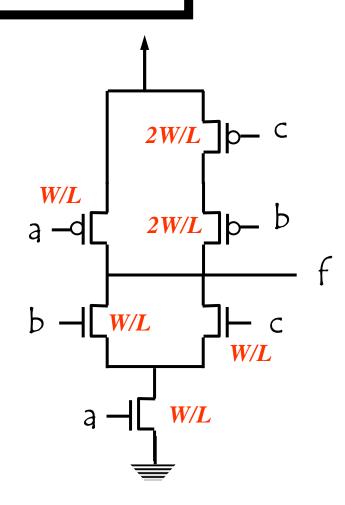

#### Example:

$$f = \overline{a} + (\overline{b}.c)$$

$$f = \overline{a} + (\overline{b+c})$$

$$f = \overline{a \cdot (b+c)}$$

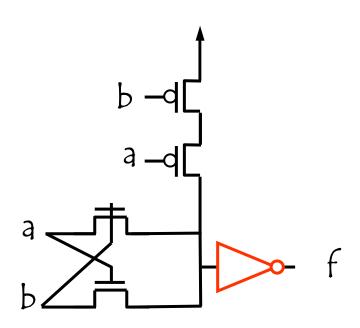

$$g = a \cdot (b+c)$$

#### Some gates:

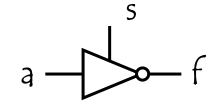

Inverter:  $f = \overline{q}$

Nand:  $f = \overline{a.b}$

Nor:  $f = \overline{a+b}$

Some gates:

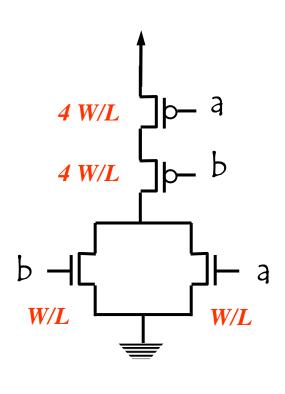

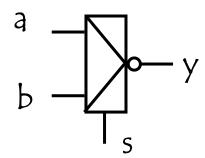

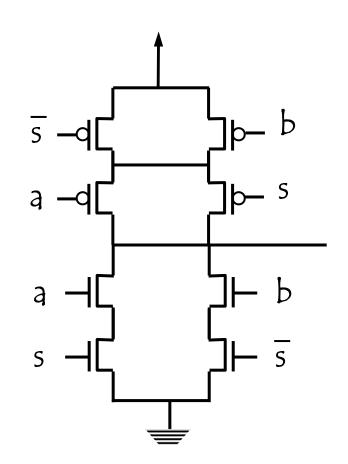

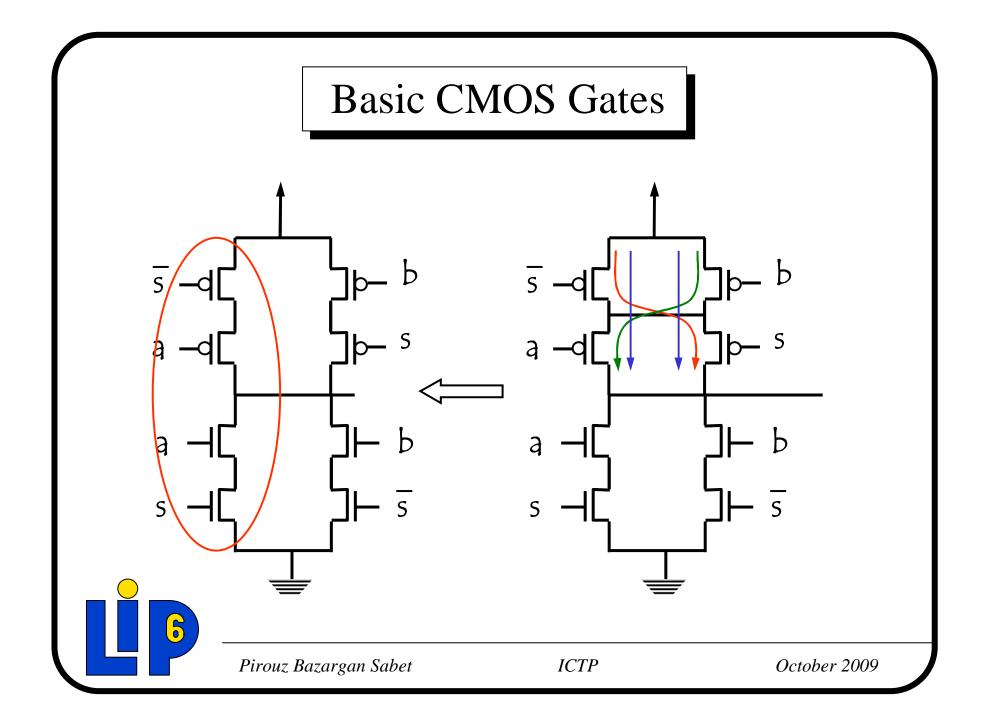

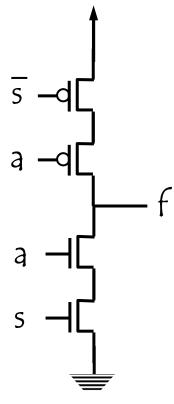

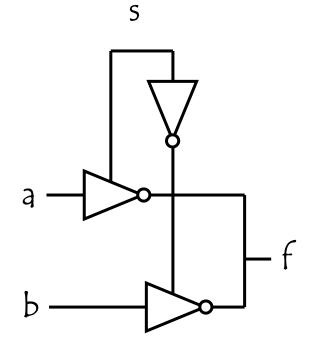

Multiplexer:

$$f = a.s + b.\overline{s}$$

Some gates: Multiplexer:

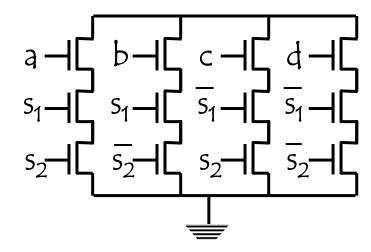

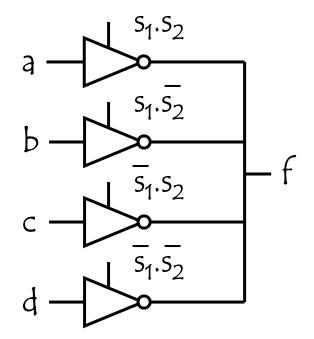

$$f = a.s_1.s_2 + b.s_1.\overline{s}_2 + c.\overline{s}_1.s_2 + d.\overline{s}_1.\overline{s}_2$$

Some gates:

Multiplexer:

$$f = a.s + b.s$$

If

$$s = 1$$

If  $s = 0$

$f = \overline{a}$  f is not defined

Tri-state driver

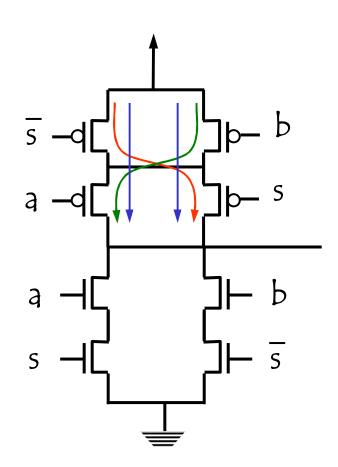

Some gates: Multiplexer:

Some gates: Multiplexer:

#### Some gates:

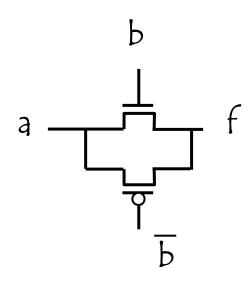

If

$$b = 1$$

If  $b = 0$

$f = a$  f is not defined

If  $a = 0$  then  $a = 0$

If  $a = 1$  then  $a = 1$

Pass-transistor

#### Some gates:

If

$$b = 0$$

If  $b = 1$

$f = a$  f is not defined

If  $a = 1$  then  $a = 1$

If  $a = 0$  then  $a = 0$

Pass-transistor

#### Some gates:

If

$$b = 1$$

If  $b = 0$

$f = a$  f is not defined

If  $a = 0$  then  $a = 0$

If  $a = 1$  then  $a = 1$

**CMOS** Switch

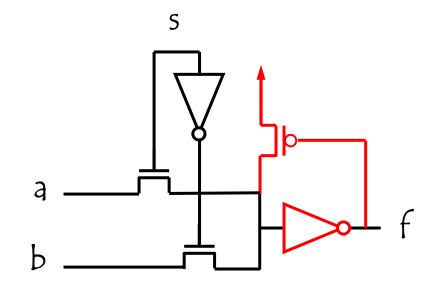

Some gates:

Multiplexer:

$$f = \overline{a.s + b.s}$$

#### Some gates:

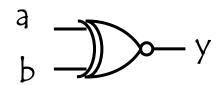

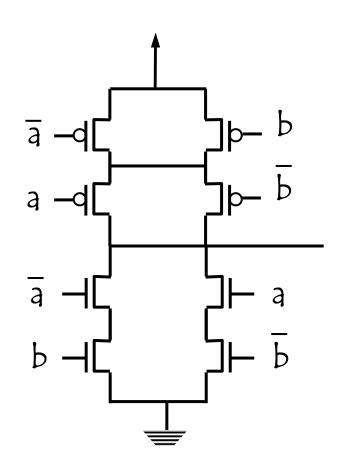

Nxor:  $f = \overline{a.b} + a.\overline{b}$

I need  $\frac{1}{4}$  and  $\frac{1}{5}$

#### Some gates:

Xor with Pass-transistors:

$$f = \overline{a.b} + \overline{a.b}$$

| a | Ь | f  |

|---|---|----|

| 0 | 0 | 1  |

| 0 | 1 | 0  |

| 1 | 0 | 0_ |

| 1 | 1 | 1  |