2177-17

#### ICTP Latin-American Basic Course on FPGA Design for Scientific Instrumentation

15 - 31 March 2010

Digital arithmetic III (basic arithmetic operations)

BAZARGAN SABET Pirouz LIP6, University Pierre et Matie Curie Paris France

## Outline

- Digital CMOS design

- Arithmetic operators

- Sequential functions

## Outline

- Digital CMOS design

- Arithmetic operators

- \_ Adders

- Comparators

- Shifters

- Multipliers

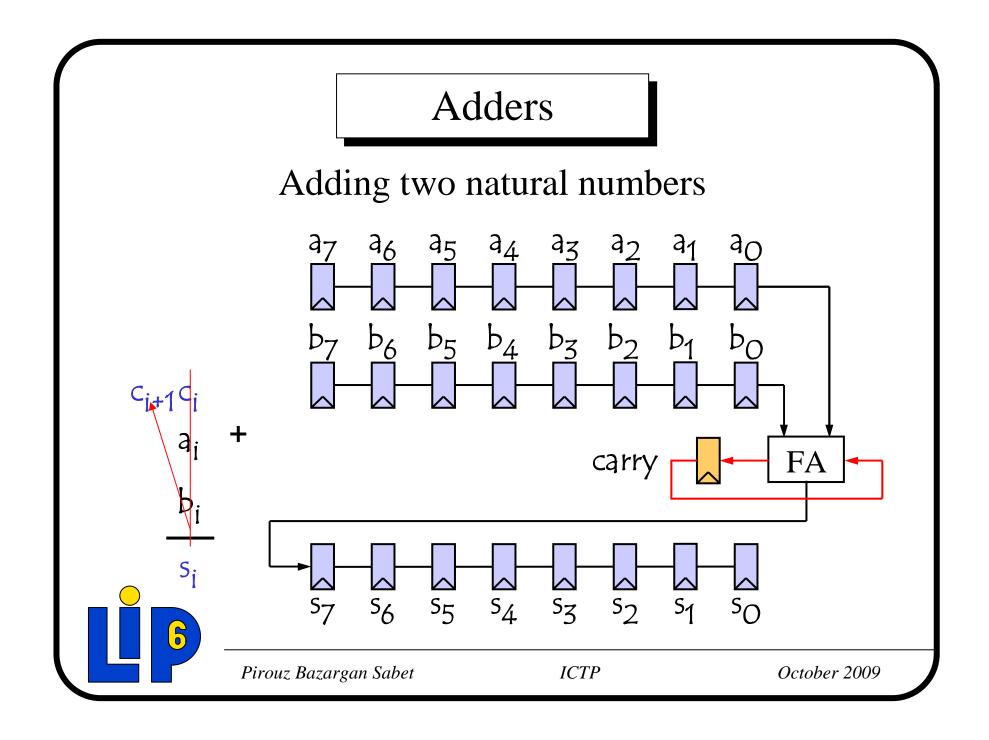

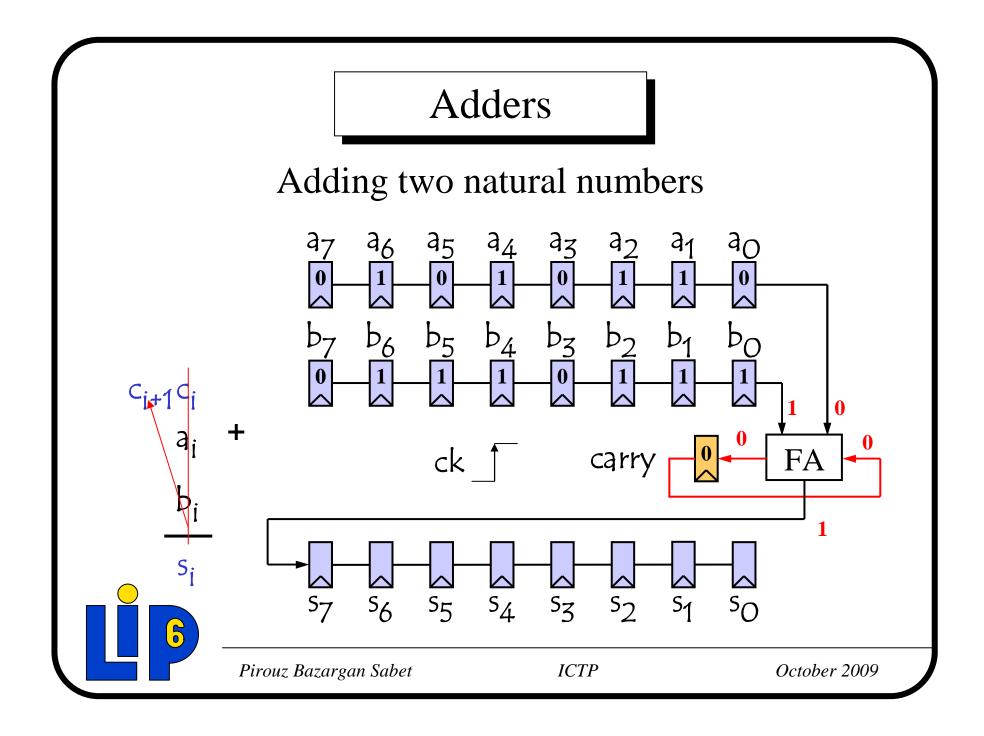

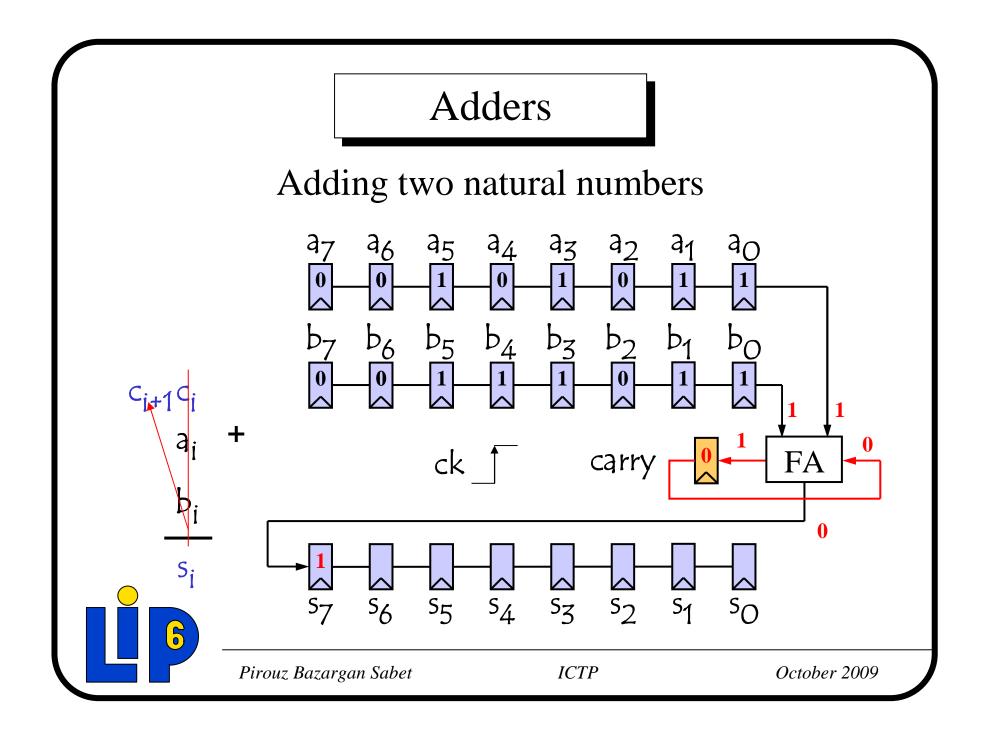

### Adding two natural numbers

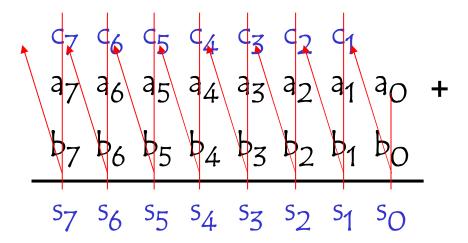

Let consider two natural numbers a and b coded on 8 bits using Natural Binary Code

### Adding two natural numbers

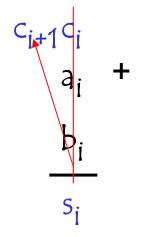

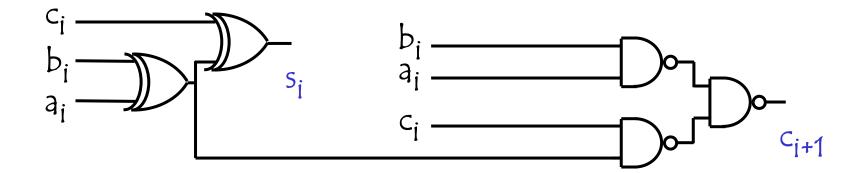

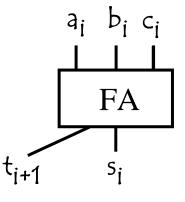

At each stage, I need to sum 3 single bit numbers  $a_i b_i c_i$ The carry out of the stage i is the input carry of the next stage

$s_i$  and  $c_{i+1}$  are Boolean functions of  $a_i$   $b_i$   $c_i$

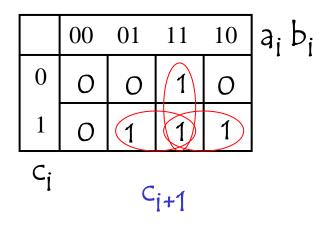

### Adding two natural numbers

|                | 00 | 01 | 11 | 10 | a <sub>i</sub> b <sub>i</sub> |

|----------------|----|----|----|----|-------------------------------|

| 0              | 0  | 1  | 0  | 1  |                               |

| 1              | 1  | 0  | 1  | 0  |                               |

| c <sub>i</sub> |    | S  | İ  |    | •                             |

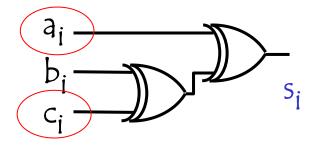

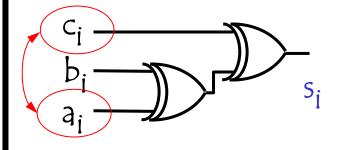

$$s_i = a_i \oplus b_i \oplus c_i$$

$$c_{i+1} = a_i . b_i + a_i . c_i + b_i . c_i$$

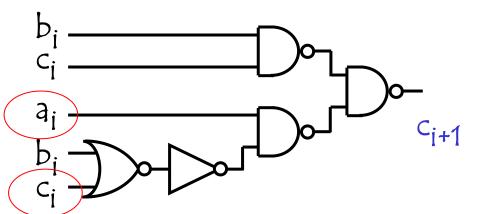

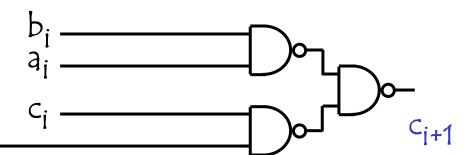

### Adding two natural numbers

$$s_i = a_i \oplus b_i \oplus c_i$$

$$c_{i+1} = a_i.b_i + a_i.c_i + b_i.c_i$$

$$c_{i+1} = a_i \cdot (b_i + c_i) + b_i \cdot c_i$$

Addition delay depends on the delay of  $c_i$  to  $c_{i+1}$

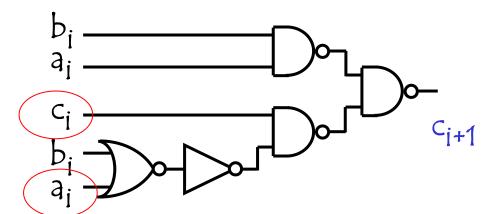

#### Adding two natural numbers

$$s_i = a_i \oplus b_i \oplus c_i$$

$$c_{i+1} = a_i . b_i + a_i . c_i + b_i . c_i$$

$$c_{i+1} = a_i . b_i + (a_i + b_i) . c_i$$

### Adding two natural numbers

$$s_i = a_i \oplus b_i \oplus c_i$$

$$c_{i+1} = a_i . b_i + a_i . c_i + b_i . c_i$$

$$c_{i+1} = a_i . b_i + (a_i + b_i) . c_i$$

$$c_{i+1} = a_i \cdot b_i + (a_i \oplus b_i) \cdot c_i$$

### Adding two natural numbers

The circuit generating  $s_i$  and  $c_{i+1}$  is called a Full Adder (FA)

### Adding two natural numbers

Sequential Adder

Area  $\propto$  n Delay  $\propto$  n cycles

Timing should be improved

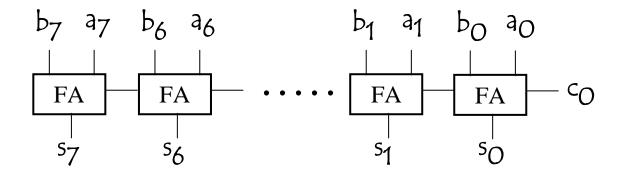

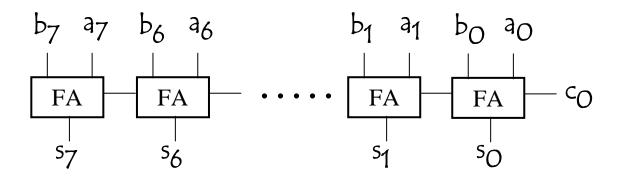

#### Adding two natural numbers

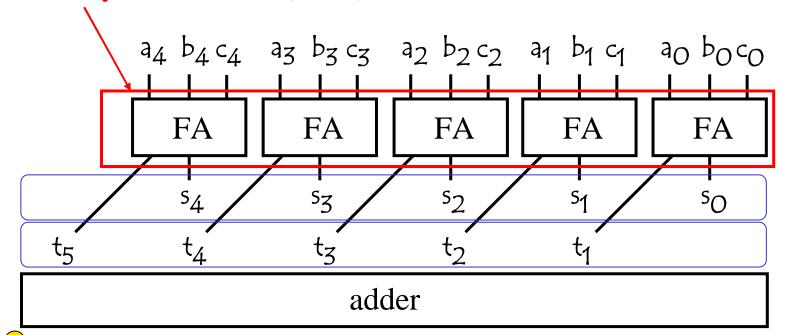

At each stage, I need to sum 3 single bit numbers  $a_i b_i c_i$ The carry out of the stage i is the input carry of the next stage

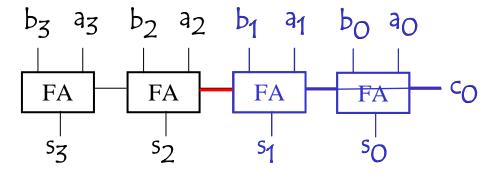

Ripple Carry Adder (RCA)

### Adding two natural numbers

Ripple Carry Adder (RCA)

Area  $\propto$  n

Delay  $\propto$  n

Timing should be improved

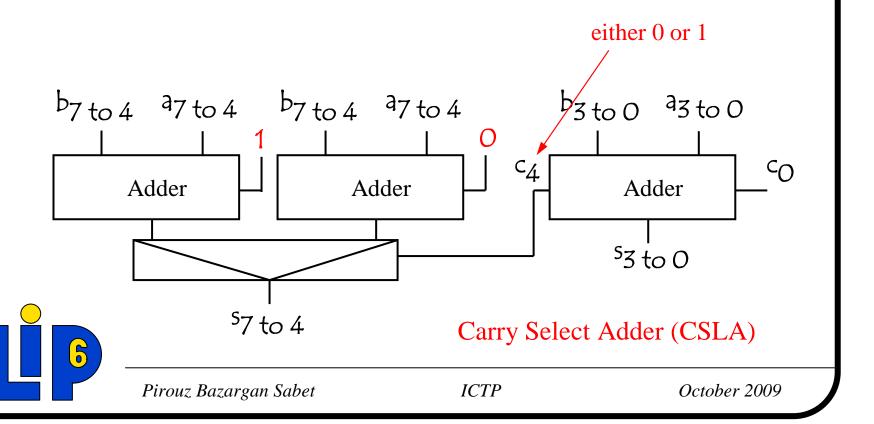

## Adding two natural numbers

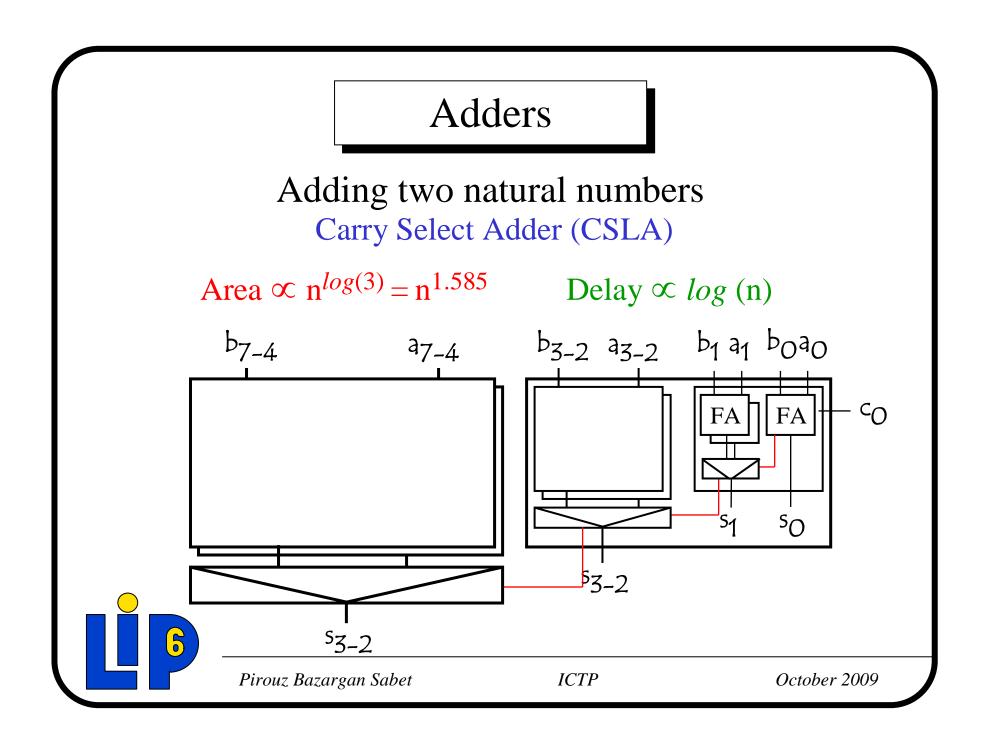

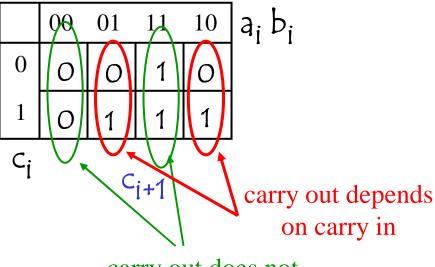

### Adding two natural numbers

Acceleration technics

| 00         | 01          | 11         | 10          | ai |

|------------|-------------|------------|-------------|----|

| absorption | propagation | generation | propagation |    |

carry out does not depend on carry in

## Adding two natural numbers

Acceleration technics

|          | 00 | 01 | 11 | 10 |

|----------|----|----|----|----|

| 0        | 0  | 0  | 1  | 0  |

| 1        | 0  | 1  | 1  | 1  |

| <u> </u> |    |    |    |    |

$C_{i+1}$

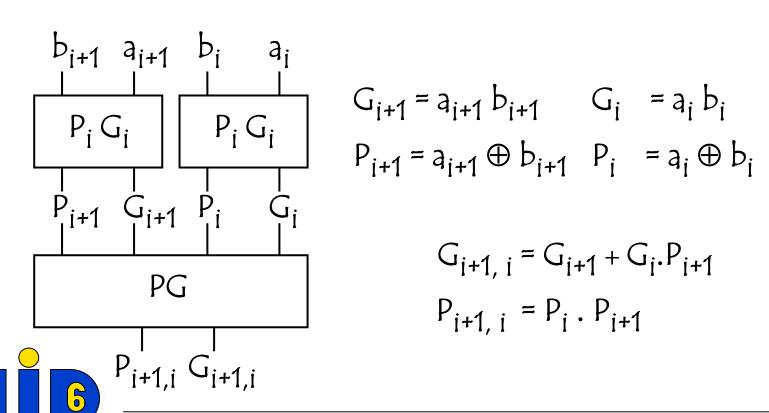

$$G_i = a_i b_i$$

$P_i = a_i \oplus b_i$

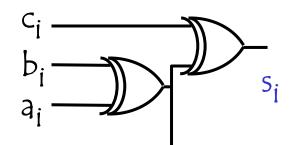

$c_{i+1} = G_i + P_i c_i$  $s_i = P_i \oplus c_i$

$$a_i b_i$$

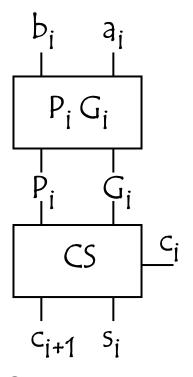

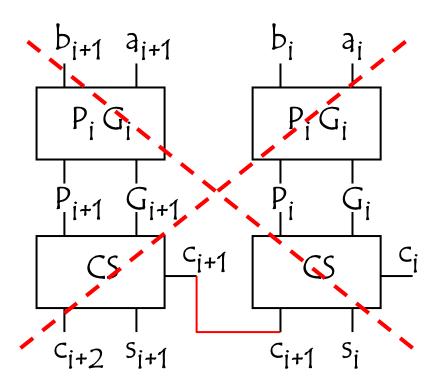

### Adding two natural numbers

| Gi      | $= a_i b_i$        |

|---------|--------------------|

| $P_{i}$ | =a <sub>i</sub> ⊕b |

$$c_{i+1} = G_i + P_i c_i$$

$$s_i = P_i \oplus c_i$$

| 00         | 01          | 11         | 10          | a <sub>i</sub> b <sub>i</sub> |

|------------|-------------|------------|-------------|-------------------------------|

| absorption | propagation | generation | propagation |                               |

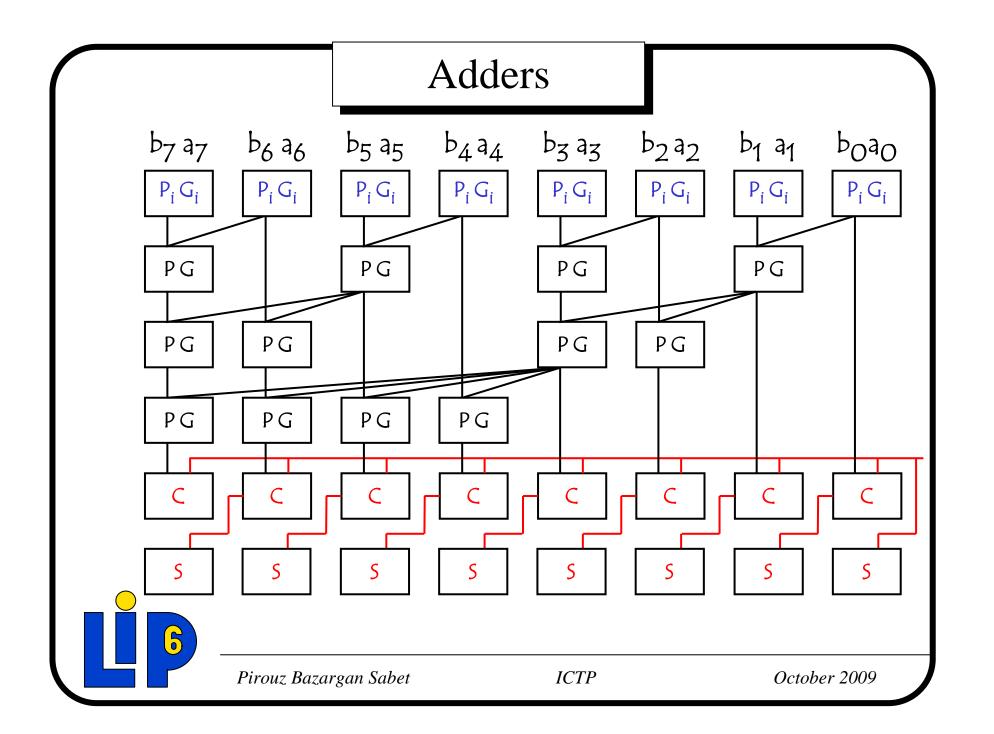

#### Adding two natural numbers

#### Adding two natural numbers

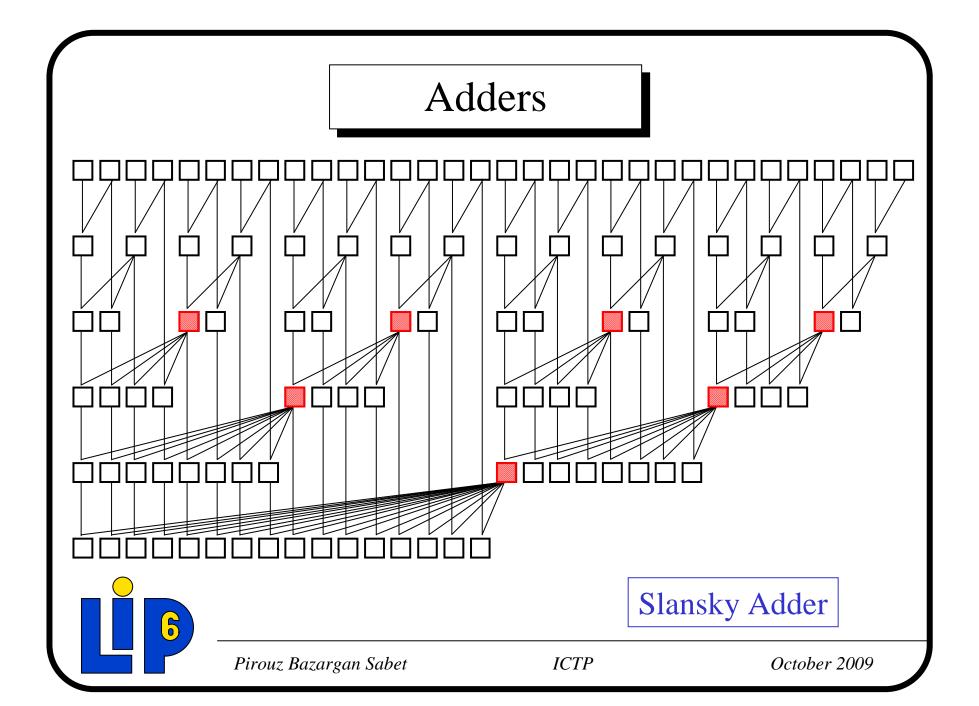

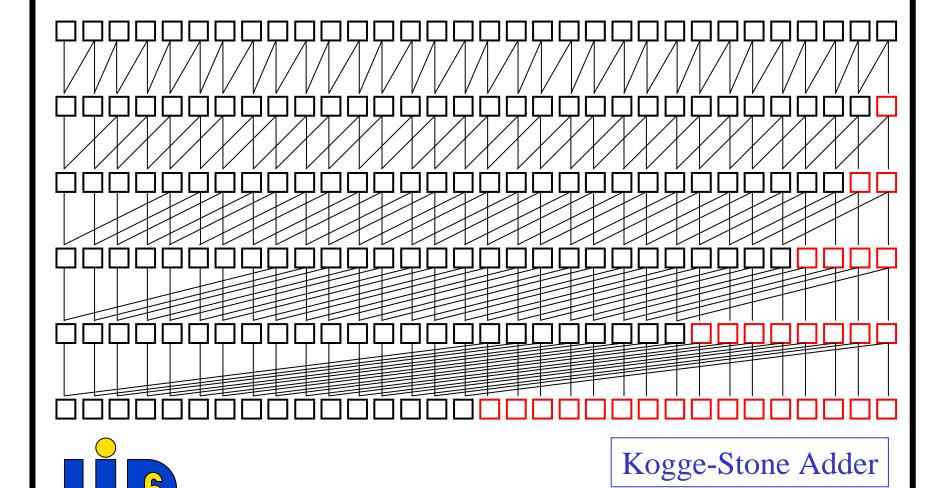

## Adding two natural numbers (summary)

|                       | Area          | Delay   |

|-----------------------|---------------|---------|

| Ripple Carry (RCA)    | n             | n       |

| Carry Select (CSLA)   | $n^{\log(3)}$ | log (n) |

| Carry Lookahead (CLA) | n log (n)     | log (n) |

| Magic Adder           | n             | Cste    |

#### More improvements?

## Adding two natural numbers

Ripple Carry Adder (RCA)

### Adding two natural numbers

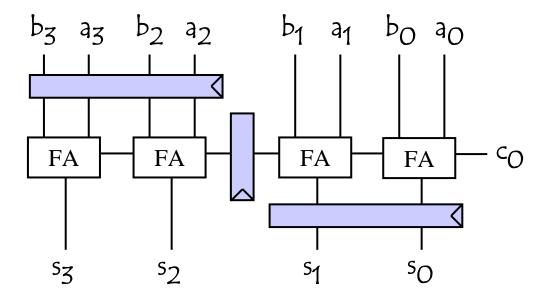

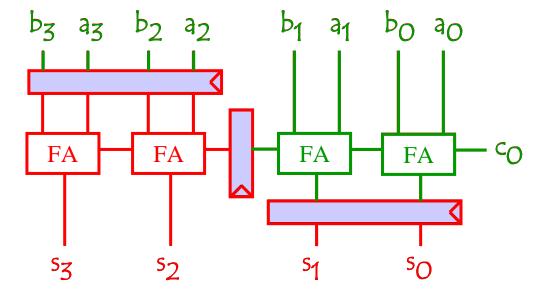

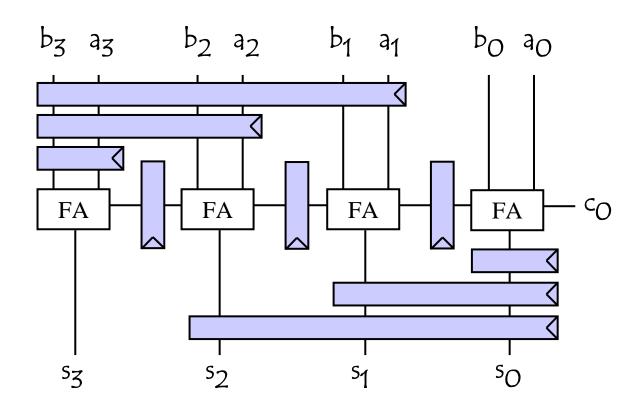

Ripple Carry Adder (RCA)

pipelining

## Adding two natural numbers

Ripple Carry Adder (RCA)

pipelining

# Adding two natural numbers

Pirouz Bazargan Sabet

ICTP

October 2009

## Adding two natural numbers (summary)

|                       | Area           | Delay          |

|-----------------------|----------------|----------------|

| Ripple Carry (RCA)    | n              | n              |

| Carry Select (CSLA)   | $n^{log(3)}$   | log (n)        |

| Carry Lookahead (CLA) | n log (n)      | log (n)        |

| Pipeline Adder        | n <sup>2</sup> | Cste (1 cycle) |

| Magic Adder           | n              | Cste           |

When there is no door to escape break the wall

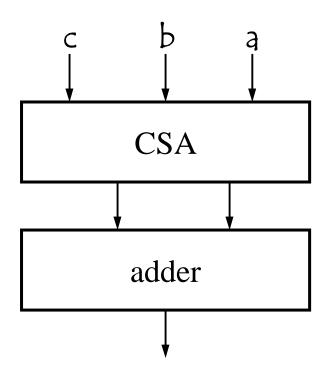

Adding three natural numbers

Adding three natural numbers

$$s_i = a_i \oplus b_i \oplus c_i$$

$$s_i = a_i \oplus b_i \oplus c_i$$

$c_{i+1} = a_i \cdot b_i + a_i \cdot c_i + b_i \cdot c_i$

the expressions are symmetrical in regard of a, b and c

A full adder creates 2 numbers from 3

### Adding three natural numbers

#### Carry Save Adder (CSA)

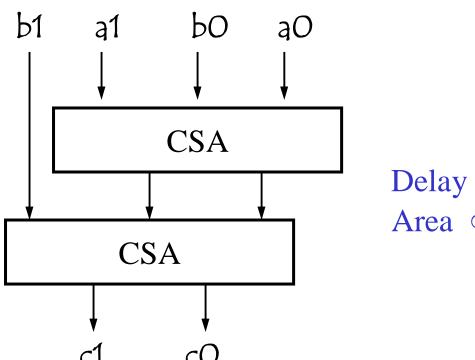

Adding three natural numbers

Delay = cste Area  $\propto$  n

#### Adding two natural numbers

Change the representation of numbers

Given a natural number a : a is coded using 2n bits

$$a = a0 + a1$$

Redundant Binary Code

Example: the number 5 can be coded on 4 bits as

#### Adding two natural numbers

Changing the representation of numbers

$$a = a0 + a1$$

$$b = bO + b1$$

Adding a and b in Redundant Binary Code is finding c

$$c = cO + c1$$

such as

$$cO + c1 = aO + a1 + bO + b1$$

Adding 4 numbers to generate 2

## Adding two natural numbers

Delay = csteArea ∝ n