2384-15

#### ICTP Latin-American Advanced Course on FPGADesign for Scientific Instrumentation

19 November - 7 December, 2012

Introduction to the WISHBONE Bus Interface

CICUTTIN Andres

ICTP Multidisciplinary Laboratory Via Beirut 31 (34100) Trieste ITALY

### Introduction to

## The WISHBONE Bus Interface

A System-on-chip (SoC) Interconnection Architecture For Portable IP Cores

Taken from the WISHBONE SoC Architecture Specification, Revision B.3

# What is Wishbone ?

1) A general purpose interface between IP cores. It defines the standard data exchange between IP core modules.

2) A flexible design methodology for use with semiconductor IP cores.

3) "It is not a bus"

# Some of the advantages

- Promotes design reuse by alleviating system-onchip integration problems.

- Improves the portability and reliability of the system.

- Faster design time.

- Can be used for soft core, firm core or hard core IP.

- Does not require the use of specific development tools or target hardware.

- Fully compliant with virtually all logic synthesis tools.

- Documentation standards simplify IP core reference manuals.

## **WISHBONE Features I**

- Simple, compact, logical IP core hardware interfaces requiring very few logic gates.

- Supports structured design methodologies used by large project teams.

- Full set of popular data transfer bus protocols including:

- READ/WRITE cycle.

- BLOCK transfer cycle.

- RMW cycle.

- Modular data bus widths and operand sizes.

- Supports both *big endian* and *little endian* data ordering.

### **WISHBONE Features II**

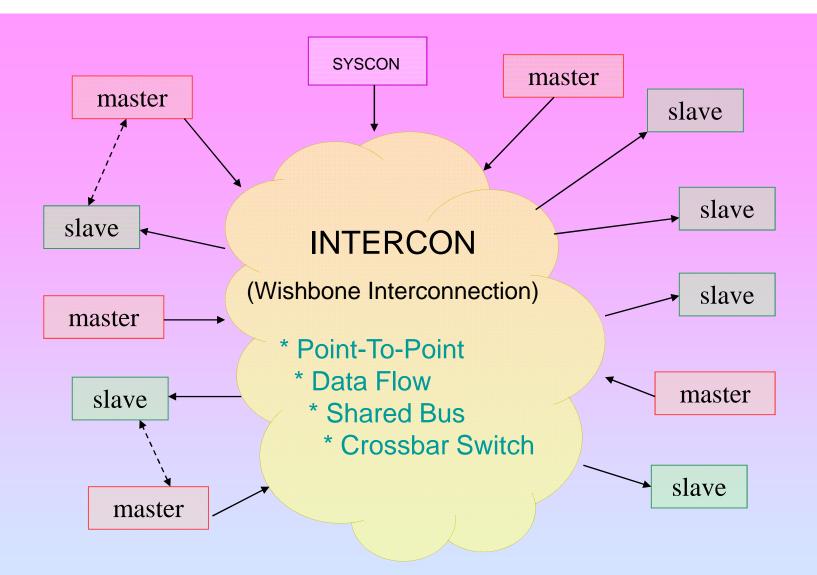

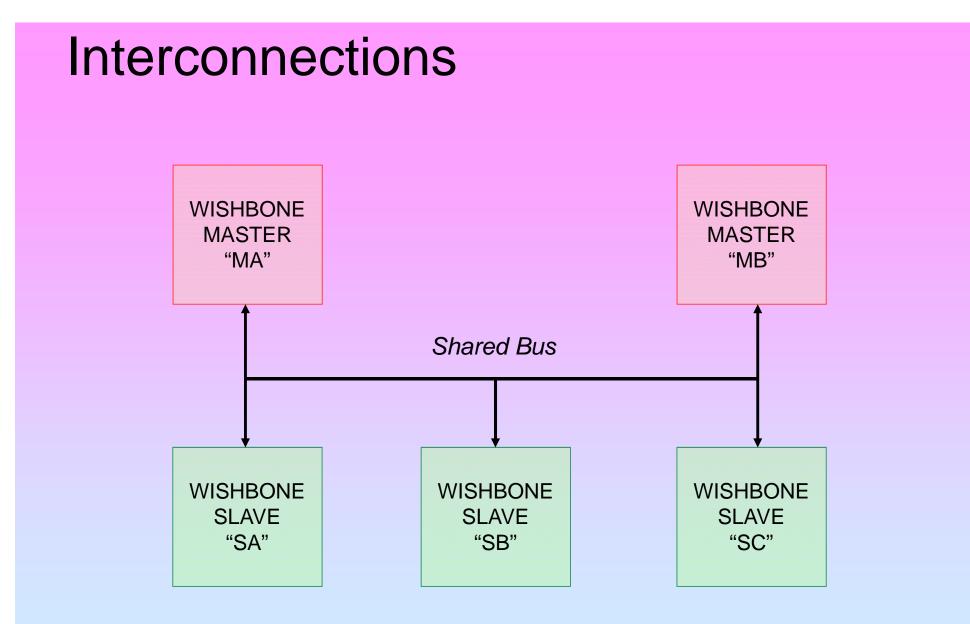

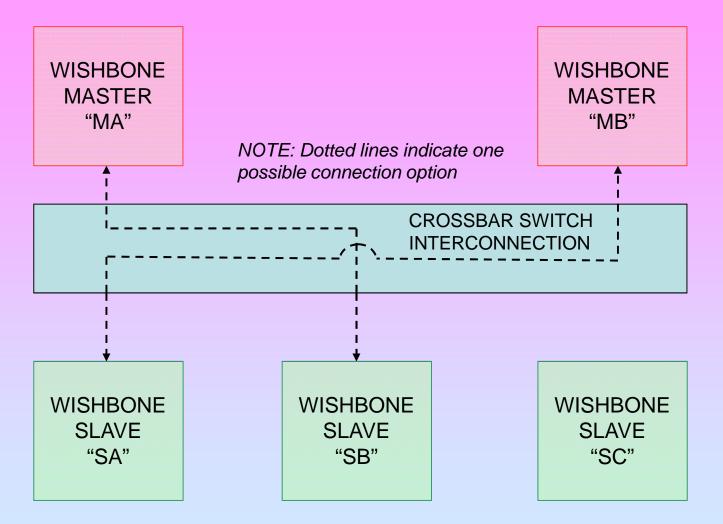

- Supports variable core interconnection methods: Point-to-point, shared bus, crossbar switch, and switched fabric interconnections.

- Handshaking protocol allows each IP core to throttle its data transfer speed.

- Supports single clock data transfers.

- Supports normal cycle termination, retry termination and termination due to error.

- Modular address widths.

- Partial address decoding scheme for slaves.

### **WISHBONE Features III**

- User-defined tags. These are useful for applying information to an address bus, a data bus or a bus cycle.

- MASTER / SLAVE architecture for very flexible system designs.

## **WISHBONE Features IV**

- Multiprocessing (*multi-MASTER*) capabilities. This allows for a wide variety of System-on-Chip configurations.

- Arbitration methodology is defined by the end user (priority arbiter, round-robin arbiter, etc.).

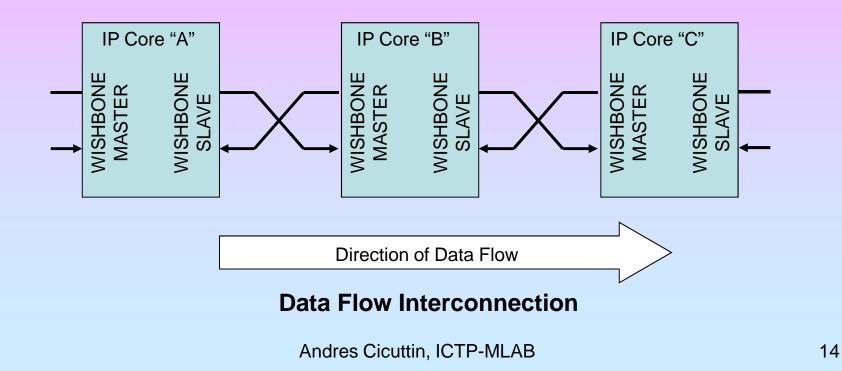

- Supports various IP core interconnection means, including:

- Point-to-point

- Shared bus

- Crossbar switch

- Data flow interconnection

- **Synchronous design** (Assures portability, and ease of use)

### **Specification Keywords**

- 1. RULES

- 2. RECOMMENDATIONS

- 3. SUGGESTIONS

- 4. PERMISSIONS

- 5. OBSERVATIONS

### RULES

Rules form the basic framework of the specification. Rules are characterized by an imperative style. The uppercase words MUST and MUST NOT are reserved exclusively for stating rules.

### RECOMMENDATIONS

Whenever a recommendation appears, designers would be wise to take the advice given. Doing otherwise might result in some awkward problems or poor performance. These are provided as guidance for the user.

### SUGGESTIONS

A suggestion contains advice which is helpful but not vital. The reader is encouraged to consider the advice before discarding it. Some design decisions are difficult until experience has been gained. Some suggestions have to do with designing compatible interconnections, or with making system integration easier.

### PERMISSIONS

In some cases a rule does not specifically prohibit a certain design approach, but the reader might be left wondering whether that approach might violate the spirit of the rule, or whether it might lead to some subtle problem. Permissions reassure the reader that a certain approach is acceptable and will not cause problems. The upper-case word MAY is reserved exclusively for stating a permission and is not used for any other purpose.

### **OBSERVATIONS**

Observations do not offer any specific advice. They usually clarify what has just been discussed. They spell out the implications of certain rules and bring attention to things that might otherwise be overlooked. They also give the rationale behind certain rules, so that the reader understands why the rule must be followed.

### **Examples:** Rules and Permissions

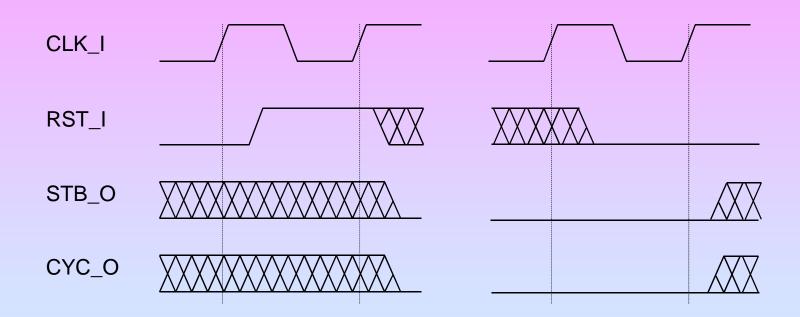

#### • RULE 3.00

All WISHBONE interfaces **MUST** initialize themselves at the rising [CLK\_I] edge following the assertion of [RST\_I]. They **MUST** stay in the initialized state until the rising [CLK\_I] edge that follows the negation of [RST\_I].

#### • RULE 3.05

[RST\_I] MUST be asserted for at least one complete clock cycle on all WISHBONE interfaces.

#### • PERMISSION 3.00

[RST\_I] MAY be asserted for more than one clock cycle, and MAY be asserted indefinitely.

#### • RULE 3.10

All WISHBONE interfaces **MUST** be capable of reacting to [RST\_I] at any time.

#### • RULE 3.15

All self-starting state machines and counters in WISHBONE interfaces **MUST** initialize themselves at the rising [CLK\_I] edge following the assertion of [RST\_I]. They **MUST** stay in the initialized state until the rising [CLK\_I] edge that follows the negation of [RST\_I].

# Examples: Recomendations, suggestions and observations

#### • **RECOMENDATION 3.00**

**Design** SYSCON modules so that they assert [RST\_O] during a power-up condition. [RST\_O] **should** remain asserted until all voltage levels and clock frequencies in the system are stabilized. When negating [RST\_O], **do so** in a synchronous manner that conforms to this specification.

### • SUGGESTION 3.00

Some circuits require an *asynchronous* reset capability. If an IP core or other SoC component requires an asynchronous reset, then **define** it as a non-WISHBONE signal. This prevents confusion with the WISHBONE reset [RST\_I] signal that uses a purely synchronous protocol, and needs to be applied to the WISHBONE interface only.

#### OBSERVATION 3.20

All WISHBONE *interfaces* respond to the reset signal. However, the IP Core connected to a WISHBONE interface does not necessarily need to respond to the reset signal.

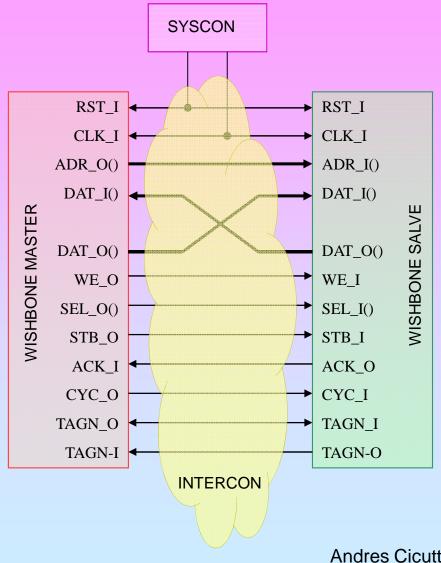

# The Wishbone Modules

**SYSCON**: drives the system clock [CLK\_O] and reset [RST\_O] signals.

**MASTER**: IP Core interface that generates bus cycles.

**SLAVE**: IP Core interface that receives bus cycles.

**INTERCON**: an IP Core that connects all of the MASTER and SLAVE interfaces together.

The Wishbone Interconnection is created by the SYSTEM INTEGRATOR, who has total control of its design!

### Interconnections

#### **Point-To-Point Interconnection**

#### **Shared Bus Interconnection**

### Interconnections

#### **Crossbar Switch Interconnection**

### The Main Wishbone Signals (Ports)

**RST\_I**: receives the reset output signal [RST\_O] from the SYSCON.

**CLK\_I**: receives the clock output signal [CLK\_O] from the SYSCON.

**ADR\_I:** receives the address from MASTER

ADR\_O: drives the address to the SLAVE

DAT\_I: receives the data

DAT\_O: drives the data

WE\_I, WE\_O: Write Enable (active high)

STB\_I, STB\_O: Strobe (kind of chip select)

ACK\_I, ACK\_O: Acknowledge (active high)

CYC\_I, CYC\_O: Bus Cycle (active high)

### **WISHBONE Classic Bus Cycles**

**The Reset Cycle**

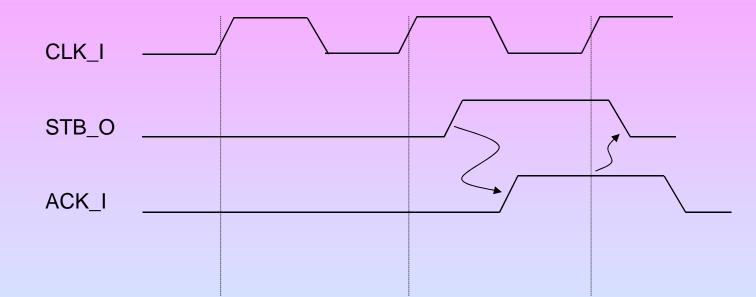

### **Local Bus Handshaking Protocol**

# Tag Types

|                 | Master   |                 | Slave    |                 |

|-----------------|----------|-----------------|----------|-----------------|

| Description     | TAG TYPE | Associated with | TAG TYPE | Associated with |

| Address tag     | TGA_O()  | ADR_O           | TGA_I()  | ADR_I()         |

| Data tag input  | TGD_I()  | DAT_I()         | TGD_I()  | DAT_I()         |

| Data tag output | TGD_O()  | DAT_O()         | TGD_O()  | DAT_O()         |

| Cycle tag       | TGC_O()  | Bus Cycle       | TGC_I()  | Bus Cycle       |

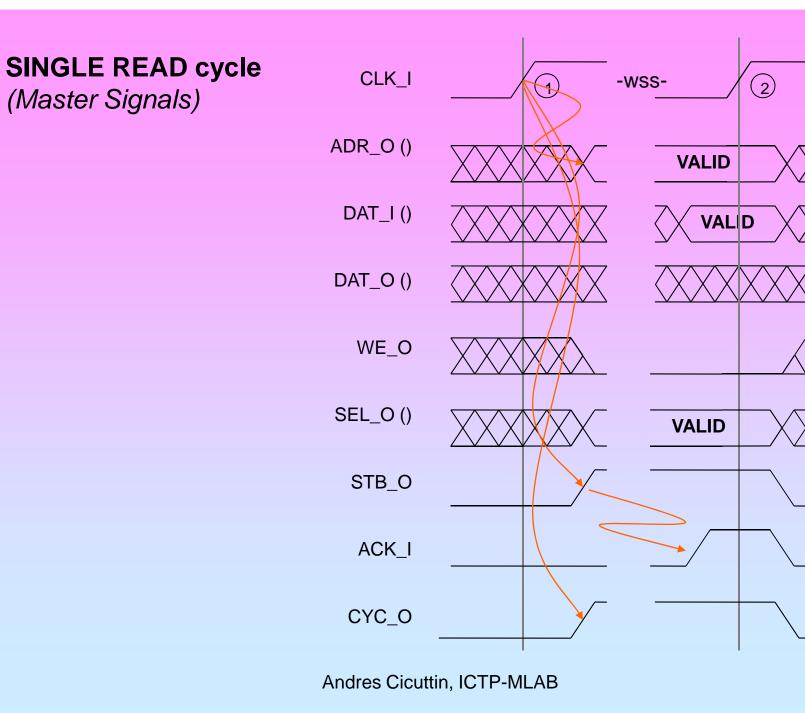

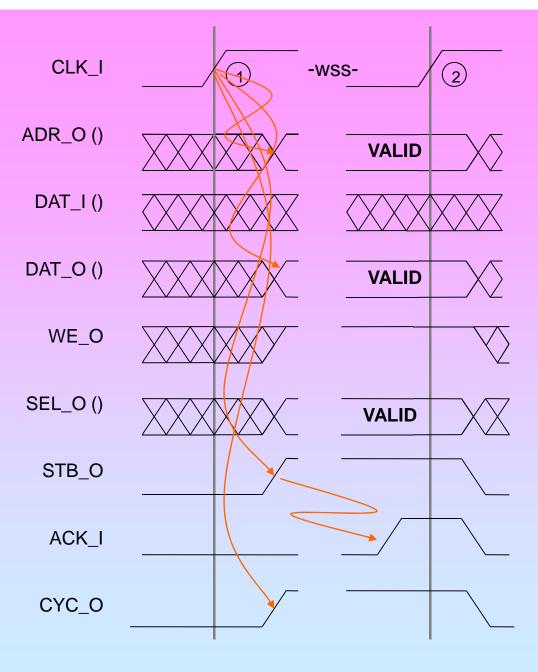

### SINGLE WRITE cycle

(Master Signals)

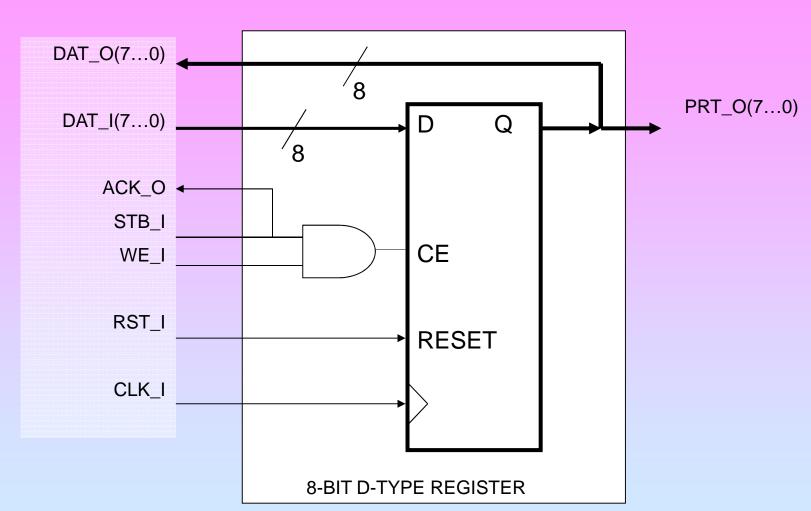

#### A Simple Example: WISHBONE SLAVE port

### VHDL implementation of the 8-bit output port interface (pag. 109)

#### library ieee; use ieee.std\_logic\_1164.all;

entity WBOPRT08 is port( -- WISHBONE SLAVE interface:

```

ACK_O: out std_logic;

CLK_I: in std_logic;

DAT_I: in std_logic_vector( 7 downto 0 );

DAT_O: out std_logic_vector( 7 downto 0 );

RST_I: in std_logic;

STB_I: in std_logic;

WE_I: in std_logic;

```

-- Output port (non-WISHBONE signals):

PRT\_O: out std\_logic\_vector( 7 downto 0)

);

```

end entity WBOPRT08;

```

```

architecture WBOPRT081 of WBOPRT08 is

signal Q: std_logic_vector( 7 downto 0 );

Begin

internal DAT I <= DAT I;

REG: process(CLK I)

begin

if(rising edge(CLK I)) then

if (RST I = '1') then --synchronous reset

Q <= B"0000000";

elsif( (STB I and WE I) = '1') then

Q \le internal DAT I(7 downto 0);

else

Q <= Q;

end if:

end if;

end process REG;

ACK O <= STB_I; --(Asynchronous assignments !)

DAT O \leq Q;

PRT O \leq Q;

end architecture WBOPRT081;

```

### **WB Clasic Bus Cycles**

**BLOCK READ**

(Page 54)

**BLOCK WRITE**

RMW (Read-Modify-Write)

(Page 57)

(Page 60)

### **Other WB Bus Cycles** (WISHBONE Registered Feedback)

Both Master and Slave MUST support "Cycle Type Identifier": [CTI\_O()], [CTI\_I()]

#### 4.2 Signal Description

| <b>CTI_IO()</b> The Cycle Type Identifier [CTI_IO()] Address Tag provides additional                                                                                | Table 4-2 Cycle Type Identifiers |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| information about the current cycle. The MASTER sends this information to the SLAVE. The SLAVE can use this information to prepare the response for the next cycle. | CTI_O(2:0) Description           |

|                                                                                                                                                                     | '000' Classic cycle.             |

| PERMISSION 4.05                                                                                                                                                     | '001' Constant                   |

| MASTER and SLAVE interfaces MAY be designed to support the [CTI_I()]                                                                                                | address burst cycle              |

| and [CTI_O()] signals. Also MASTER and SLAVE interfaces MAY be<br>designed to support a limited number of burst types.                                              | '010' Incrementing               |

| designed to support a limited number of burst types.                                                                                                                | burst cycle                      |

| RULE 4.05                                                                                                                                                           | '011' Reserved                   |

| MASTER and SLAVE interfaces that do support the [CTI_I()] and                                                                                                       | '100' Reserved                   |

| [CTI_O()] signals MUST at least support the Classic cycle<br>[CTI_IO()='000'] and the End-of-Cycle [CTI_IO()='111'].                                                | '101 Reserved                    |

|                                                                                                                                                                     | '110' Reserved                   |

| <b>RULE 4.10</b><br>MASTER and SLAVE interfaces that are designed to support a limited<br>number of burst types MUST complete the                                   | '111' End-of-Burst               |

|                                                                                                                                                                     |                                  |

### **Other WB Bus Cycles**

**Classic Cycle** (with wait states –ws-)

(Page 77)

(Page 83)

#### **Constant Address Burst**

(e.g. for fifos, ports, etc)

#### **Incrementing Burst Cycle**

(Page 86)

An incrementing burst is defined as multiple accesses to consecutive addresses. Each transfer the address is incremented. The increment is dependent on the data array [DAT\_O()], [DAT\_I()] size; for an 8bit data array the increment is 1, for a 16bit data array the increment is 2, for a 32bit data array the increment is 4, etc.

All the information related to the

Wishbone SoC Architecture Specification

is contained in its official documentation:

### wbspc\_b3.pdf

•It is very clear and easy to read and understand

•It includes design examples

•The specification doesn't infringe patents, copyright, trademarks or trade secret rights of others

# Conclusion

- 1. There are many and very good reasons to adopt the **Wishbone SoC Architecture Specification** as the standard interface for open-source projects such as the **Reconfigurable Virtual Instrumentation** project proposed by ITCP.

- 2. Your are strongly encouraged to use it to develop reusable IP blocks that can be easily shared by a large community of users and developers