2499-7

International Training Workshop on FPGA Design for Scientific Instrumentation and Computing

11 - 22 November 2013

Introduction to VLSI Digital Design Scaling

> Sandro BONACINI CERN, Geneva Switzerland

# Outline

- Introduction

- Transistors

- The CMOS inverter

- Technology

- Scaling

- Scaling objectives

- Scaling variables

- Scaling consequences

- Gates

- Sequential circuits

- Storage elements

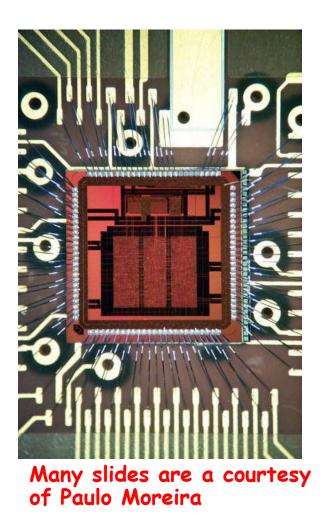

# Technology scaling

- Technology scaling has a <u>threefold</u> <u>objective</u>:

- Increase the transistor density

- Reduce the gate delay

- Reduce the power consumption

- At present, between two technology generations, the objectives are:

- Doubling of the transistor density;

- Reduction of the gate delay by 30% (43% increase in frequency);

- Reduction of the power by 50% (at 43% increase in frequency);

## Technology scaling

- How is scaling achieved?

- All the device dimensions (lateral and vertical) are reduced by  $1/\alpha$

- Concentration densities are increased by  $\alpha$  to make the junctions depletion region smaller by  $1/\alpha$

- Device voltages reduced by  $1/\alpha$  (for constant field)

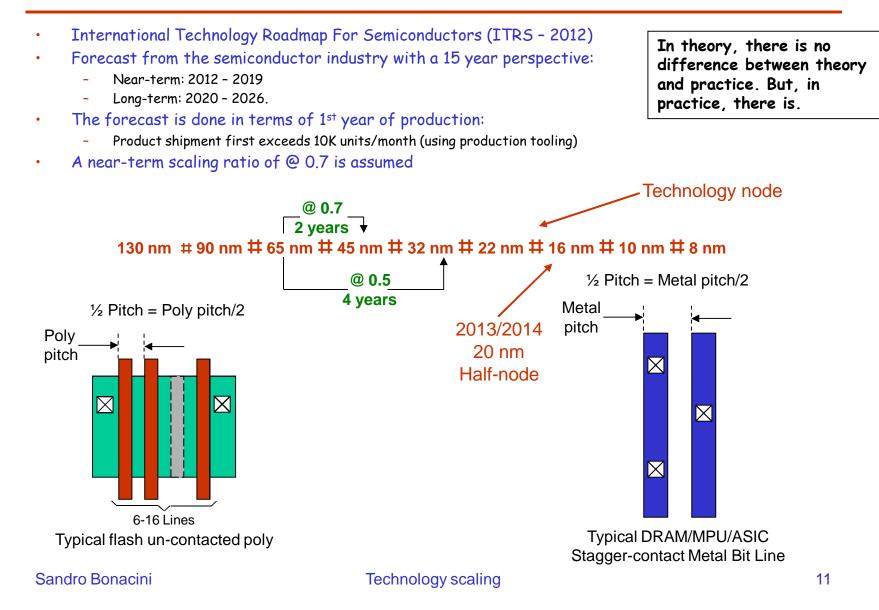

- Typically  $1/\alpha = 0.7$  (30% reduction in the dimensions)

# Technology scaling

#### • The scaling variables are:

| <ul> <li>Supply voltage:</li> </ul>       | $V_{dd}$        | $\rightarrow$ | V <sub>dd</sub> / $\alpha$ |

|-------------------------------------------|-----------------|---------------|----------------------------|

| <ul> <li>Gate length:</li> </ul>          | L               | $\rightarrow$ | L/α                        |

| <ul> <li>Gate width:</li> </ul>           | W               | $\rightarrow$ | <b>W /</b> α               |

| <ul> <li>Gate-oxide thickness:</li> </ul> | † <sub>ox</sub> | $\rightarrow$ | $t_{ox}$ / $\alpha$        |

| <ul> <li>Junction depth:</li> </ul>       | Xj              | $\rightarrow$ | <b>Χ</b> j / α             |

| <ul> <li>Substrate doping:</li> </ul>     | Ň <sub>A</sub>  | $\rightarrow$ | $N_A \times \alpha$        |

This is called <u>constant field</u> scaling because the electric field across the gate-oxide does not change when the technology is scaled

If the power supply voltage is maintained constant the scaling is called <u>constant voltage</u>. In this case, the electric field across the gate-oxide increases as the technology is scaled down.

Due to gate-oxide breakdown, below  $0.8\mu m$  only "constant field" scaling is used.

#### Scaling consequences

Some consequences of 30% scaling in the constant field regime ( $\alpha = 1.43$ ,  $1/\alpha = 0.7$ ):

• Device/die area:

$W \times L \rightarrow (1/\alpha)^2 = 0.49$

- "Historically", microprocessor <u>die size grows</u> about 25% per technology generation! This is a result of added functionality.

- Transistor density:

(unit area) /(W  $\times$  L)  $\rightarrow$   $\alpha^2$  = 2.04

- In practice, <u>memory density</u> has been scaling as expected.

### Scaling consequences

• Gate capacitance:

W × L /

$$t_{ox} \rightarrow 1/\alpha = 0.7$$

• Drain current:

(W/L)

$$\times$$

(V²/t<sub>ox</sub>)  $\rightarrow$  1/ $\alpha$  = 0.7

• Gate delay:

$(C \times V) / I \rightarrow 1/\alpha = 0.7$ Frequency  $\rightarrow \alpha = 1.43$

In practice, microprocessor frequency has doubled every technology generation (2 to 3 years)! This faster increase rate is due to super-pipelined architectures ("less gates per clock cycle")

### Scaling consequences

• Power:

$$C \times V^2 \times f \rightarrow (1/\alpha)^2 = 0.49$$

• Power density:

$$1/t_{ox} \times V^2 \times f \rightarrow 1$$

- In practice, the power density has been increasing faster than foreseen by the simple scaling theory. This is due to the faster than foreseen increase in frequency

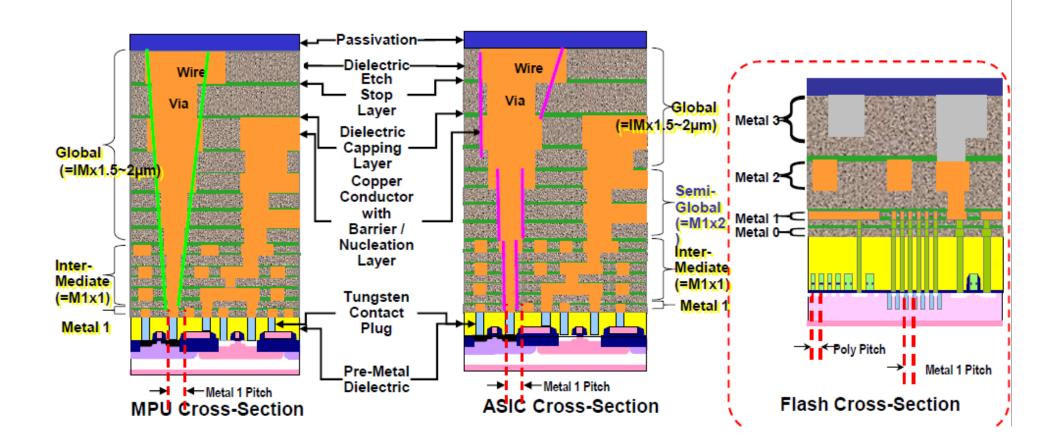

## Interconnects scaling

- Interconnects scaling:

- Higher densities are only possible if the interconnects also scale.

- Reduced width  $\rightarrow$  increased resistance

- Denser interconnects  $\rightarrow$  <u>higher capacitance</u>

- To account for <u>increased parasitics</u> and <u>integration</u> <u>complexity</u> more interconnection layers are added:

- thinner and tighter layers  $\rightarrow$  local interconnections

- thicker and sparser layers  $\rightarrow$  global interconnections and power

#### IC Cross Sections

Source: ITRS

Technology scaling

# Scaling table

| Supply voltage (Vdd) $1/\alpha$ $1/\alpha$ $1$ Length (L) $1/\alpha$ $1/\alpha$ $1/\alpha$ Width (W) $1/\alpha$ $1/\alpha$ $1/\alpha$ Gate-oxide thickness (tox) $1/\alpha$ $1/\alpha$ $1/\alpha$ Junction depth (Xj) $1/\alpha$ $1/\alpha$ $1/\alpha$ Substrate doping (NA) $\alpha$ $\alpha$ $\alpha$ Electric field across gate oxide (E) $1$ $\alpha$ Depletion layer thickness $1/\alpha$ $1/\alpha$ Gate area (Die area) $1/\alpha^2$ $1/\alpha^2$ DeviceGate capacitance (load) (C) $1/\alpha$ $1/\alpha$ Drain-current (Idss) $1/\alpha$ $\alpha$ Transconductance (gm) $1/\alpha$ $\alpha^3$ Gate delay $1/\alpha^2$ $\alpha$ Gate delay $1/\alpha$ $1/\alpha^2$ Power density $1$ $\alpha^3$ Power-Delay product $1/\alpha^3$ $1/\alpha$ Sandro BonaciniTechnology scaling                                              | Parameter                               | Constant Field           | Cons         | tant Voltage   |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------------|--------------|----------------|

| Width (W) $1/\alpha$ $1/\alpha$ $1/\alpha$ $1/\alpha$ Gate-oxide thickness ( $t_{ox}$ ) $1/\alpha$ $1/\alpha$ $1/\alpha$ Junction depth ( $X_j$ ) $1/\alpha$ $1/\alpha$ $1/\alpha$ Substrate doping ( $N_A$ ) $\alpha$ $\alpha$ $\alpha$ Electric field across gate oxide (E)1 $\alpha$ Depletion layer thickness $1/\alpha$ $1/\alpha$ Gate area (Die area) $1/\alpha^2$ $1/\alpha^2$ Gate capacitance (load) (C) $1/\alpha$ $1/\alpha$ Drain-current ( $I_{dss}$ ) $1/\alpha$ $\alpha$ Transconductance ( $g_m$ ) $1/\alpha$ $\alpha$ Gate delay $1/\alpha$ $\alpha$ Current density $\alpha$ $\alpha^3$ Power density1 $\alpha^3$ Power-Delay product $1/\alpha^3$ $1/\alpha$                                                                                                                                                  | Supply voltage (V <sub>dd</sub> )       | 1/α                      | 1            | ↑ <sup>−</sup> |

| Gate-oxide thickness $(t_{ox})$ $1/\alpha$ $1/\alpha$ $1/\alpha$ $1/\alpha$ VariablesJunction depth $(X_j)$ $1/\alpha$ $1/\alpha$ $1/\alpha$ $1/\alpha$ $1/\alpha$ $1/\alpha$ Substrate doping $(N_A)$ $\alpha$ $\alpha$ $\alpha$ $\alpha$ Electric field across gate oxide (E)1 $\alpha$ $\alpha$ Depletion layer thickness $1/\alpha$ $1/\alpha$ $1/\alpha$ Gate area (Die area) $1/\alpha^2$ $1/\alpha^2$ DeviceGate capacitance (load) (C) $1/\alpha$ $1/\alpha$ RepercussionDrain-current ( $I_{dss}$ ) $1/\alpha$ $\alpha$ $\alpha^3$ Transconductance ( $g_m$ ) $1/\alpha$ $\alpha^3$ $\alpha^3$ Gate delay $1/\alpha^2$ $\alpha^3$ $\alpha^3$ DC & Dynamic power dissipation $1/\alpha^3$ $1/\alpha$ $\alpha^3$ Power-Delay product $1/\alpha^3$ $1/\alpha$ $1/\alpha$                                                    | Length (L)                              | 1/α                      | 1/α          |                |

| Gate-oxide thickness $(t_{ox})$ $1/\alpha$ $1/\alpha$ $1/\alpha$ $1/\alpha$ VariablesJunction depth $(X_j)$ $1/\alpha$ $1/\alpha$ $1/\alpha$ $1/\alpha$ $1/\alpha$ $1/\alpha$ $1/\alpha$ Substrate doping $(N_A)$ $\alpha$ $\alpha$ $\alpha$ $\alpha$ $\alpha$ $\alpha$ Electric field across gate oxide (E)1 $\alpha$ $1/\alpha$ $1/\alpha$ Depletion layer thickness $1/\alpha$ $1/\alpha$ $1/\alpha$ $1/\alpha$ Gate area (Die area) $1/\alpha^2$ $1/\alpha^2$ $1/\alpha^2$ DeviceGate capacitance (load) (C) $1/\alpha$ $1/\alpha$ $\alpha$ $1/\alpha^2$ $\alpha$ Drain-current ( $I_{dss}$ ) $1/\alpha$ $\alpha$ $\alpha^3$ $1/\alpha^2$ $\alpha^3$ Gate delay $1/\alpha$ $1/\alpha^2$ $\alpha$ $\alpha^3$ $Circuit$ Gate delay $1/\alpha^2$ $\alpha^3$ $\alpha^3$ $Circuit$ Power density1 $\alpha^3$ $1/\alpha$ $1/\alpha$ | Width (W)                               | 1/α                      | 1/α          | Scaling        |

| Junction depth $(X_j)$ $1/\alpha$ $1/\alpha$ $1/\alpha$ Substrate doping $(N_A)$ $\alpha$ $\alpha$ Electric field across gate oxide (E)1 $\alpha$ Depletion layer thickness $1/\alpha$ $1/\alpha$ Gate area (Die area) $1/\alpha^2$ $1/\alpha^2$ Gate capacitance (load) (C) $1/\alpha$ $1/\alpha$ Drain-current ( $I_{dss}$ ) $1/\alpha$ $\alpha$ Transconductance ( $g_m$ )1 $\alpha$ Gate delay $1/\alpha$ $\alpha^3$ Current density $\alpha$ $\alpha^3$ Power density1 $\alpha^3$ Power-Delay product $1/\alpha^3$ $1/\alpha$                                                                                                                                                                                                                                                                                                | Gate-oxide thickness (t <sub>ox</sub> ) | 1/α                      | 1/α          | •              |

| Electric field across gate oxide (E)1 $\alpha$ Depletion layer thickness $1/\alpha$ $1/\alpha$ Gate area (Die area) $1/\alpha^2$ $1/\alpha^2$ Gate capacitance (load) (C) $1/\alpha$ $1/\alpha$ Drain-current ( $I_{dss}$ ) $1/\alpha$ $\alpha$ Transconductance ( $g_m$ ) $1/\alpha$ $\alpha$ Gate delay $1/\alpha$ $1/\alpha^2$ Current density $\alpha$ $\alpha^3$ Dower density $1/\alpha^3$ $1/\alpha$                                                                                                                                                                                                                                                                                                                                                                                                                       | Junction depth (Xi)                     | 1/α                      | 1/α          |                |

| Depletion layer thickness $1/\alpha$ $1/\alpha$ Gate area (Die area) $1/\alpha^2$ $1/\alpha^2$ $1/\alpha^2$ Gate capacitance (load) (C) $1/\alpha$ $1/\alpha$ $1/\alpha$ Drain-current ( $I_{dss}$ ) $1/\alpha$ $\alpha$ Transconductance ( $g_m$ ) $1/\alpha$ $\alpha$ Gate delay $1/\alpha$ $1/\alpha^2$ Current density $\alpha$ $\alpha^3$ DC & Dynamic power dissipation $1/\alpha^2$ $\alpha$ Power density $1$ $\alpha^3$ Power-Delay product $1/\alpha^3$ $1/\alpha$                                                                                                                                                                                                                                                                                                                                                      | Substrate doping (N <sub>A</sub> )      | α                        | α            |                |

| Gate area (Die area) $1/\alpha^2$ $1/\alpha^2$ $1/\alpha^2$ Device<br>RepercussionGate capacitance (load) (C) $1/\alpha$ $1/\alpha$ $1/\alpha$ RepercussionDrain-current ( $I_{dss}$ ) $1/\alpha$ $\alpha$ $\alpha$ $\alpha$ Transconductance ( $g_m$ ) $1/\alpha$ $\alpha$ $1/\alpha^2$ $\alpha$ Gate delay $1/\alpha$ $1/\alpha^2$ $\alpha$ $\alpha^3$ Current density $\alpha$ $\alpha^3$ $\alpha^3$ CircuitDC & Dynamic power dissipation $1/\alpha^2$ $\alpha$ $\alpha^3$ Power density $1$ $\alpha^3$ $1/\alpha$ $1/\alpha$                                                                                                                                                                                                                                                                                                 | Electric field across gate oxide (E)    | 1                        | α            | Ť              |

| Gate capacitance (load) (C) $1/\alpha$ $1/\alpha$ RepercussionDrain-current ( $I_{dss}$ ) $1/\alpha$ $\alpha$ Transconductance ( $g_m$ ) $1/\alpha$ $\alpha$ Gate delay $1/\alpha$ $1/\alpha^2$ Current density $\alpha$ $\alpha^3$ DC & Dynamic power dissipation $1/\alpha^2$ $\alpha$ Power density $1$ $\alpha^3$ Power-Delay product $1/\alpha^3$ $1/\alpha$                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Depletion layer thickness               | 1/α                      | 1/α          |                |

| Gate capacitance (load) (C) $1/\alpha$ $1/\alpha$ RepercussionDrain-current ( $I_{dss}$ ) $1/\alpha$ $\alpha$ $\alpha$ Transconductance ( $g_m$ )1 $\alpha$ $1/\alpha^2$ Gate delay $1/\alpha$ $1/\alpha^2$ $\alpha$ Current density $\alpha$ $\alpha^3$ $\alpha$ DC & Dynamic power dissipation $1/\alpha^2$ $\alpha$ Power density1 $\alpha^3$ $1/\alpha$ Power-Delay product $1/\alpha^3$ $1/\alpha$                                                                                                                                                                                                                                                                                                                                                                                                                           | Gate area (Die area)                    | <b>1/</b> α <sup>2</sup> | <b>1/</b> α² | Device         |

| Drain-current $(I_{dss})$ $1/\alpha$ $\alpha$ Transconductance $(g_m)$ 1 $\alpha$ Gate delay $1/\alpha$ $1/\alpha^2$ Current density $\alpha$ $\alpha^3$ DC & Dynamic power dissipation $1/\alpha^2$ $\alpha$ Power density1 $\alpha^3$ Power-Delay product $1/\alpha^3$ $1/\alpha$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Gate capacitance (load) (C)             | 1/α                      | 1/α          |                |

| Gate delay $1/\alpha$ $1/\alpha^2$ Current density $\alpha$ $\alpha^3$ DC & Dynamic power dissipation $1/\alpha^2$ $\alpha$ Power density1 $\alpha^3$ Power-Delay product $1/\alpha^3$ $1/\alpha$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Drain-current (I <sub>dss</sub> )       | 1/α                      | α            |                |

| Current density $\alpha$ $\alpha^3$ CircuitDC & Dynamic power dissipation $1/\alpha^2$ $\alpha$ RepercussionPower density1 $\alpha^3$ $1/\alpha$ Power-Delay product $1/\alpha^3$ $1/\alpha$ $1/\alpha$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Transconductance (g <sub>m</sub> )      | 1                        | α            | Ļ              |

| DC & Dynamic power dissipation $1/\alpha^2$ $\alpha$ CircuitPower density1 $\alpha^3$ RepercussionPower-Delay product $1/\alpha^3$ $1/\alpha$ $\sqrt{2}$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Gate delay                              | 1/α                      | $1/\alpha^2$ | Ť              |

| DC & Dynamic power dissipation $1/\alpha^2$ $\alpha$ RepercussionPower density1 $\alpha^3$ $1/\alpha^3$ I/ $\alpha$ Power-Delay product $1/\alpha^3$ $1/\alpha$ I/ $\alpha$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Current density                         | α                        | $\alpha^3$   |                |

| Power density1 $\alpha^3$ Power-Delay product $1/\alpha^3$ $1/\alpha$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | DC & Dynamic power dissipation          | $1/\alpha^2$             | α            |                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Power density                           | 1                        | $\alpha^3$   | Repercussion   |

| Sandro Bonacini Technology scaling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Power-Delay product                     | <b>1/</b> α <sup>3</sup> | 1/α          | Ļ              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Sandro Bonacini                         | Technology scaling       |              | 1              |

## 2013 and beyond ...

## 2013 and beyond ...

| ITRS Road Map, 2012 edition:                     | 2013    | 2017   | 2020   | 2023 (year of first production)          |

|--------------------------------------------------|---------|--------|--------|------------------------------------------|

| Gate length, physical (nm)                       | 20      | 14     | 11     | 8 (7 years for $\frac{1}{2}$ L, 2 nodes) |

| Gate length, printed (nm)                        | 28      | 17.7   | 12.5   | 8.8                                      |

| Flash Poly ½ pitch (nm)                          | 18      | 13     | 10     | 8 (flash drives the scaling)             |

| DRAM $\frac{1}{2}$ pitch (nm)                    | 28      | 179    | 12.6   | 8.9                                      |

| Wafer diameter (mm)                              | 300     | 450    | 450    | 450 (wafers getting larger)              |

| Wiring levels (maximum)                          | 13      | 14     | 14     | 15 (tall metal stack)                    |

| DRAM:                                            |         |        |        |                                          |

| Bits/chip (Gbits)                                | 4.29    | 8.59   | 34.36  | 34.36 (increase and saturate)            |

| Chip size (mm <sup>2</sup> )                     | 35      | 19     | 37     | 19 (small chips for low-cost bits)       |

| Gbits/cm <sup>2</sup>                            | 12.24   | 46.25  | 92.5   | 185                                      |

| Flash:                                           |         |        |        |                                          |

| Bits/chip (Gbits) SLC                            | 69      | 137    | 275    | 412 (3D flash starts in 2016)            |

| Chip size (mm <sup>2</sup> )                     | 149.8   | 135.88 | 162.42 | 158.13                                   |

| Gbits/cm <sup>2</sup>                            | 45.9    | 101    | 169    | 261                                      |

| Bits/chip (Gbits) MLC [3D 2 bits/o               | cell] - | 550    | 1100   | 2199 (end of hard disks??)               |

| Chip size (mm <sup>2</sup> )                     | -       | 159.82 | 102.73 | 124.03                                   |

| Gbits/cm <sup>2</sup>                            | -       | 344    | 1070   | 1770                                     |

| μP (high performance):                           |         |        |        |                                          |

| Transistors/chip (Millions)                      | 8848    | 17696  | 35391  | 70782 (doubling cores)                   |

| Chip size (mm <sup>2</sup> )                     | 260     | 206    | 206    | 206 (small chips for cheap MIPS)         |

| Transistors/cm <sup>2</sup> (M/cm <sup>2</sup> ) | 3403    | 8575   | 17150  | 34300                                    |

| Total pads                                       | 3072    | 3072   | 3072   | 3072 (66.7% for power/ground)            |

| Performance:                                     |         |        |        |                                          |

| On-Chip clock (GHz)                              | 4       | 4.74   | 5.33   | 6 (saturate)                             |

| GFLOPs [Not ITRS data!] ~<br>Power supply:       | 100 (*) | 237    | 533    | 1200 [not ITRS data!]                    |

| Vdd (V):                                         | 0.85    | 0.75   | 0.68   | 0.62 (low-power for freg. increase)      |

| Maximum allowable power (W)                      | 149     | 130    | 130    | ? (With heat sink)                       |