2572-9

#### Winter College on Optics: Fundamentals of Photonics - Theory, Devices and Applications

10 – 21 February 2014

Photonic packaging and integration technologies I

Sonia M. García Blanco University of Twente The Netherlands

### **UNIVERSITY OF TWENTE.**

## Photonic packaging and integration technologies I

Winter School on Optics ICTP, Trieste, February 2014 Sonia M. García Blanco, University of Twente

### UNIVERSITY OF TWENTE: NETHERLANDS

UNIVERSITY OF TWENTE.

### ... ENSCHEDE ....

### CAMPUS OF THE UNIVERSITY OF TWENTE

**UNIVERSITY OF TWENTE.**

26/02/2014 4

### **MESA+ INSTITUTE FOR NANOTECHNOLOGY**

# PHOTONIC PACKAGING AND INTEGRATION TECHNOLOGIES

[Lars Zimmerman, Helios, Silicon Photonics course] [P. O'Brien, Tyndall National Institute, Cork, Ireland]

# PACKAGING GOALS

- Protect devices from environment

- Provide the correct atmosphere for proper functioning (vacuum, nitrogen)

- Interaction of device with environment:

- Electrical signals Optical signals: transparent window, optical waveguides, fibers Fluidics

- Pressure, gases, etc

- Increase reliability

- Low cost

- Small size

### LECTURE LEARNING GOALS

1. Get an overview of different available packaging and integration technologies

- 2. Get a "feeling" for the challenges of packaging

- 3. Acquire a "design-for-packaging" attitude

### OUTLINE

- 1. Packaging of LEDs, detectors and image sensors

- 2. Packaging of photonic devices

- 3. Hybrid and heterogeneous integration technologies

# PACKAGING OF LEDS, DETECTORS AND IMAGE SENSORS

- Die-level versus wafer level packaging

- Overview of bonding technologies

- <u>Example</u>: Wafer level packaging of microbolometer detectors

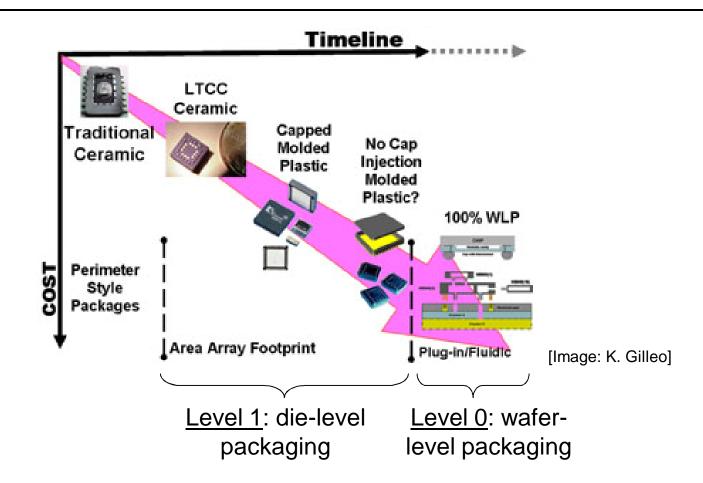

# TRENDS ON LED, DETECTOR AND IMAGE SENSOR PACKAGING

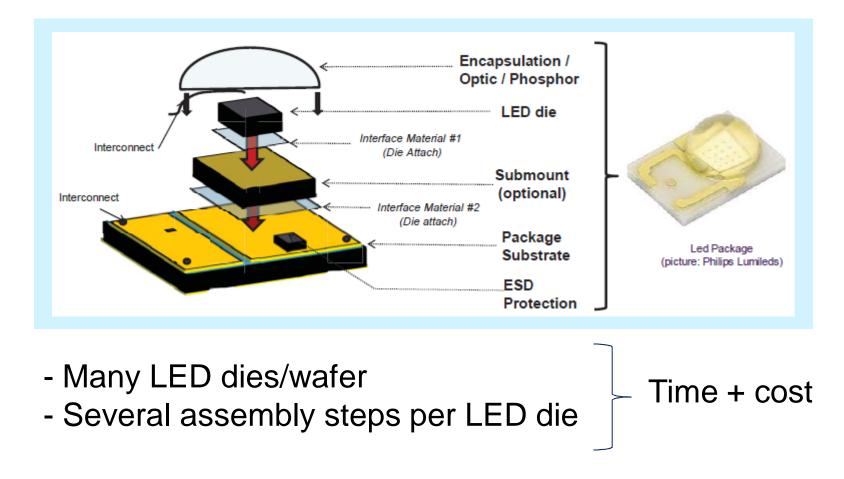

### CHIP LEVEL PACKAGING OF LEDs

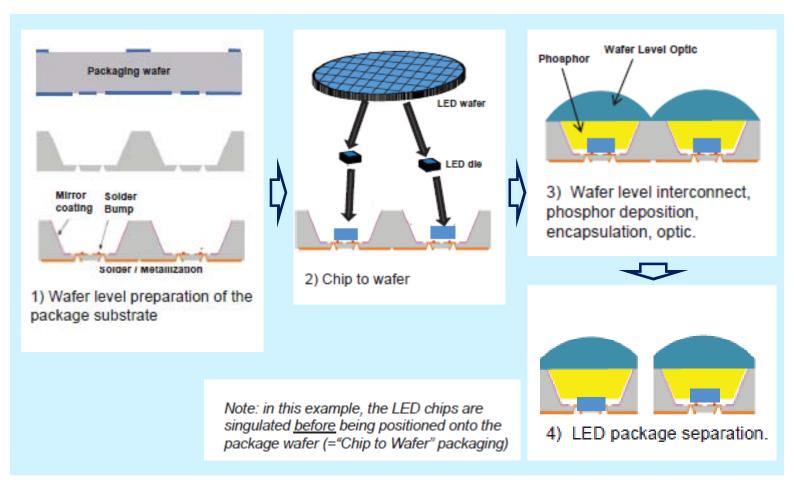

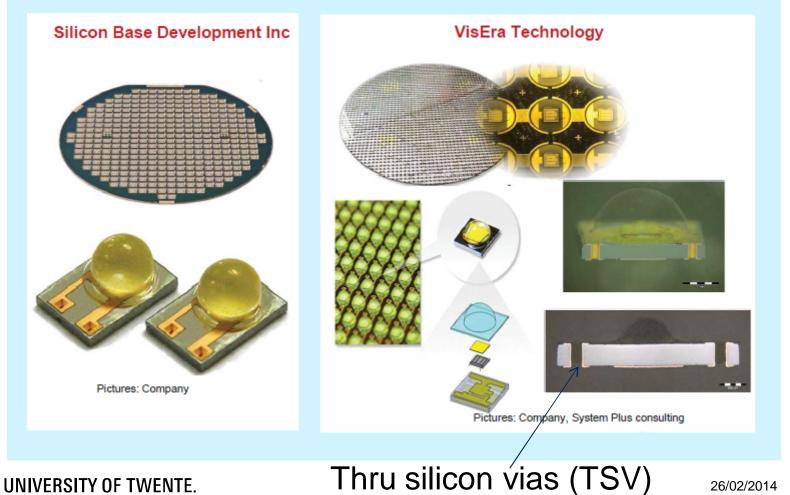

### WAFER LEVEL PACKAGING OF LEDs

**UNIVERSITY OF TWENTE.**

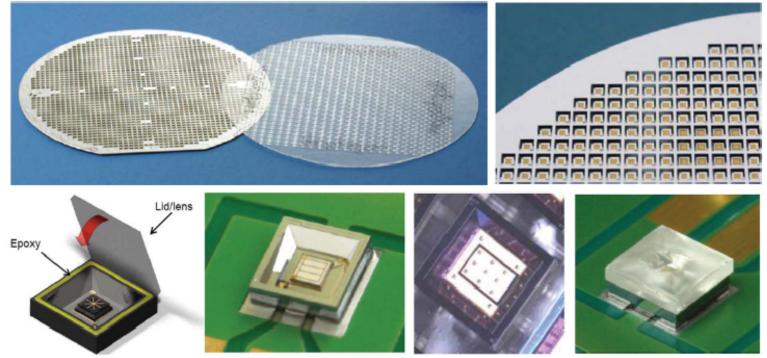

### WAFER LEVEL PACKAGING OF LEDs

#### Hymite (technology acquired by Touch Microsystem Technology in 2010)

Courtesy of Hymite

[Yole Development, Semicon West 2011]

#### UNIVERSITY OF TWENTE.

### WAFER LEVEL PACKAGING OF LEDs

15

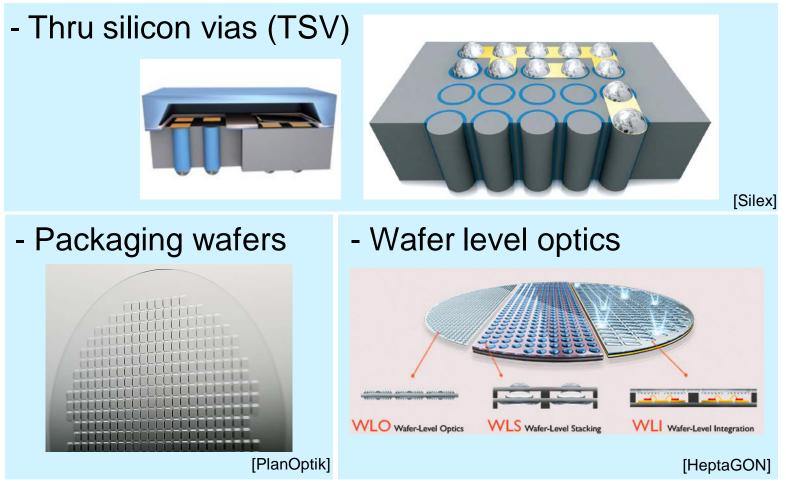

## **TECHNOLOGIES FOR WAFER LEVEL PACKAGING**

**UNIVERSITY OF TWENTE.**

# PACKAGING OF LEDS, DETECTORS AND IMAGE SENSORS

- Die-level versus wafer level packaging

- Overview of bonding technologies

- <u>Example</u>: Wafer level packaging of microbolometer detectors

## **BONDING TECHNIQUES**

| Technique Advantages       |                               | Disadvantages                        |

|----------------------------|-------------------------------|--------------------------------------|

| Bonding without interlayer | Hermetic                      | Flat surface required                |

| Direct                     | Strong bond                   | High-T                               |

| Plasma activated           | Low T                         | Complex equipment                    |

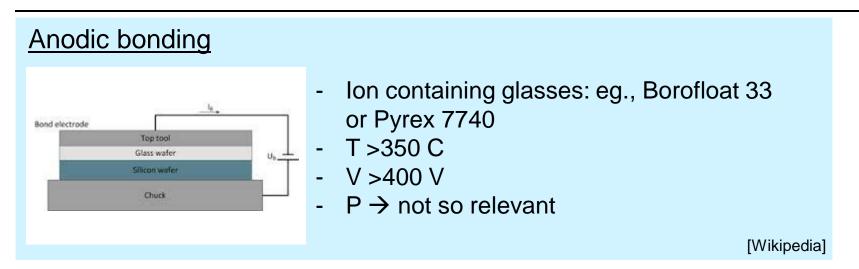

| Anodic                     | Strong bond                   | High T, high voltage,<br>ionic glass |

| Metallic interlayer        | Hermetic, non flat surface OK | Specific metals required             |

| Eutectic                   | Strong bond                   | Flat surface                         |

| Thermocompression          | More tolerant to flatness     | High pressure                        |

| Solder                     | Self-alignment                | Solder flow possible                 |

| Insulating layer           | Non flat surface ok           | Vary                                 |

| Glass frit                 | hermetic                      | High T, large bond area              |

| Adhesive                   | Versatile, low T              | Non hermetic                         |

### **DIRECT BONDING**

### REQUIREMENTS:

- Suitable surface chemistry (hybrophilicity vs hydrophobicity)

- Matching CTEs (otherwise stress-induced cracks)

- Smooth surfaces (<1.5 nm rms)

- Flat wafers (on cm-scale)

- No particles (voids larger than particles!)

- T>500C typically (depending on materials)

[D. Epstein, MIT]

### **DIRECT BONDING**

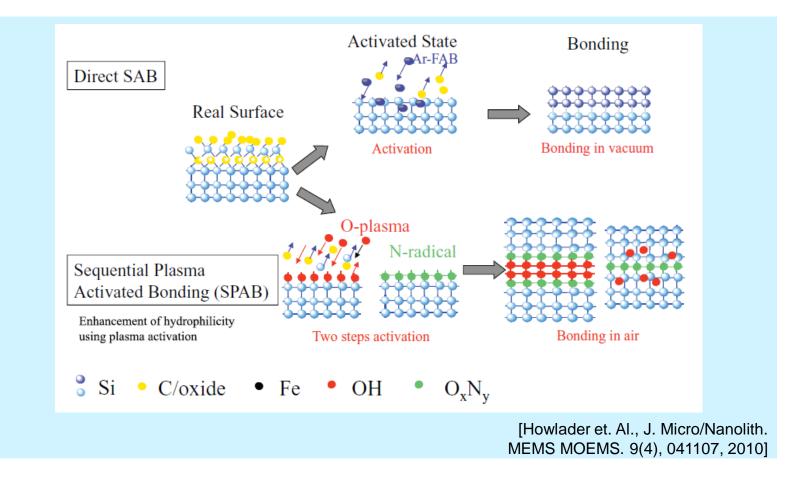

### PLASMA ACTIVATED DIRECT BONDING

Anneal Temperature <200 C

**UNIVERSITY OF TWENTE.**

### **ANODIC BONDING**

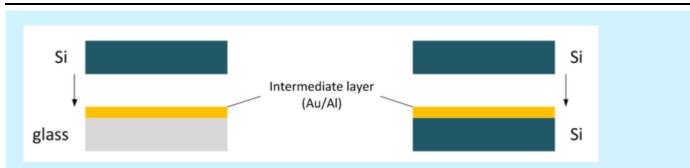

### **EUTECTIC BONDING**

- Tolerant to surface quality and wafer bow

- Low temperature process

- Sensitive to surface oxides

[Wikipedia]

| Materials | Composition    | Temperature |

|-----------|----------------|-------------|

| Au-Sn     | 80/20 wt%      | 280 C       |

| Au-Si     | 97.15/2.85 wt% | 370 C       |

| Au-Ge     | 28/72 wt%      | 361 C       |

| AI-Si     | 87.5/12.5 wt%  | 580 C       |

| Cu-Sn     | 5/95 wt%       | 231 C       |

| Au-In     | 0.6/99.4 wt%   | 156 C       |

26/02/2014 23

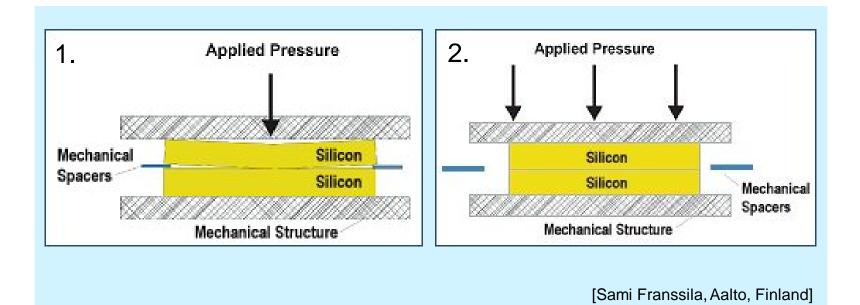

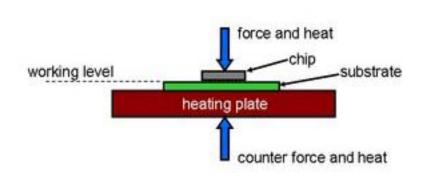

# METAL THERMOCOMPRESSION BONDING

[Suss Microtec]

### PROCESS:

- Metal between chip and substrate

- T

- Pressure

### **BONDING MECHANISM:**

- Breaking of surface oxides

- Interface formation

- Grain growth

| Metal | Temperature | Applied<br>Force<br>Range <sup>†</sup> | Time      | Atmo-<br>sphere                          |

|-------|-------------|----------------------------------------|-----------|------------------------------------------|

| Al    | 400-450°C   | >70KN                                  | 20-45 min | Vac or<br>H <sub>2</sub> /N <sub>2</sub> |

| Au    | 300-450°C   | >40KN                                  | 20-45 min | Vac or<br>H <sub>2</sub> /N <sub>2</sub> |

| Cu    | 380-450°C   | >30KN                                  | 20-60 min | Vac or<br>H <sub>2</sub> /N <sub>2</sub> |

**UNIVERSITY OF TWENTE.**

26/02/2014 24

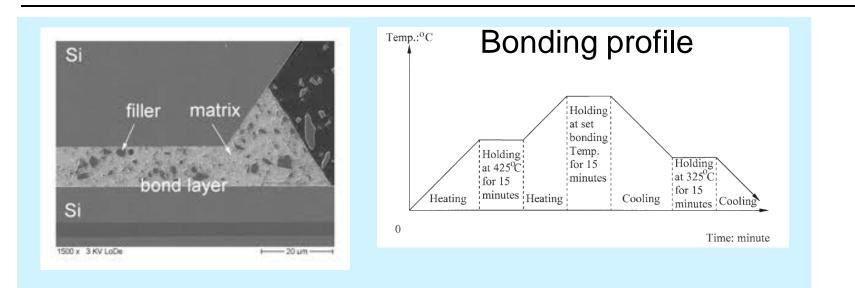

### **GLASS FRIT BONDING**

### Characteristics:

- T>400 C

- Tolerant to particles

- Tolerant to surface quality

- Possible voids

- Possible outgassing

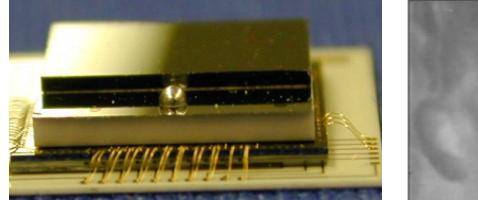

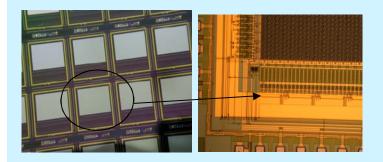

### EXAMPLE OF WAFER-LEVEL PACKAGING

### INO's µ-package:

160x120 pixel FPA 130 mK:

|                   | μ-pack     |

|-------------------|------------|

| Footprint (mmxmm) | 10.5 x 9.7 |

| Volume            | 60 μL      |

| Weight (g)        | 0.53       |

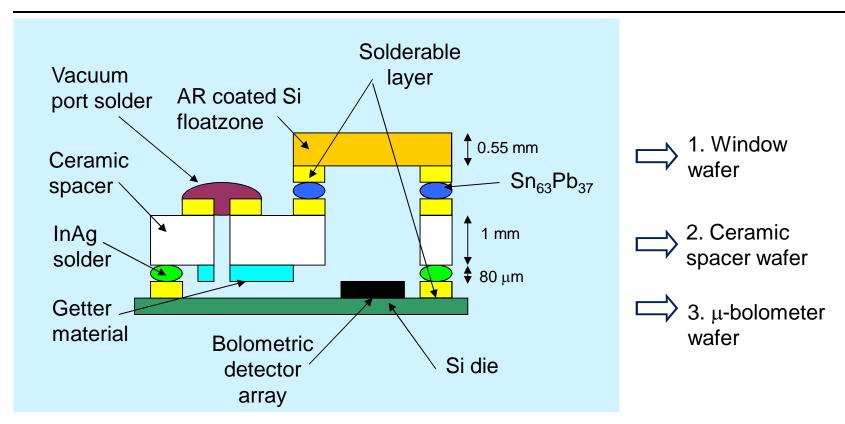

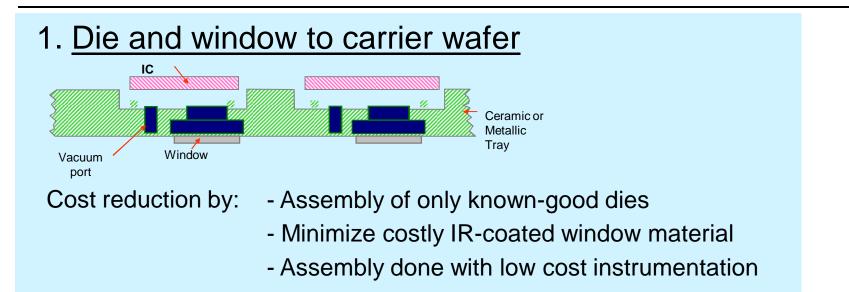

# CONCEPT OF LOW-T MICROPACKAGE

### Each level microfabricated at the wafer level

[S. García-Blanco et. al., « Hybrid wafer-level vacuum hermetic micropackaging technology for MOEMS-MEMS », Proc. SPIE 720602, 2009]

UNIVERSITY OF TWENTE.

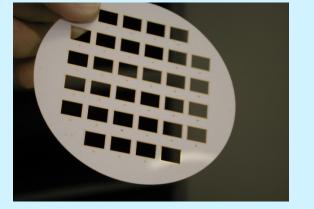

## CONCEPT OF LOW-T MICROPACKAGE

- 1. IR window wafer

- 2. Ceramic spacer wafer

### 3. Microbolometer wafer

Batch microfabrication technologies

#### Low cost devices

#### UNIVERSITY OF TWENTE.

## CONCEPT OF LOW-T MICROPACKAGE

### 2. Wafer-to-wafer bonding

UNIVERSITY OF TWENTE.

### OUTLINE

- 1. Packaging of LEDs, detectors and image sensors

- 2. Packaging of photonic devices

- 3. Hybrid and heterogeneous integration technologies

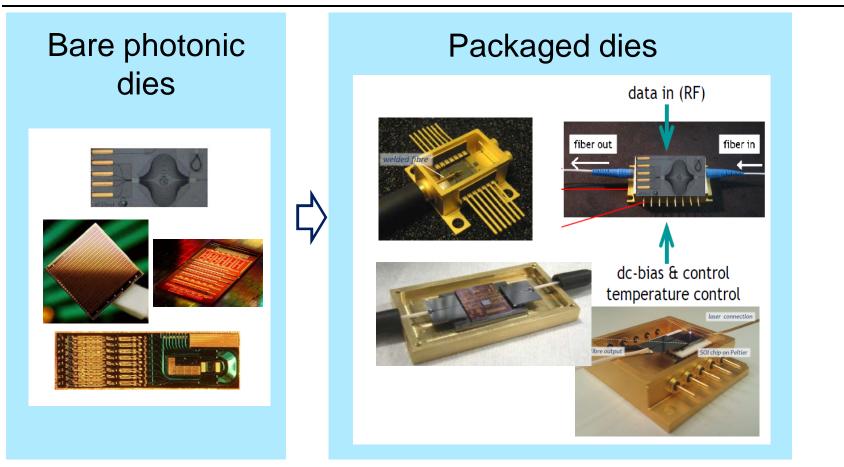

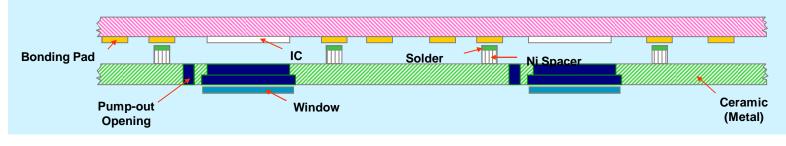

# PACKAGING OF PHOTONIC DEVICES

- 1. Two examples of packaging of photonic modules

- Laser diode in butterfly package

- Transmitter optical subassembly (TOSA)

- 2. "Fiber-to-the-chip" assembly strategies

- Ferrule welding

- Fiber array butt coupling (active vs passive alignment)

- Grating couplers

## PACKAGING OF PHOTONIC MODULES

Laser diode module package:

- Butterfly package

- Laser chip

- Thermistor

- Thermoelectric cooler

- Focusing lens

- Isolator

- Optical fiber

- Electrical leads

26/02/2014

### **EXAMPLES OF PACKAGES**

THE NEW VALUE FRONTIER.

Home Hens Products About

sents + Components for Fiber-Optic Communication Modules + Packages for Fiber-Optic Communication Modules

#### Packages for Fiber-Optic Communication

#### Modules

LO. Laser Diode, PD: Photodode, UK: Lithium Nobele, EA: Electro-Absorption, Mux / Demuz: Multiplexer / Demultiplexer, TO: Translator Outline, TOSA: Transmitter Optical Sub-Assembly; MOM: Multi-Chip Module, GFN: Guad Flat No Lead

\* STF PKGE is a registered insdemark of KYOCERA Corporation.

| Suntace Mount Rx Packages                                        | Cooled TO 8A Paokages                                            | Cooled TO Can Paokages                                |

|------------------------------------------------------------------|------------------------------------------------------------------|-------------------------------------------------------|

| -Surface Mount Package<br>-1003ops (4x25)                        | -Ceramic Feedthrough<br>-100Gbps (4x25) / 40Gbps<br>(4x10)       | -50R Impedance Matching<br>-Up to 10Gbps              |

| Mux / Demux Paokages                                             | Modulator Driver Paokages                                        | LN Modulator Paokages                                 |

| -Surface Mount BGA Package<br>-100Gbps (4x25) / 40Gbps<br>(2x20) | -Surface Mount QFN Package<br>-1008bps (4x25) / 408bps<br>(2x20) | -RF Connectors<br>-1005bps (4)(25) / 405bps<br>(1)(4) |

| Cooled TO BA Paokages                 | TO Can Paokages                                | 10 Ceramic Paokages                     |

|---------------------------------------|------------------------------------------------|-----------------------------------------|

| Ø 🔗                                   | <b>S</b>                                       | <i>\\</i>                               |

| Up to 18 pins<br>Up to 25Gops         | Thin-Film Submount<br>Attached<br>Up to 25Gbps | -GND In Ceramic Layers<br>-Up to 25Gbps |

| Burtace Mount MCM<br>Packages         | Mini Flat Packages                             | Butterity Type Packages<br>(BTF PKGS)   |

| Heat Sink Available                   | Surface Mount Package                          | -XLIND MEA Compatible<br>-Up to 408pcs  |

| Butterity Type Paokages<br>(BTF PK06) | Butterilly Type Paokages<br>(BTF PKGG)         | Butterity Type Packages<br>(BTF PKGS)   |

| Ceramic Feedbrough                    | 4 RF Connectors                                | RF Connector                            |

| -Up to 40Gbps                         | Up to 40Gbps                                   | -Up to 40Gbps                           |

|                                       |                                                | Semiconductor Components                |

[Kyocera] 26/02/2014

#### UNIVERSITY OF TWENTE.

33

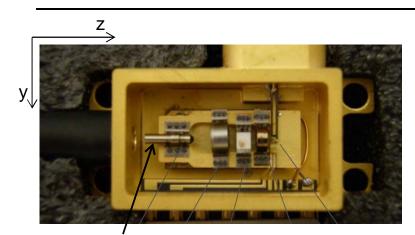

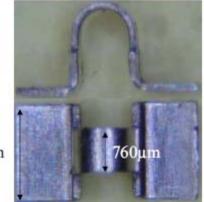

### **EXAMPLE 1**: LASER DIODE MODULE

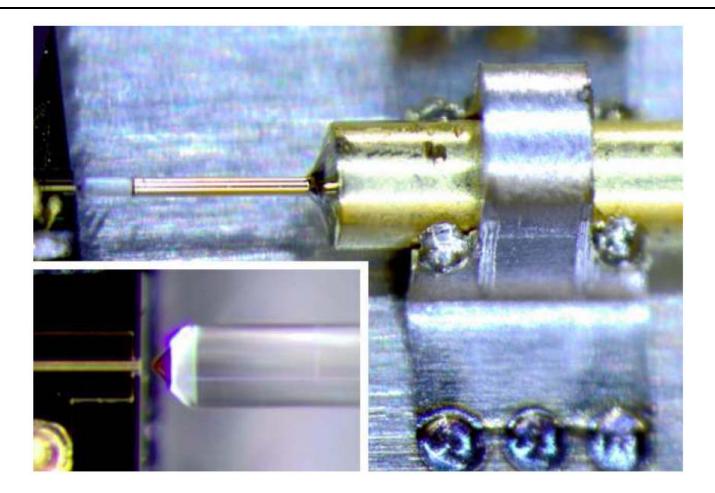

#### Welded fiber ferrule

1700µm

Ni weld clip

(Ni 99%+ Fe 0.4%+Cu 0.25% +etc)

#### **UNIVERSITY OF TWENTE.**

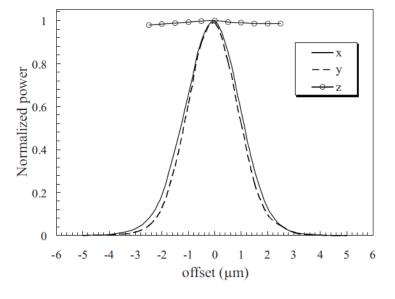

### Sensitivity to alignment errors:

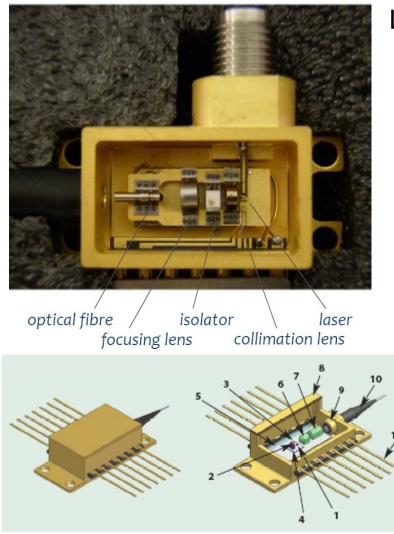

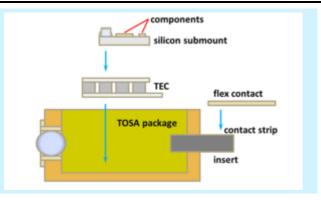

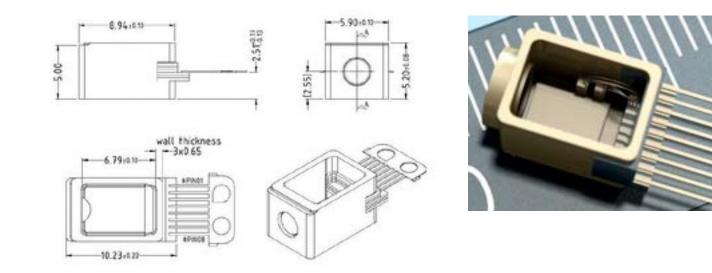

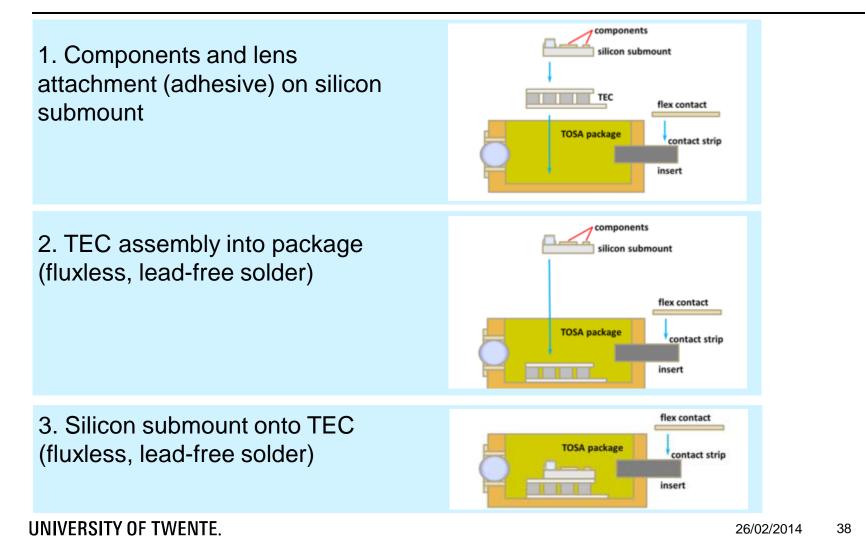

## EXAMPLE 2: ASSEMBLY OF A TRANSMITTER OPTICAL SUBASSEMBLY (TOSA) PACKAGE

1. Components and lens attachment (adhesive) on silicon submount

### **TOSA PACKAGE**

### TOSA package from TEC Microsystems

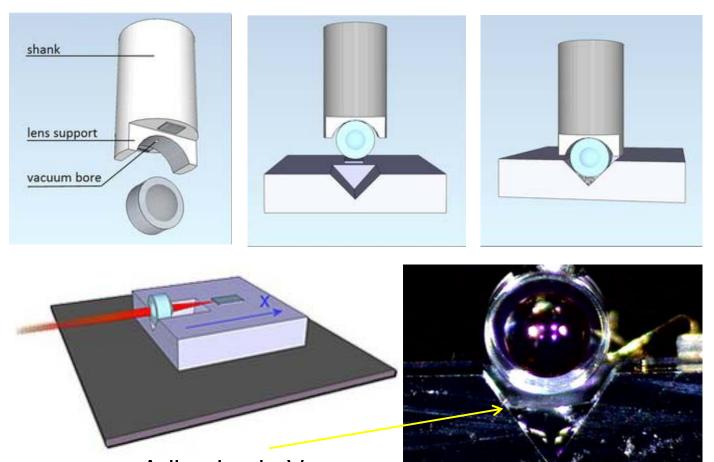

### LENS PLACEMENT

Adhesive in V-groove UNIVERSITY OF TWENTE.

### EXAMPLE 2: ASSEMBLY OF A TRANSMITTER OPTICAL SUBASSEMBLY (TOSA) PACKAGE

# PACKAGING OF PHOTONIC DEVICES

- 1. Two examples of packaging of photonic modules

- Laser diode in butterfly package

- Transmitter optical subassembly (TOSA)

- 2. Fiber-to-the-chip assembly strategies

- Ferrule welding

- Fiber array butt coupling (active vs passive alignment)

- Grating couplers

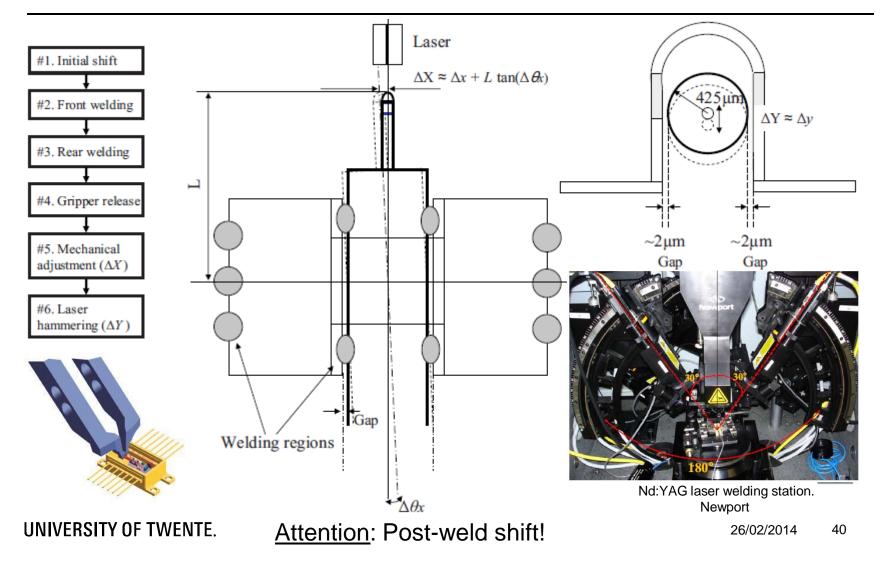

### FIBER WELDING

### FIBER WELDING

**UNIVERSITY OF TWENTE.**

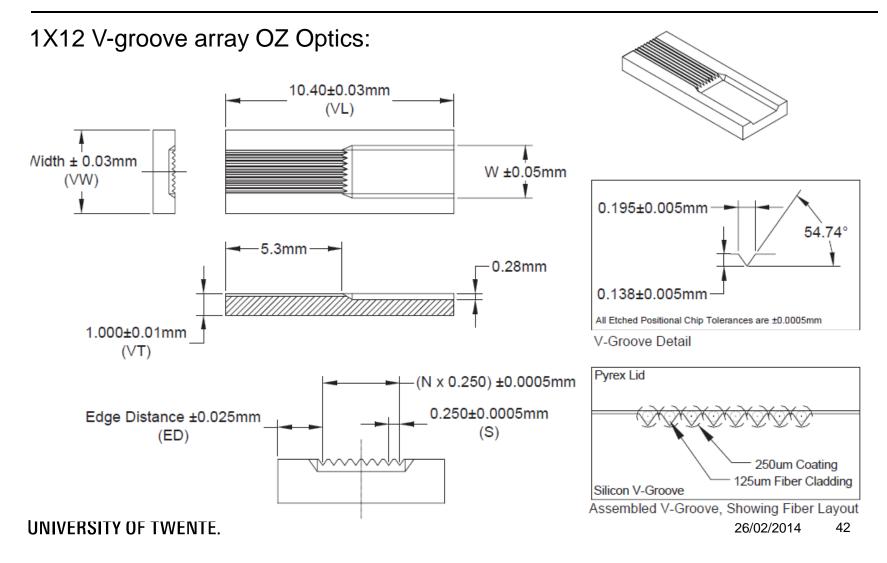

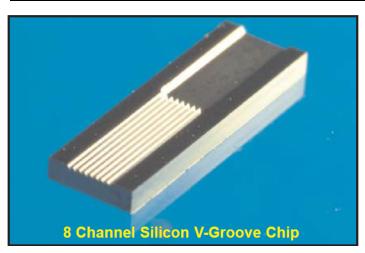

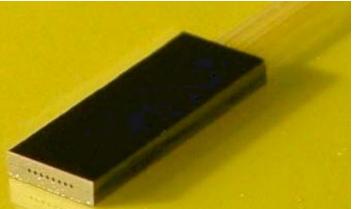

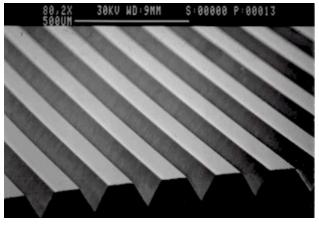

### FIBER PIGTAILING: FIBER GROOVE ARRAYS

### FIBER PIGTAILING: FIBER GROOVE ARRAYS

#### Accurate Silicon Spacer Chips for an Optical-Fiber Cable Connector

By C. M. SCHROEDER (Manuscript submitted July 1, 1977)

[O/E Land Inc]

#### **UNIVERSITY OF TWENTE.**

### **ACTIVE ALIGNMENT**

### PROCEDURE:

- Move fibre array vs chip in 6-axes to maximize coupling of light

- Glue in place with typically UV curable epoxy

#### CONSIDERATIONS:

- Time consuming, costly procedure

- Mode mismatch between fibre and waveguides  $\rightarrow$  Low coupling efficiency

- Pitch mismatch between fibre array and photonic chip  $\rightarrow$  Loss of real-state UNIVERSITY OF TWENTE. 26/02/2014 44

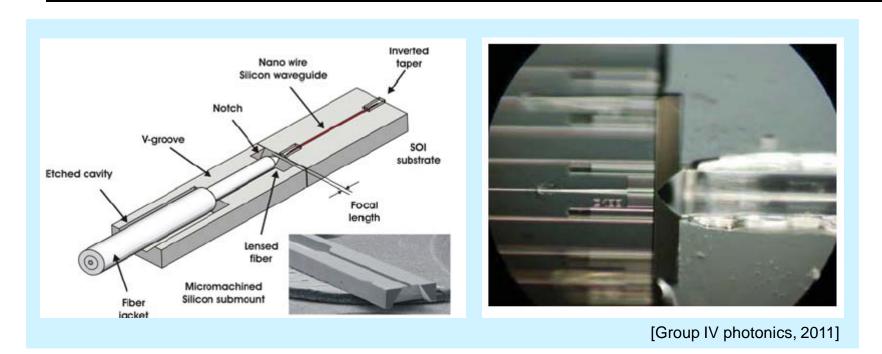

# PASSIVE ALIGNMENT: SILICON MICROBENCH TECHNOLOY

- Etched V-grooves lithographically aligned to photonic device

- Extra notch for glue relief

- Alignment errors limit the overall performance

### **ACTIVE ALIGNMENT**

#### PROCEDURE:

- Move fibre array vs chip in 6-axes to maximize coupling of light

- Glue in place with typically UV curable epoxy

#### **CONSIDERATIONS**:

- Time consuming, costly procedure

- Mode mismatch between fibre and waveguides  $\rightarrow$  Low coupling efficiency

- Pitch mismatch between fibre array and photonic chip  $\rightarrow$  loss of real-state UNIVERSITY OF TWENTE. 26/02/2014 46

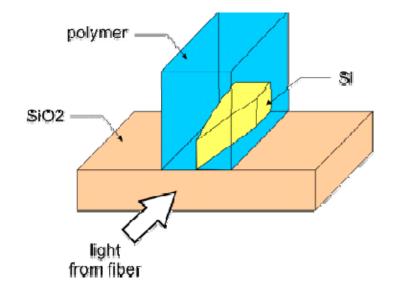

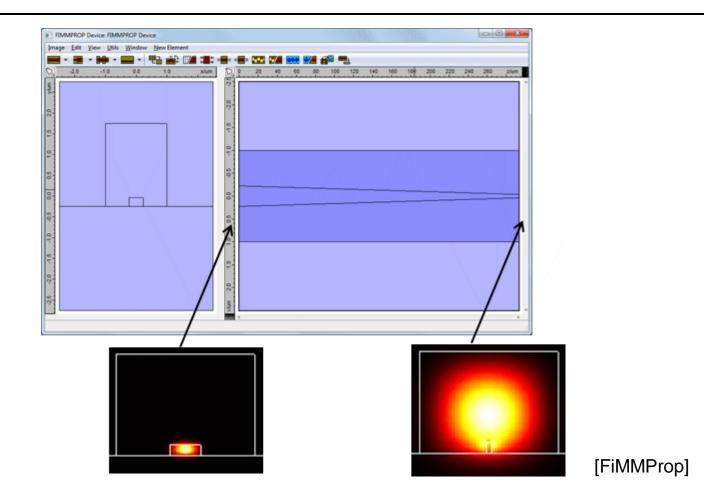

### MODE SIZE CONVERTERS

| Si layer thickness                 | 220nm                            |

|------------------------------------|----------------------------------|

| Silicon layer width                | 450nm to 75nm                    |

| Refractive index of polymer        | 1.58                             |

| Total size of the polymer<br>layer | 2um by 2um                       |

| Thickness of silica substrate      | 2.5um                            |

| Taper length                       | Varied between<br>10um and 300um |

| Wavelength                         | 1.5um                            |

[FiMMProp]

### MODE SIZE CONVERTERS

### **ACTIVE ALIGNMENT**

### PROCEDURE:

- Move fibre array vs chip in 6-axes to maximize coupling of light

- Glue in place with typically UV curable epoxy

### CONSIDERATIONS:

- Time consuming, costly procedure

- Mode mismatch between fibre and waveguides  $\rightarrow$  Low coupling efficiency

- Pitch mismatch between fibre array and photonic chip  $\rightarrow$  loss of real-state

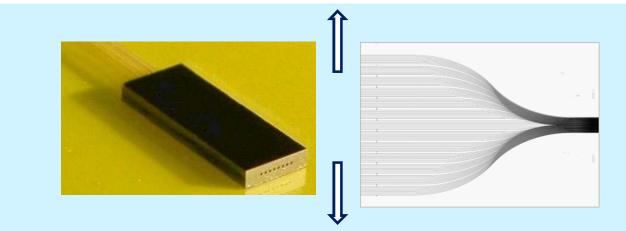

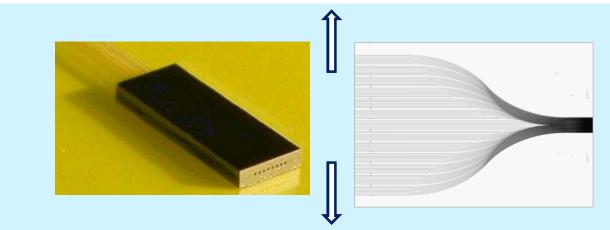

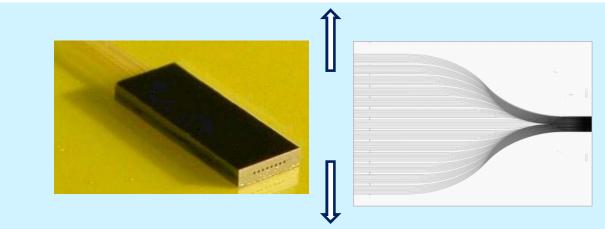

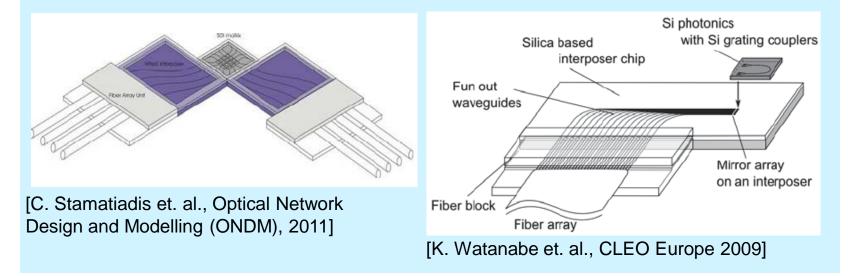

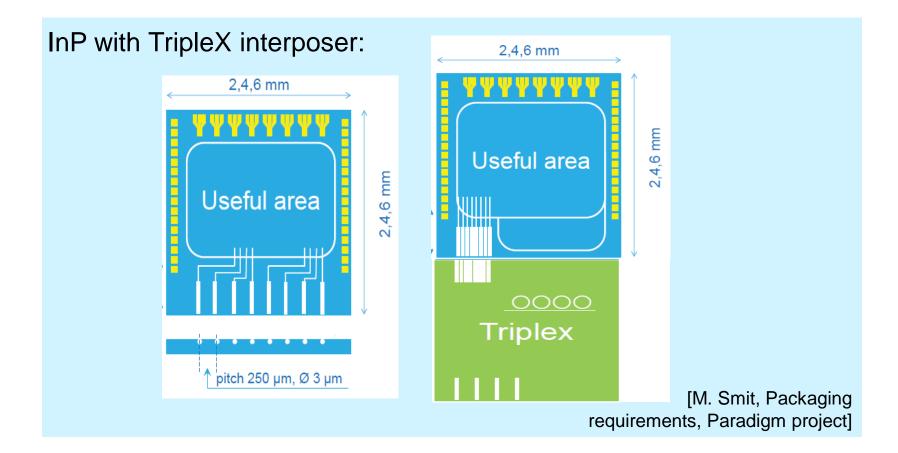

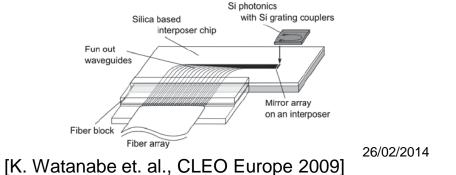

### **INTRODUCTION OF DIFFERENT INTERPOSERS**

50

## INTRODUCTION OF DIFFERENT INTERPOSERS

Interposer in TripleX (Si $_3N_4$ /SiO $_2$  based waveguide technology from LioniX):

### INTRODUCTION OF DIFFERENT INTERPOSERS

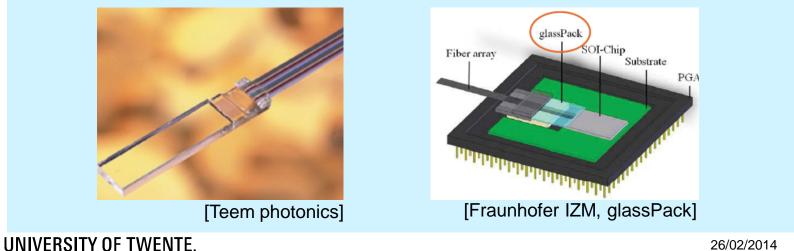

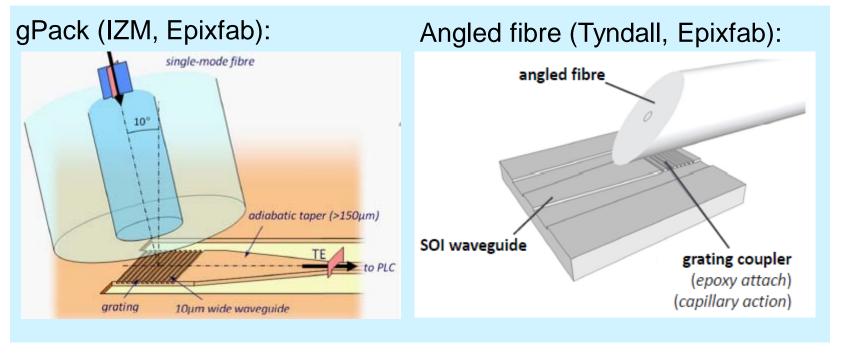

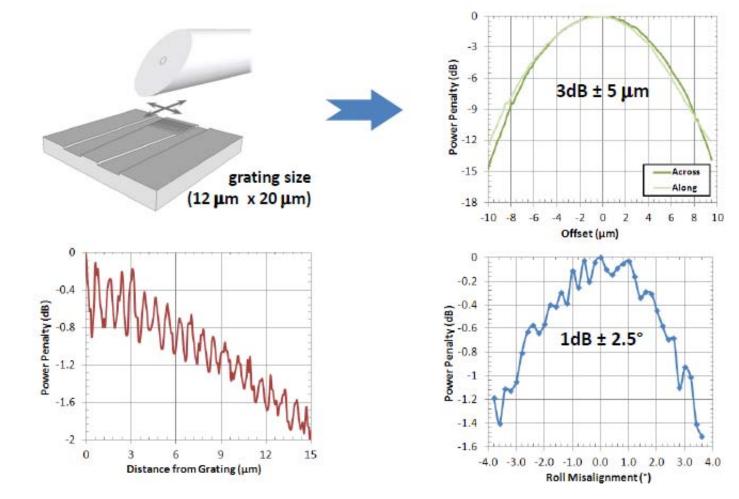

### **GRATING COUPLING**

[P. O'Brien, ECOC 2012]

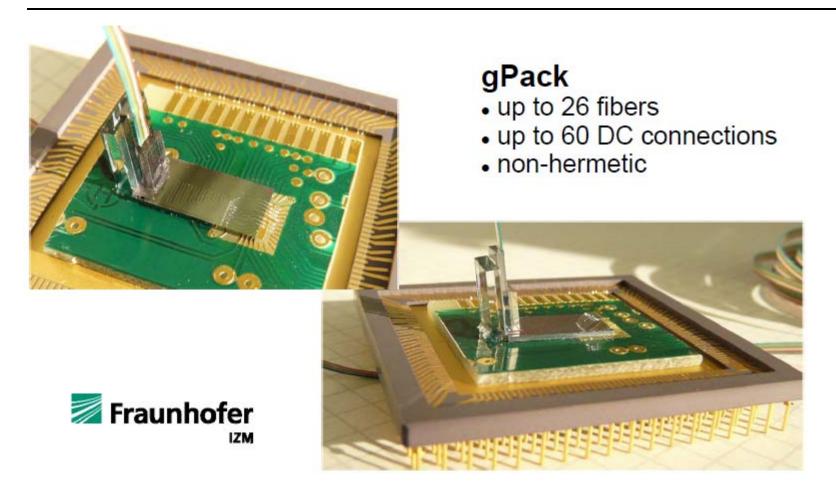

### gPACK (IZM, Epixfab)

UNIVERSITY OF TWENTE.

### ANGLED FIBER (Tyndall, EPIXFAB)

**UNIVERSITY OF TWENTE.**

[P. O'Brien, ECOC 2012]

### ANGLED FIBER (Tyndall, EPIXFAB)

Still size and pitch problem!

$\rightarrow$  Use of interposer

UNIVERSITY OF TWENTE.

56

### OUTLINE

- Packaging of LEDs, detectors and image sensors

- Packaging of photonic devices

- Hybrid and heterogeneous integration technologies

### LECTURE LEARNING GOALS

1. Get an overview of different available packaging and integration technologies

- 2. Get a "feeling" for the challenges of packaging

- 3. Acquire a "design-for-packaging" attitude