# Zynq Evaluation and Development Board

Cristian Sisterna

Universidad Nacional San Juan Argentina

## ZedBoard

#### **AVNET**

ZedBoard™ is a complete development kit for designers interested in exploring designs using the AMD Xilinx Zynq®-7000 All Programmable SoC. The board contains all the necessary interfaces and supporting functions to enable a wide range of applications.

The expandability features of the board make it ideal for rapid prototyping and proof-of-concept development.

#### **DIGILENT**

ZedBoard™ is a low-cost development board for the Xilinx Zynq-7000 all programmable SoC (AP SoC). This board contains everything necessary to create a Linux®, Android®, Windows®, or other ∞/RTOS based design. Additionally, several expansion connectors expose the processing system and programmable logic I/Os for easy user access.

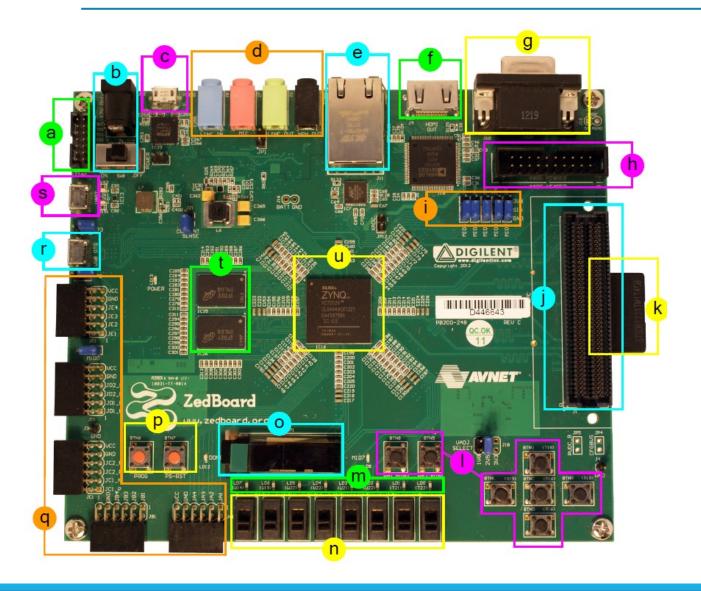

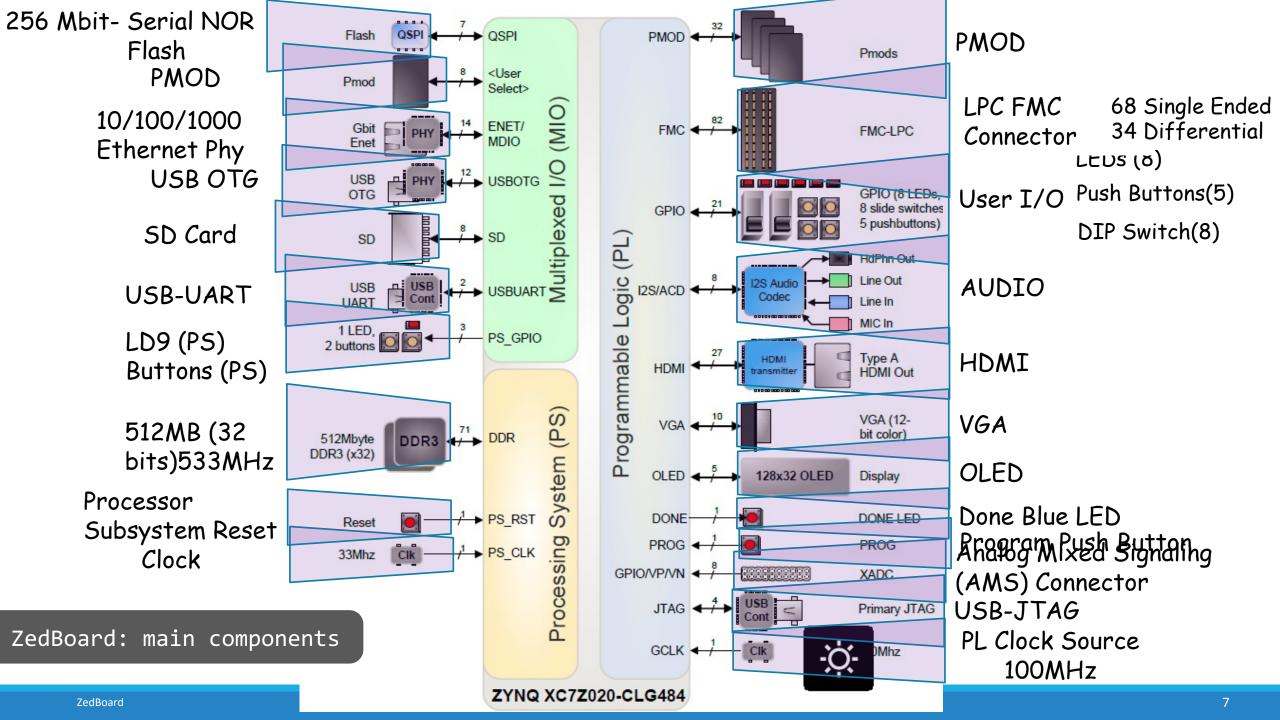

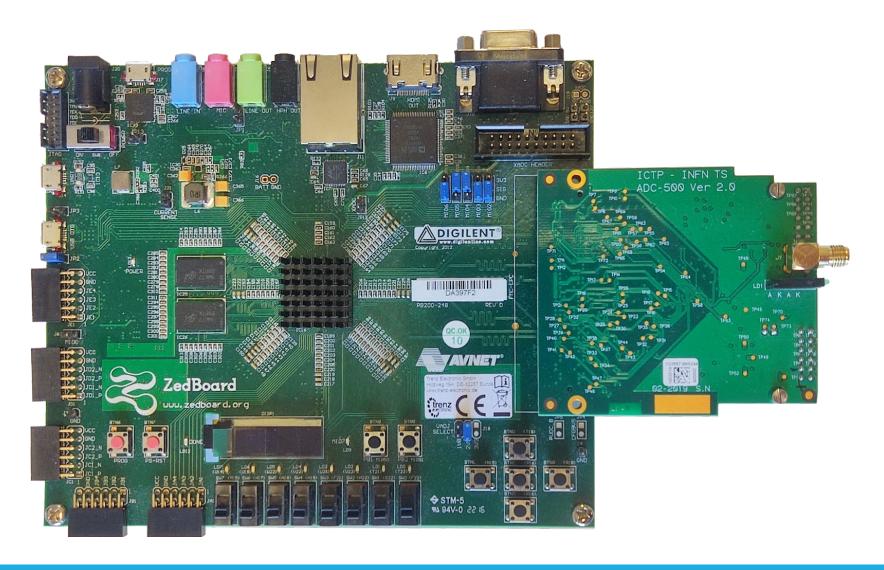

# **ZedBoard Main Components**

- a Xilinx JTAG connector

- b Power input and switch

- C USB-JTAG (programming)

- d Audio ports

- Ethernet port

- f HDMI port (output)

- 9 VGA port

- NADC header port

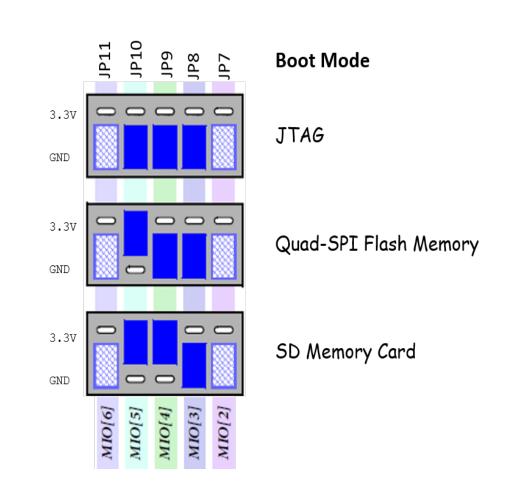

- Configuration jumpers

- J FMC connector

- K SD card (underside)

- User push buttons

- m LEDs

- n Switches

- OLED display

- Prog & reset push buttons

- 9 5 x Pmod connector ports

- USB-OTG peripheral port

- S USB-UART port

- t DDR3 memory

- Zynq device (+ heatsink)

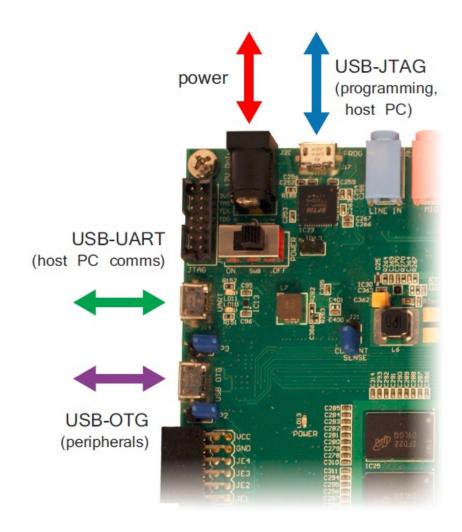

## **ZedBoard Main Connectors**

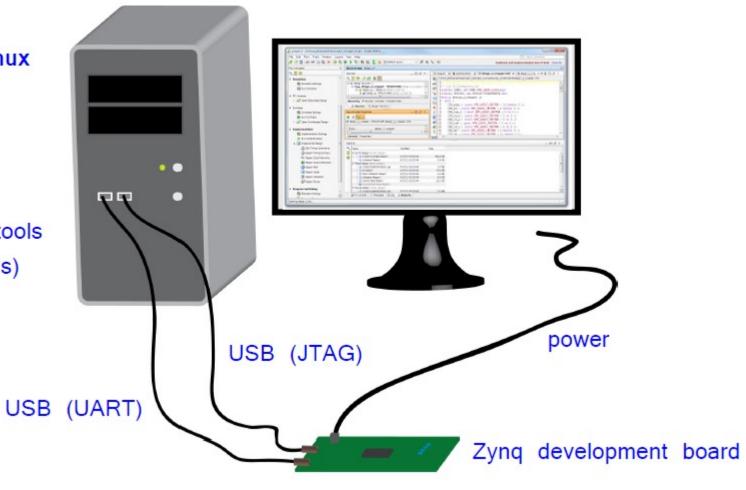

## **Conection Between PC-ZedBoard**

Windows / Linux computer

4GB+ RAM

Xilinx design tools (3rd party tools)

# **Programming the ZedBoard**

# ZedBoard Hardware User Guide

### **ZedBoard**

(Zynq™ Evaluation and Development) Hardware User's Guide

Version 2.2 27 January 2014

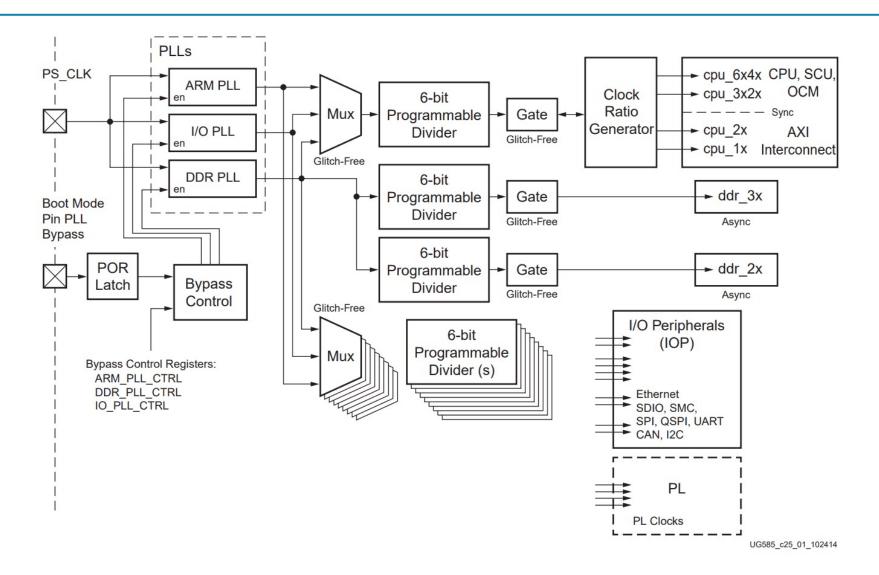

## **ZedBoard Clock Sources**

#### 2.5 Clock sources

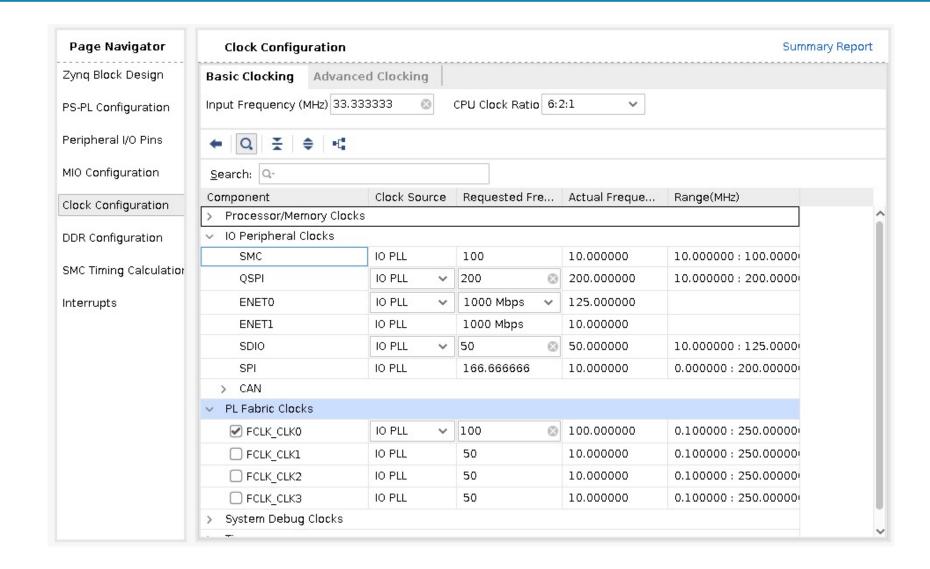

The Zynq-7000 AP SoC's PS subsystem uses a dedicated 33.3333 MHz clock source, IC18, Fox 767-33.33333-12, with series termination. The PS infrastructure can generate up to four PLL-based clocks for the PL system. An on-board 100 MHz oscillator, IC17, Fox 767-100-136, supplies the PL subsystem clock input on bank 13, pir Y9.

## **Zynq Clock Resources**

## **Zynq Clock Resources – Configuration in Vivado**

# ZedBoard Available I/Os for the User (1)

#### 2.7 User I/O

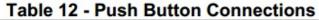

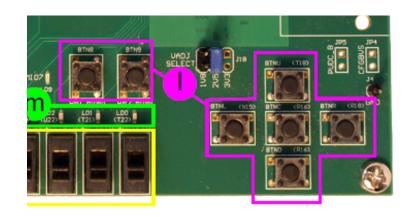

#### 2.7.1 User Push Buttons

The ZedBoard provides 7 user GPIO push buttons to the Zynq-7000 AP SoC; five on the PL-side and two on the PS-side.

Pull-downs provide a known default state, pushing each button connects to Vcco.

| Signal Name | Subsection | Zynq pin     |

|-------------|------------|--------------|

| BTNU        | PL         | T18          |

| BTNR        | PL         | R18          |

| BTND        | PL         | R16          |

| BTNC        | PL         | P16          |

| BTNL        | PL         | N15          |

| PB1         | PS         | D13 (MIO 50) |

| PB2         | PS         | C10 (MIO 51) |

# ZedBoard Available I/O for the User (2)

#### VADJ R57 SW<sub>0</sub> SW0 10K R58 SW1 SWI R61 10K SW2 10K R63 SW3 SW3 R64 10K SW4 SW4 10K R66 SW5 SW5 R68 10K SW6 SW6 10K R69 SW7 10K **GND**

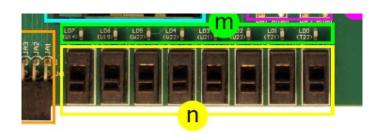

#### 2.7.2 User DIP Switches

The ZedBoard has eight user dip switches, SW0-SW7, providing user input. SPDT switches connect the I/O through a  $10k\Omega$  resistor to the VADJ voltage supply or GND.

**Table 13 - DIP Switch Connections**

| Signal Name | Zynq pin |

|-------------|----------|

| SW0         | F22      |

| SW1         | G22      |

| SW2         | H22      |

| SW3         | F21      |

| SW4         | H19      |

| SW5         | H18      |

| SW6         | H17      |

| SW7         | M15      |

# ZedBoard Available I/O for the User (3)

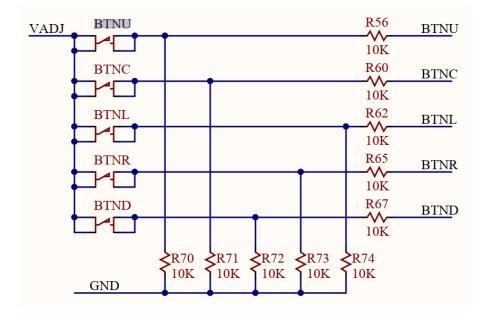

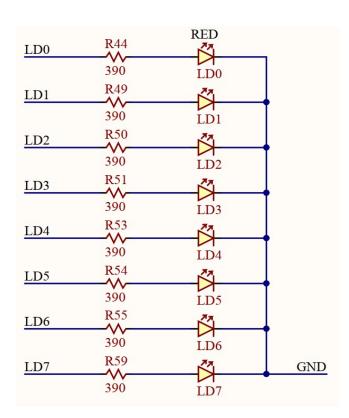

#### 2.7.3 User LEDs

The ZedBoard has eight user LEDs, LD0 – LD7. A logic high from the Zynq-7000 AP SoC I/O causes the LED to turn on. LED's are sourced from 3.3V banks through  $390\Omega$  resistors.

**Table 14 - LED Connections**

| Signal Name | Subsection | Zynq pin  |

|-------------|------------|-----------|

| LD0         | PL         | T22       |

| LD1         | PL         | T21       |

| LD2         | PL         | U22       |

| LD3         | PL         | U21       |

| LD4         | PL         | V22       |

| LD5         | PL         | W22       |

| LD6         | PL         | U19       |

| LD7         | PL         | U14       |

| LD9         | PS         | D5 (MIO7) |

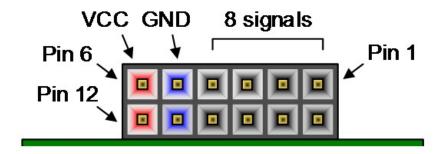

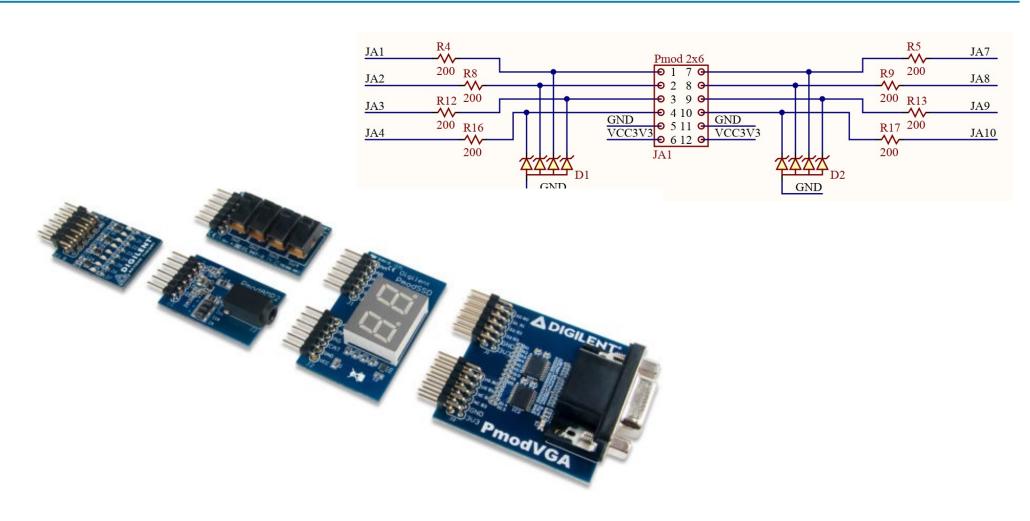

## **ZedBoard PMOD Connectors**

**Table 16 - Pmod Connections**

| Pmod       | Signal<br>Name | Zynq pin | Pmod | Signal Name | Zynq pin |

|------------|----------------|----------|------|-------------|----------|

| JA8<br>JA9 | JA1            | Y11      | JB1  | JB1         | W12      |

|            | JA2            | AA11     |      | JB2         | W11      |

|            | JA3            | Y10      |      | JB3         | V10      |

|            | JA4            | AA9      |      | JB4         | W8       |

|            | JA7            | AB11     |      | JB7         | V12      |

|            | JA8            | AB10     |      | JB8         | W10      |

|            | JA9            | AB9      |      | JB9         | V9       |

|            | JA10           | AA8      |      | JB10        | V8       |

## **ZedBoard PMOD Boards**

https://digilent.com/reference/pmod/start

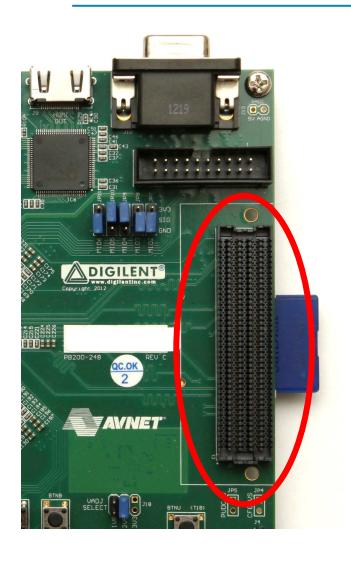

### **LPC FMC Connector**

LPC: Low-Pin-Count

FMC: FPGA Mezzanine Card

- ✓ The LPC FMC exposes 68 single-ended I/O, which can be configured as 34 differential pairs.

- ✓ ADC500: an ICTP MLAB board is plugged into the LPC FMC and will be used in the final lab.

18

## ZedBoard + ICTP-INFN ADC500

## **ZedBoard Bank Power Voltages**

#### Vadj is selected by JP18:

- 1.8V

- 2.5V

- 3.3V