Joint ICTP-IAEA School on Systems-on-Chip based on FPGA for Scientific Instrumentation and Reconfigurable Computing

# **Verification - Test Bench**

Cristian Sisterna UNSJ

A brief chronology of events:

July 1994—A summer intern discovers a bug in the floating point unit during testing; however, Intel did not expect it to be major problem for its users. Hence they continued to produce the flawed chip, while planning to produce the corrected chip starting 1995.

September 1994—A mathematics professor in Virginia, Thomas Nicely discovers the bug that causes errors in floating-point divisions with more than 5 significant digits. He reported it to Intel but got no official response from Intel.

November 1994—The EE times reported the story, but Intel claimed that the error occurs very infrequently and will not be seen by the average user. The story was picked up many newspapers including the New York Times, the San Jose Mercury News, and the San Francisco Chronicle.

December 1994—IBM stops shipping IBM PCs that used the affected Pentium chip in early December. Following that, on December 21, Intel officially apologized and announced that users could get their Pentium P5 chips exchanged for an updated processor in which the flaw is corrected.

January 1995—Intel spent \$475 million against earnings to replace the flawed processors.

The bug was caused because of incorrect elements returned by the PLA lookup table used in the floating-point division in the chip. When discovered in July 1994, the cost to fix the bug was estimated to be several hundred thousand dollars, but it would take a few months to make the change, verify the chip, and produce the corrected chips.

The field of "Verification" got a lot of attention following this event, since companies are interested in avoiding this kind of economic damage and embarrassment. In the years following this event, PhD graduates with dissertations in verification were heavily sought after by chip design companies.

The Intel Pentium P5 chips with the FDIV bug looked like this.

#### **Verification**

It's an IMPORTANT part of the design process:

How do I know that the design works as expected?

- It's IMPORTANT/NECESSARY to verify the behavior of the daesign in at least one of following parts of the design process:

- Functional Verification / Pre-synthesis Verification

- Post-synthesis

- Timing Verification / Post-Place & Route Verification

## Verification, Where in the design flow?

- **▼** Functional Verification / Pre-synthesis Verification:

- Where most errors can and should be found

- ALWAYS do this verification

- **⋖** Post-synthesis Verification

- not necessary unless several synthesis attributes were used and it's necessary to verify the behavior after synthesis

- **▼** Timing Verification / Post-Place & Route Verification

- Necessary in high frequency designs, in the order of >100MHz

- Time consuming verification process (very long verification time)

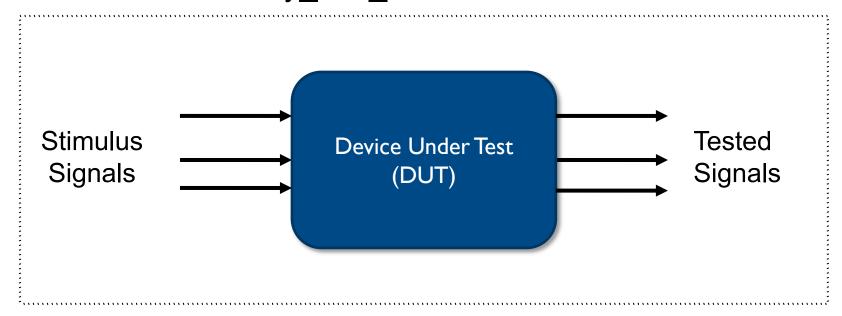

### What is a Test Bench?

- It has three main purposes:

- To generate a pattern stimulus for executing a simulation

- To apply the generated stimulus to the entity under test and to collect output's responses

- To compare output's responses with expected values

### What is a Test Bench?

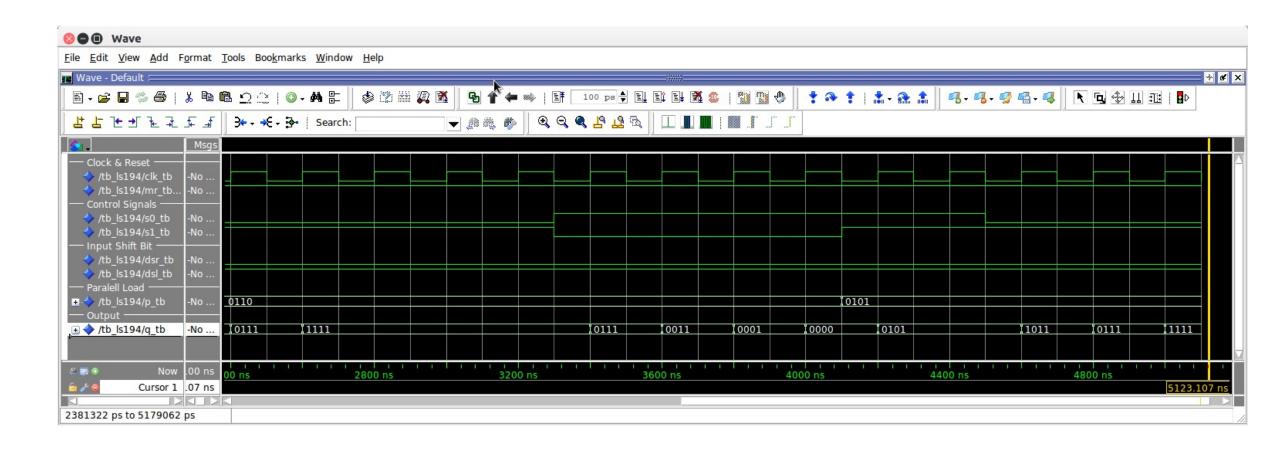

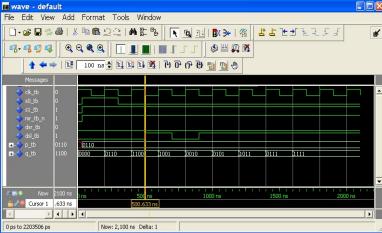

A test bench is usually executed in a simulation tool (ModelSim, ISIM, etc) where the test pattern and the outputs can seen graphically as waveforms with precise time information.

Test bench should be created by a DIFFERENT engineer than the one who created the device under test (DUT)

#### my\_test\_bench.vhd

© Cristian Sisterna

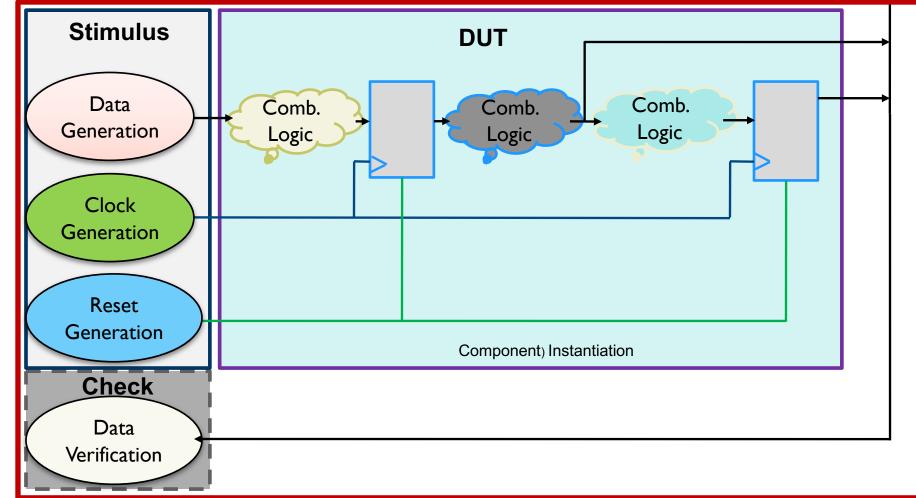

## VHDL Components of a Test Bench

- Test bench entity:

- Empty declaration

- Test bench architecture:

- Component declaration

- Local signal declaration

- Component instantiation

- Data stimulus generation statements

- Clock/Reset generation statements

- Output's values check statements (optional)

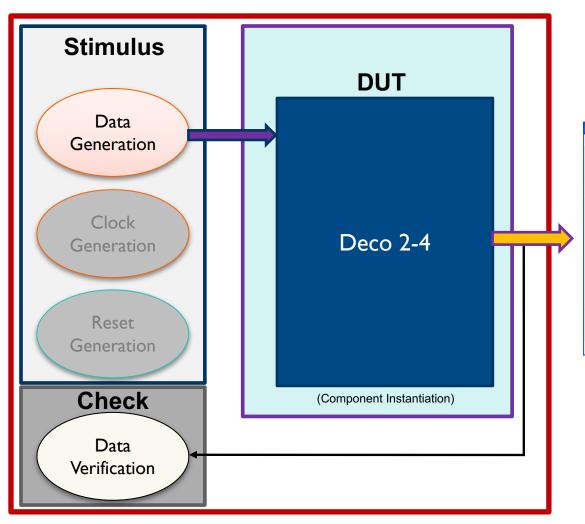

## **Test Bench Block Diagram**

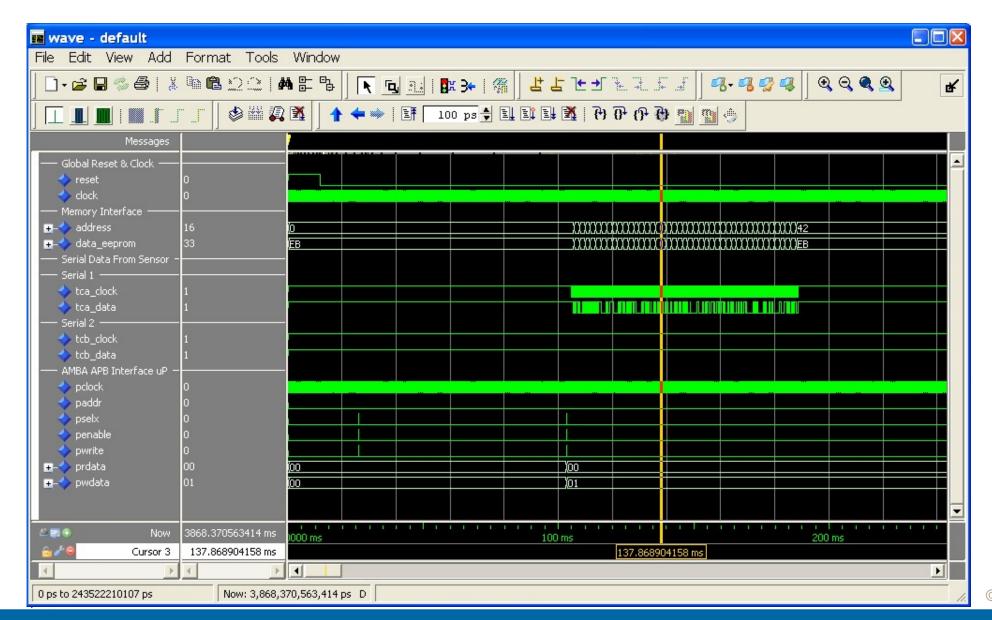

# File Edit View Add Format Tools Window | Section | Sect

wave - default

#### Test Bench

#### Simulator

#### **Test Bench Simulation Result - Waveforms**

## **Test Bench VHDL Template**

```

library ieee;

use ieee.std logic 1164.all;

-- TB entity declaration del TB (empty entity)

entity testbench is

end testbench;

-- architecture declaration

architecture tb of testbench is

-- component declaration: component to test

component device under test

port(list of ports);

end component;

-- local signal declarations. Used to:

-- stimulate the DUT's inputs

-- test the DUT's outputs

<local signal declarations;>

```

## **Test Bench VHDL Template**

```

begin

-- component instantiation:

-- associate the top-level (TB)

-- signals to their equivalent DUT's signals

DUT: entity under test port map ( list of ports);

-- stimulus statements for the input signals.

-- values are assigned at different times per each input

generate input waveforms;

-- ouptut signals' check

monitor output statements; -- optional

end tb;

```

## **Test Bench Template - Example**

```

library ieee;

Define library, same as in VHDL

use ieee.std logic 1164.all;

source code

entity test my design is

VHDL model without entity interface

end test my design;

architecture testbench of test my design is

component my design is

Component declaration of the device to test

port (a,b : in std logic;

x,y : out std logic);

end component;

signal as,bs : std_logic:='1';

Define signal names

signal xs,ys : std logic;

begin

uut : my design port map

Instantiated UUT in test

(a=>as, b=>bs, x=>xs, y=>ys);

as <= not(as) after 50 us;

Define the stimulus for the

process begin

inputs of the component under

bs <= '1'; wait for 75 us;

test

bs <= '0'; wait for 25 us;

end process;

end testbench;

```

## Most Common VHDL Statements for Test Bench

#### wait statement

The wait statement can be located anywhere between begin and end process

```

# Basic Usages:

wait for time;

wait until condition;

wait on signal_list;

wait;

```

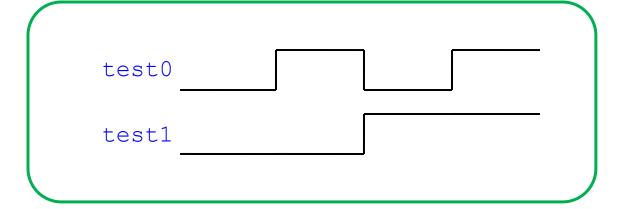

## Use of wait (1)

## Use of wait (2)

```

process

. . . .

wait on A until CLK = '1';-- the process is resumed

-- after a change on A signal,

-- but only when the value of

-- the signal CLK is equal to '

end process;

```

© Cristian Sisterna

## Data Stimulus Generation

## **Periodic Signal Generation**

```

architecture testbench of test my design is

signal clk 50 : std logic := '1';

signal clk 75 : std logic := '0';

constant clk period: time := 100 us;

constant h clk period: time := 50 us;

begin

-- case 1: concurrent statement

clk 50 <= not(clk 50) after h clk period; -- 50% duty

-- case 2: sequential statement

clk 75 proc: process

50

begin

100

clk 75 <= '1';

clk 50

wait for 75 us; -- 75% duty

clk 75 <= '0';

wait for 25 us;

end process clk 75 proc;

clk 75

end testbench;

```

#### **Stimulus Generation**

- Avoid race conditions between data and clock

- Applying the data and the active edge of the clock simultaneously might cause a race condition

- To keep data synchronized with the clock while avoiding race condition, apply the data at a different point in the clock period that at the active edge of clock

## **Data Generation (1)**

Example of

Data generation

on inactive clock

edge

Clock generation process

Data generation process

```

clk gen proc: process

begin

clk <= '0';

wait for 25 ns;

clk<= '1';

wait for 25 ns;

end process clk gen proc;

data gen proc: process

while not (data_done) loop

DATA1 \leq X1;

DATA2 <= X2;

wait until falling edge(clk);

end loop;

end process data gen proc;

```

## **Data Generation (2)**

**Relative time**: signal waveforms that are specified to change at simulation times relative to the previous time, in a time accumulated manner

```

architecture relative timing of myTest is

signal Add Bus : std logic vector(7 downto 0);

begin

patt gen proc: process

00000101

00000000

begin

10101010

00000000

00000101

Add Bus <= "00000000";

wait for 10 us;

Add Bus <= "00000101";

wait for 10 us;

Add Bus <= "10101010";

wait for 10 us;

end process patt gen proc;

end relative timing;

```

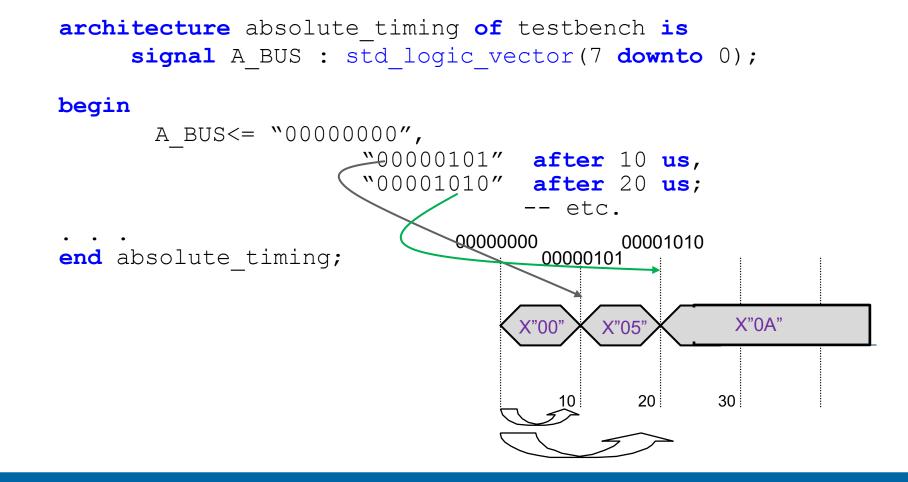

## **Data Generation (3)**

<u>Absolute time</u>: signal waveforms that are specified to change at simulation times absolute since the moment that the simulation begin

## **Data Generation (4)**

## **Data Generation (5)**

```

architecture array usage of in test benches is

signal add bus : std logic vector(7 downto 0);

-- type & signal declarations: 5 data for 8 bits

subtype stimulus is array (0 to 4) of

std logic vector (7 downto 0);

constant data : stimulus :=

("0000000",

-- declare the stimulus

"00000001", -- as an array.

"00000010", -- these values will be

"00000011", -- used to stimulate the

"00000100"); -- inputs

begin

stim proc: process

begin

for i in 0 to 4 loop — for loop that

assign

add bus <= data(i); -- to add bus a new value

end loop;

end process stim proc;

end array usage;

```

## **Data Generation (6)**

```

architecture array usage of in test benches is

-- same declarations as previous example

begin

process

begin

for i in 0 to 4 loop

Add BUS <= DATA(i);

wait until falling edge(clk);

for k in 1 to 7 loop

wait until rising edge(clk);

end loop;

end loop;

end process;

end array usage;

```

In this case each pattern in the sequence is held for how many clock cycles???

#### **Reset Generation**

```

-- asynchronous desassert

reset

reset: process

begin

rst <= '1';

wait for 23 us;

rst <= '0';

wait for 1402 us;

rst <= '1';

wait for 23 us;

rst <= '0';

wait;

end process;

```

```

-- synchronous desassert reset

sreset: process

begin

rst <= '1';

for i in 1 to 5 loop

wait until clk = '1';

end loop;

rst <= '0';

wait;

end process;

```

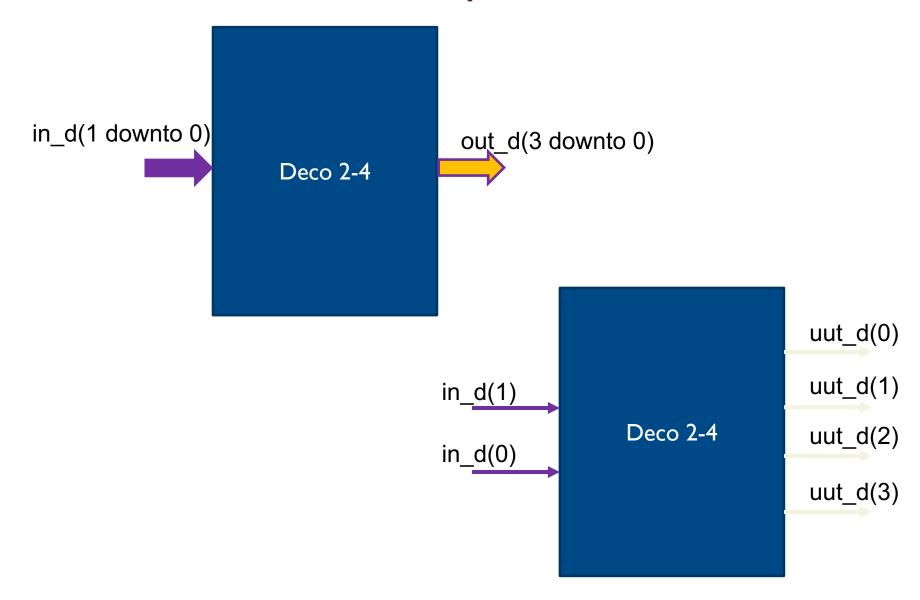

# Simple Example

#### 2:4 Decoder

```

library Library ieee;

use ieee.std logic 1164.all;

entity decoder 2 4 is

port (in d : in std logic vector (1 downto 0);

out d : out std logic vector (3 downto 0));

end decoder 2 4 ;

architecture dataflow of decoder 2 4 is

begin

with in1 select

out1 <= "0001" when "00",

"0010" when "01",

"0100" when "10",

"1000" when "11",

"0000" when others;

end dataflow;

```

# How to test 'Simple Decoder''??

## Test Bench for Simple 2:4 Decoder

#### Test Bench

#### Simulator

```

library ieee;

use ieee.std logic 1164.all;

-- Test Bench to exercise and verify

-- correctness of decoder 2 4 entity

entity tb case1 decode is

end tb case1 decode ;

architecture tb c1 of tb case1 decode is

-- signal declarations

signal in tb : std logic vector (1 downto 0);

signal out tb : std logic vector (3 downto 0);

-- component declaration

component decode

port (

in d : in std logic vector(1 downto 0);

out d: out std logic vector(3 downto 0));

end component;

```

```

begin

Component

dut: decode port map(

in d => in tb

Instantiation-

out d => out tb \int

Inputs

Stimulus and

patt gen proc: process

Outputs port

begin

map

in tb<= "00";

wait for 10 us;

in tb <= "01";

wait for 10 us;

Stimulus

generation

in tb <= "10";

wait for 10 us;

in tb <= "11";

wait for 10 us;

end process patt gen proc;

end architecture tb c1 ;

```

```

library ieee;

use ieee.std logic 1164.all;

-- Test Bench to exercise and verify

-- correctness of decoder 2 4 entity

entity tb case2 decode is

end tb case2 decode ;

architecture tb c2 of tb case2 decode is

-- signal declarations

signal in tb : std logic vector (1 downto 0);

signal out tb : std logic vector (3 downto 0);

-- component declaration

component decode

port (

in d : in std logic vector(1 downto 0);

out d: out std logic vector(3 downto 0));

end component;

```

```

begin

Component

dut: decode port map (

Instantiation-

in d \Rightarrow in tb,

Inputs

out d => out tb);

Stimulus and

Outputs port

map

begin

in tb <= "00",

"01" after 10 us,

Stimulus

"10" after 20 us,

generation

"11" after 20 us;

end architecture tb c2;

```

© Cristian Sisterna

```

library ieee;

use ieee.std logic 1164.all;

use ieee.numeric std.all;

-- Test Bench to exercise and verify

-- correctness of decoder 2 4 entity

entity tb case3 decode is

end tb case3 decode ;

architecture tb c3 of tb case3 decode is

-- signal declarations

signal in tb : std logic vector (1 downto 0);

signal out tb : std logic vector (3 downto 0);

-- component declaration

component decode

port (

in d : in std logic vector(1 downto 0);

out d: out std logic vector(3 downto 0));

end component;

```

```

signal count: unsigned(1 downto 0); -- numeric std

begin

dut: decode port map(

in_d => in_tb,

out d

=> out tb);

apply inputs: process

begin

wait on (rising edge(clk));

count <= count + 1;</pre>

end process apply inputs;

in_tb <= std_logic_vector(count);</pre>

end architecture tb c3;

```

Component

InstantiationInputs

Stimulus and

Outputs port

map

generation

Data

Any error?

```

library ieee;

use ieee.std logic 1164.all;

entity tb case4 decode is

end tb case4 decode;

architecture tb c4 of tb case4 decode is

subtype input array is array(0 to 3) of

std logic vector(1 downto 0);

constant input vectors: input array :=

("00", "01", "10", "11");

signal in tb : std logic vector (1 downto 0);

signal out tb : std logic vector (3 downto 0);

component decode

port (

in d : in std logic vector(1 downto 0);

out d: out std logic vector(3 downto 0));

end component;

```

```

begin

dut: decode port map (

in_d => in_tb,

out d => out tb);

apply_inputs: process

begin

for j in input_vectors 'range loop

in_tb <= input_vectors(j);</pre>

Data

wait for 50 ns;

generation

end loop;

wait; -- ???

end process apply_inputs;

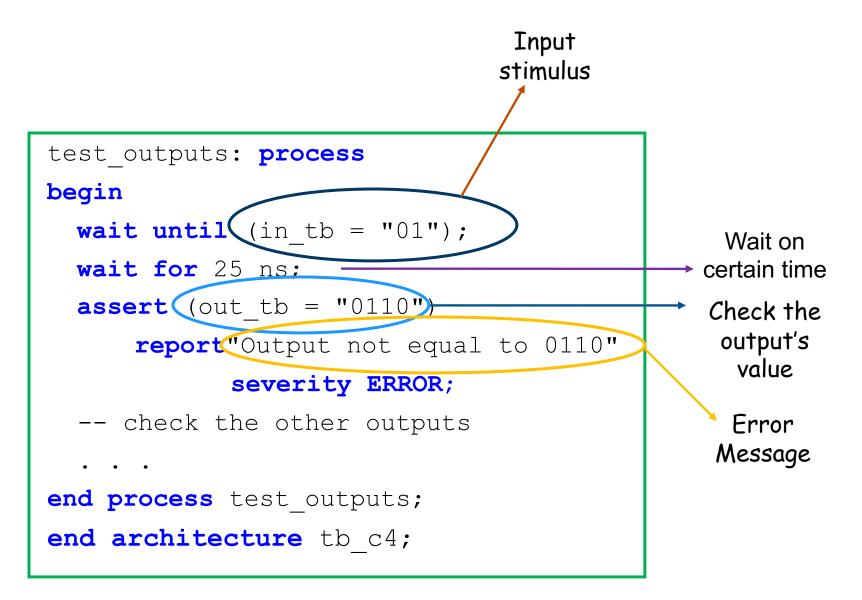

-- verification process

```

```

library ieee;

use ieee.std logic 1164.all;

entity tb case5 decode is

end tb case5 decode;

architecture tb c5 of tb case5 decode is

type decoder test is record

in_tb_stimulus: std logic vector(1 downto 0);

out tb stimulus: std logic vector(3 downto 0);

end record;

type test array is array(natural range <>) of decoder test;

constant test data: test array :=

(("00", "0001"),

("01", "0010"),

("10", "0100"),

("11", "1000"));

-- same component declaration as before

signal in1 tb : std_logic_vector(1 downto 0);

signal out1 tb: std logic vector(3 downto 0);

```

```

begin

dut: decode port map (

in1 => in1 tb,

out1 => out1 tb);

apply in check outs: process

begin

for j in test data'range loop

in1 tb <= test data(j).in tb stimulus);</pre>

wait for 50 ns;

assert (out1 tb = test data(j).out tb stimulus)

report "Output not equal to the expected value,

error en indice " & integer'image(j);

severity ERROR;

end loop;

end process apply in check outs;

end architecture tb c5;

```

```

begin

apply inputs: process

begin

for j in test data'range loop

in1 tb <= test data(j). in tb stimulus);</pre>

wait for 50 ns;

end loop;

end process apply inputs;

data_verif: process

begin

wait for 25 ns;

assert (out1 tb = test data(j).out tb stimulus)

report "Output not equal to the expected value"

severity ERROR;

wait for 50 ns;

end process data verif;

```

# Synchronous 2:4 Decoder

```

entity synch decoder 2 4 is

port (in d : in std logic vector(1 downto 0);

clk : in std logic ;

out d : out std logic vector(3 downto 0));

end synch decoder 2 4;

architecture dataflow of synch decoder 2 4 is

signal out1 i: std logic vector (3 downto 0);

begin

with in1 select

out1 i <= "0001" when "00",

"0010" when "01",

"0100" when "10",

"1000" when "11",

"0000" when others;

reg proc: process(clk)

begin

if(rising edge(clk)) then

out d <= out1 i;

end if;

end process reg proc;

end dataflow;

```

# Synchronous 2:4 Decoder – Test Bench

```

entity tb synch decode is

end tb synch decode ;

architecture test bench of the synch decode is

-- component declaration

type decoder test is record

in tb: std logic vector(1 downto 0);

out tb: std logic vector(3 downto 0);

end record:

subtype test array is array(natural range <>) of decoder test;

constant test data: test array :=

("00", "0001",

"01", "0010",

"10", "0100",

"11", "1000");

```

# TB – Synch. Decoder 2:4

```

begin

dut: decode port map( in d => in tb, out d => out tb);

apply_inputs: process

begin

for j in test data'range loop

in d <= test data(j).in tb);</pre>

clk <= '0';

wait for 5 ns;

clk <= '1';

wait for 5 ns;

assert (out d = test data(j).out tb)

report "Output not equal to the expected value"

severity ERROR;

end loop;

wait;

end process apply inputs;

```

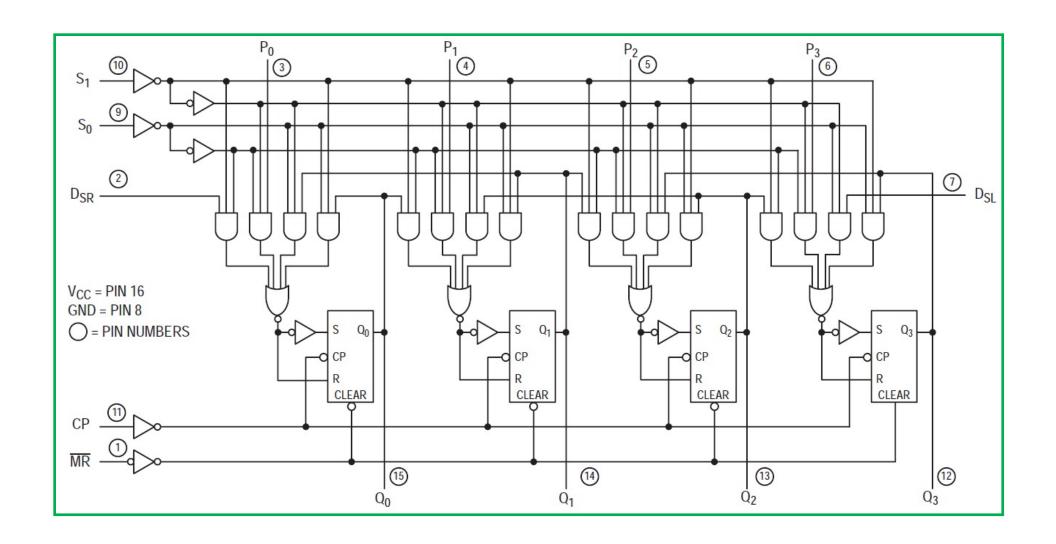

# Another Example Test Bench for a Shift Register

# 74x194

# 74x194

#### MODE SELECT — TRUTH TABLE

| OPERATING MODE | INPUTS |                |                |                 |                 |                | OUTPUTS                          |                                  |                                                |                                  |

|----------------|--------|----------------|----------------|-----------------|-----------------|----------------|----------------------------------|----------------------------------|------------------------------------------------|----------------------------------|

|                | MR     | S <sub>1</sub> | S <sub>0</sub> | D <sub>SR</sub> | D <sub>SL</sub> | P <sub>n</sub> | $Q_0$                            | Q <sub>1</sub>                   | $Q_2$                                          | $Q_3$                            |

| Reset          | L      | X              | X              | X               | X               | X              | L                                | L                                | L                                              | L                                |

| Hold           | Н      | - 1            | I              | X               | X               | X              | $q_0$                            | $q_1$                            | $q_2$                                          | $q_3$                            |

| Shift Left     | H H    | h<br>h         | 1              | X<br>X          | l<br>h          | X              | q <sub>1</sub><br>q <sub>1</sub> | q <sub>2</sub><br>q <sub>2</sub> | <b>q</b> <sub>3</sub><br><b>q</b> <sub>3</sub> | L<br>H                           |

| Shift Right    | H      | I              | h<br>h         | l<br>h          | X<br>X          | X              | L<br>H                           | <b>q</b> <sub>0</sub>            | 9 <sub>1</sub><br>9 <sub>1</sub>               | q <sub>2</sub><br>q <sub>2</sub> |

| Parallel Load  | Н      | h              | h              | Х               | Х               | Pn             | P <sub>0</sub>                   | P <sub>1</sub>                   | P <sub>2</sub>                                 | P <sub>3</sub>                   |

L = LOW Voltage Level

H = HIGH Voltage Level

X = Don't Care

I = LOW voltage level one set-up time prior to the LOW to HIGH clock transition

h = HIGH voltage level one set-up time prior to the LOW to HIGH clock transition

$p_n(q_n)$  = Lower case letters indicate the state of the referenced input (or output) one set-up time prior to the LOW to HIGH clock transition.

# 74x194 – VHDL Description

```

-- example of a 4-bit shift register

-- LS194 4-bit bidirectional universal shift register

-- Based on the 74LS194 true table

MODE

INPUTS - OUTPUTS

| MR\ S1 S0 Dsr Dsl Pn | Q0 Q1 Q2 Q3

-- Reset | L X X X

-- Hold | H L L X X X | Q0 Q1

-- Shift Left \mid H H L X H/L X \mid Q1 Q2

-- Shift Right | H L H H/L X X | H/L Q0

-- Parallel Load | H H H X X Pn| P0 P1

```

# 74x194 – VHDL Description

```

library ieee;

use ieee.std logic 1164.all;

-- entity declaration

entity 1s194 is

port(

-- main clock

clk : in std logic;

-- async master reset

mr n : in std logic;

-- shift control signals

s0,s1 : in std logic;

-- shift input data

dsr, dsl ser: in std logic;

-- parallel load data

p : in std logic vector(3 downto 0);

-- output data

q : out std logic vector(3 downto 0));

end 1s194;

```

# 74x194 – VHDL Description

```

architecture behav of 1s194 is

signal temp: std logic vector(3 downto 0);

signal ctrl: std logic vector (1 downto 0);

begin

ctrl <= s0 & s1;

shift proc: process(clk, mr n)

begin

if (mr n = '0') then

temp <= (others => '0');

elsif (rising edge(clk)) then

case ctrl is

when "11" => temp <= p;</pre>

when "10" => temp <= dsr & temp(3 downto 1);</pre>

when "01" => temp <= temp(2 downto 0) & dsl;</pre>

when others => temp <= temp;</pre>

end case;

end if;

end process shift proc;

q \le temp;

end behav;

```

## 74x194 - Test Bench

```

-- example of test bench to test the 1s194

library ieee;

use ieee.std logic 1164.all;

entity test bench is

end test bench;

architecture tb of test bench is

-- internal signal declarations

signal clk tb: std logic:= '1';

signal s0 tb, s1 tb, mr tb n, dsr tb, dsl tb: std logic:= '0';

signal p tb, q tb : std logic vector (3 downto 0);

```

## 74x194 - Test Bench

```

-- constant declarations

constant clk period: time := 200 ns;

begin

-- component instantiation

U1: work.entity.ls194 port map(

clk => clk tb,

mr_n => mr tb n,

s0 => s0 tb

s1 \Rightarrow s1 tb,

dsr => dsr tb,

dsl => dsl tb,

p => p_tb,

q \Rightarrow q \text{ tb};

-- clock generation

clk tb <= not clk tb after clk period/2;</pre>

```

#### 74x194 – Test Bench

```

main proc: process

begin

-- check initialization (reset)

wait for 10 ns;

assert q_tb = "0000"

report " Initialization Error "

severity ERROR;

wait for 2 * clk period;

mr tb n <= '1';

-- check synchronous load

s0 tb <= '1';

s1 tb <= '1';

p tb <= "0110";

wait for clk period;

```

## 74x194 - Test Bench

```

-- wait until falling edge clk tb

wait until clk tb = '0';

assert q tb = "0110"

report " Load Error "

severity ERROR;

-- check shift left

s0 tb <= '0';

-- wait until falling edge clk tb

wait until clk tb = '0';

assert q tb = "1100"

report " Error: Shift left Failed "

severity ERROR;

wait for 3 * clk period;

```

## 74x194 - Test Bench

```

-- three more shift left

for i in 0 to 2 loop

if i = 1 then

dsl tb <= '0';

else

dsl_tb <= \1';

end if;

wait until clk tb = '0';

end loop;

assert q_tb = "0101"

report " Error: serial left shift failed "

severity ERROR;

wait for 5 * clk period;

wait until clk tb = '0';

```

## 74x194 – Test Bench

```

-- shift right

s0 tb <= '1';

s1 tb <= '0';

wait for c3 * clk period;

assert q tb = "0001"

report " Error: serial left shift failed "

severity ERROR;

wait for clk period;

-- change load value

s0 tb <= '1';

s1 tb <= '1';

p tb <= "0101";

wait for clk period;

```

# 74x194 - Test Bench

```

-- wait until falling edge clock

wait until clk tb = '0';

assert q tb = "0101"

report " Error: load failure. . "

severity ERROR;

wait for clk period;

-- check left shift

s0 tb <= '0';

s1 tb <= '1';

wait for 3 *clk period;

assert q tb = "0111"

report " Error: shift left failure. . "

severity ERROR;

end process main proc;

end tb;

```

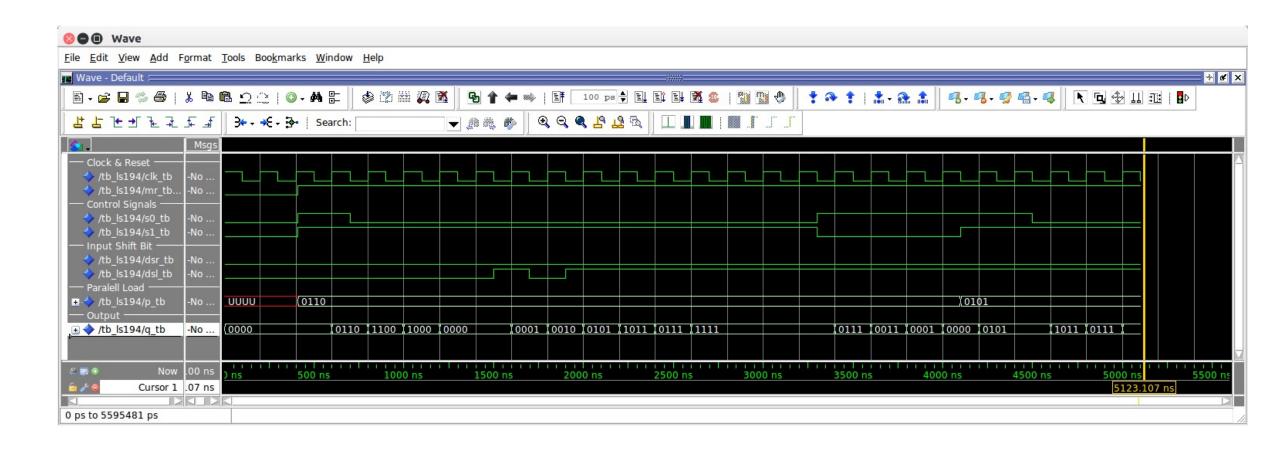

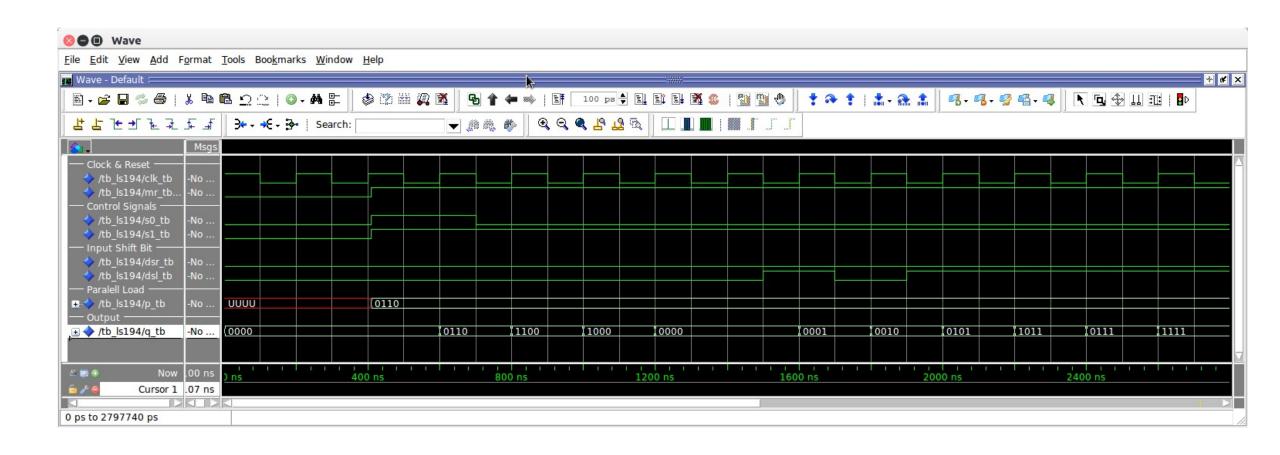

# **Simulation Waveforms - 1**

# Simulation Waveforms – 1a

# Simulation Waveforms – 1b