### The Abdus Salam International Centre for Theoretical Physics

The RVI communication block: ComBlock

**Maynor Ballina**

Multidisciplinary Laboratory ICTP

> Trieste - Italy 2023

Joint ICTP-IAEA School on Systems-on-Chip based on FPGA for Scientific Instrumentation and Reconfigurable Computing

# IAEA

### Introduction

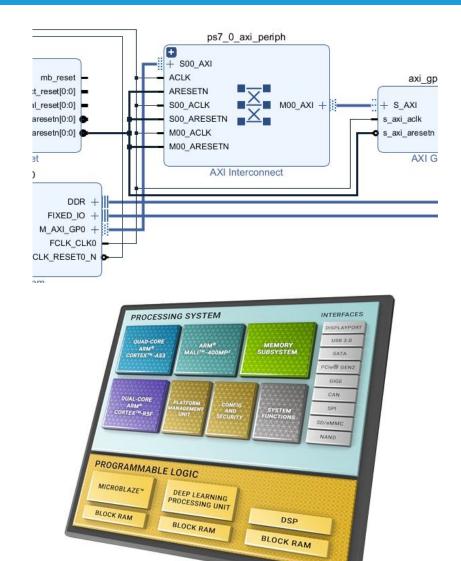

- Vendor specific interconnects (AXI, AVALON, Chiplink).

- What we learned yesterday?

- AXI interconnect,

- memory address,

- data.

- Communication Block (ComBlock ).

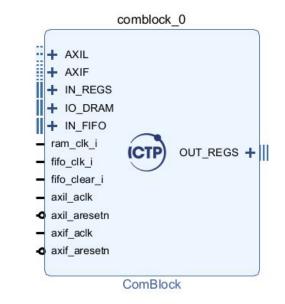

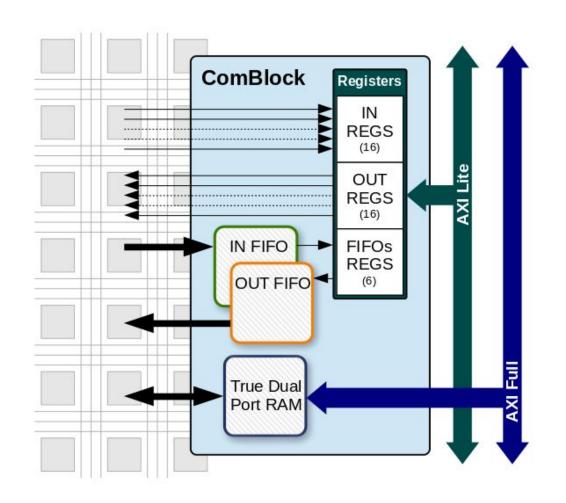

### What is the ComBlock?

A communication block that abstracts you from the AXI protocol.

- Interconnect: AXI Known interfaces (registers, RAM and FIFOs).

- Configurable resources, width, length, etc.

- Simple Clock-Domain-Crossing with FIFOs and TDPRAM.

- C driver for easy complete project integration.

### **Features**

- I/O Registers, I/O FIFOS, and TDPRAM.

- AXI Lite: Registers and FIFOs.

- AXI Full: TDPRAM.

## Registers

- 16 input registers (FPGA to Processor).

- 16 output registers (Processor to FPGA).

- User configurable data width, 1-32 bits.

- Input and output independently enabled.

| (                                                      |                                      | Registers      |       |          |              |          |            |

|--------------------------------------------------------|--------------------------------------|----------------|-------|----------|--------------|----------|------------|

| + AXIL<br>Ⅲ — IN_REGS                                  | OUT_REGS -                           | Input (FPGA to | PROC) |          | Output (PROC | to FPGA) |            |

| <ul> <li>reg0_i[31:0]</li> <li>reg1_i[31:0]</li> </ul> | reg0_o[15:0] > -<br>reg1_o[15:0] > - | 🗹 Enable       |       |          | 🕑 Enable     |          |            |

| axil_aclk                                              | reg2_o[15:0] 🕨 -                     | Data Width     | 32 📀  | [1 - 32] | Data Width   | 16       | 🔕 [1 - 32] |

| • axil_aresetn                                         |                                      | Quantity       | 2 🔇   | [1-16]   | Quantity     | 3        | 8 [1 - 16] |

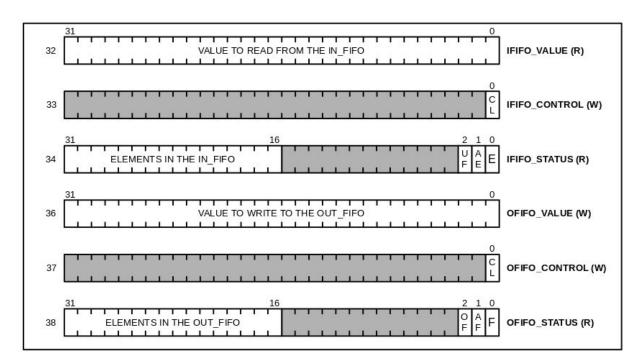

### **FIFOs**

- Input and output FIFOs.

- Customizable width and depth.

- Asynchronous.

- Control registers on the Processor's side.

| + AXIL                                                                              |                                                         | FIFOs                |      |                       |                     |     |           |

|-------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------|------|-----------------------|---------------------|-----|-----------|

| - IN_FIFO                                                                           |                                                         | Input (FPGA to PROC) |      | Output (PROC to FPGA) |                     |     |           |

| <ul> <li>▶ fifo_we_i</li> <li>▶ fifo_data_i(15:0)</li> <li>◄ fifo_full_o</li> </ul> | OUT_FIFO — III<br>fifo_re_i < -<br>fifo_data_o(7:0) > - | 🗹 Enable             |      |                       | 🕑 Enable            |     |           |

| ◄ fifo_afull_o                                                                      | fifo_valid_o 🕨 🗕                                        | Data Width           | 16   | 🕲 [1 - 32]            | Data Width          | 8   | 0 [1 - 32 |

| ◄ fifo_overflow_o<br>fifo_clk_i                                                     | fifo_empty_o > -<br>fifo_aempty_o > -                   | Depth                | 1024 | 0                     | Depth               | 256 | 3         |

| · fifo_clear_i<br>· axil_aclk                                                       | fifo_underflow_o 🕨 🗕                                    | Almost Full Offset   | 1    | 0                     | Almost Full Offset  | 1   | 3         |

| axil_aresetn                                                                        |                                                         | Almost Empty Offset  | 1    | 8                     | Almost Empty Offset | 1   | \$        |

### **TDPRAM**

- Bidirectional.

- Clock-domain-crossing.

- Configurable depth, width and address width.

| + AXIF                                                        | True Dual Port RA | M (FPGA to | PROC, PR | ROC to FPGA) |

|---------------------------------------------------------------|-------------------|------------|----------|--------------|

| – IO_DRAM<br>🕨 ram_we_i                                       | 🕑 Enable          |            |          |              |

| <ul> <li>ram_addr_i[15:0]</li> <li>ram_data_i[7:0]</li> </ul> | Data Width        | 8          | 0        | [1 - 32]     |

| ◀ ram_data_o[7:0]<br>ram_clk_i                                | Address Width     | 16         | ٨        | [1 - 32]     |

| axif_aclk<br>axif_aresetn                                     | Depth             | 0          | 0        |              |

### **Processor interaction**

- Device information in **xparameters.h.**

- Register mappings in **comblock.h**.

- CB\_IREG, CB\_OREG, ...

- Control registers.

### **C** Drivers

• Read and write functions **single memory position**:

void cbWrite(UINTPTR baseaddr, u32 reg, u32 value)

u32 cbRead(UINTPTR baseaddr, u32 reg)

• Read and write several **contiguous memory positions**:

void cbWriteBulk(UINTPTR baseaddr, int \*buffer, u32 depth)

void cbReadBulk(int \*buffer, UINTPTR baseaddr, u32 depth)

### Where and how to get it?

• Hosted on GitLab:

git clone <u>https://gitlab.com/ictp-mlab/core-comblock.git</u>

- Completely open source under BSD 3-clause license.

- Rodrigo Melo, collaboration between the Multidisciplinary Laboratory (MLAB) from The Abdus Salam International Centre for Theoretical Physics (ICTP, Italy) and the FPGA division of Micro and Nanotechnology from the National Institute of Industrial Technology (INTI, Argentina).

The Abdus Salam International Centre for Theoretical Physics

**Introduction to Lab 2**

# ComBlock and RTL instantiation

Prepared by Maynor Ballina and Bruno Valinoti

Multidisciplinary Laboratory ICTP

Joint ICTP-IAEA School on Systems-on-Chip based on FPGA for Scientific Instrumentation and Reconfigurable Computing

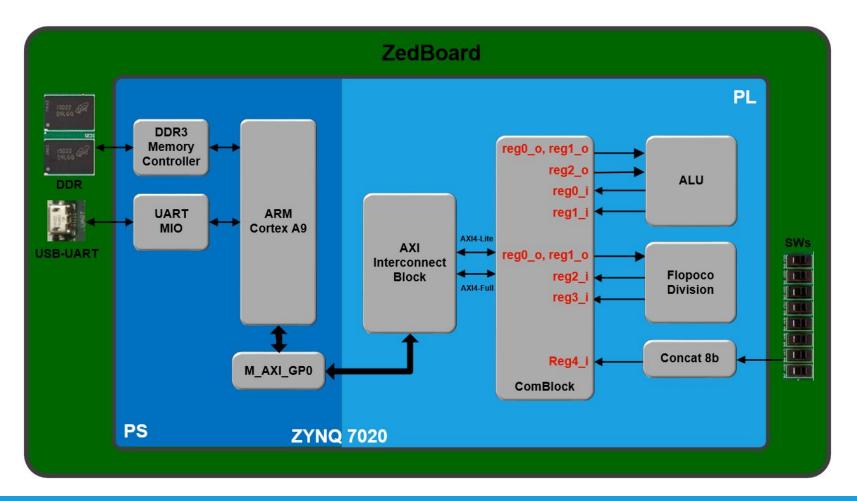

# **Objectives**

- Simulate a simple Arithmetic Logic Unit and understand the VHDL code.

- Use and configuration of the ComBlock IP.

- Understand the data transfer between PL and PS using ComBlock IP.

- Instantiate RTL blocks and control them through the ComBlock registers.

- Perform unsigned integer arithmetic operations.

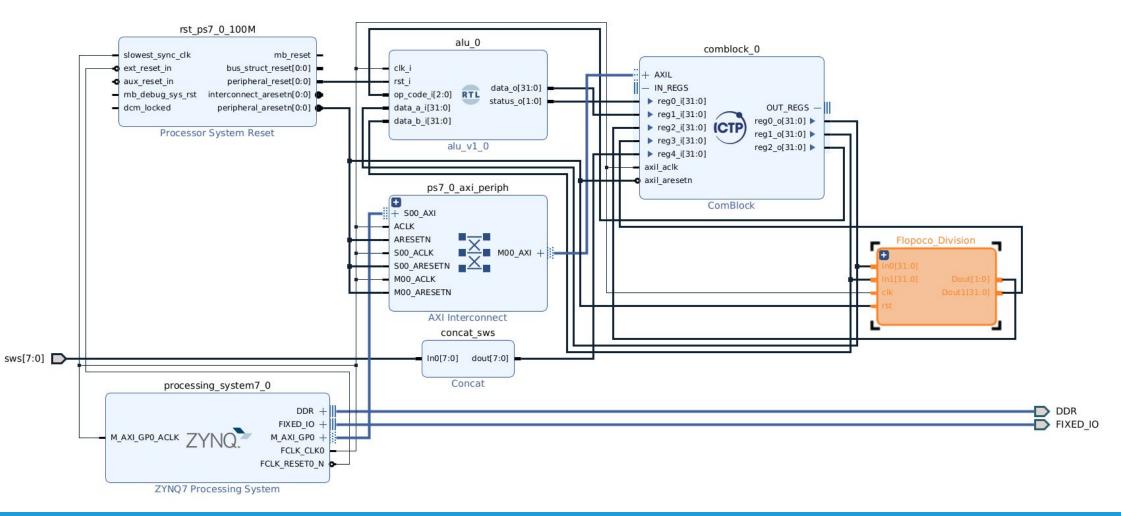

### **Design description**

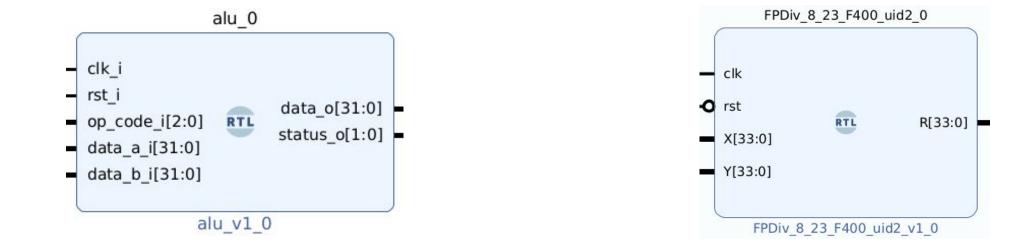

## **ALU and Division Block**

- RTL block, VHDL coded.

- Unsigned integer data.

- Customizable data width.

- RTL block, VHDL, generated by **Flopoco**.

- 32 bit floating point representation.

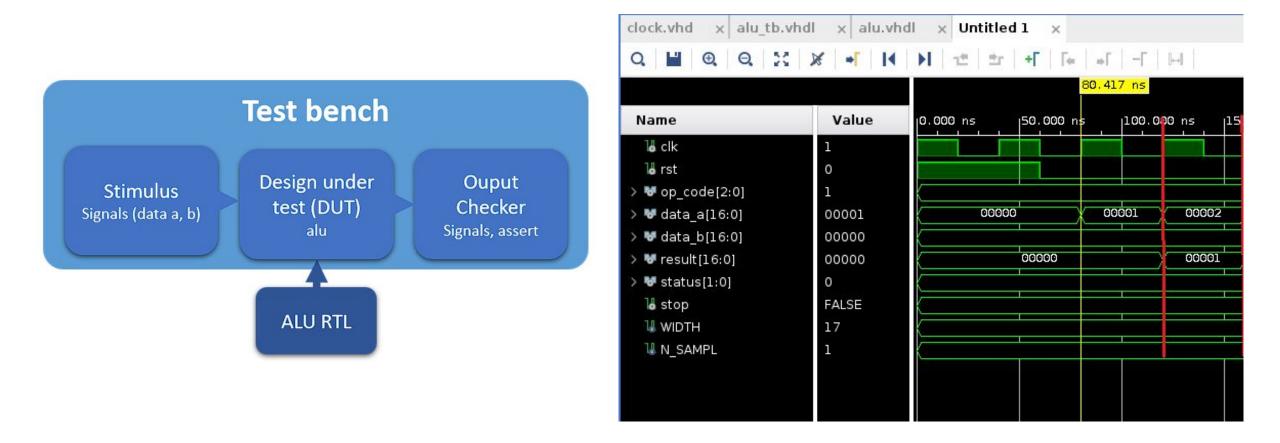

### **Simulation**

### **Hardware creation**

### **Software**

- C driver, use ComBlock instructions.

- Configuration and data exchange.  $\bullet$

- Unsigned integer arithmetic operations. lacksquare

- Select the operation with an SW. lacksquare

- Identify and print status flag.  ${\color{black}\bullet}$

| ### Testing the Comblock Registers |

|------------------------------------|

| Data in A=10, B=5                  |

| operation status: 0                |

| operation option = 0, result = 0   |

| operation status: 0                |

| operation option = 1, result = 15  |

| operation status: 0                |

| operation option = 2, result = 5   |

| operation status: 0                |

| operation option = 3, result = 0   |

| operation status: 0                |

| operation option = 4, result = 0   |

| operation status: 0                |

| operation option = 5, result = 0   |

| operation status: 0                |

| operation option = 6, result = 0   |

| operation status: 0                |

| operation option = 7, result = 320 |

| operation exn: 0                   |

| division R = 320                   |

| sws value: 9                       |

### The Abdus Salam International Centre for Theoretical Physics

Joint ICTP-IAEA School on Systems-on-Chip based on FPGA for Scientific Instrumentation and Reconfigurable Computing

### Thank you!