Joint ICTP-IAEA School on Systems-on-Chip based on FPGA for Scientific Instrumentation and Reconfigurable Computing

# School on FPGA-based SoC Lab 3: UDMA

**Agustin Silva**

- Import HLS IP block

- Understand the usage of the UDMA

- Transfer data between the PC and the FPGA

- Interact within JupyterLab with custom hardware

- Every step is described in Laboratory 3 UDMA

- Import HLS IP block

- Understand the usage of the UDMA

- Transfer data between the PC and the FPGA

- Interact within JupyterLab with custom hardware

- Every step is described in Laboratory 3 UDMA

- Import HLS IP block

- Understand the usage of the UDMA

- Transfer data between the PC and the FPGA

- Interact within JupyterLab with custom hardware

- Every step is described in Laboratory 3 UDMA

- Import HLS IP block

- Understand the usage of the UDMA

- Transfer data between the PC and the FPGA

- Interact within JupyterLab with custom hardware

- Every step is described in Laboratory 3 UDMA

- Import HLS IP block

- Understand the usage of the UDMA

- Transfer data between the PC and the FPGA

- Interact within JupyterLab with custom hardware

- Every step is described in Laboratory 3 UDMA

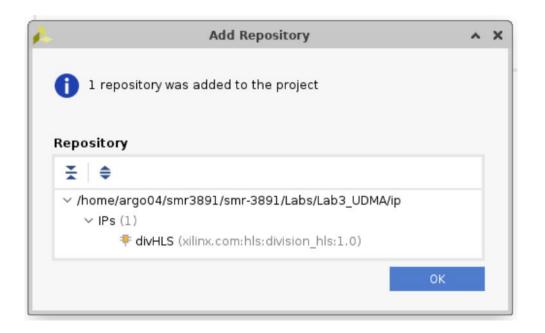

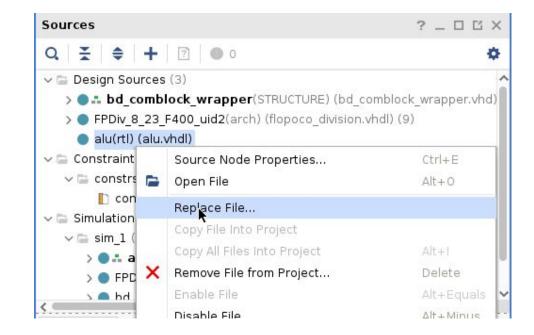

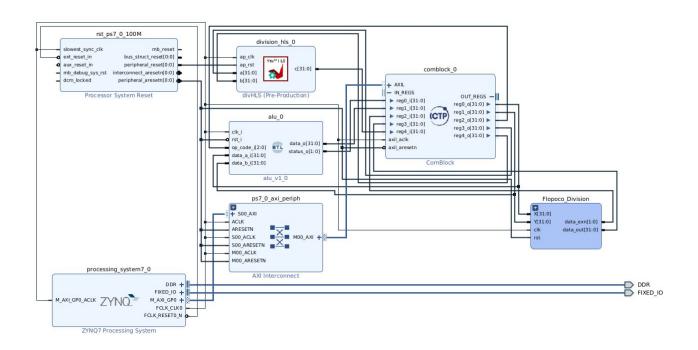

# Import HLS IP and update modules

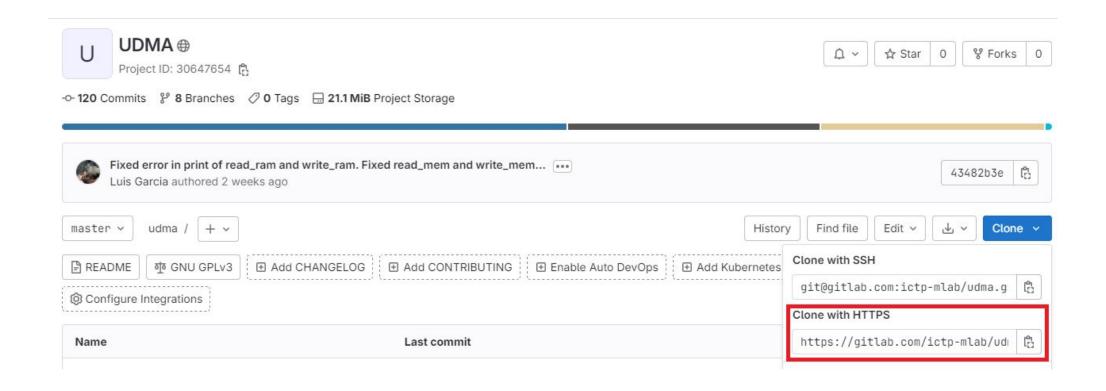

#### Install UDMA

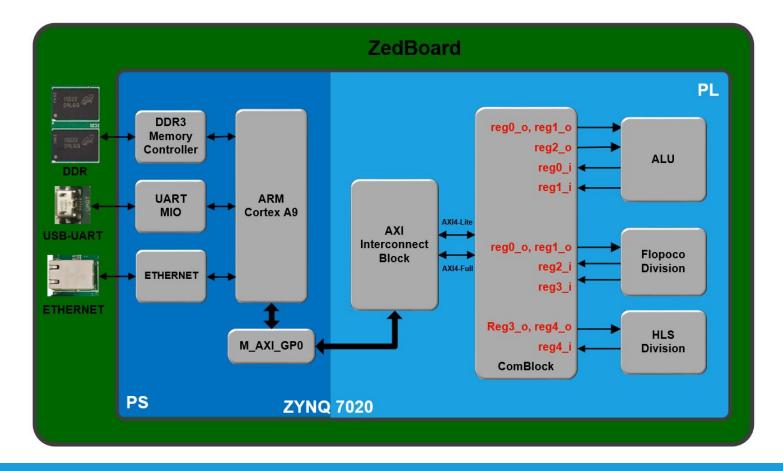

# Software/hardware co-design

- Vhdl same as always

- Python same as always

# Software/hardware co-design

- Vhdl same as always

- Python same as always

```

import udma

import numpy as np

import matplotlib.pyplot as plt

from tqdm import trange

```

#### FreeRTOS + UDMA server in the PS

#### Make sure connection is established

```

GTKTerm - /dev/ttyACM0 115200-8-N-1

File Edit Log Configuration Control signals View Help

-----UDMA Server-----

Board IP: 192.168.1.10

Netmask : 255.255.255.0

Gateway : 192.168.1.1

Start PHY autonegotiation

Waiting for PHY to complete autonegotiation.

autonegotiation complete

link speed for phy address 0: 1000

unable to determine type of EMAC with baseaddress 0xE000B000

Server Port Connect With..

UDMA server 7

/dev/ttyACM0 115200-8-N-1

DTR RTS CTS CD DSR RI

```

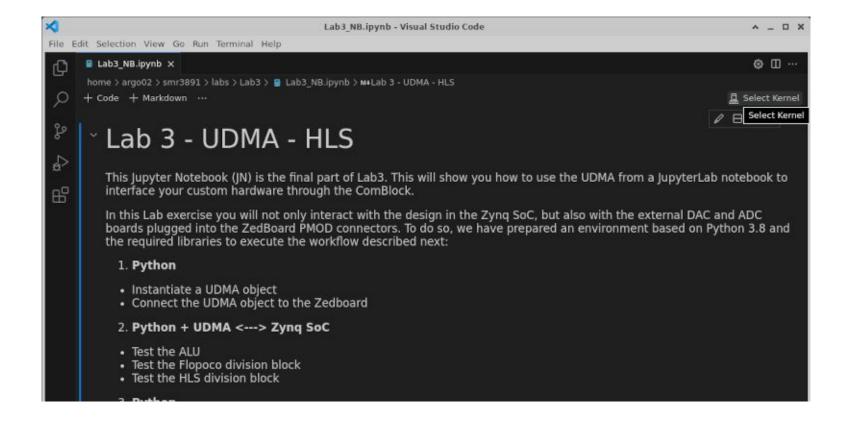

### Jupyter Notebook and UDMA

#### How to use it

- Import udma class to write and read the comblock

- Interact with registers, fifos and RAM with python

```

cb = udma.UDMA_CLASS('192.168.1.10', 7)

cb.connect()

cb.log(0)

```

#### How to use it

- Import udma class to write and read the comblock

- Interact with registers, fifos and RAM with python

```

for i in trange(100):

x = np.random.randint(0,32767)

cb.write_fifo(1, [x])

#print(x)

while (cb.read_reg(1)[1][0] & 1 == 0):

pass

```

#### **UDMA Methods**

```

UDMA class

13

Attributes:

14

15

ip: str

16

port: int

s: socket

17

18

Methods

19

set ip(ip)

/ get ip()

set port(port)

/ get port()

20

connect()

disconnect()

21

22

read reg(reg)

/ write reg(reg, data)

read fifo(N)

23

/ write fifo(N, data)

read ram(addr, length, inc)

/ write ram(addr, length, inc, data)

24

read mem(addr, length, inc)

/ write mem(addr, length, inc, data)

25

select comblock()

26

log()

27

```

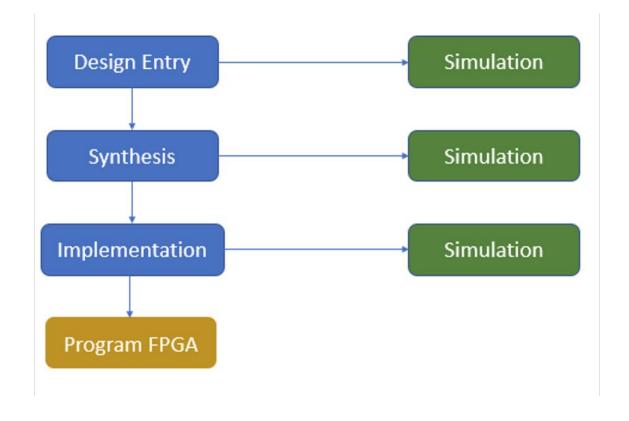

# Debugging, testbench and verification

### Examples 1.

https://github.com/agustinsilva447/QMARL\_FPGA/blob/main/QMARL\_6/qmarl\_udma.ipynb

### Examples 2.

https://github.com/agustinsilva447/QMARL\_FPGA/blob/main/final\_2qagents/qdma.ipynb

Thank you! Have fun =D