Joint ICTP-IAEA School on Systems-on-Chip based on FPGA for Scientific Instrumentation and Reconfigurable Computing

## Introduction to Laboratory 4

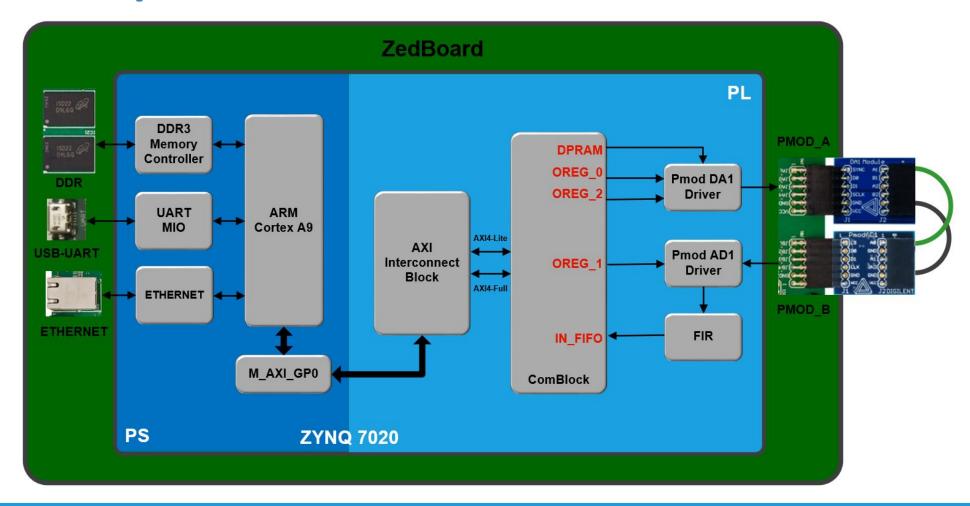

# SoC-FPGA DAQ system and TCL

Prepared by Iván Morales and Romina Molina

Multidisciplinary Laboratory STI Unit, ICTP

Trieste - Italy 2023

• Learn how to work in a collaborative environment with version control tools, employing **tcl** commands for hardware recreation.

- Learn how to work in a collaborative environment with version control tools, employing tcl

commands for hardware recreation.

- Perform the instantiation of an IP core previously designed through High-level Synthesis tool.

- Learn how to work in a collaborative environment with version control tools, employing **tcl** commands for hardware recreation.

- Perform the instantiation of an IP core previously designed through High-level Synthesis tool.

- Integrate PMOD modules into the hardware design to control and acquire signals in the analog domain from the SoC.

- Learn how to work in a collaborative environment with version control tools, employing **tcl** commands for hardware recreation.

- Perform the instantiation of an IP core previously designed through High-level Synthesis tool.

- Integrate PMOD modules into the hardware design to control and acquire signals in the analog domain from the SoPC.

- Understand the benefits of a higher abstraction level when using the UDMA environment for interaction.

## **Design description**

Learn how to work in a collaborative environment with version control tools, employing **tcl** commands for hardware recreation.

- Git-compatible text-based source code

- Reproducibility

- Collaboration

- Reliability

- Complex deployments

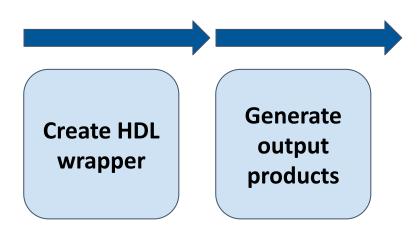

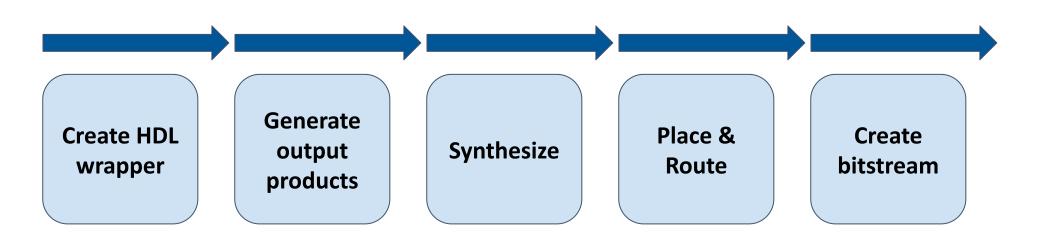

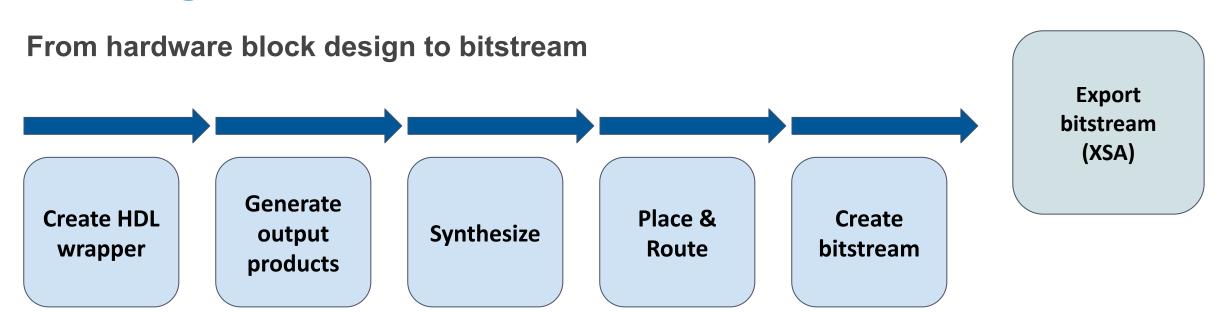

Vivado - Hardware block design

Vivado - Hardware block design

Vivado - Hardware block design

Vivado - Hardware block design

Add the IP

locations

to the repo

Vivado - Hardware block design

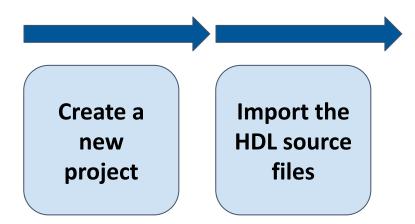

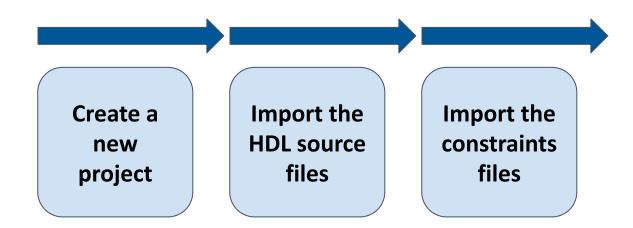

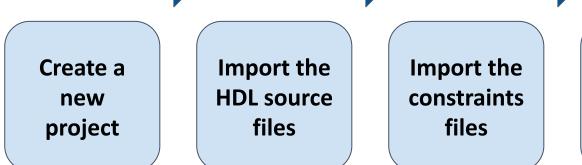

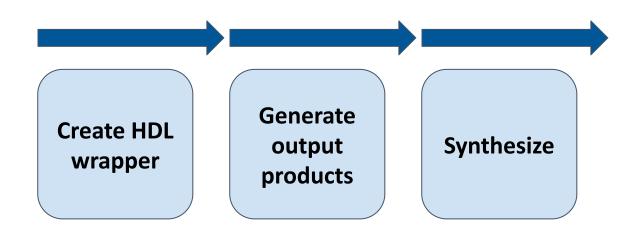

Create a new project

Import the HDL source files

Import the constraints files

Add the IP locations to the repo

Recreate the Block Design using TCL

Vivado - Hardware block design

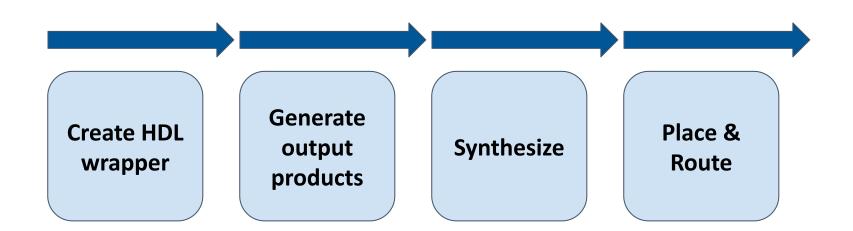

Create a new project

Import the HDL source files

Import the constraint files

Add the IP locations to the repo

Recreate the Block Design using TCL Block design created from source code

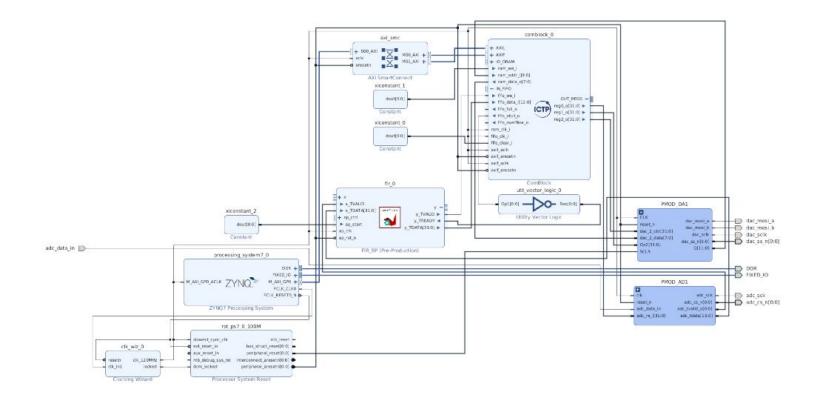

#### Vivado - Expected block design

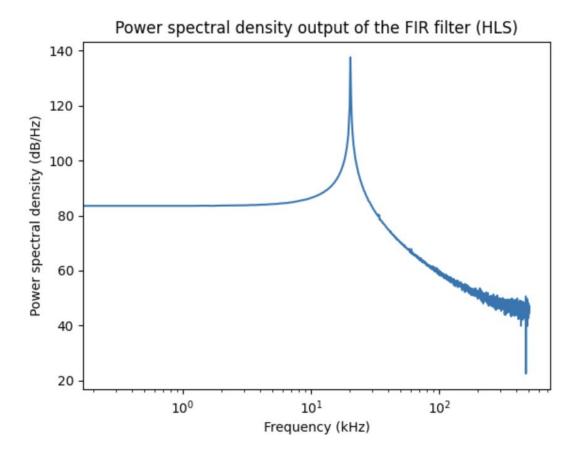

## Perform the instantiation of an IP core previously designed through High-level Synthesis (HLS) tool.

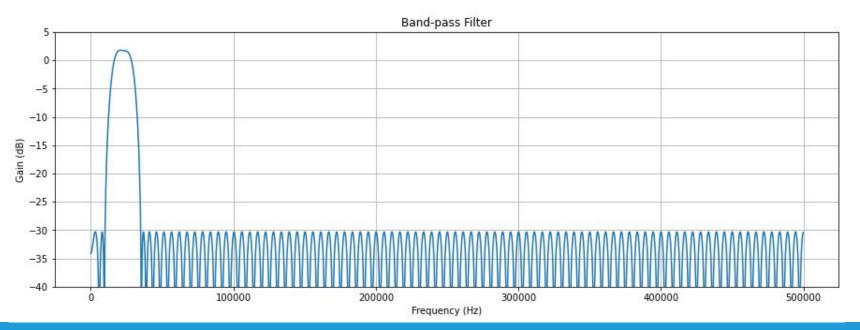

- Finite-impulse response (FIR) bandpass filter implemented in HLS

- Instantiation in Vivado Block Design

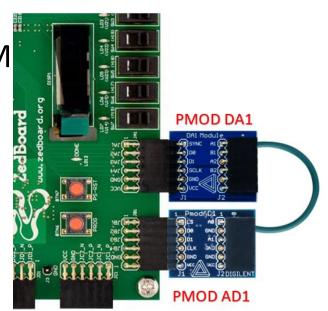

## Integrate PMOD modules into the hardware design to control and acquire signals in the analog domain from the SoPC.

- A/D and D/A Control using ComBlock's output registers

- Start conversion, data format

- D/A converter (1 Msps)

- Arbitrary waveform generator using ComBlock's DP-RAM

- A/D converter (1 Msps)

- Digitizing analog output from D/A (wire loopback)

- Data acquisition using ComBlock's Input FIFO

## Understand the benefits of a higher abstraction level when using the UDMA environment for interaction.

- UDMA in Jupyter Notebook to interface the ComBlock in the PL remotely

- Arbitrary waveforms from Python numeric libraries

- Plotting and recording A/D data using Matplotlib (Python)

- Using markdown to document within the Jupyter Notebook

## Understand the benefits of a higher abstraction level when using the UDMA environment for interaction.

- Post-processing of recorded data in Jupyter Notebook

- FFT of the bandpass filter response

- Challenges

- Experimental bode plot

- Changing HLS FIR filter response

Joint ICTP-IAEA School on Systems-on-Chip based on FPGA for Scientific Instrumentation and Reconfigurable Computing

#### Thank you!

Trieste - Italy 2023