Joint ICTP-IAEA School on Systems-on-Chip based on FPGA for Scientific Instrumentation and Reconfigurable Computing

**Introduction to Project 1**

#### Digital Pulse Processing for Isotope Identification

Prepared by Iván Morales, Mladen Bogovac, and Romina Molina

Multidisciplinary Laboratory STI Unit, ICTP

## Lab Project 1 - Goals and methodology

Main objective

• Build a radiation detection and processing system in the SoC/FPGA to identify a gamma source

Methodology

- Model the detector behavior using experimental data (offline processing)

- Use the detector characteristics to fine-tune the digital pulse processing (DPP) system

- Determine an unknown isotope type from its energy spectrum information (fingerprint)

- (Challenge) Update the DPP to improve its reliability in aggressive environments

#### Lab Project 1 - Two stages + challenge

- Stage 1 Modeling the detector

- Build a data acquisition system (DAQ) using the SoC/FPGA to record several pulses from the gamma radiation detector

- $\circ$   $\,$  Use the recorded pulse shapes to fit the parameters that better describe the detector  $\,$

- Stage 2 Identifying the isotope

- Build and fine-tune a digital pulse processing (DPP) system in the SoC/FPGA to:

- Compute the energy deposited in the detector of each interaction with a gamma radiation source (energy spectrum)

- Assess the functionality of the multiple DPP stages using a Python-based interface

- Stage 3 Challenge

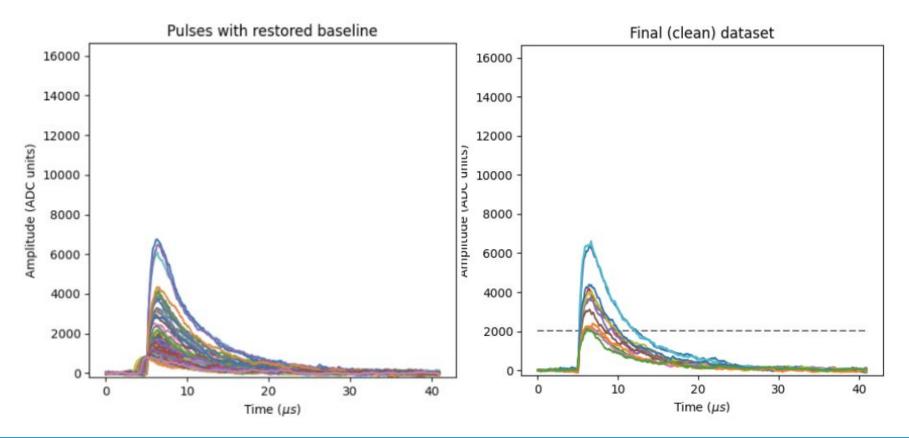

- Improve the DPP with a baseline restorer and pile-up rejector

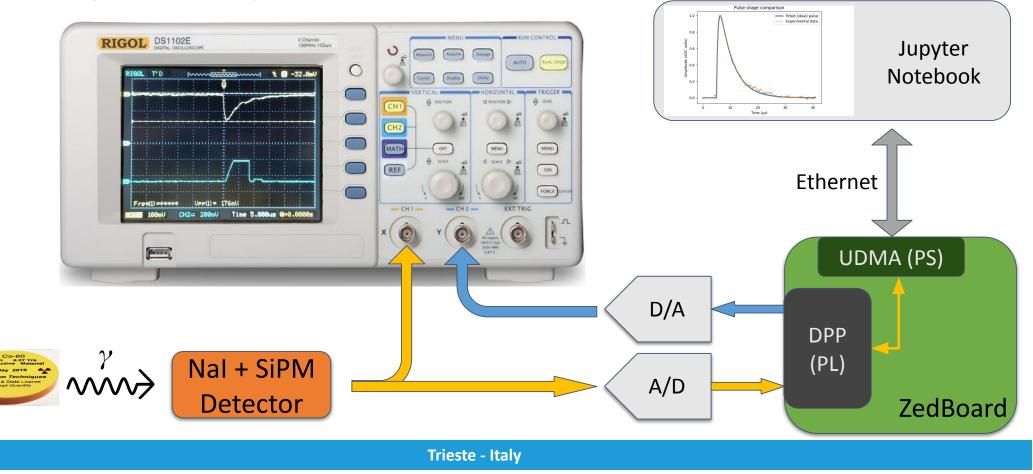

#### Lab Project 1 - System overview

# Stage 1

# Data acquisition system for detector characterization

## Lab Project 1 - stage 1: specific objectives

• Compute the parameters that better fit the behavior of the detector

Methodology

- Acquire and record a dataset of several raw pulses from the detector, using the SoC/FPGA DAQ via UDMA

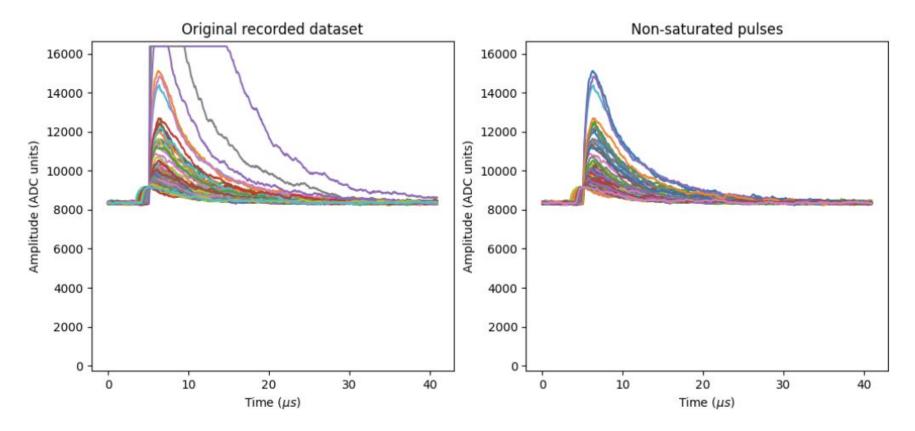

- Wrangle the experimental dataset to remove unwanted pulses and restore their baseline.

- Fit the recorded pulses to get the average parameters that better represent the ideal pulse model of the detector.

### Lab Project 1 - stage 1: specific objectives

#### ... but this is not a data science school!

# Stage 1.1 - DAQ

#### Lab Project 1 - stage 1: methodology

- Your task ← create the DAQ and acquire the data

- Our task ← semi-automatic data analysis library

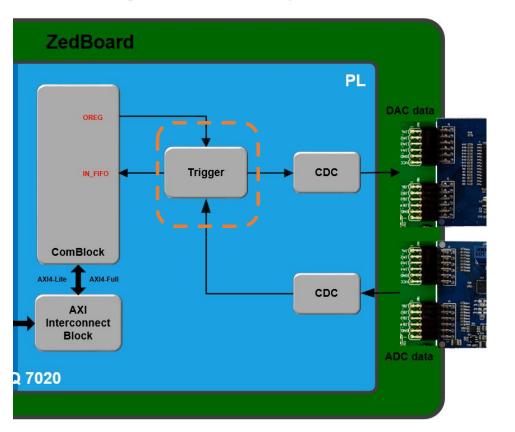

#### **Design description - DAQ**

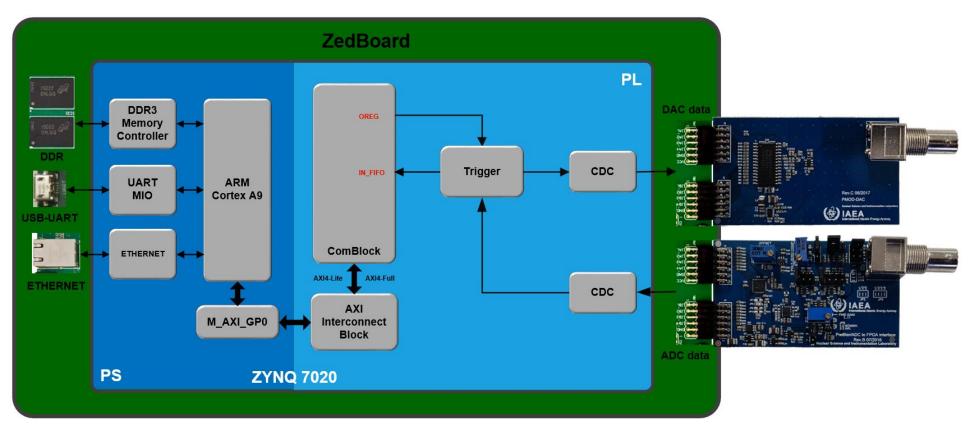

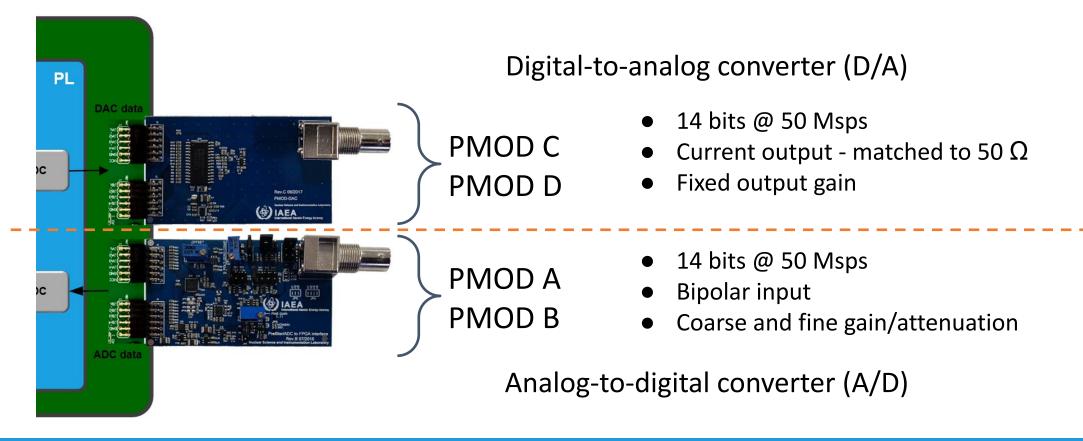

### **Design description - analog front-end**

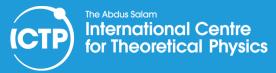

#### **Design description - multiple clock domains**

#### **Design description - data recording interface**

Trigger logic - basic oscilloscope core

- Input registers

- Pulse length (in sample units)

- Threshold level (in ADC units)

- Samples before trigger (delay)

- Output stream

- $\circ$  Captured pulse

# **Stage 1.2 - Offline data analysis**

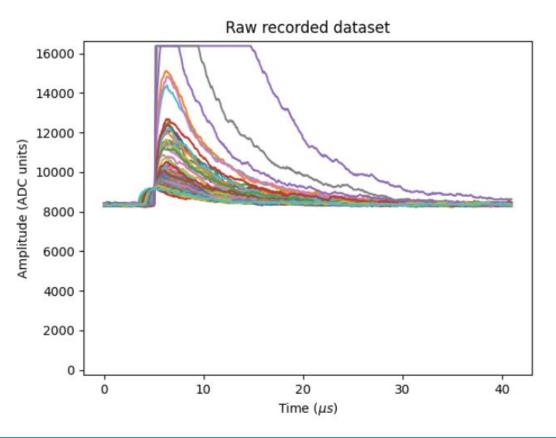

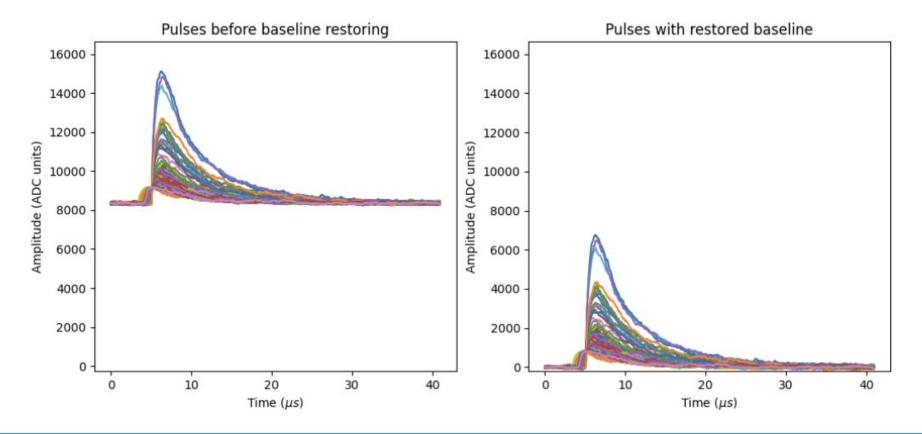

#### Raw dataset

- Saturation

- Baseline offset

- Small amplitude events

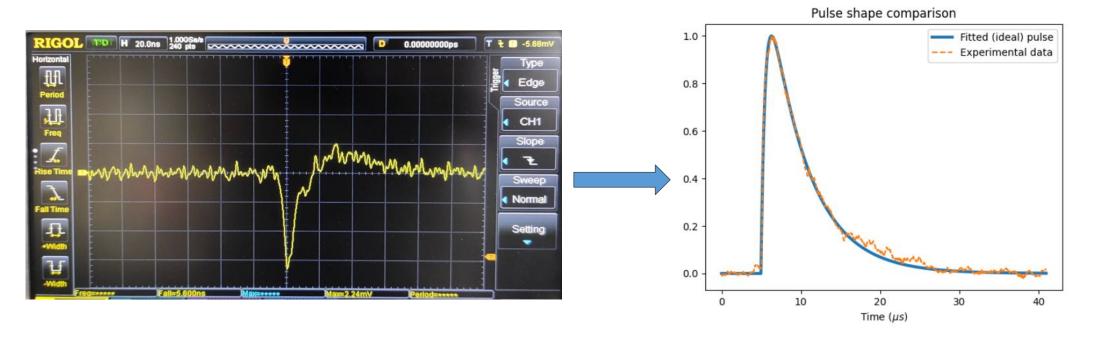

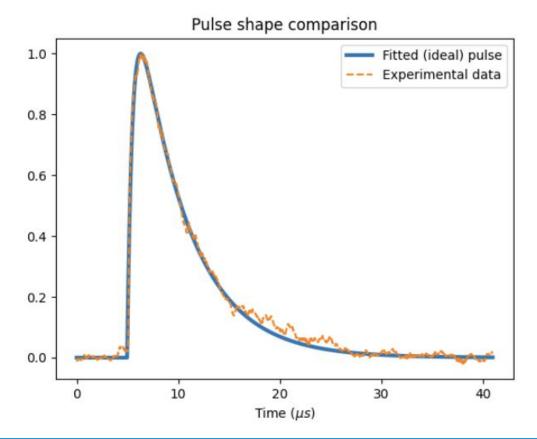

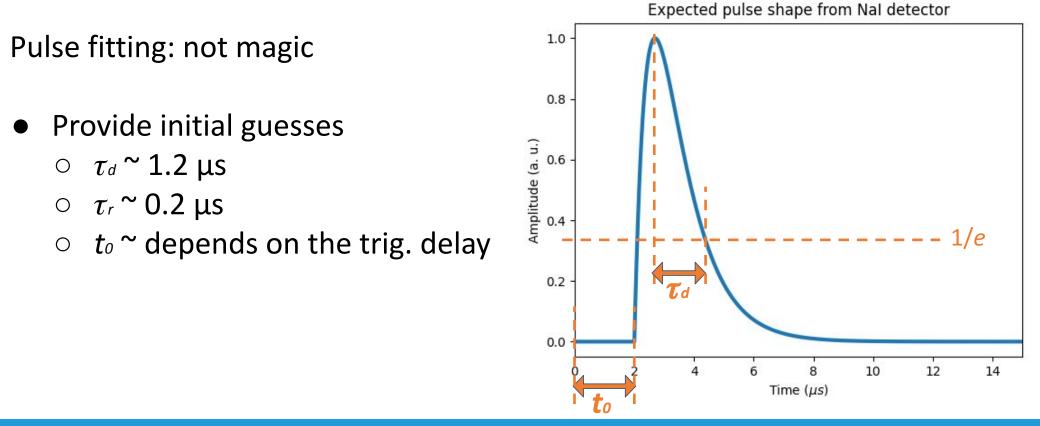

#### **Pulse model fitting**

Pulse model

$$y(t) = A\left(e^{(t-t_0)/ au_d} - e^{(t-t_0)/ au_r}

ight)$$

#### Fitting parameters

- Decay time constant  $(\tau_d)$

- Rise time constant (*τ*<sub>r</sub>)

- Time of arrival (t<sub>0</sub>)

## **Pulse model fitting**

#### Lab setup distribution

- Eight experimental setups

- One setup per row

- ictp\_share\_usb

Joint ICTP-IAEA School on Systems-on-Chip based on FPGA for Scientific Instrumentation and Reconfigurable Computing

#### Thank you!