# Workshop on Fully Programmable Systems-on-Chip for Scientific Applications

#### Lab 0: User environment

#### **Maynor Ballina**

### **Welcome: Lab tutors**

Maynor Ballina (ICTP, UNIT) [Guatemala]

Dr. Luis Garcia (ICTP) [Guatemala]

Dr. Romina Molina (ICTP) [Argentina]

Dr. Agustin silva (TII) [Argentina]

#### **Labs Overview:**

- Lab 0: User environment

- Lab 1: Hello World and GPIO In/Out

- Lab 2: ComBlock and RTL

- Lab 3: SoC-FPGA Development Framework

#### **Projects**

- Introduction to machine learning and SoC/FPGA

- Digital Pulse Processing for Isotope Identification

### **Labs Overview:**

- Lab 0: User environment

- Lab 1: Hello World and GPIO In/Out

- Lab 2: ComBlock and RTL

- Lab 3: SoC-FPGA Development Framework

#### **Projects**

- Introduction to machine learning and SoC/FPGA

- Digital Pulse Processing for Isotope Identification

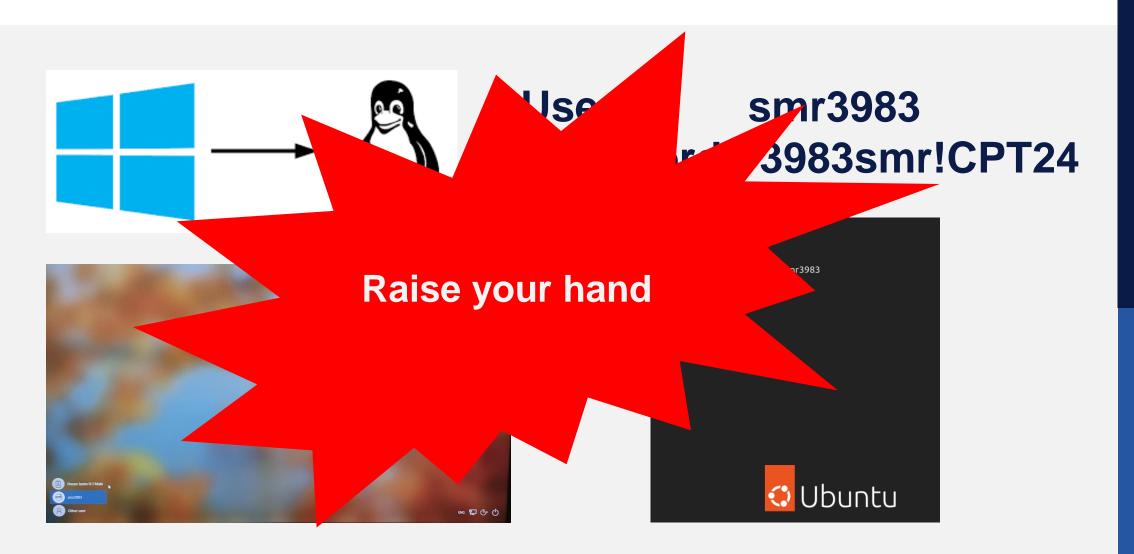

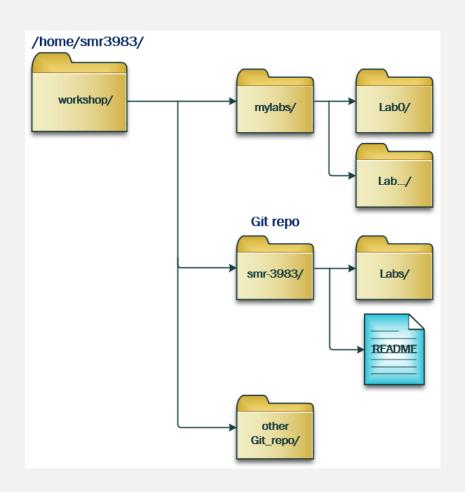

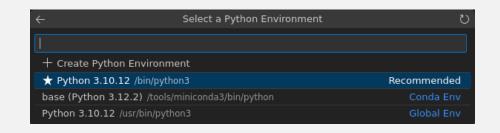

### **User Environment:**

## **User Environment:**

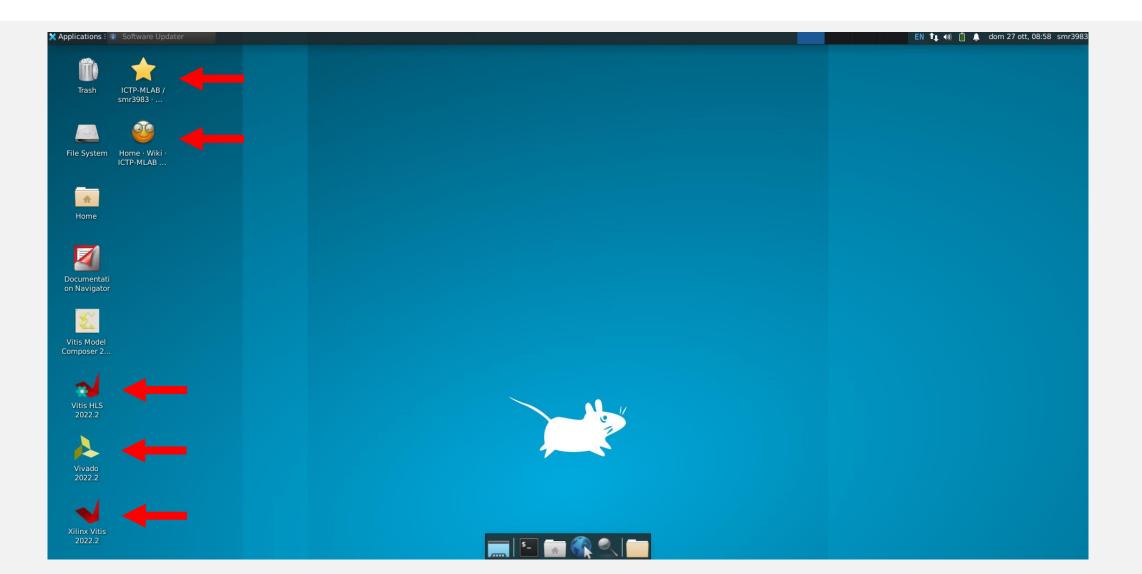

# **Important links:**

https://gitlab.com/ictp-mlab/smr-3983

# **Important links:**

https://gitlab.com/ictp-mlab/smr-3983/-/wikis/home

## Labs 0:

### Lab 1: Hello World and GPIO In/Out

#### **Maynor Ballina**

# **Labs 1: Objectives**

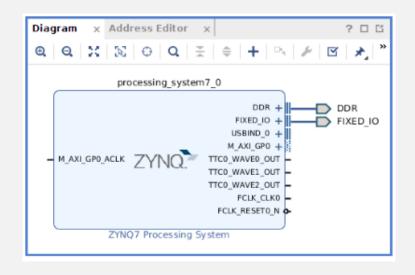

- Acquire the knowledge of the SoC-FPGA design flow using the Vitis Unified Software Platform.

- Create the hardware to configure the FPGA part of the SoC, configure the PS

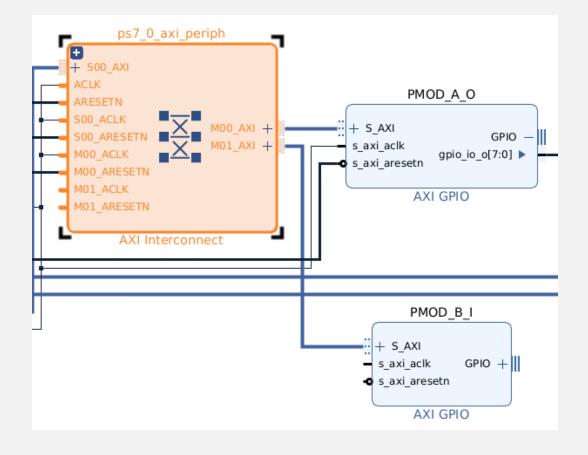

instantiate the GPIO blocks and understand the communication between the different

components of the design

- Create the 'C' application that will run on the PS to control the reading and the writing of the generated hardware

- Test the complete design on the ZedBoard platform to verify the implementation.

# **Labs 1: Design description**

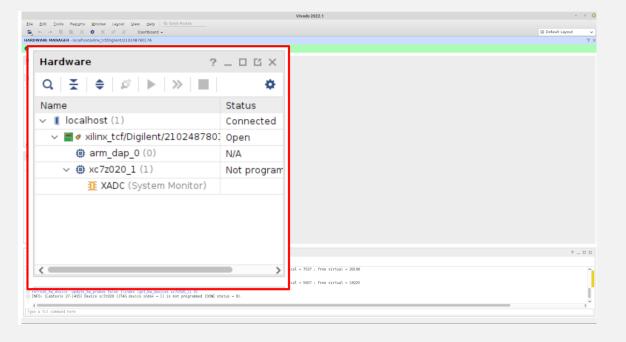

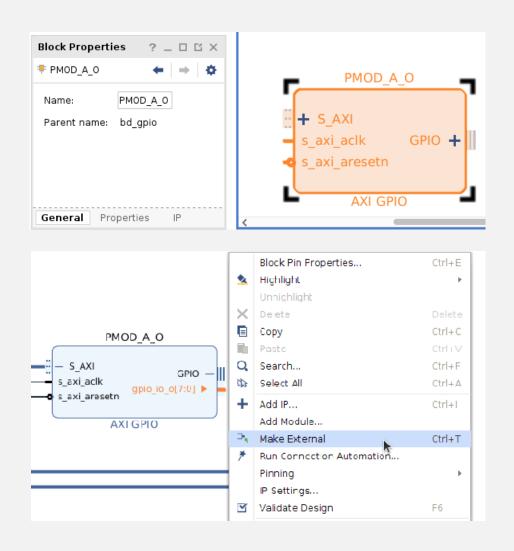

### **Labs 1: Hardware**

# Labs 1: Steps

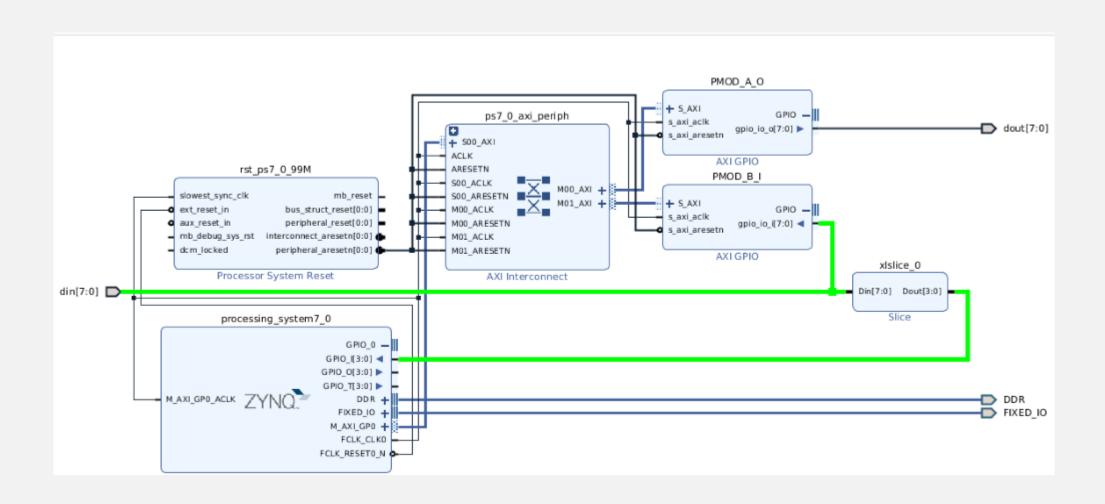

# **Labs 1: Final Block Design**

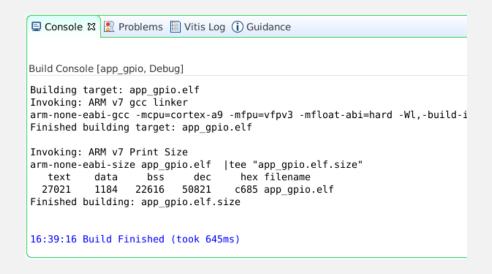

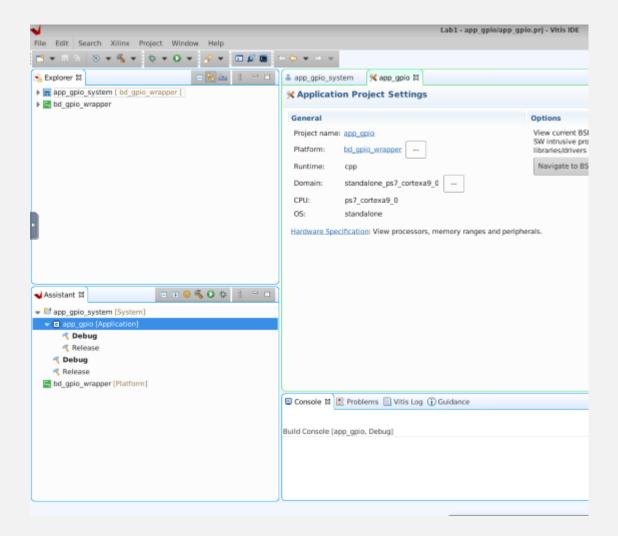

### **Labs 1: Software**

- Application project

- C program

- AXI Communication

### **Labs 1: Results**

- PL Hardware

- PS program

- AXI Communication

- PMOD data transfer

#### Optional:

Challenge

```

MODA Output: 213, PMODB Receive: 213 PSGPIO Receive 13

MODA Output: 214, PMODB Receive: 214 PSGPIO Receive 13

MODA Output: 215, PMODB Receive: 215 PSGPIO Receive 13

PMODA Output: 216, PMODB Receive: 216 PSGPIO Receive 13

PMODA Output: 217, PMODB Receive: 217 PSGPIO Receive 13

MODA Output: 218, PMODB Receive: 218 PSGPIO Receive 13

MODA Output: 219, PMODB Receive: 219 PSGPIO Receive 13

MODA Output: 220, PMODB Receive: 220 PSGPIO Receive 13

MODA Output: 221, PMODB Receive: 221 PSGPIO Receive 13

PMODA Output: 222, PMODB Receive: 222 PSGPIO Receive 13

MODA Output: 223, PMODB Receive: 223 PSGPIO Receive 13

MODA Output: 224, PMODB Receive: 224 PSGPIO Receive 14

MODA Output: 225, PMODB Receive: 225 PSGPIO Receive 14

PMODA Output: 226, PMODB Receive: 226 PSGPIO Receive 14

MODA Output: 227, PMODB Receive: 227 PSGPIO Receive 14

MODA Output: 228, PMODB Receive: 228 PSGPIO Receive 14

MODA Output: 229, PMODB Receive: 229 PSGPIO Receive 14

MODA Output: 230, PMODB Receive: 230 PSGPIO Receive 14

MODA Output: 231, PMODB Receive: 231 PSGPIO Receive 14

MODA Output: 232. PMODB Receive: 232 PSGPIO Receive 14

MODA Output: 233, PMODB Receive: 233 PSGPIO Receive 14

MODA Output: 234, PMODB Receive: 234 PSGPIO Receive 14

MODA Output: 235, PMODB Receive: 235 PSGPIO Receive 14

MODA Output: 236, PMODB Receive: 236 PSGPIO Receive 14

MODA Output: 237, PMODB Receive: 237 PSGPIO Receive 14

MODA Output: 238, PMODB Receive: 238 PSGPIO Receive 14

MODA Output: 239, PMODB Receive: 239 PSGPIO Receive 14

```

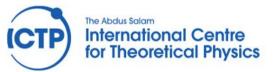

User: smr3983 Password: 3983smr!CPT24

WARNING: Do not fail the password more than 3 times. Feel free to raise your hand. Is better ask for help.

#### Links:

WhatsApp group

### **Google Fotos**