Workshop on Fully Programmable Systems-on-Chip for Scientific Applications

#### VHDL Fo thesis

**ICTP** 1964-2024

Cristian Sisterna

Senior Associate, ICTP-MLAB

Universidad Nacional San Juan- Argentina 🧿

#### Introduction

# Hardware Description Language

High level of abstraction

```

if(reset='1') then

count <= 0;

elsif(rising_edge(clk)) then

count <= count+1;

end if;</pre>

```

Easy to debug

Parameterized designs

Re-uso

IP Cores (free) available

#### HDL Synthesis Sub-Set

### HDL Synthesis Sub-Set

✓ VHDL is used to DESCRIBE the behavior and/or structure of a Digital System

Be careful ! -> you are *describing Hardware*

Concurrent Code -> Executed in Paralell

✓ With HDL it is possible to describe from a simple combinational circuit to a whole i7 processor

# VHDL Describing Digital System

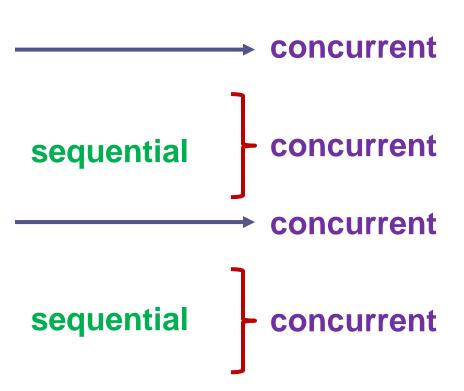

- The operations in real systems are executed concurrently.

- The VHDL language describes real systems as a set of components (statements) that operate concurrently.

- Each of these components is described with concurrent statements.

- The complexity of each component may vary from a simple logic gate to a processor

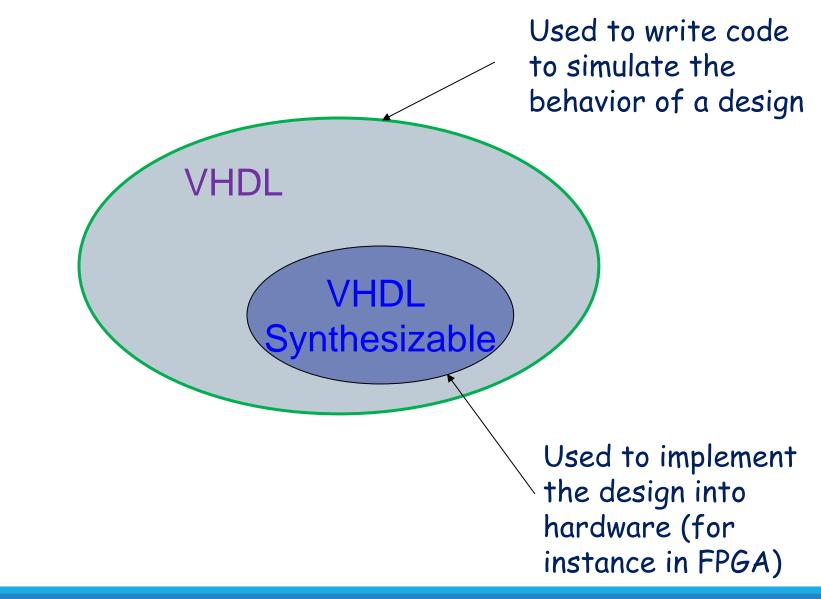

#### Synthesis versus Simulation

Extremely important to understand that VHLD is both, a *Synthesis* language and a *Simulation* language.

- Small subset of the language is '*synthesizable*', meaning that it can be translated into logic gates, flip-flops, and other 'hardware' components

- Every line of VHDL code must have a direct translation into hardware.

- Another subset of the language include many features for '*simulation*' or '*verification*', features that have NO meaning in hardware

### VHDL 'Description' Examples

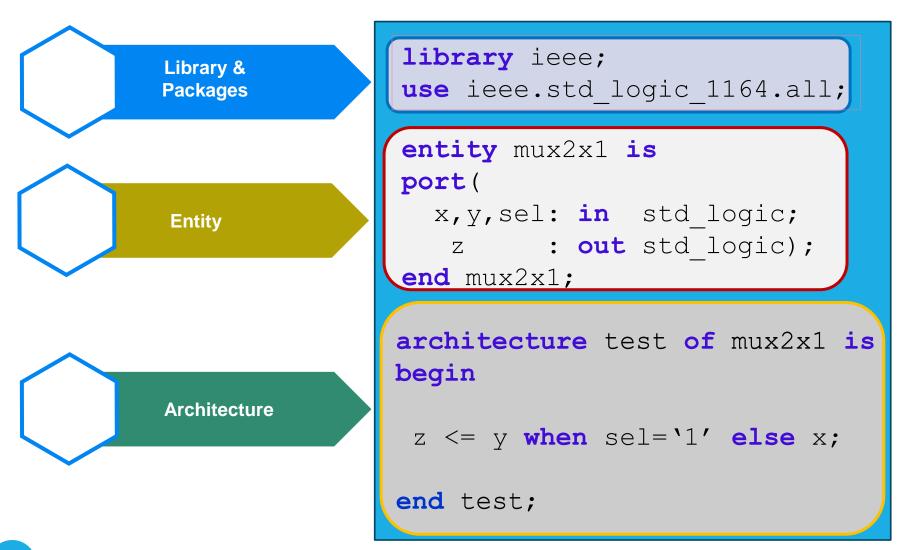

#### z <= y when sel='1' else x;

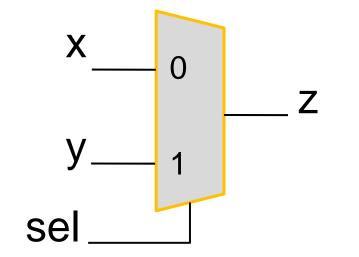

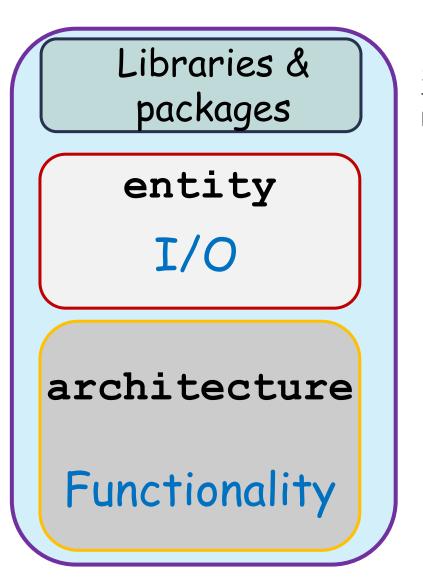

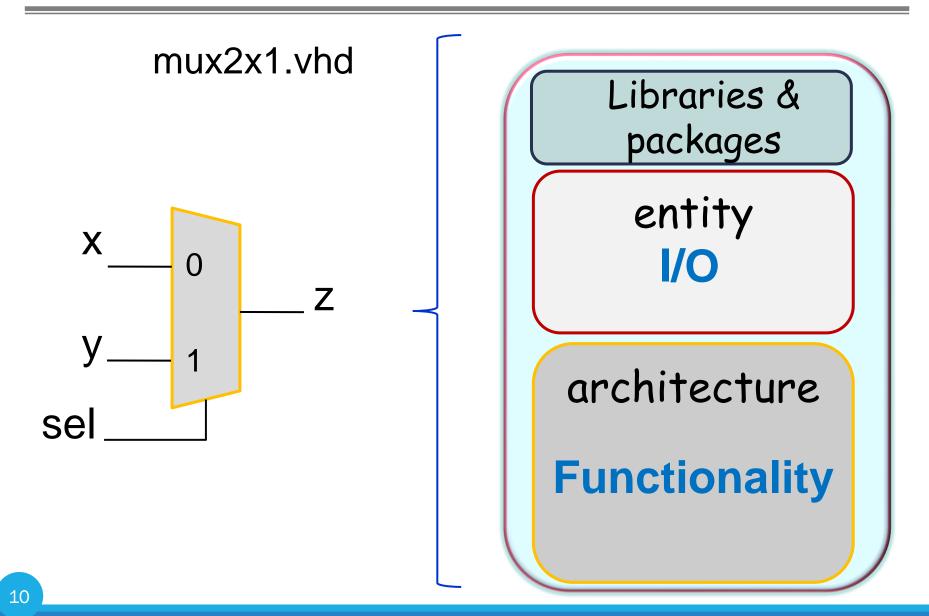

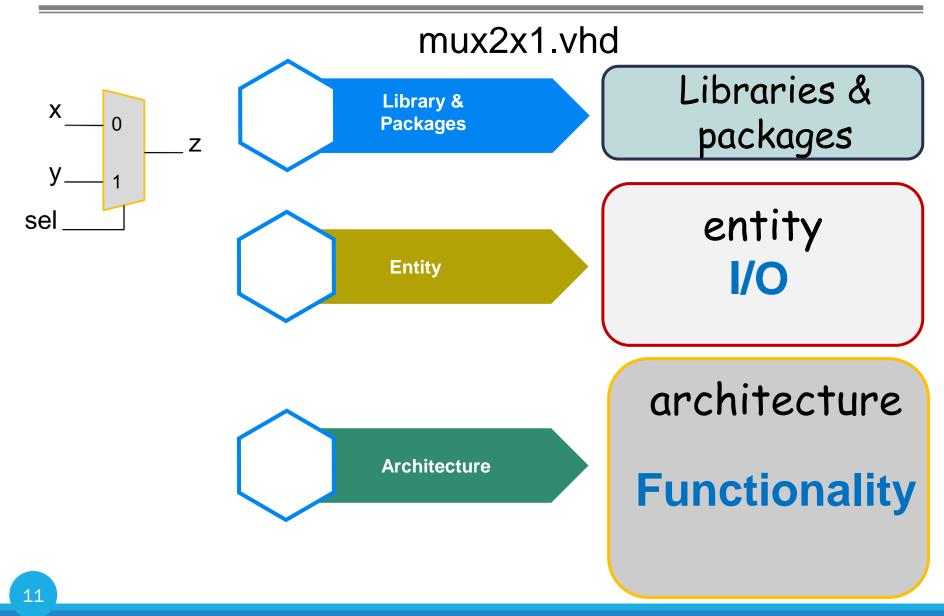

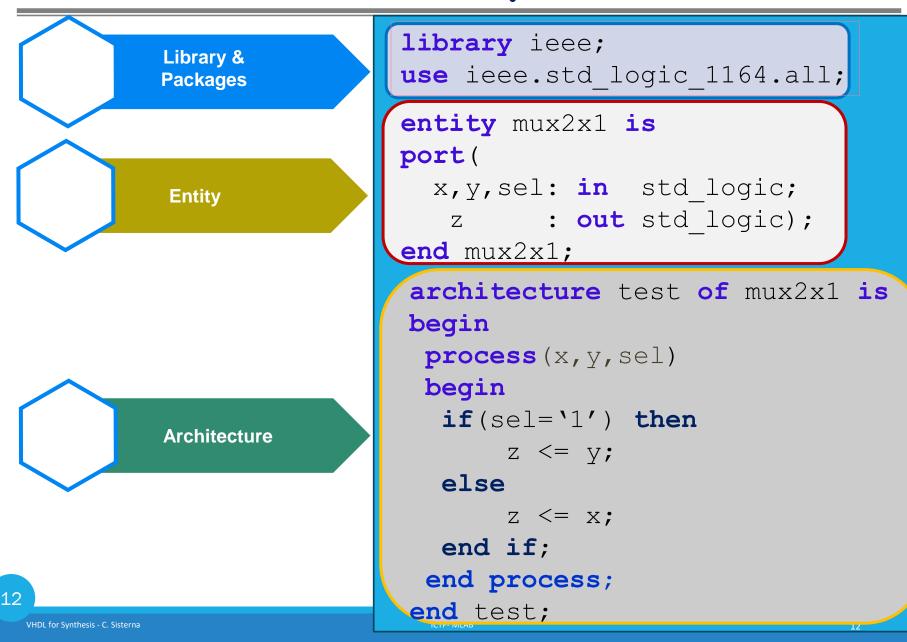

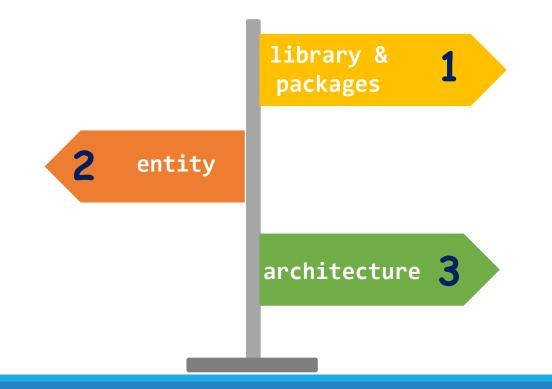

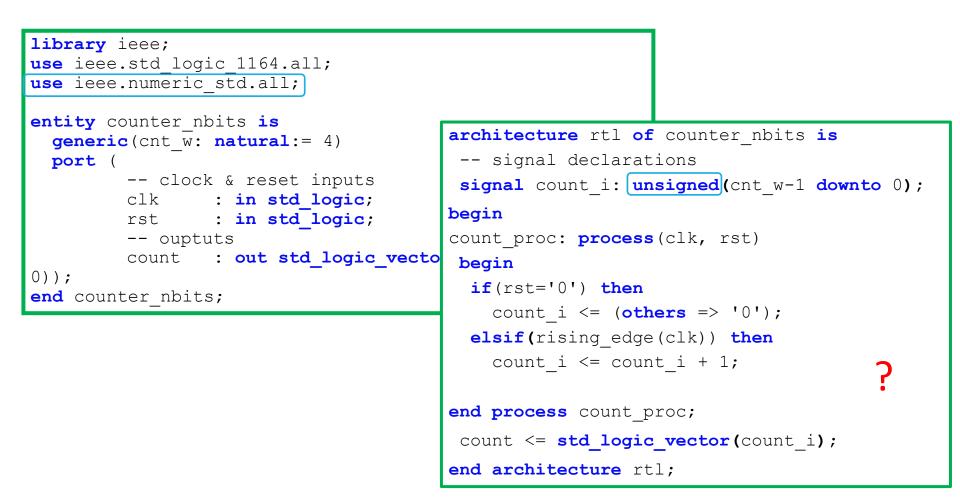

Libraries and packages provides the incorporation of external functions, data types and components to the component to be described

Defines the I/O ports as well as the name of the component. Some times a constant(s) is defined (generic) to write parameterized VHDL code

It's where the hardware **behavior** and/or **structure** is described. It can have from 1 to thousands lines of code… ALL CONCURRENTs !

#### VHDL Code - Is it really Works?

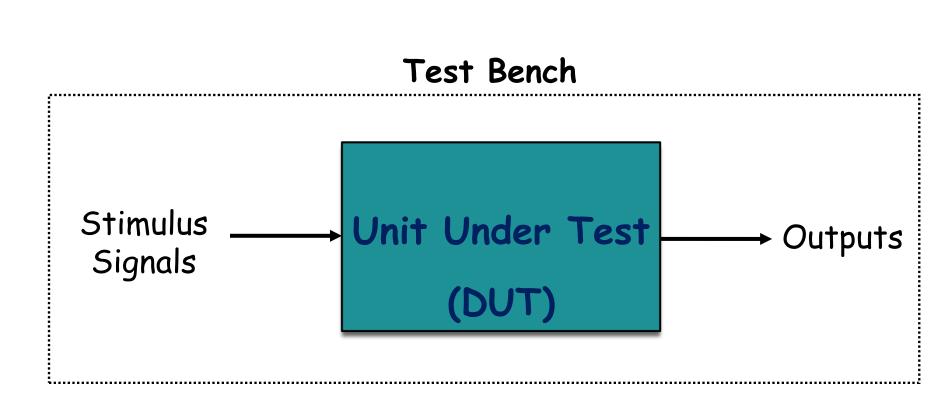

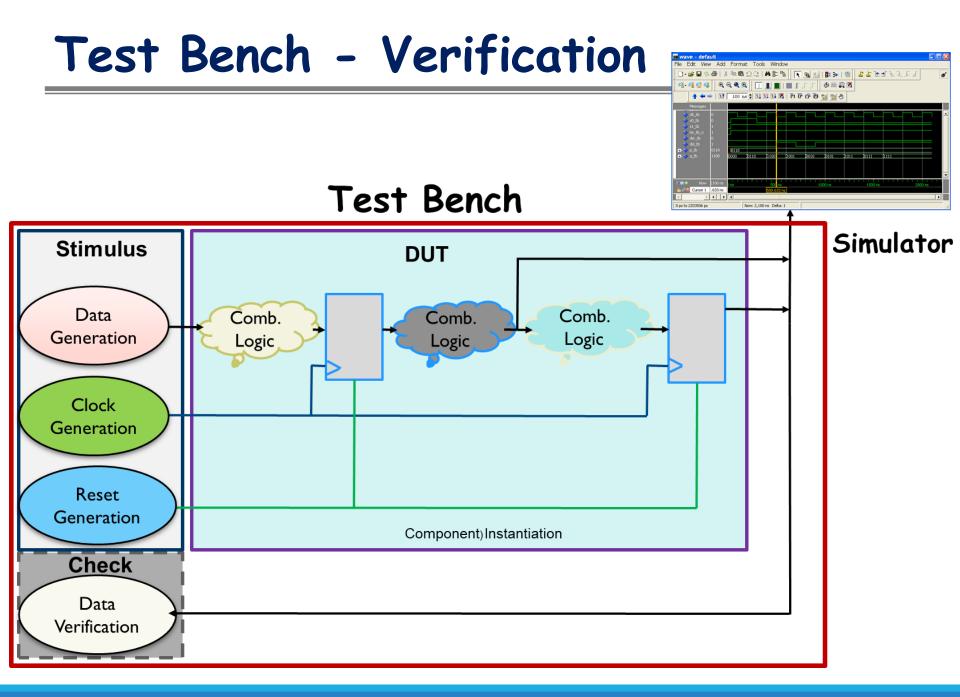

## VHDL - Simulation / Verification

|   | <b>ie wave - defa</b><br>File Edit View                              |         | Forma         | t Tools      | Wi    | ndow   | 1     |      |             |      |         |      |     |             |   |           |

|---|----------------------------------------------------------------------|---------|---------------|--------------|-------|--------|-------|------|-------------|------|---------|------|-----|-------------|---|-----------|

|   | ┃ ◘ + ☞ 🖬 🗇 🚳   ¾ 🛍 ≌ ≌   🛤 🖺 ╚   💽 🖬 🔜   💽 3+   ∰ 🚽 🖢 Ҽ Ҽ Ҽ Ҽ Ҫ Ҫ б |         |               |              |       |        |       |      |             |      | ď       |      |     |             |   |           |

|   | │ -                                                                  |         |               |              |       |        |       |      |             |      |         |      |     |             |   |           |

|   | 100 ns 🛊 💷 🖺 🖺 🛣 [ ?) (?) (?) (?) 👘 🌇 🚳                              |         |               |              |       |        |       |      |             |      |         |      |     |             |   |           |

|   | Messages                                                             |         |               |              |       |        |       |      |             |      |         |      |     |             |   |           |

|   | <pre></pre>                                                          | 0<br>0  |               |              |       |        |       |      |             |      |         |      |     |             | - | $\cap$    |

|   |                                                                      | 1<br>1  |               |              |       |        |       |      |             |      |         |      |     |             |   |           |

| U | ♦ dsr_tb♦ dsl_tb                                                     | 0<br>1  |               |              |       |        |       |      |             |      |         |      |     |             |   | D         |

| Π | <b>⊥</b>                                                             | 0110    | 0110          |              |       |        |       |      |             |      |         |      |     |             |   | $\square$ |

|   | ₽-今 q_tb                                                             | 1100    | 0000          | 0110         | 1100  |        | 1001  | 0010 | 0101        | 1011 | 0111    | 1111 |     |             |   |           |

|   |                                                                      |         |               |              |       |        |       |      |             |      |         |      |     |             | Ī | Γ         |

|   | 🛎 📰 💿 🛛 Now                                                          | 2100 ns | i i i<br>Dins |              | 500   | ns -   | 1 I I | 100  | lııı<br>Ons |      | 1500 ns | 1    | 200 | lıı<br>Dins |   |           |

|   | 👼 🌽 🤤 Cursor 1                                                       |         |               |              |       |        |       |      |             |      |         |      |     |             |   |           |

|   |                                                                      |         |               |              |       |        |       |      |             | Þ    |         |      |     |             |   |           |

|   | 0 ps to 2203506 ps                                                   |         |               | Now: 2,100 r | ns De | lta: 1 |       |      |             |      |         |      |     |             | / |           |

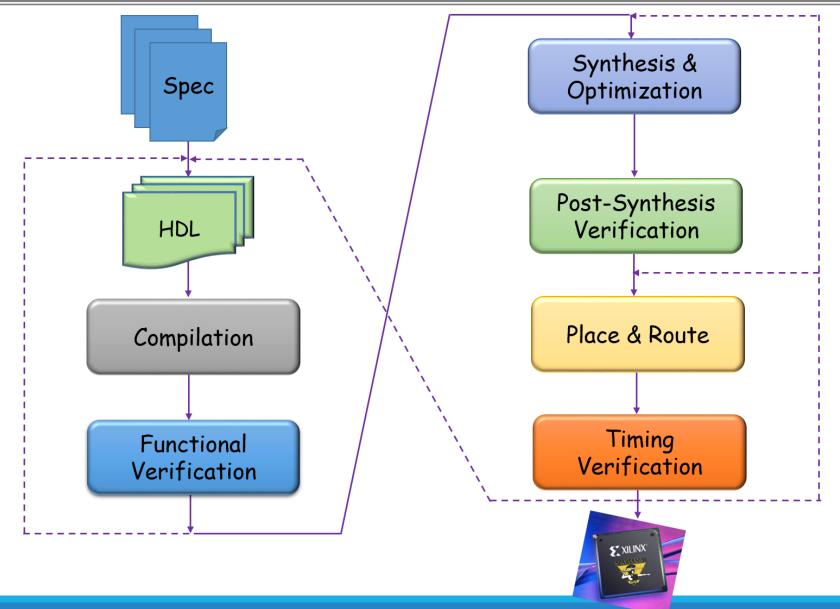

### VHDL - FPGA Design Flow

17

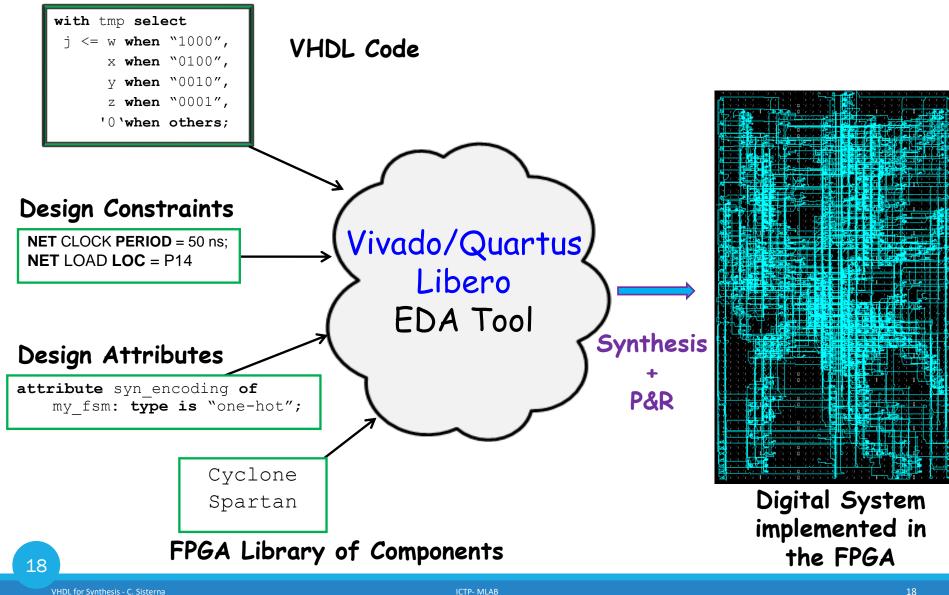

#### VHDL - FPGA: Synthesis + P&R

VHDL for Synthesis - C. Sisterna

#### VHDL Simple Example

#### Simple Example - VHDL

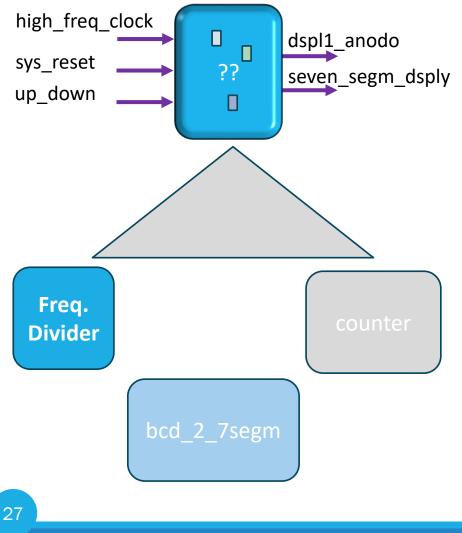

Design a BCD up-down counter. The count should be displayed in a 7-segment display.

The system has a high frequency clock and system reset as inputs.

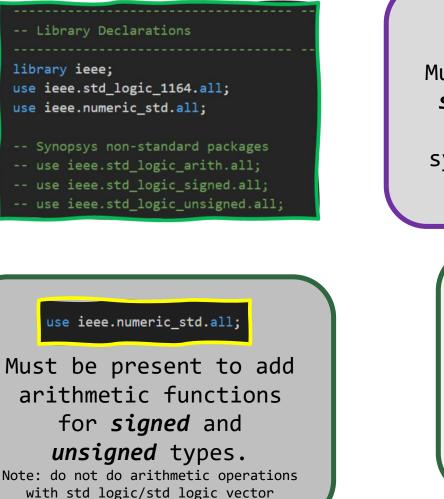

#### Libraries & Packages

library ieee; use ieee.std\_logic\_1164.all;

Must be present to use std\_logic type. That is, for ALL synthesisable designs.

-- Synopsys non-standard packages

-- use ieee.std logic\_arith.all;

-- use ieee.std\_logic\_signed.all;

-- use ieee.std\_logic\_unsigned.all;

DO NOT USE these

packages. There do not belong to the VHDL IEEE standard.

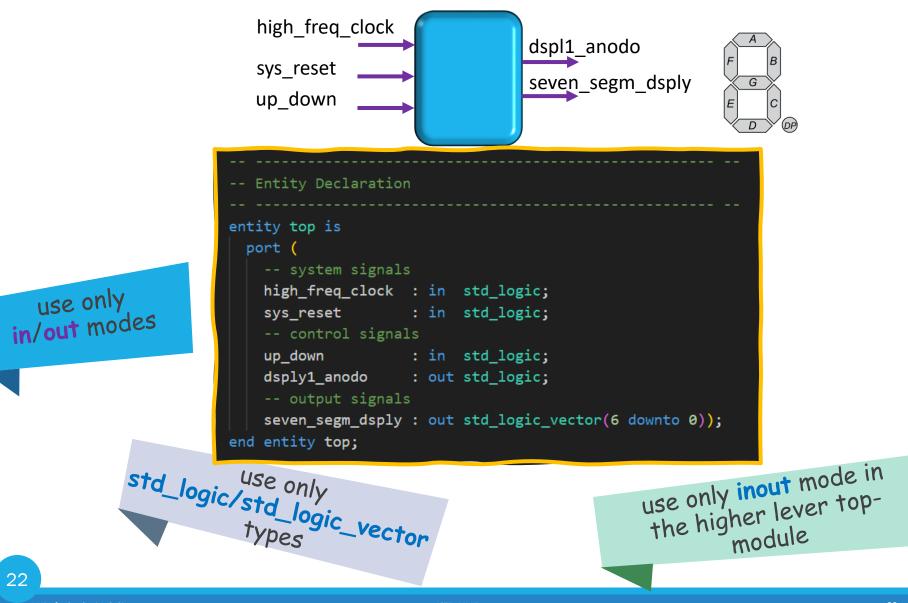

### Signal/Port Declarations in the Entity

ICTP- MLAB

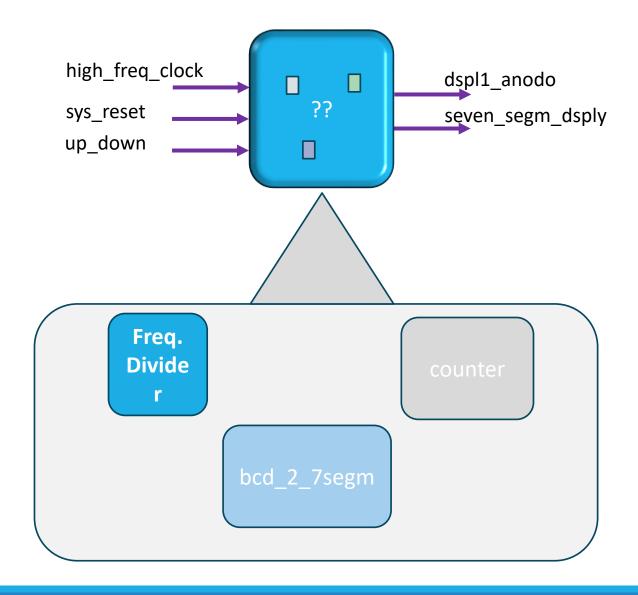

# Architecture (top)

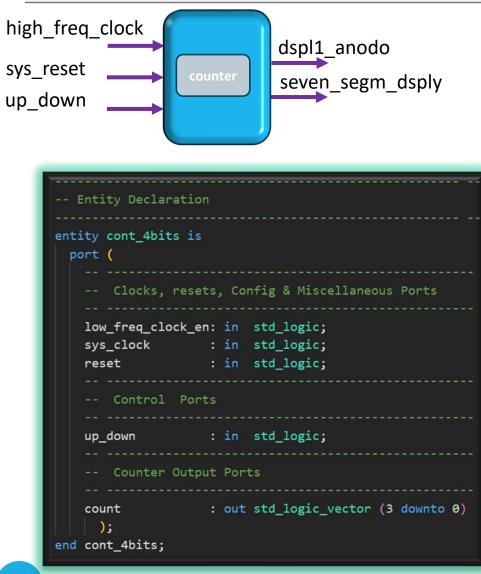

# Counter entity/arch.

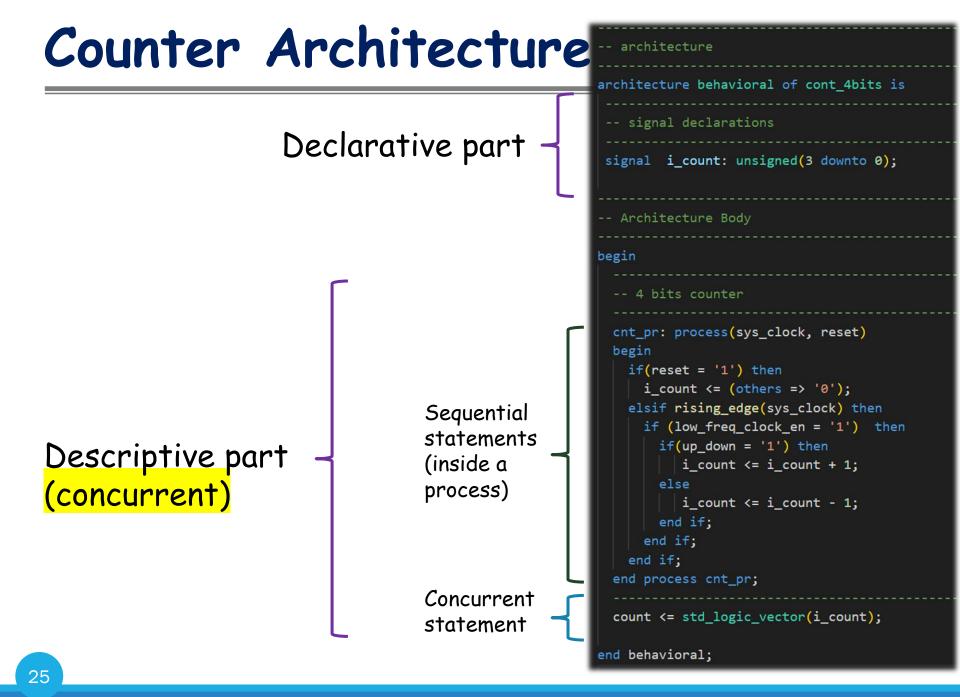

| architecture                                                                                                                                                                                                                                                                                                                                                  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| architecture behavioral of cont_4bits is                                                                                                                                                                                                                                                                                                                      |

| signal declarations                                                                                                                                                                                                                                                                                                                                           |

| <pre>signal i_count: unsigned(3 downto 0);</pre>                                                                                                                                                                                                                                                                                                              |

| Architecture Body                                                                                                                                                                                                                                                                                                                                             |

| begin                                                                                                                                                                                                                                                                                                                                                         |

| 4 bits counter                                                                                                                                                                                                                                                                                                                                                |

| <pre>cnt_pr: process(sys_clock, reset) begin</pre>                                                                                                                                                                                                                                                                                                            |

| <pre>if(reset = '1') then<br/>i_count &lt;= (others =&gt; '0');<br/>elsif rising_edge(sys_clock) then<br/>if (low_freq_clock_en = '1') then<br/>if(up_down = '1') then<br/>  i_count &lt;= i_count + 1;<br/>else<br/>  i_count &lt;= i_count + 1;<br/>else<br/>  i_count &lt;= i_count - 1;<br/>end if;<br/>end if;<br/>end if;<br/>end process cnt_pr;</pre> |

| <pre>count &lt;= std_logic_vector(i_count);</pre>                                                                                                                                                                                                                                                                                                             |

| end behavioral;                                                                                                                                                                                                                                                                                                                                               |

#### Understanding Concurrency

architecture example of entity\_ex is

-- architecture declarative part

#### begin

-- architecture descriptive part

signal assignment concurrent statement; signal assignment concurrent statement; process concurrent statement;

begin

signal assignment sequential statement; signal assignment sequential statement; end process; signal assignment concurrent statement; process concurrent statement; begin signal assignment sequential statement; signal assignment sequential statement; end process; end example;

# Architecture (top)

| architecture                                                                              |

|-------------------------------------------------------------------------------------------|

| architecture structural of top is                                                         |

| internal signal declarations                                                              |

| signal count_i : std_logic_vector(3 downto 0);<br>signal low_freq_clock_en_i : std_logic; |

| architecture body                                                                         |

| begin                                                                                     |

| component instantiations                                                                  |

| ·····                                                                                     |

| bdc-7seg decoder<br>bcd_7seg_1: entity work.bcd_7seg<br>port map (                        |

| <pre>bcd_in =&gt; count_i,</pre>                                                          |

| <pre>segs_out =&gt; seven_segm_dsply, enable =&gt; '1',</pre>                             |

| <pre>dot_out =&gt; open);</pre>                                                           |

| divisor de frecuencia (50MHz-> ~ 1 seg)                                                   |

| <pre>freq_div_1: entity work.freq_div     port map (</pre>                                |

| <pre>sys_rst =&gt; sys_reset,</pre>                                                       |

| <pre>sys_clock_50 =&gt; high_freq_clock,</pre>                                            |

| <pre>low_freq_clock_en =&gt; low_freq_clock_en_i);</pre>                                  |

| contador de 4 bits con reloj de baja frecuencia                                           |

| <pre>cont_4bits_1: entity work.cont_4bits</pre>                                           |

| port map (                                                                                |

| <pre>low_freq_clock_en =&gt; low_freq_clock_en_i,</pre>                                   |

| <pre>sys_clock =&gt; high_freq_clock,</pre>                                               |

| reset => sys_reset,                                                                       |

| <pre>up_down =&gt; up_down,<br/>count =&gt; count_i);</pre>                               |

| count => count_1);                                                                        |

ICTP- MLAB

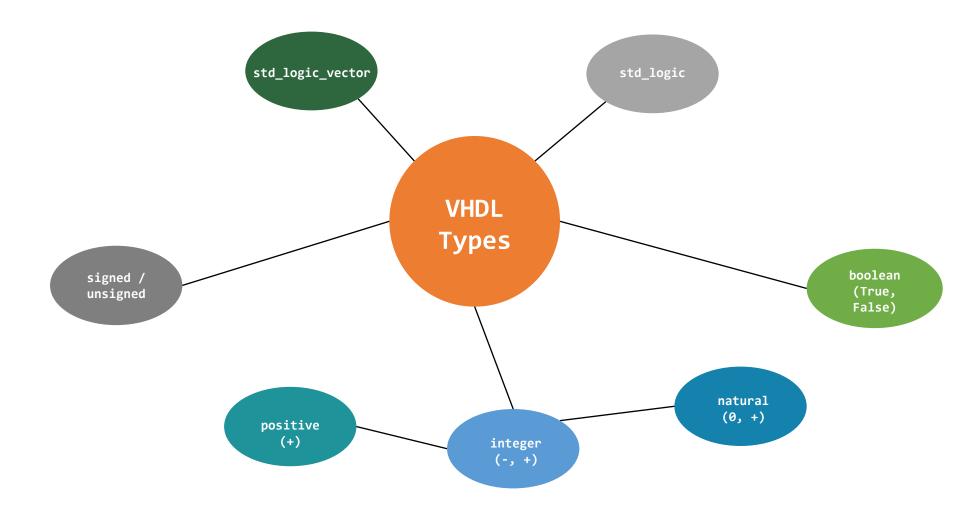

#### **VHDL Data Types**

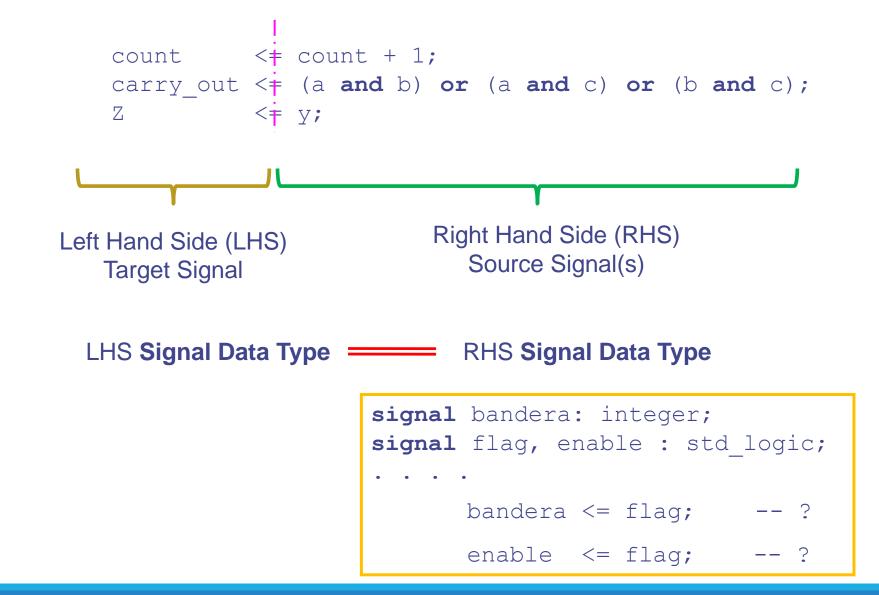

## Signal Assignment - strongly typed

# VHDL Object

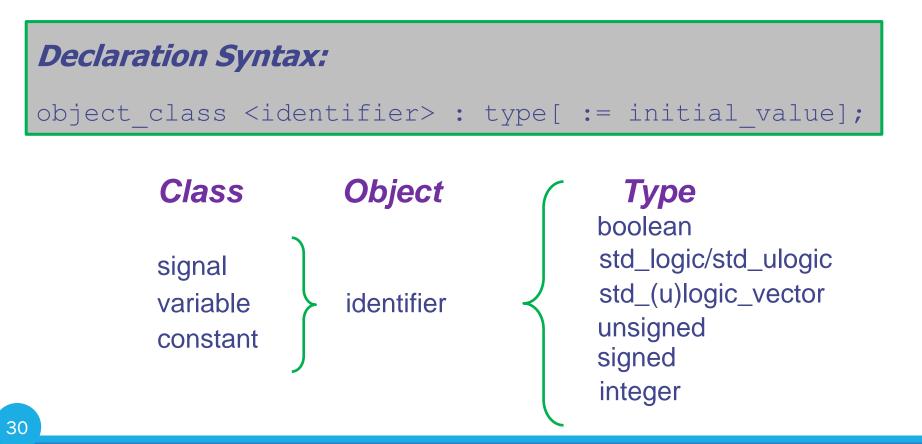

An **object** holds a value of some specified **type** and can be one of the three **classes**: **signal**, **variable**, **constant**

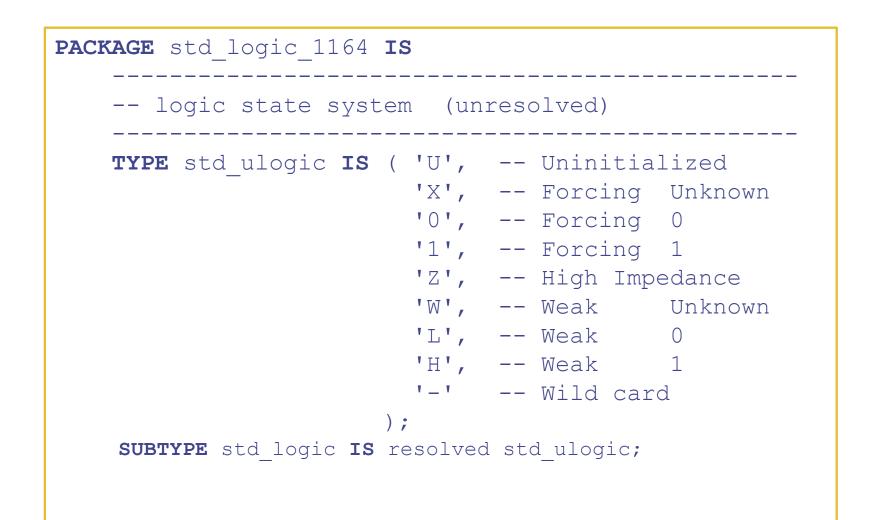

# std\_logic Type

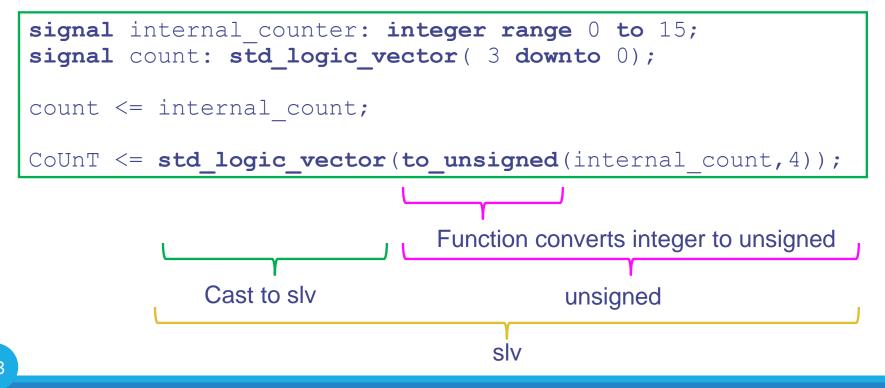

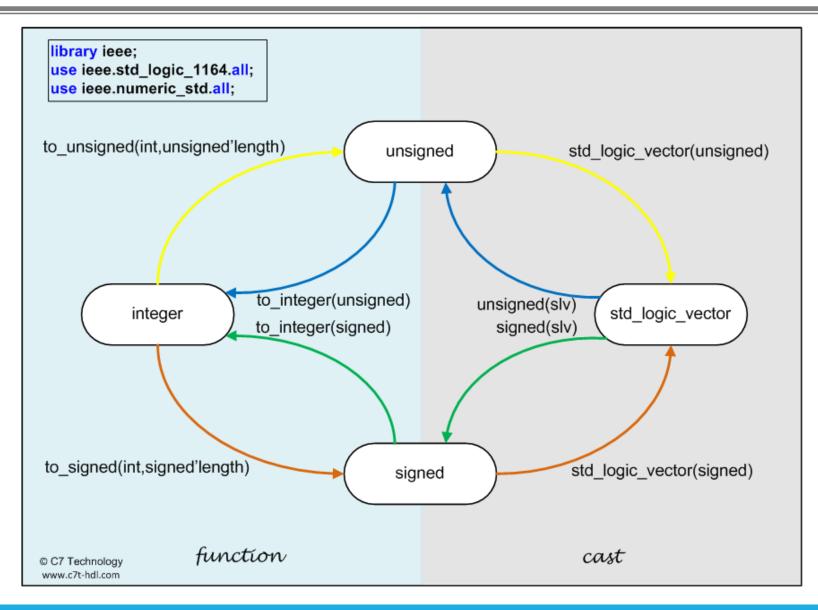

# **Type Conversion - Casting**

VHDL does allow restricted type of <u>CASTING</u>, that is converting values between related types

```

datatype <= type(data_object);</pre>

```

```

signal max_rem: unsigned (7 downto 0);

signal more_t: std_logic_vector( 7 downto 0);

max_rem <= more_t;

max_rem <= unsigned(more_t);</pre>

```

unsigned and std\_logic\_vector are both vectors of the same element type, therefore it's possible a direct conversion by casting. When there is not type relationship a conversion function is used.

# **Type Conversion - Functions**

VHDL does have some built-in functions to convert some different data types (not all the types allow conversions)

datatype <= to\_type(data\_object);</pre>

#### Type Conversion - Cast / Function

#### **VHDL** Operators

| Operator                                                    | Description                                                                          | Data type<br>of a           | Data type<br>of b | Data type<br>of result |  |  |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------|-------------------|------------------------|--|--|

| a ** b                                                      | exponentiation                                                                       | integer                     |                   |                        |  |  |

| abs a                                                       | absolute value                                                                       | integer                     |                   |                        |  |  |

| not a                                                       | negation                                                                             | boolean, bit, bit_vector    |                   |                        |  |  |

| a * b, a / b,<br>a <b>mod</b> b, a <b>rem</b> b             | multiplication, division, modulo, remainder                                          | integer                     |                   |                        |  |  |

| +a, -a                                                      | identity, negation                                                                   | integer                     |                   | integer                |  |  |

| a + b, a - b                                                | addition, subtraction,                                                               | integer                     |                   |                        |  |  |

| a & b                                                       | concatenation                                                                        | 1D array, element           |                   |                        |  |  |

| a sll b, a srl b,<br>a sla b, a sra b,<br>a rol b, a ror b  | shift-left (right) logical,<br>shift-left (right) arithmetic,<br>rotate left (right) | bit_vector                  | integer           | bit_vector             |  |  |

| a = b, a /= b,                                              |                                                                                      | any                         | same as a         | boolean                |  |  |

| a < b, a <= b,<br>a > b, a >= b                             |                                                                                      | scalar or 1D<br>array       | same as a         | boolean                |  |  |

| a and b, a or b,<br>a xor b, a nand b,<br>a nor b, a xnor b |                                                                                      | boolean, bit,<br>bit_vector | same as a         | same as a              |  |  |

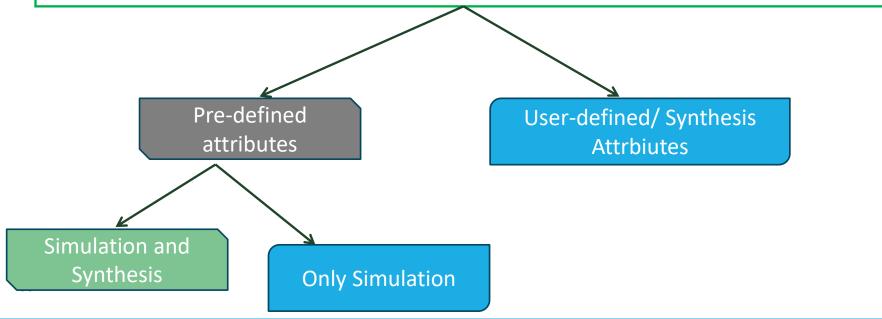

#### **VHDL** Attributes

- It's way of extracting information from a type, from the values of a type or it might define new implicit signals from explicitly declared signals

- It's also a way to allow to assign additional information to objects in your design description (such as data related to synthesis)

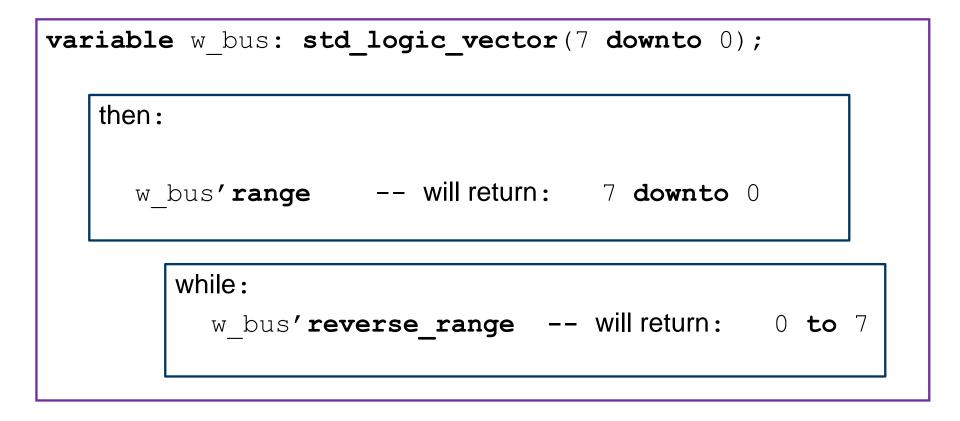

## Array Attributes

Array attributes are used to obtain information on the size, range and indexing of an array

It's good practice to use attributes to refer to the size or range of an array. So, if the size of the array is change, the VHDL statement using attributes will automatically adjust to the change

| Array Attributes – Range Related |                                                  |

|----------------------------------|--------------------------------------------------|

| A'range                          | Returns the range value of a constrained array   |

| A'reverse_range                  | Returns the reverse value of a constrained array |

## Array Attributes

Use of the attributes *range* and *reverse\_range*

### User-defined/Synthesis Attributes

VHDL provides designers/vendors with a way of adding additional information to the system to be synthesized

- Synthesis tools use this features to add timing, placement, pin assignment, hints for resource locations, type of encoding for state machines and several others physical design information

- The bad side of synthesis attributes is that the VHDL code becomes synthesis tools/FPGA dependent, NO TRANSPORTABLE ....

#### User-defined/Synthesis Attributes

Syntax

attribute attr\_name: type;

attribute attr\_name of data\_object: ObjectType is AttributeValue;

Example

attribute syn preserve: boolean;

attribute syn\_preserve of ff\_data: signal is true;

type my fsm state is (reset, load, count, hold);

attribute syn encoding: string;

attribute syn\_encoding of my\_fsm\_state: type is "gray";

### User-defined/Synthesis Attributes

Example:

## **VHDL** Statements

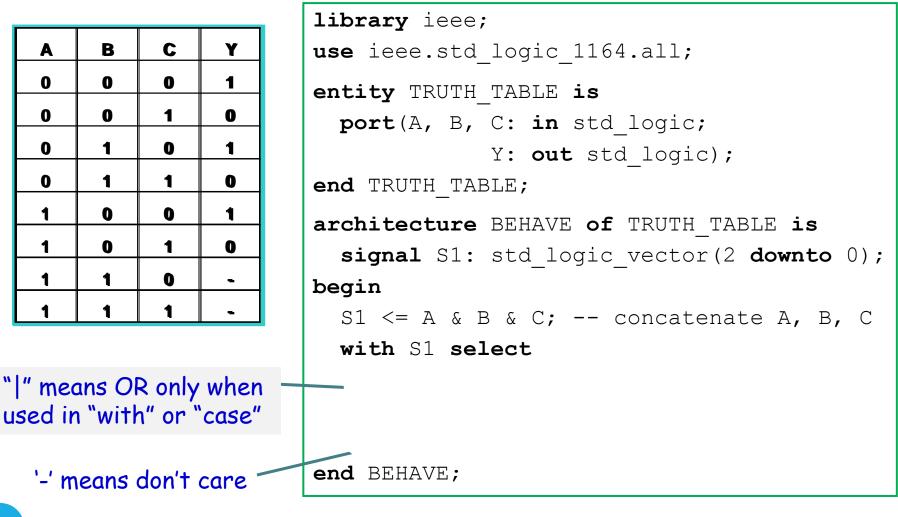

### Selective Signal Assignment Statement

#### Syntax

####

A selective signal assignment describes logic based on mutually exclusive combinations of values of the selection signal

## Selective Signal Assignment Statement

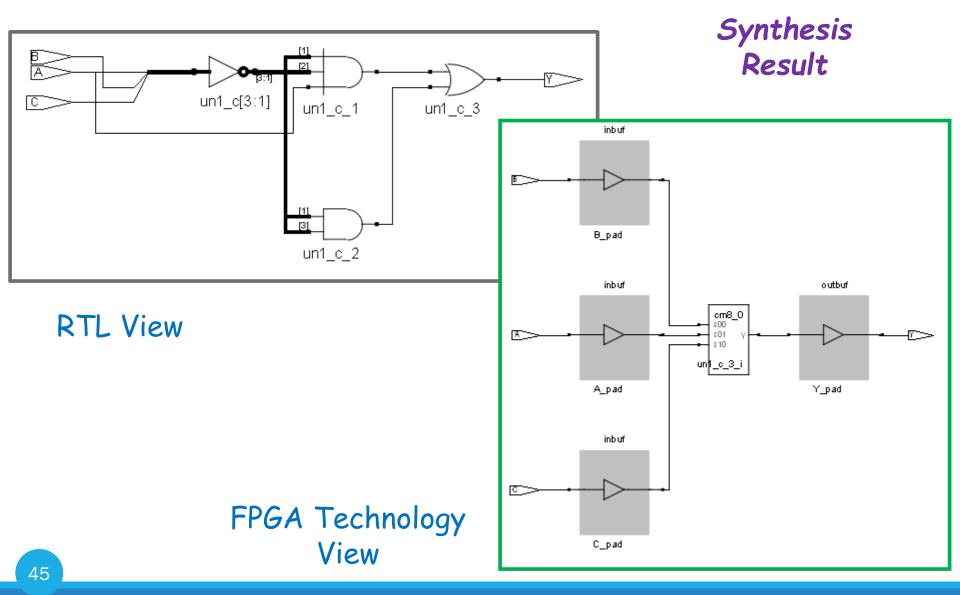

#### **Example: Truth Table**

## Selective Signal Assignment Statement

## **Conditional Signal Assignment**

#### Syntax

```

target_signal <=

<expression> when <boolean_condition> else

<expression> when <boolean_condition> else

....

<expression> when <boolean_condition>[else

<expression>];

```

A conditional signal assignment describes logic based on unrelated boolean\_conditions, the first condition that is true the value of expression is assigned to the target\_signal

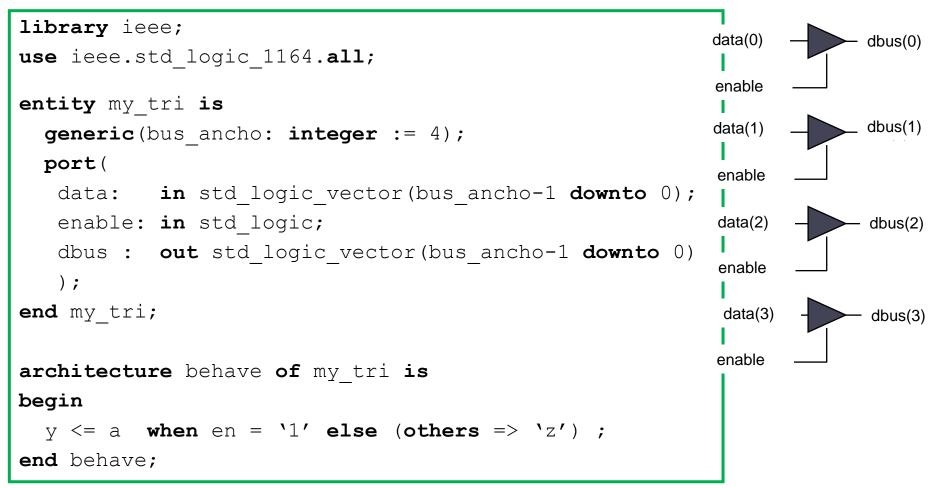

## **Conditional Signal Assignment**

Main usage

dbus <= data when enable = '1' else 'Z';

#### dbus <= data when enable = '1' else (others=>'Z');

## **Conditional Signal Assignment**

#### Example

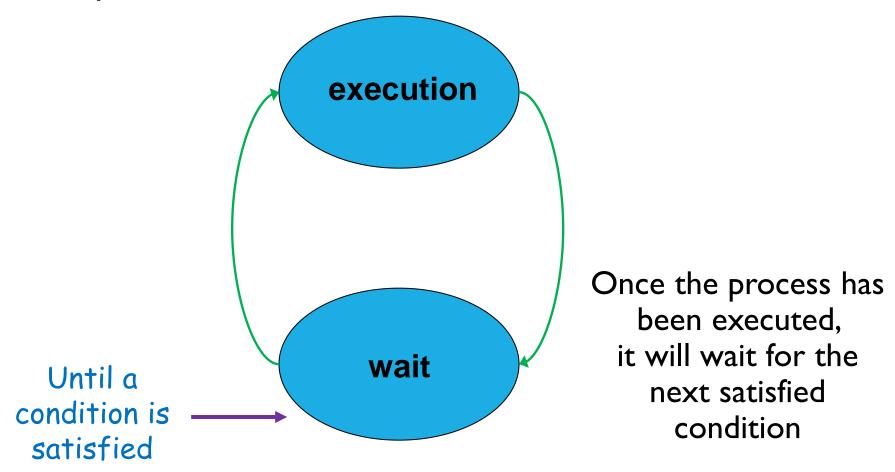

process Statement

A process is a concurrent statement, but it is the primary mode of introducing sequential statements

�A process, with all the sequential

statements, is a simple concurrent

statement.

\*From the traditional programming view, it

is an infinite loop

Multiple processes can be executed in

parallel

### Process Statement

A process has two states: execution and wait

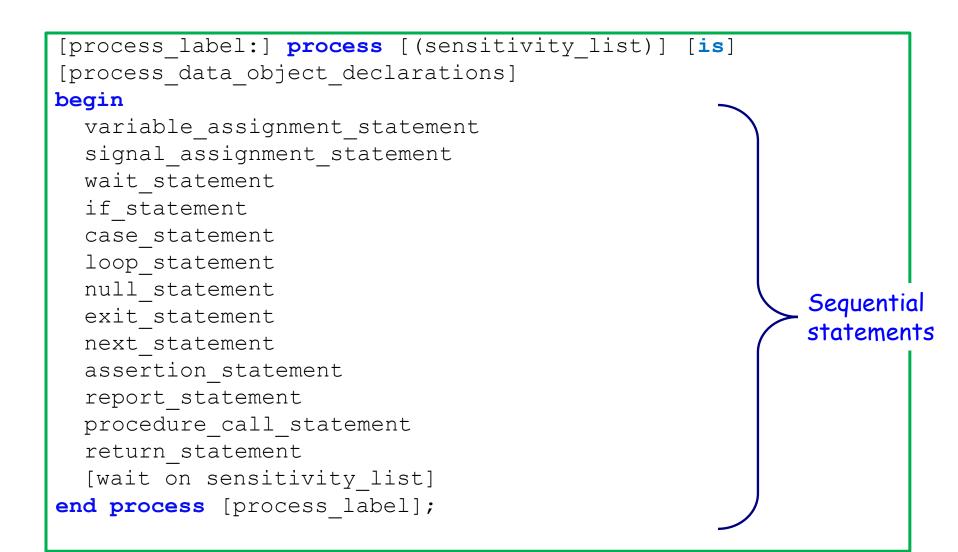

## **Process Statement**

- Processes are composed of sequential statements, but process declarations are concurrent statements.

- The main features of a process are the following:

- It is executed in parallel with other processes;

- It defines a region of the architecture where statements are executed sequentially

- It must contain an explicit sensitivity list or a wait statement

- It allows functional descriptions, similar to the programming languages;

## **Process Statement**

## Parts of the process statement

#### sensitivity\_list

• List of all the signals that are able to trigger the process

- Simulation tools monitor events on these signals

- Any event on any signal in the sensitivity list will cause to execute the process at least once

#### declarations

- Declarative part. Types, functions, procedures and variables can be declared in this part

- Each declaration is local to the process

#### sequential\_statements

All the sequential statements that will be executed each time that the process is activated

## Signal Behaviour in a process

While a process is running ALL the SIGNALS in the system

remain unchanged -> Signals are in effect CONSTANTS during

process execution, EVEN after a signal assignment, the

signal will NOT take a new value

SIGNALS are updated at the end of a process

Signals are a mean of communication between processes -> VHDL can be seen as a network of processes intercommunicating via signals

## Variable Behavior in a process

While a process is running ALL the Variables

in the system are updates **IMMEDIATELY** by a

variable assignment statement

## **Combinational Process**

- In a combinational process all the input signals must be contained in the sensitivity list

- If a signal is omitted from the sensitivity list, the VHDL simulation and the synthesized hardware will behave differently

- All the output signals from the process must be assigned a value each time the process is executed. If this condition is not satisfied, the signal will retain its value (latch !)

## **Combinational Process**

```

a_process: process (a_in, b_in)

begin

c_out <= not(a_in and b_in);

d_out <= not b_in;

end process a process;</pre>

```

```

architecture rtl of com_ex is

begin

ex_c: process (a,b)

begin

z <= a and b;

end process ex_c;

end rtl;</pre>

```

#### if-elsif-end if Statement

Syntax

```

if <boolean_expression> then

<sequential_statement(s)>

[elsif <boolean_expression> then

<sequential_statement(s)>]

. .

[else

<sequential_statement(s)>]

end if;

```

## if Statement - 3 to 8 Decoder

a(2:0) ??

```

entity if decoder example is

b(7:0)

port(

a: in std logic vector(2 downto 0);

z: out std logic vector(7 downto 0);

end entity;

architecture rtl of if decoder example is

begin

if dec ex: process (a)

begin

end process if dec ex;

end rtl;

```

## if Statement

Most common mistakes for describing combinatorial logic

```

entity example3 is

port ( a, b, c: in std logic;

z, y: out std logic);

end example3;

architecture beh of example3 is

begin

process (a, b)

begin

if c='1' then

z <= a;

else

y <= b;

end if;

end process;

end beh;

```

### case Statement

```

[case label:]case <selector expression> is

when <choice 1> =>

<sequential statements> -- branch #1

when <choice 2> =>

<sequential statements> -- branch #2

[when <choice n to/downto choice m > =>

<sequential statements>] -- branch #n

. . . .

[when <choice x | choice y | . . .> =>

<sequential statements>] -- branch #...

[when others =>

<sequential statements>]-- last branch

end case [case label];

```

### case Statement

```

entity mux4 is

port ( sel : in std ulogic vector(1 downto 0);

d0, d1, d2, d3 : in std ulogic;

: out std ulogic );

Z

end entity mux4;

architecture demo of mux4 is

begin

out select : process (sel, d0, d1, d2, d3) is

begin

case sel is

when "00" =>

z <= d0;

when "01" =>

z <= d1;

when "10" =>

z <= d2;

when others =>

z <= d3;

end case;

end process out select;

end architecture demo;

```

62

### case Statement with if Statement

```

mux mem bus :process

(cont_out, I_P0, I_P1, I_A0, I_A1, Q_P0, Q_P1, Q_A0, Q_A1)

begin

mux out <= I P0;</pre>

case (cont out) is

when "00" =>

if(iq bus = '0') then

mux out <= I P0;--I A0;</pre>

else

mux out <= Q P0;--Q A0;</pre>

end if;

when "01" =>

if(iq bus = '0') then

mux out <= I A0;--I P0;</pre>

else

mux out <= Q A0;--Q P0;</pre>

end if;

```

. . . . . .

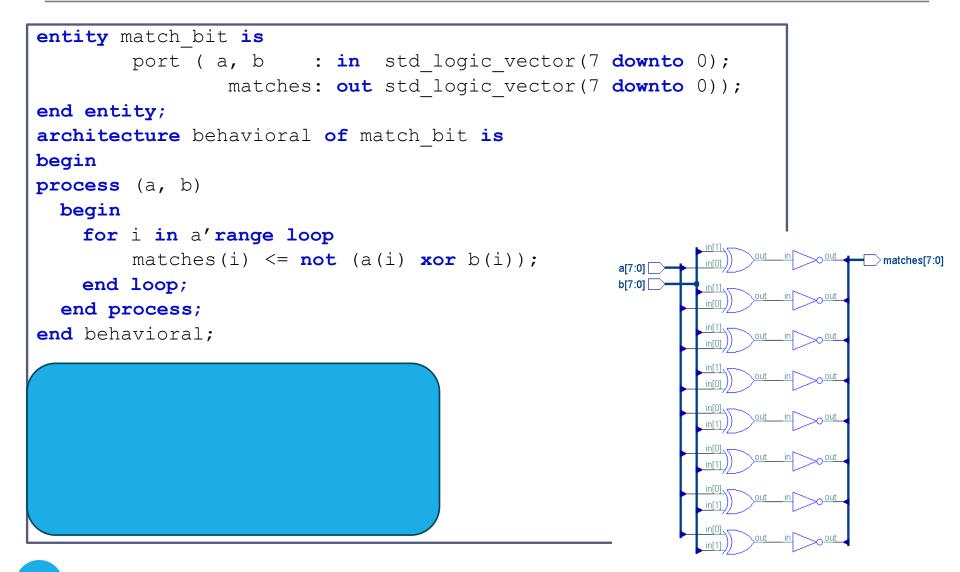

## for loop-end loop Statement

[loop\_label]: for <identifier> in discrete\_range loop

<sequential\_statements>

end loop [loop\_label];

#### <identifier>

- The identifier is called loop parameter, and for each iteration of the loop, it takes on successive values of the discrete range, starting from the left element

- It is not necessary to declare the identifier

- By default the type is integer

- Only exists when the loop is executing

### for-loop Statement

### for-loop Statement

```

library ieee;

use ieee.std logic 1164.all;

use ieee.numeric std.all;

entity count ??? is

port(vec: in std logic vector(15 downto 0);

count: out std logic vector (3 downto 0))

end count ones;

architecture behavior of count ???? is

begin

cnt ones proc: process(vec)

variable result: unsigned(3 downto 0);

begin

result:= (others =>'0');

for i in vec'range loop

if vec(i)='1' then

result := result + 1;

end if:

end loop;

count <= std logic vector(result);</pre>

end process cnt ones proc;

end behavior;

```

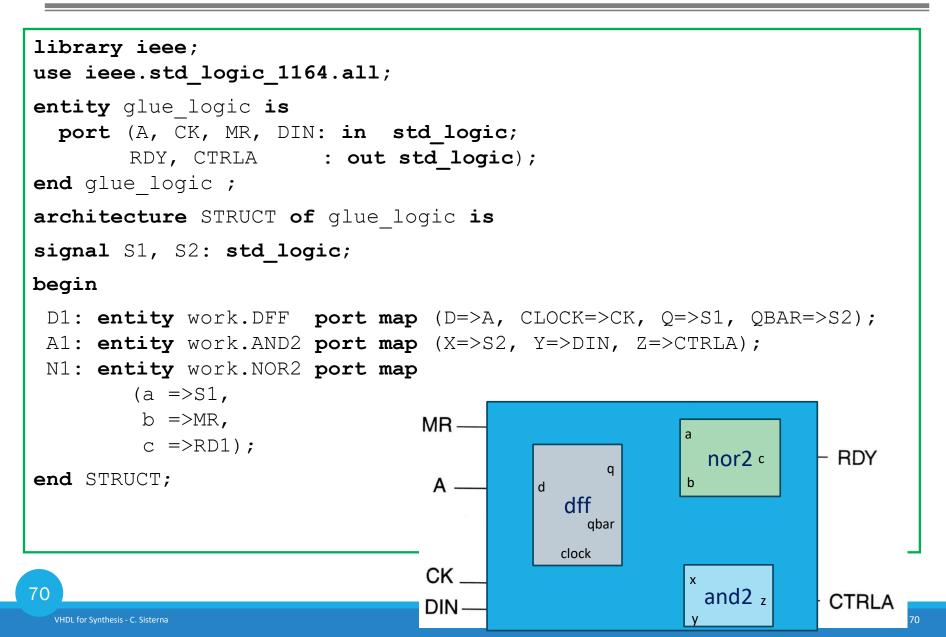

## The Role of Componentes in VHDL

#### Hierarchy in VHDL

4 Divide & Conquer

Each subcomponent can be designed and completely tested

4 Create library of components (technology independent if possible)

4Third-party available components

## **Component Instantiation**

Component instantiation is a concurrent statement that is used to connect a component I/Os to the internal signals or to the I/Os of the higher lever component

component\_label: entity work.component\_name

[generic map (generic assocation list)]

port map (port\_association\_list);

- component\_label it labels the instance by giving a name to the instanced

- generic\_assocation\_list assign new values to the default generic values (given in the entity declaration)

- port\_association\_list associate the signals in the top entity/architecture with the ports of the component. There are two ways of specifying the port map:

- Positional Association / Name Association

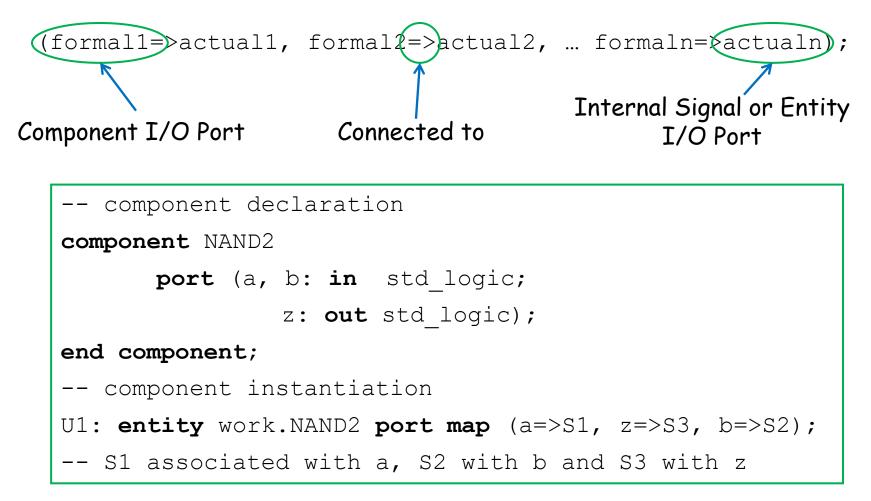

## Association By Name

In named association, an association list is of the form

## **Component Instantiation Example**

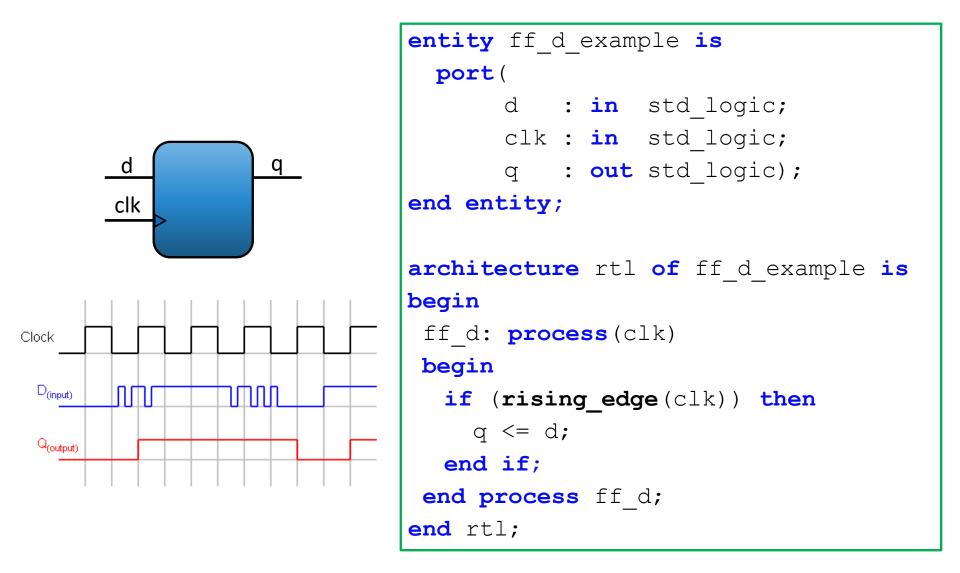

# VHLD for Sequential Logic Design

## D Flip-Flop - VHDL

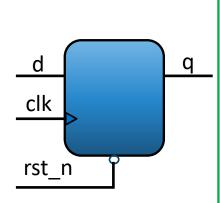

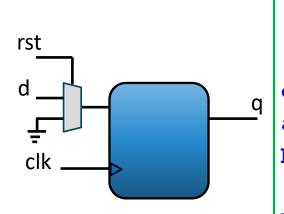

# D-ff with asynchronous reset

entity ff example is port( d, clk, rst n: in std logic; q: out std logic); end entity; architecture rtl of ff example is begin ff d rst: process (clk, rst n) end process ff d rst; end rtl;

# D-ff with synchronous reset

entity ff d srst is port( d, clk, rst: in std logic; q: out std logic); end entity; architecture rtl of ff d srst is begin ff d srst: process (clk) begin

end process ff\_d\_srst;

end rtl;

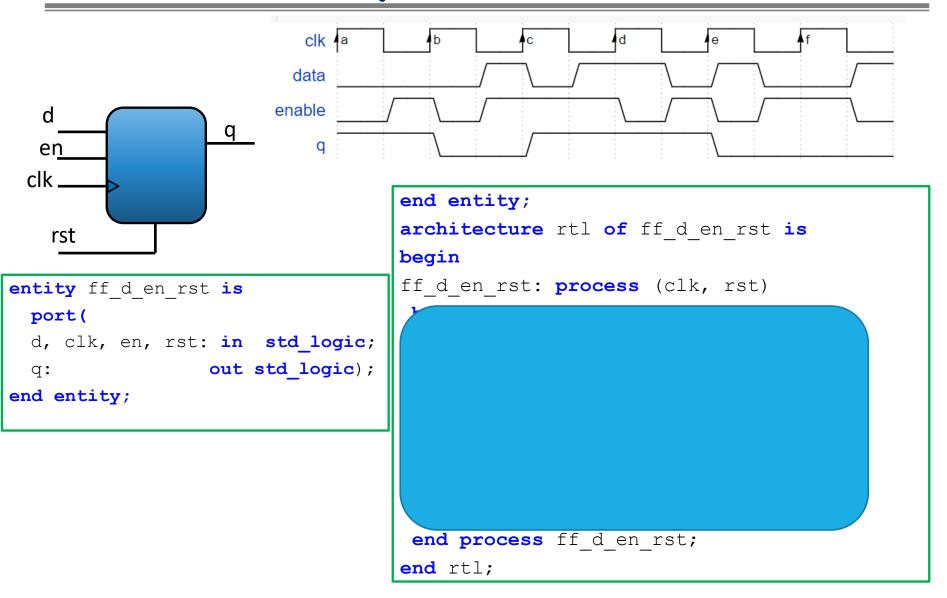

# D-ff with async. reset and enable

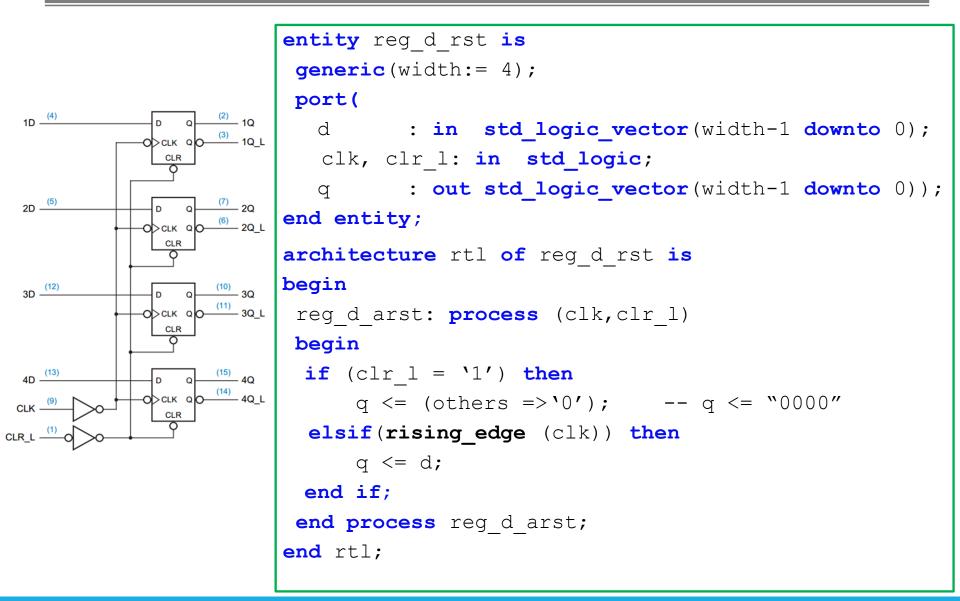

# Registers

### What is the implementation result??

```

library ieee;

use ieee.std logic 1164.all;

entity shift pi po x8 is

port(

clk, clr : in std logic;

serial in : in std logic;

data out : out std logic vector(7 downto 0);

end shift pi po x8;

architecture behav of shift si so x4 is

signal data out temp: std logic vector(3 downto 0);

begin

shift proc: process(clk, clr)

begin

if (clr = '0') then

data out temp <= others(=>'0');

elsif (rising edge(clk)) then

data out temp <= serial in & data out temp(3 downto 1);</pre>

end if;

end process shift proc;

data out <= data out temp;</pre>

end behave;

```

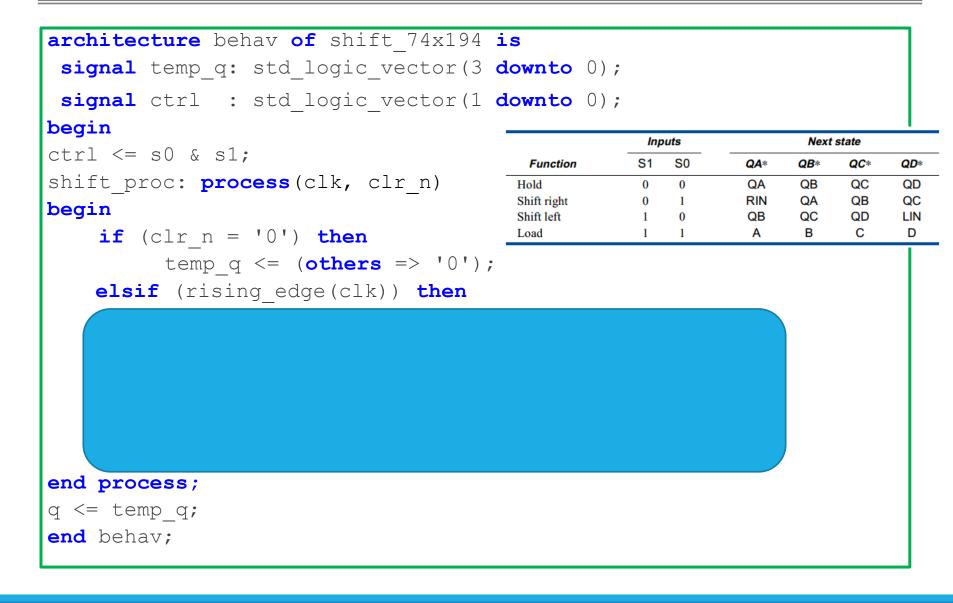

# Shift Register : 74x194

### Counter

# **Up/Down Counter**

```

architecture rtl of counter ud is

-- signal declarations

library ieee;

signal count i: unsigned(cnt w-1 downto 0);

use ieee.std logic 1164.all;

use ieee.numeric std.all;

begin

count proc: process(clk, rst)

entity counter ud is

begin

generic(cnt w: natural:= 4)

if(rst='0') then

port (

count i <= (others => '0');

-- clock & reset inputs

elsif(rising edge(clk)) then

clk : in std logic;

if(up dw = '1') then -- up

rst : in std logic;

count i <= count i + 1;</pre>

-- control input signals

else

-- down

up dw : in std logic;

count i <= count i - 1;</pre>

-- ouptuts

end if:

count : out std logic vector (

end if;

0));

end process count proc;

end counter ud;

count <= std logic vector(count i);</pre>

end architecture rtl;

```

# Up/Down Counter - Integers

```

architecture rtl of counter ud i is

begin

count proc: process(clk, rst)

variable count i: integer range 0 to 255;

begin

if(rst n = '0') then

count i := 0;

elsif(rising edge(clk)) then

if (count i = 255) then

count i := 0;

else

count i := count i + 1;

end if:

end if;

end process count proc;

count <= std logic vector(to unsigned(count i, 8));</pre>

end architecture rtl;

```

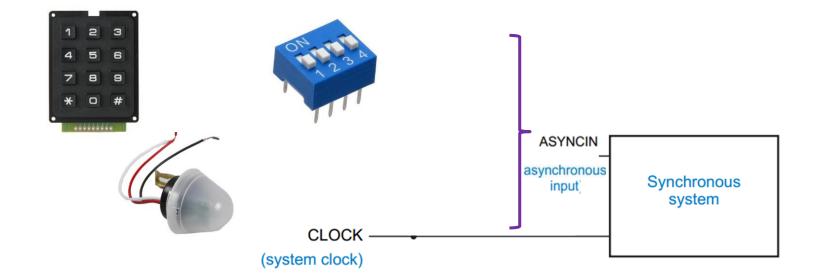

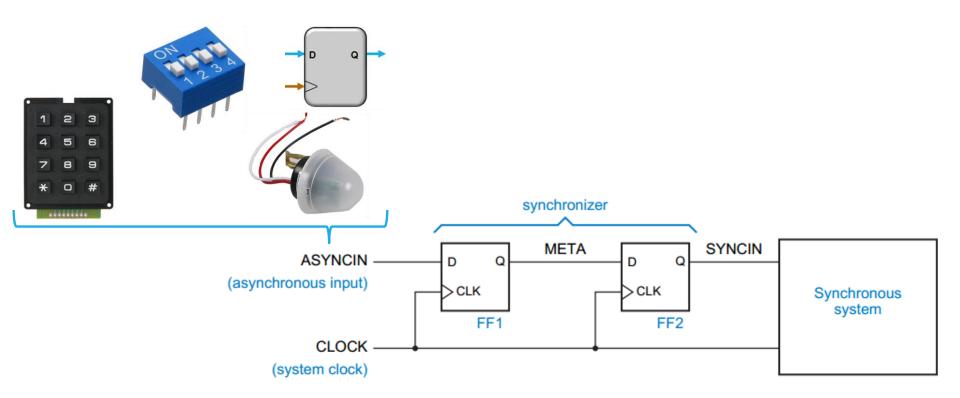

## Asynchronous Inputs

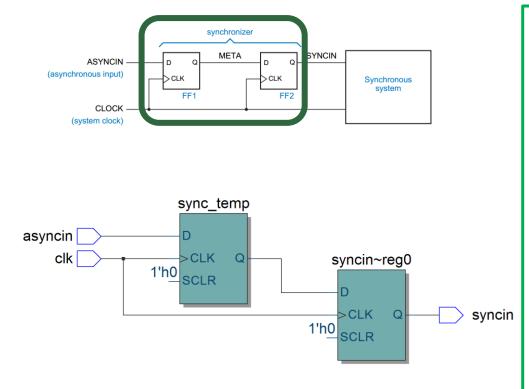

# Synchronizer

# Synchronizer

```

library ieee;

use ieee.std logic 1164.all;

entity synchronizer is

port(

: in std logic;

clk

asyncin : in std logic;

syncin : out std logic);

end synchronizer;

architecture behave of synchronizer is

signal sync temp: std logic;

begin

sync proc: process(clk)

begin

if (rising edge(clk)) then

sync temp <= asyncin;</pre>

syncin <= sync temp;</pre>

end if;

end process;

end behave;

```

# FINITE STATE MACHINES (FSM) DESCRIPTION IN VHDL

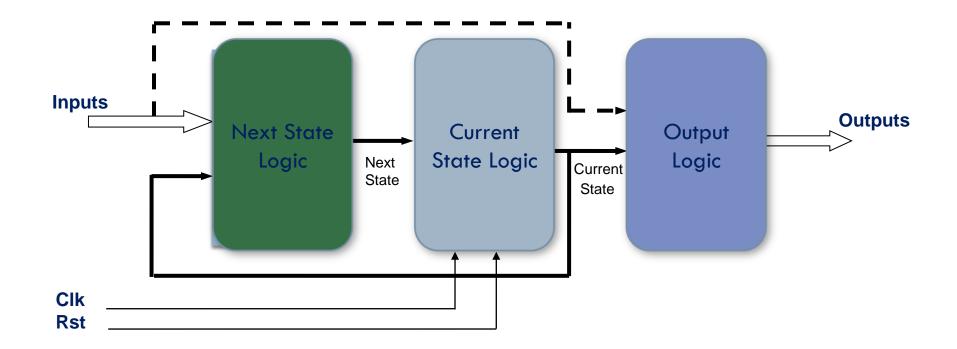

### State Machine General Scheme 1

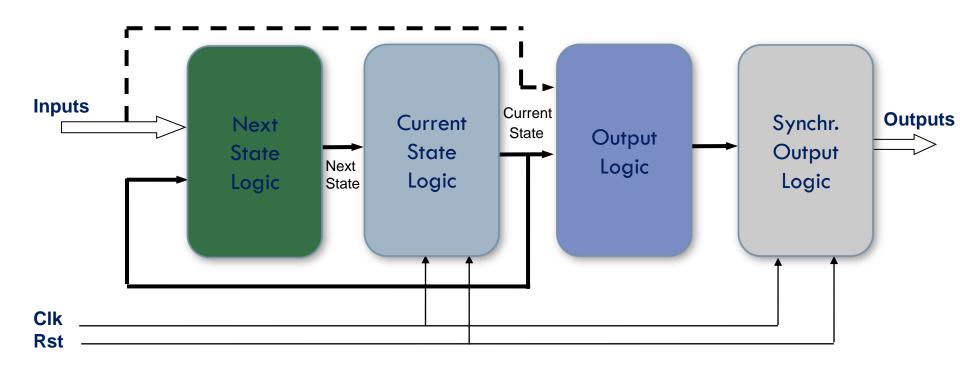

### State Machine General Scheme 2

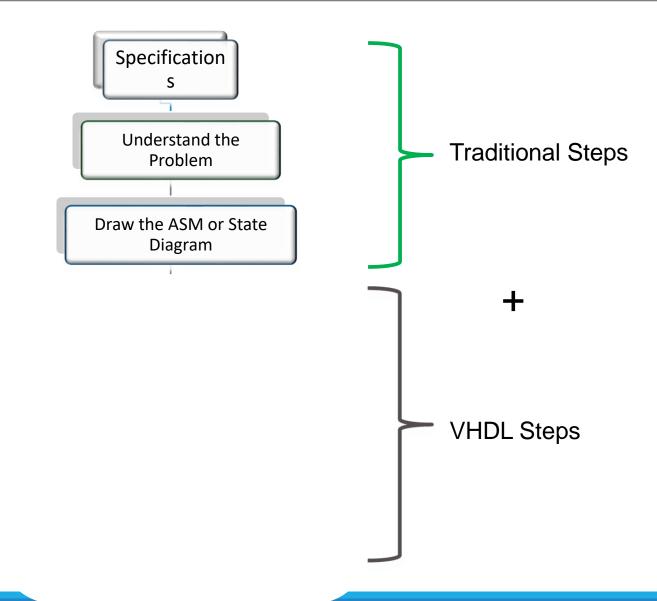

# FSM VHDL General Design Flow

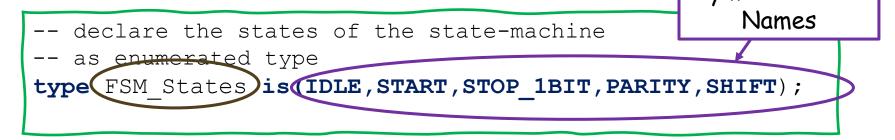

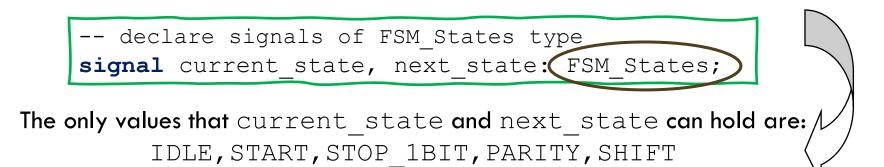

# FSM Enumerated Type Declaration

Declare an enumerated data type with values (names) that symbolize the states of the state machine Symbolic State

Declare the signals for the next state and current state of the state machine as signal of the enumerated data type already defined for the state machine

# FSM Encoding Techniques

### State Assignment

During synthesis each symbolic state name has to be mapped to a unique binary representation

type FSM\_States is(IDLE, START, STOP\_1BIT, PARITY, SHIFT);

signal current\_state, next\_state: FSM\_States;

A good state assignment can *reduce* the circuit *size* and *increase* the *clock rate* (by reducing propagation delays)

The hardware needed for the implementation of the next state logic and the output logic is *directly related* to the state assignment selected

# FSM Encoding Schemes

An FSM with n symbolic states requires at least  $[\log_2 n]$  bits to encode all the possible symbolic values

Commonly used state assignment schemes:

- Binary: assign states according to a binary sequence

- **Gray:** use the Gray code sequence for assigning states

- One-hot: assigns one 'hot' bit for each state

- Almost one-hot: similar to one-hot but add the all zeros code (initial state)

# **FSM Encoding Schemes**

|            | Binary | Gray | One-Hot | Almost One-hot |  |  |  |  |  |  |

|------------|--------|------|---------|----------------|--|--|--|--|--|--|

| idle       | 000    | 000  | 00001   | 0000           |  |  |  |  |  |  |

| start      | 001    | 001  | 00010   | 0001           |  |  |  |  |  |  |

| stop_1 bit | 010    | 011  | 00100   | 0010           |  |  |  |  |  |  |

| parity     | 011    | 010  | 01000   | 0100           |  |  |  |  |  |  |

| shift      | 100    | 110  | 10000   | 1000           |  |  |  |  |  |  |

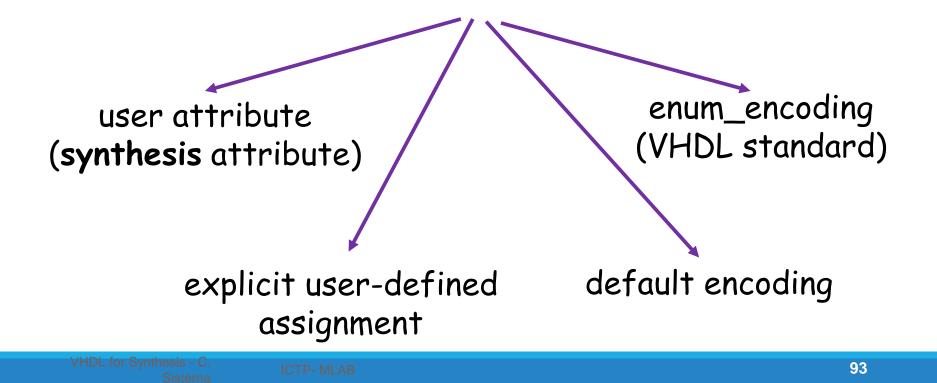

# Encoding Schemes in VHDL

During synthesis each symbolic state name has to be mapped to a unique binary representation

### syn\_encoding-Quartus & Synplify

- syn\_encoding is the synthesis <u>user-attribute</u> of Quartus (Synplify) that specifies encoding for the states modeled by an enumeration type

- To use the syn\_encoding attribute, it must first be declared as string type. Then, assign a value to it, referencing the current state signal.

```

-- declare the (state-machine) enumerated type

type my_fms_states is (IDLE,START,STOP_1BIT,PARITY,SHIFT);

-- declare signals as my_fsm_states type

signal nxt_state, current_state: my_fsm_states;

-- set the style encoding

attribute syn_encoding: string;

attribute syn_encoding of my_fms_states : type is "one-hot";

```

### **Results for Different Encoding Schemes**

Simple, 5 states, state machine

|                                      | One-hot<br>safe | One-hot | Gray   | Gray-Safe | Binary | Johnson |

|--------------------------------------|-----------------|---------|--------|-----------|--------|---------|

| Total<br>combination<br>al functions | 76              | 66      | 66     | 68        | 66     | 68      |

| Dedicated<br>logic<br>registers      | 45              | 45      | 43     | 43        | 43     | 43      |

| Max. frq.                            | 352.24          | 340.95  | 331.02 | 335.01    | 338.34 | 311.72  |

### **Results for Different Encoding Schemes**

19 states, state machine

|                                     | One-hot<br>safe | One-hot | Gray   | Gray-Safe | Binary | Johnson |

|-------------------------------------|-----------------|---------|--------|-----------|--------|---------|

| Total<br>combinational<br>functions | 556             | 523     | 569    | 566       | 561    | 573     |

| Dedicated<br>logic registers        | 215             | 215     | 201    | 201       | 201    | 206     |

| Max. frq.                           | 187.3           | 175.22  | 186.39 | 180.6     | 197.63 | 186.22  |

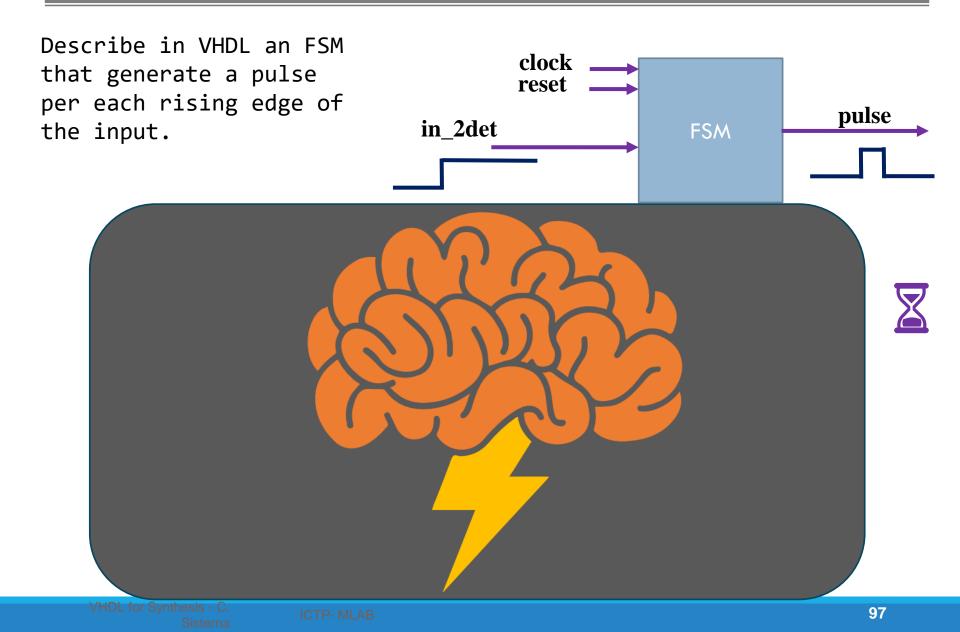

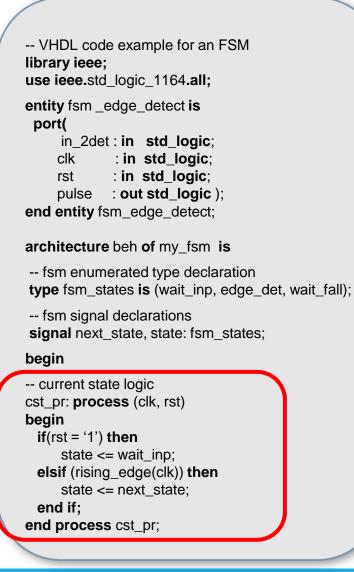

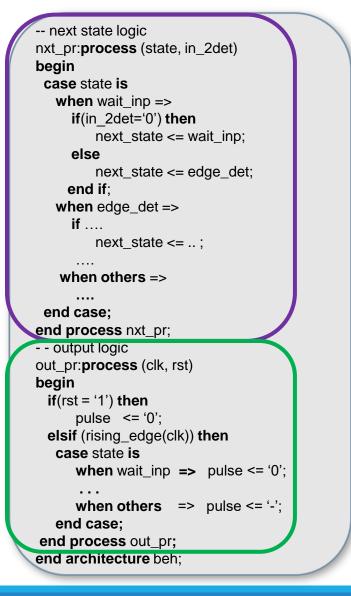

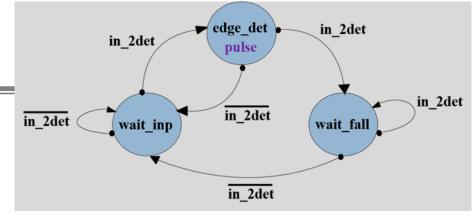

### State Machine VHDL Coding - Example

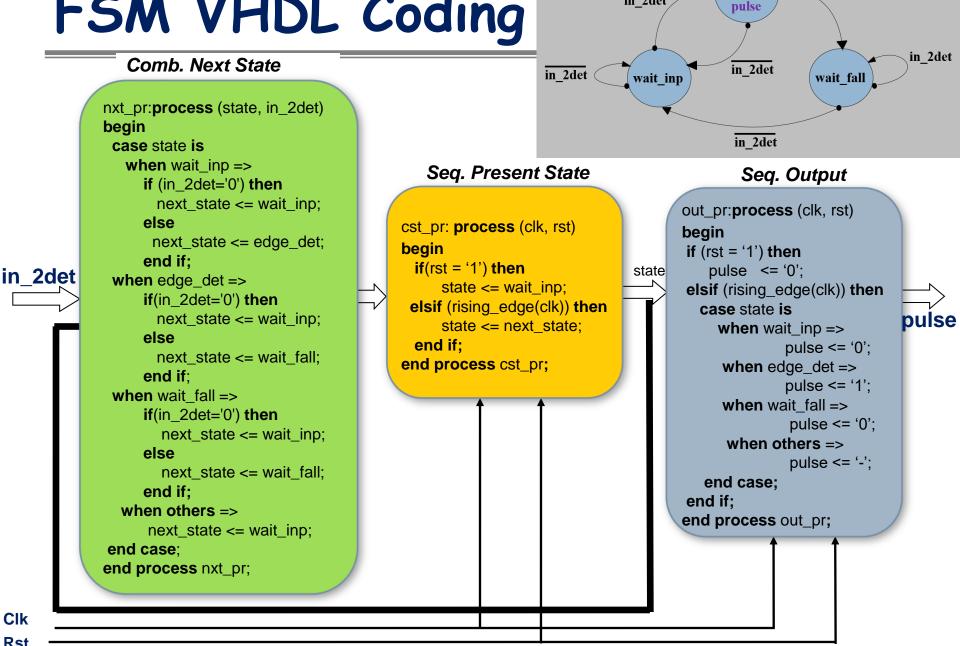

# FSM VHDL Coding

Clk Rst edge det

in 2det

in 2det

### State Machine VHDL Coding (complete)

ICTP- MLAE

## **FSM** Simulation

#### Wave

De el une en lue March and America Liste

| <u>F</u> ile <u>E</u> dit <u>V</u> iew | Add For  | nat <u>T</u> oo | ls Boo <u>k</u> | marks                                 | Windov | w <u>H</u> el | p            |          |          |           |          |           |     |           |                   |          |      |      |      |                   |      |   |

|----------------------------------------|----------|-----------------|-----------------|---------------------------------------|--------|---------------|--------------|----------|----------|-----------|----------|-----------|-----|-----------|-------------------|----------|------|------|------|-------------------|------|---|

| 📰 Wave - Default :                     |          |                 |                 |                                       |        |               |              |          |          |           |          |           |     |           |                   |          |      |      |      |                   | * 4  | x |

| 🛛 🖬 🕶 🖬 🛸                              | 🖨   🐰    | Þa 🛍            | മല              | • • • • • • • • • • • • • • • • • • • | ₩ ≞-   | 8             | 2 M          | Ø 🕅      | තු       | 1 🖛 🛸     | 1        | 00000 p 📥 |     | 1 🕺 💲     |                   | 🎱 🖑      | •    | ⋧ 1  |      | - 🧟               | . 1  |   |

| 🛛 🖏 - 🖏 - 🧊 🐗                          | 🖥 • 🐗 📗  |                 | \$> 11 :        | 🗈   <mark>5</mark> 0                  | L [    | <u></u> L 1   | <b>• →</b> ] | ╘╶┹╴┺    | <b>_</b> | 3• - →€ - | <b>?</b> | Search:   |     |           | ) <i>(</i> 11 at, | <i>6</i> | •    | ର୍ 🔍 | 18 I | <mark>,2</mark> 🛝 |      |   |

| ] 💷 🔳 💵 🕴                              | J.       | J               |                 |                                       |        |               |              |          |          |           |          |           |     |           |                   |          |      |      |      |                   |      |   |

| <b>*</b>                               | Msgs     |                 |                 |                                       |        |               |              |          |          |           |          |           |     |           |                   |          |      |      |      |                   |      |   |

| ── Clk ^ Rst ──                        | 0<br>0   |                 |                 |                                       |        |               |              |          |          |           |          |           |     |           |                   |          |      |      |      |                   |      |   |

|                                        | 1        |                 |                 |                                       |        |               |              |          |          |           |          |           |     |           |                   |          |      |      |      |                   |      |   |

| Output Pulse                           | 1        | L               |                 |                                       |        |               |              |          |          |           |          |           |     |           |                   |          |      |      |      |                   |      |   |

| state                                  | wait_inp | wait in         | 0               |                                       |        |               |              | edge de  | et       | wait inp  |          |           |     | edge de   | t                 | wait f   | fall |      |      |                   |      |   |

| nxt_state                              | edge_det |                 |                 |                                       |        |               | X            | wait_fal |          | (wait_inp | X        |           | let | wait_fall |                   |          |      |      |      |                   |      |   |

|                                        |          |                 |                 |                                       |        |               |              |          |          |           |          |           |     |           |                   |          |      |      |      |                   |      | Z |

|                                        | 0000 ps  | ps              |                 |                                       |        | 20000         | )0 ps        |          |          | 4000      | 00 ps    | 0.2       |     | 6000      | 00 ps             |          |      |      | 8    | 00000             | ) ps |   |

| Cursor 1                               | 5983 ps  |                 |                 |                                       |        |               |              |          |          |           | 4359     | 83 ps     |     |           |                   |          |      |      |      |                   |      |   |

| 0 ps to 840 ns                         |          |                 | Output P        | ulse                                  |        |               |              |          |          |           |          |           |     |           |                   |          |      |      |      |                   |      |   |

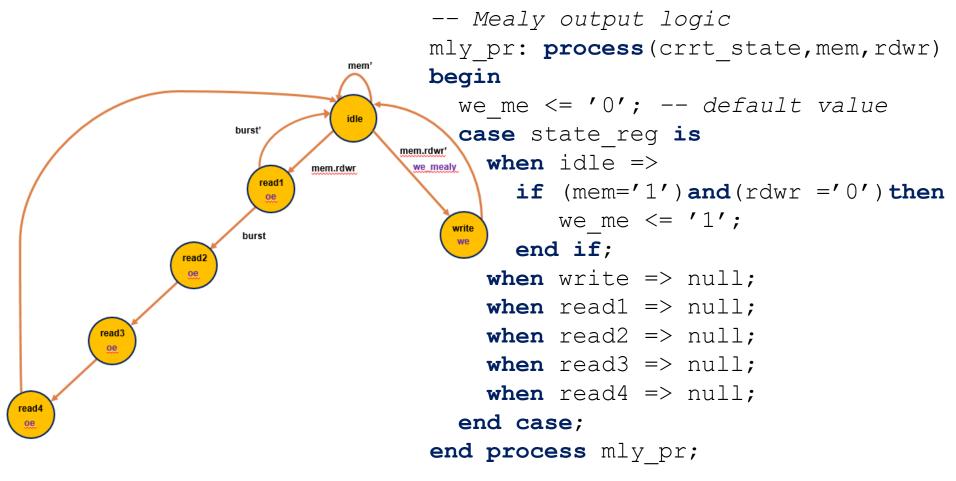

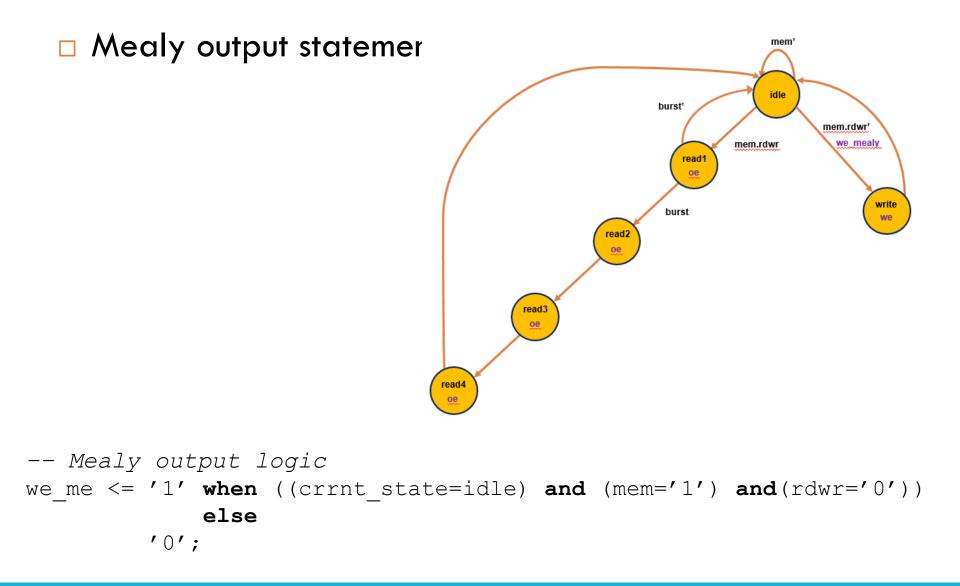

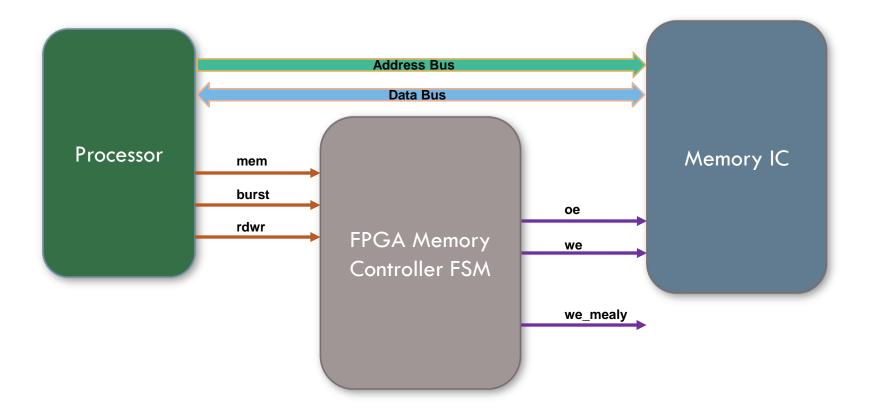

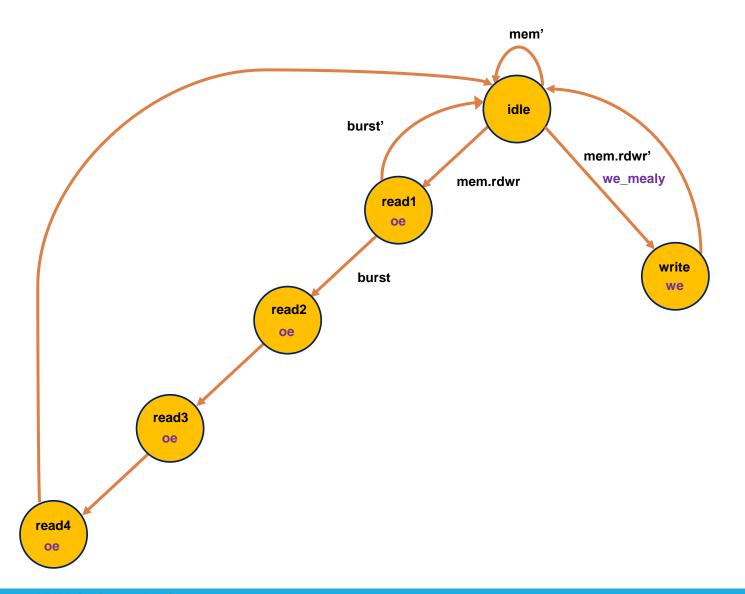

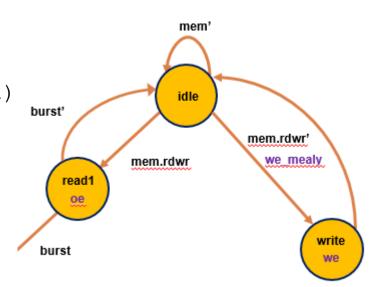

## Another Ex.: Memory Controller FSM

Let's try to obtain an state diagram of a hypothetical memory controller FSM that has the following specifications:

The controller is between a processor and a memory chip, interpreting commands from the processor and then generating a control sequence accordingly. The commands, *mem*, *rw* and **burst**, from the processor constitute the input signals of the FSM. The **mem** signal is asserted to high when a memory access is required. The *rdwr* signal indicates the type of memory access, and its value can be either '1' or '0', for memory read and memory write respectively. The burst signal is for a special mode of a memory read operation. If it is asserted, four consecutive read operations will be performed. The memory chip has two control signals, oe (for output enable) and we (for write enable), which need to be asserted during the memory read and memory write respectively. The two output signals of the FSM, oe and we, are connected to the memory chip's control signals. For comparison purpose, let also add an artificial Mealy output signal, we\_mealy, to the state diagram. Initially, the FSM is in the idle state, waiting for the mem command from the processor. Once *mem* is asserted, the FSM examines the value of *rdwr* and moves to either the *read1* or the *write* state. The input conditions can be formalized to logic expressions, as shown below:

• *mem'* : represents that *n*o memory operation is required (mem='0')

- *mem.rdwr*: represents that a memory *read* operation is required (mem=rdwr='1').

- *mem.rdwr*': represents that a memory *write* operation is required (mem='1'; rdwr='0')

Based on an example from the "RTL Hardware Design Using VHDL" book, By Pong Chu

# Memory Controller FSM

# Memory Controller FSM

```

library ieee ;

use ieee.std logic 1164.all;

entity mem ctrl is

port (

clk, reset : in std logic;

mem, rdwr, burst: in std logic;

oe, we, we mealy: out std logic

);

end mem ctrl ;

architecture mult seg arch of mem ctrl is

type fsm states type is

(idle, read1, read2, read3, read4, write);

signal crrnt state, next state: fsm states type;

begin

```

```

-- current state process

cs_pr: process (clk, reset)

begin

if(reset = '1') then

crrnt_state <= idle ;

elsif(rising_edge(clk))then

crrnt_state <= next_state;

end if;

end process cs_pr;</pre>

```

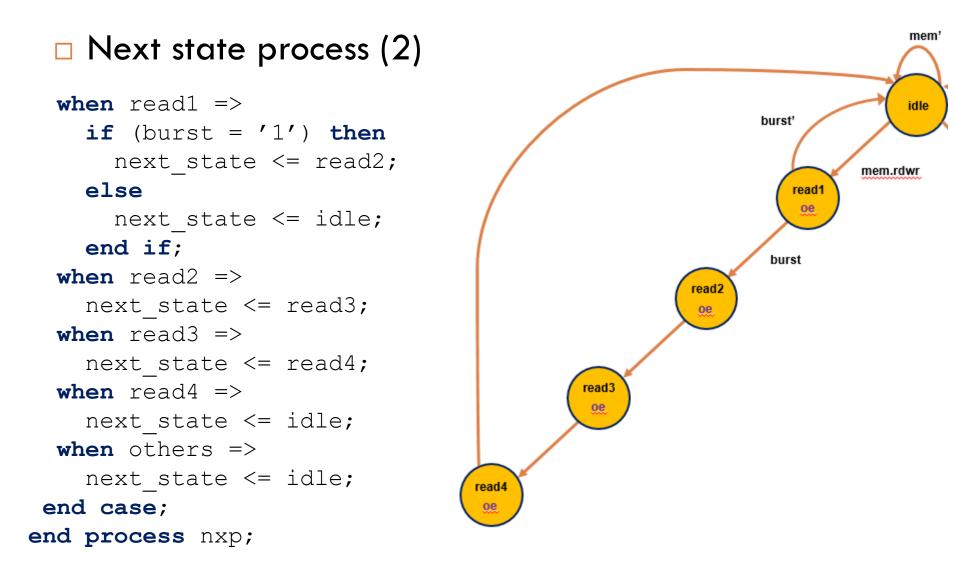

#### Next state process (1)

```

-- next-state logic

nxp:process(crrnt state,mem,rdwr,burst)

begin

case crrnt state is

when idle =>

if mem = '1 ' then

if rdwr = '1' then

next state <= read1;</pre>

else

next state <= write;</pre>

end if;

else

next state <= idle;</pre>

end if;

when write =>

next state <= idle;</pre>

```

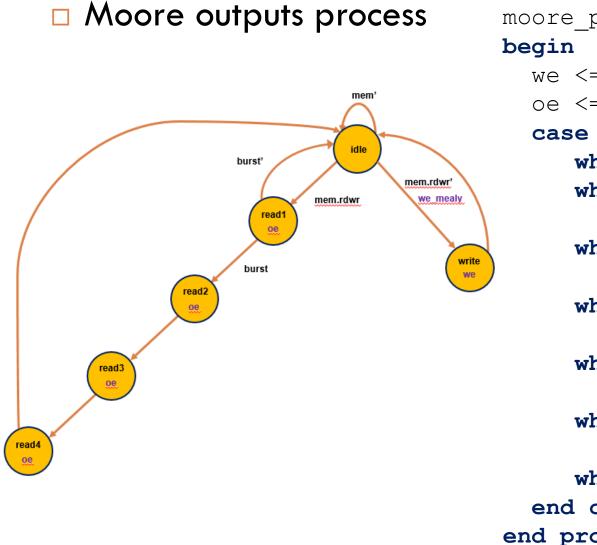

-- Moore output logic moore\_pr: process (crrnt\_state) begin

we  $\leq 10'$ ; -- default value  $oe \leq '0'; -- default value$ case crrnt state is when idle => null; when write => we <= '1'; **when** read1 => oe <= '1'; when read2 => oe <= '1'; **when** read3 => oe <= '1'; **when** read4 => oe <= '1'; when others => null; end case ; end process moore pr;