Workshop on Fully Programmable Systems-on-Chip for Scientific Applications

### Lab 2: The RVI communication block: ComBlock

OATAR UNIVERSITY

#### **Maynor Ballina**

# Introduction

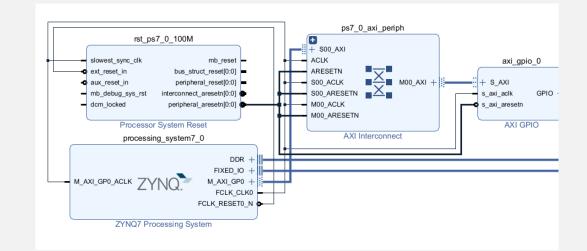

- Vendor specific interconnects (AXI, AVALON, Chiplink).

- What we learned yesterday?

- ✓ AXI interconnect,

- ✓ memory address,

- ✓ data.

- Communication Block (ComBlock ).

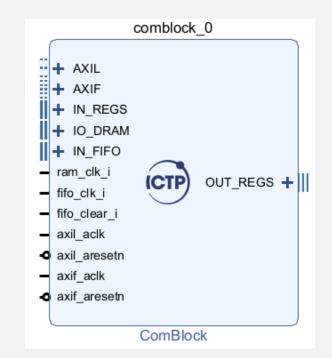

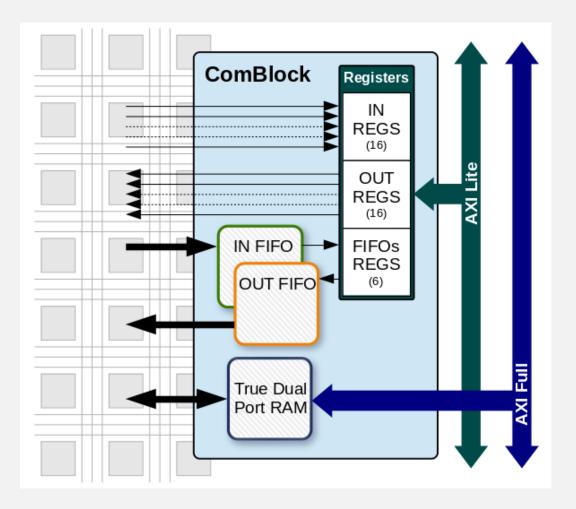

# What is the ComBlock?

A communication block that abstracts you from the AXI protocol.

- Interconnect: AXI Known interfaces (registers, RAM and FIFOs).

- Configurable resources, width, length, etc.

- Simple Clock-Domain-Crossing with FIFOs and TDPRAM.

- C driver for easy complete project integration.

### **Features**

- I/O Registers, I/O FIFOS, and TDPRAM.

- AXI Lite: Registers and FIFOs.

- AXI Full: TDPRAM.

# Registers

- 16 input registers (FPGA to Processor).

- 16 output registers (Processor to FPGA).

- User configurable data width, 1-32 bits.

- Input and output independently enabled.

|                                                                                        | Registers            |                          |

|----------------------------------------------------------------------------------------|----------------------|--------------------------|

| + AXIL<br>- IN_REGS OUT_REGS -                                                         | Input (FPGA to PROC) | Output (PROC to FPGA)    |

| <pre>- &gt; reg0_i[31:0] reg0_o[15:0] &gt; &gt; reg1_i[31:0] reg1_o[15:0] &gt; -</pre> | 🕑 Enable             | 🕑 Enable                 |

| axil_aclk reg2_o[15:0] ▶ =<br>•o axil_aresetn                                          | Data Width 32        | [1 - 32] Data Width 16   |

|                                                                                        | Quantity 2           | [1-16] Quantity 3 (1-16) |

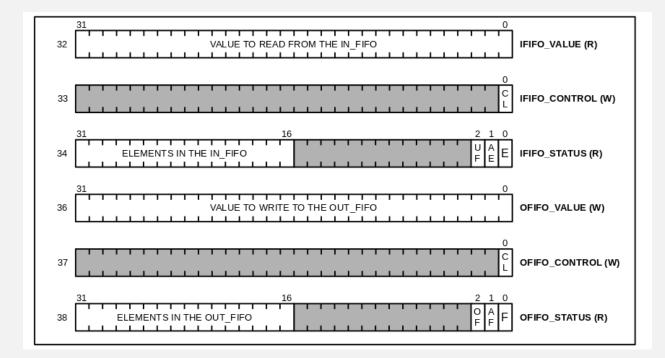

### **FIFOs**

- Input and output FIFOs.

- Customizable width and depth.

- Asynchronous.

- Control registers on the Processor's side.

|   | + AXIL                             |                                      | F | FIFOs                |      |            |                      |       |          |

|---|------------------------------------|--------------------------------------|---|----------------------|------|------------|----------------------|-------|----------|

| Ï | - IN_FIFO                          |                                      |   | Input (FPGA to PROC) |      |            | Output (PROC to FPGA | A)    |          |

|   | ▶ fifo_we_i<br>▶ fifo_data_i(15:0) | OUT_FIFO —<br>fifo_re_i ┥ -          |   | 🕑 Enable             |      |            | 🕑 Enable             |       |          |

|   | <ul> <li>fifo_full_o</li> </ul>    | fifo_data_o[7:0] 🕨 -                 | - |                      |      |            |                      | _     |          |

|   | fifo_afull_o                       | fifo_valid_o 🕨 -<br>fifo_empty_o 🕨 - |   | Data Width           | 16   | 🛞 [1 - 32] | Data Width           | 8 🛞   | [1 - 32] |

|   | fifo_clk_i                         | fifo_aempty_o 🕨                      | - | Depth                | 1024 | $\otimes$  | Depth                | 256 🛞 |          |

|   | fifo_clear_i                       | fifo_underflow_o 🕨 🔸                 |   | Almost Full Offset   | 1    | 8          | Almost Full Offset   | 1 🛞   |          |

|   | axil_aclk<br>axil_aresetn          |                                      |   |                      | -    | -          |                      | -     |          |

|   |                                    |                                      |   | Almost Empty Offset  | 1    | 8          | Almost Empty Offset  | 1 🛞   |          |

### **TDPRAM**

- Bidirectional.

- Clock-domain-crossing.

- Configurable depth, width and address width.

| + AXIF                                                        | True Dual Port RA | AM (FPGA to PROC, I | PROC to FPGA) |

|---------------------------------------------------------------|-------------------|---------------------|---------------|

| - IO_DRAM<br>- > ram_we_i                                     | 🗹 Enable          |                     |               |

| <ul> <li>ram_addr_i[15:0]</li> <li>ram_data_i[7:0]</li> </ul> | Data Width        | 8                   | 3 [1 - 32]    |

| <ul> <li>aram_data_o[7:0]</li> <li>ram_clk_i</li> </ul>       | Address Width     | 16 6                | 3 [1 - 32]    |

| <ul> <li>axif_aclk</li> <li>axif_aresetn</li> </ul>           | Depth             | 0                   | 3             |

### **Processor Interaction**

- Device information in **xparameters.h**.

- Register mappings in **comblock.h**.

- CB\_IREG, CB\_OREG, ...

- Control registers.

### **C** Drives

• Read and write functions **single memory position**:

void **cbWrite**(UINTPTR baseaddr, u32 reg, u32 value) u32 **cbRead**(UINTPTR baseaddr, u32 reg)

Read and write several contiguous memory positions:

void **cbWriteBulk**(UINTPTR baseaddr, int \*buffer, u32 depth) void **cbReadBulk**(int \*buffer, UINTPTR baseaddr, u32 depth)

# Where and how to get it?

• Hosted on GitLab (with continuous updates):

git clone <a href="https://gitlab.com/ictp-mlab/core-comblock.git">https://gitlab.com/ictp-mlab/core-comblock.git</a>

- Completely open source under BSD 3-clause license.

- Rodrigo Melo, collaboration between the Multidisciplinary Laboratory (MLAB) from The Abdus Salam International Centre for Theoretical Physics (ICTP, Italy). (not updated)

Workshop on Fully Programmable Systems-on-Chip for Scientific Applications

### Lab 2: ComBlock and RTL instantiation

IUB Independent University, Bangladesh

#### **Maynor Ballina**

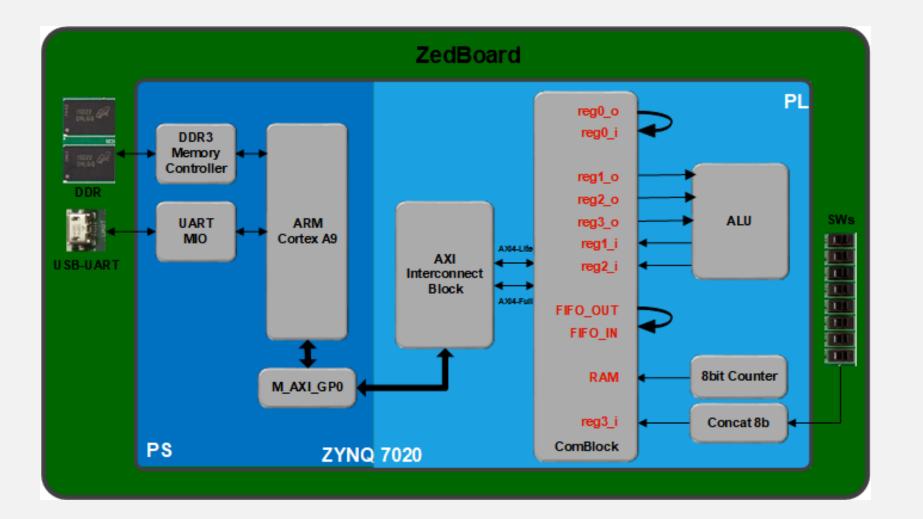

# Labs 2: Objectives

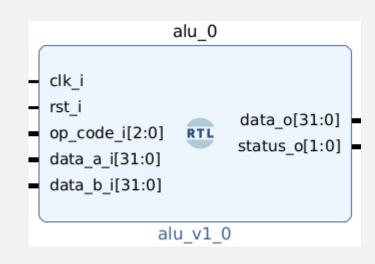

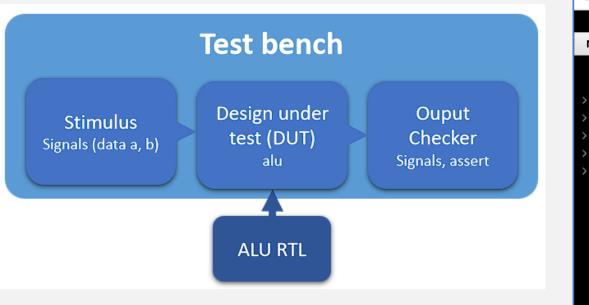

- Simulate a simple ALU and understand the VHDL code.

- Use and configuration of the \*\*ComBlock\*\* IP.

- Understand the data transfer between PL and PS using \*\*ComBlock\*\* IP.

- Instantiate RTL blocks and control them through the \*\*ComBlock\*\* registers.

- Perform unsigned integer arithmetic operations.

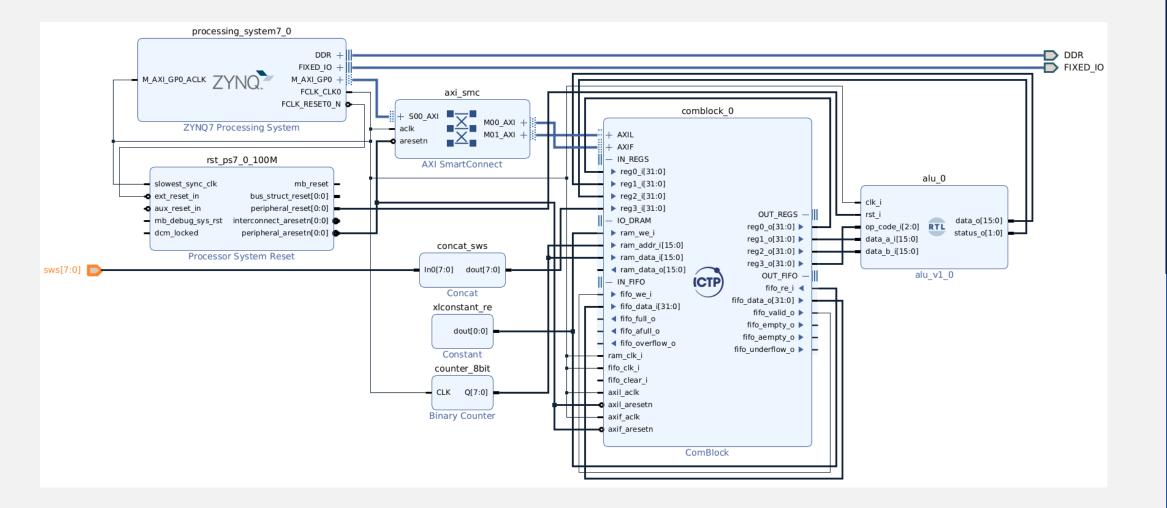

# Labs 2: Design description

# Labs 2: Hardware

RTL block, VHDL coded. Unsigned integer data. Customizable data width.

|                                                                                                                                                                                                                                      | Re-                                                                                                                                                                                                                                       | customize IP    |                                     |              |                                      |                 | ^                          |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------------|--------------|--------------------------------------|-----------------|----------------------------|

| omBlock (2.0)                                                                                                                                                                                                                        |                                                                                                                                                                                                                                           |                 |                                     |              |                                      |                 | 4                          |

| Documentation 🛛 🕞 IP Location                                                                                                                                                                                                        |                                                                                                                                                                                                                                           |                 |                                     |              |                                      |                 |                            |

| Show disabled ports<br>+ AXIL<br>+ AXIF<br>+ AXIF<br>+ IN_REGS<br>+ IO_DRAM<br>+ IN_FIFO<br>- ram_clk_i OUT_REGS +<br>- fifo_clk_i OUT_FIFO +<br>- fifo_clear_i<br>- axil_aclk<br>- axil_aresetn<br>- axif_aresetn<br>- axif_aresetn | Component Name combio<br>Registers<br>Input (FPGA to PROC)<br>© Enable<br>Data Width 32<br>Quantity 4<br>True Dual Port RAM (FPG<br>© Enable<br>Data Width 16<br>Address Width 16<br>Depth 0<br>FIFOS<br>Input (FPGA to PROC)<br>© Enable | A to PROC, PRO  | [1 - 32]<br>[1 - 32]<br>[0 - 671088 | 63]<br>Outpu | 32<br>4<br>t (PROC to FPGA<br>Enable |                 |                            |

|                                                                                                                                                                                                                                      | Data Width<br>Depth<br>Almost Full Offset                                                                                                                                                                                                 | 32<br>1024<br>1 | 8                                   | Dej          | ost Full Offset                      | 32<br>1024<br>1 | [1 - 32] [1 - 16] [1 - 32] |

|                                                                                                                                                                                                                                      | Almost Empty Offset                                                                                                                                                                                                                       | 1               | 8                                   | Alm          | ost Empty Offset                     |                 | , `                        |

# Labs 2: Simulation

| ର୍ 🔛 🔍 ର୍ 🔀      | * +   | H   ±   ±r | + <b>F</b>   Fe |                       | -Γ    | [⊷    |    |           |

|------------------|-------|------------|-----------------|-----------------------|-------|-------|----|-----------|

|                  |       |            |                 | 8 <mark>0.41</mark> 7 | ns    |       |    |           |

| Name             | Value | 0.000 ns   | 50.000 n        | <sup>\$</sup> .       | 100.0 | 10 ns | 15 | ). C      |

| 谒 clk            | 1     |            |                 |                       |       |       |    |           |

| Ъ rst            | 0     |            |                 |                       |       |       |    |           |

| > 😻 op_code[2:0] | 1     |            |                 |                       |       |       |    |           |

| > 😻 data_a[16:0] | 00001 | 00000      |                 | 000                   | 01    | 00002 |    | $\subset$ |

| > 😻 data_b[16:0] | 00000 | $\langle$  |                 |                       |       |       |    |           |

| > 😻 result[16:0] | 00000 |            | 00000           |                       |       | 00001 |    | $\subset$ |

| > 😻 status[1:0]  | 0     |            |                 |                       |       |       |    |           |

| 🐻 stop           | FALSE |            |                 |                       |       |       |    |           |

| \rm WIDTH        | 17    |            |                 |                       |       |       |    |           |

| USAMPL           | 1     |            |                 |                       |       |       |    |           |

|                  |       |            |                 |                       |       |       |    |           |

|                  |       |            |                 |                       |       |       |    |           |

|                  |       |            |                 |                       |       |       |    |           |

|                  |       |            |                 |                       |       |       |    |           |

|                  |       |            |                 |                       |       |       |    |           |

clock.vhd x alu\_tb.vhdl x alu.vhdl x Untitled 1 x

### Labs 2: Final Block Design

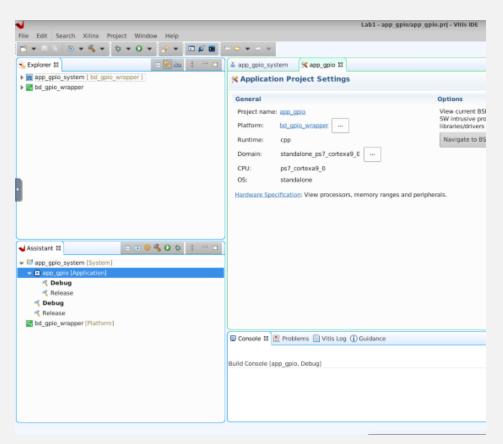

# Labs 2: Software

- C driver, use ComBlock instructions.

- Configuration and data exchange.

- Unsigned integer arithmetic operations.

- Select the operation with an SW.

- Identify and print status flag.

### Labs 2: Results

- PL Hardware

- PS program

- Comblock Communication

- data transfer

Optional:

Challenge

| 10   | GTKTerm - /dev/ttyACM0 115200-8-N-1              | -    | ` _ |    | × |

|------|--------------------------------------------------|------|-----|----|---|

| File | Edit Log Configuration Control signals View Help |      |     |    |   |

| ##   | Testing the Comblock Registers                   |      |     |    |   |

|      |                                                  |      |     |    |   |

|      | Testing the Loopback                             |      |     |    |   |

| 00P  | value send 100, read 100                         |      |     |    |   |

| ##   | Testing the ALU                                  |      |     |    |   |

|      | in $A=10$ , $B=5$                                |      |     |    |   |

|      | ation status: 2                                  |      |     |    |   |

|      | ation option = 0, result = 0                     |      |     |    |   |

| per  | ation status: 0                                  |      |     |    |   |

|      | ation option = 1, result = 15                    |      |     |    |   |

|      | ation status: 0                                  |      |     |    |   |

|      | ation option = 2, result = 5                     |      |     |    |   |

|      | ation status: 0                                  |      |     |    |   |

|      | ation option = 3, result = 15<br>ation status: 2 |      |     |    |   |

|      | ation option = 4, result = 0                     |      |     |    |   |

|      | ation status: 0                                  |      |     |    |   |

|      | ation option = 5, result = 15                    |      |     |    |   |

|      | ation status: 2                                  |      |     |    |   |

| per  | ation option = 6, result = 0                     |      |     |    |   |

|      | ation status: 0                                  |      |     |    |   |

|      | ation option = 7, result = 320                   |      |     |    |   |

|      | sting FIFOs with 1024 values                     |      |     |    |   |

|      | • _ ETEO _ A A                                   |      |     |    | ľ |

| /dev | /ttyACM0 115200-8-N-1 DTR RTS CT                 | S CD | DS  | RR | Ł |

# User: smr3983 Password: 3983smr!CPT24

WARNING: Do not fail the password more than 3 times. Feel free to raise your hand. Is better ask for help.

### Links: WhatsApp group

### **Google Fotos**