## 1st Mesoamerican Workshop on Reconfigurable X-ray Scientific Instrumentation for Cultural Heritage

#### Lab 0: User environment

Antigua Guatemala, Junio 2025

#### **Maynor Ballina**

The Abdus Salam International Centre for Theoretical Physics

#### **Welcome: Lab tutors**

Maynor Ballina (ICTP, UNITS) [Guatemala] Dr. Luis Garcia (ICTP) [Guatemala]

Dr. Romina Molina (ICTP) [Argentina]

Dr. Fabian Castano (UdeA) [Colombia]

M.Eng. Jorge Balsells (USAC) [Guatemala]

## Labs Overview:

- Lab 0: User environment

- Lab 1: Getting started with SoC-FPGA

- Lab 2: Reconfigurable instrumentation on SoC-FPGA: digital

- oscilloscope using comblock and RTL instantiation

- Lab 3:

Soc-FPGA Development Framework for Analog signal interfaces

• Lab 4:

Digital Pulse Processing Electronics for X-ray Photon Detection in Cultural Heritage Analysis

• Lab 5:

Introduction to machine learning and SoC/FPGA

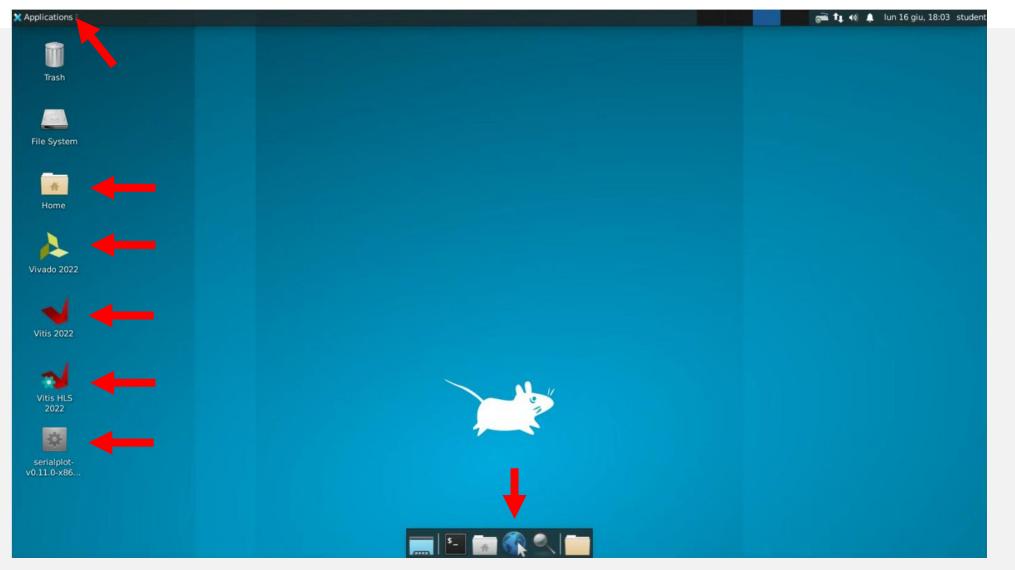

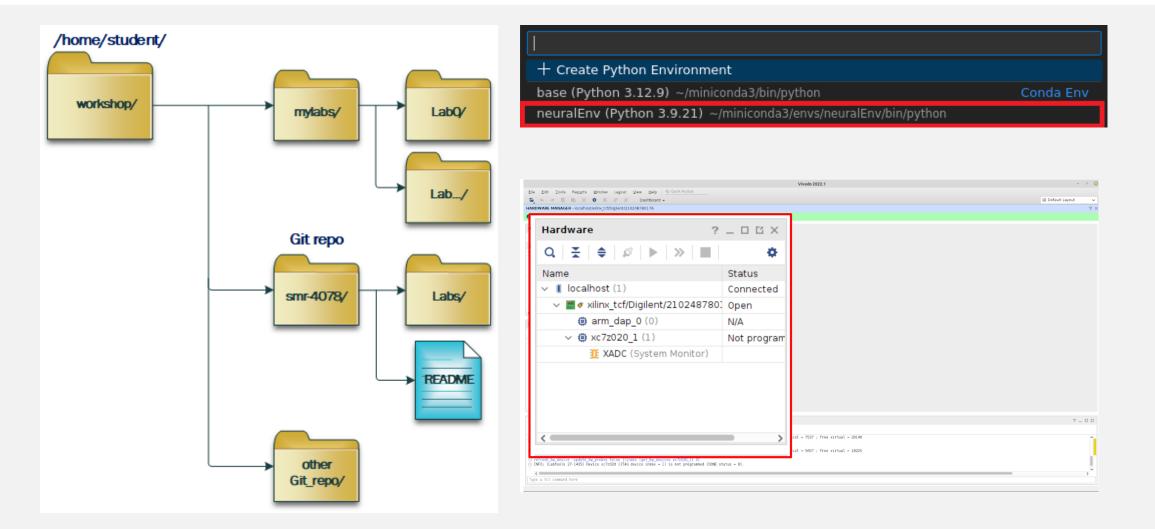

### **User Environment:**

## **User Environment:**

## **Important links:**

#### https://gitlab.com/ictp-mlab/smr-4078

## **Important links:**

#### https://gitlab.com/ictp-mlab/smr-4078/-/wikis/home

### Labs 0:

## **1st Mesoamerican Workshop on Reconfigurable X-ray Scientific Instrumentation for Cultural Heritage**

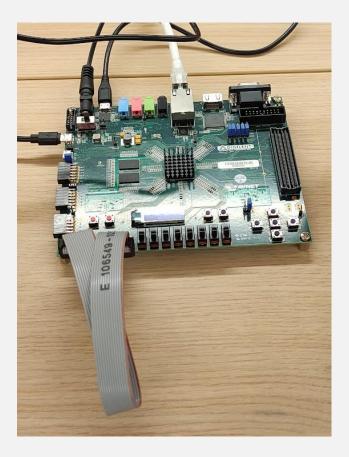

### Lab 1: Getting started with SoC-FPGA

Antigua Guatemala, Junio 2025

#### **Maynor Ballina**

International Centre for Theoretical Physics

## Labs 1: Objectives

- Acquire the knowledge of the SoC-FPGA design flow using the Vitis Unified Software Platform.

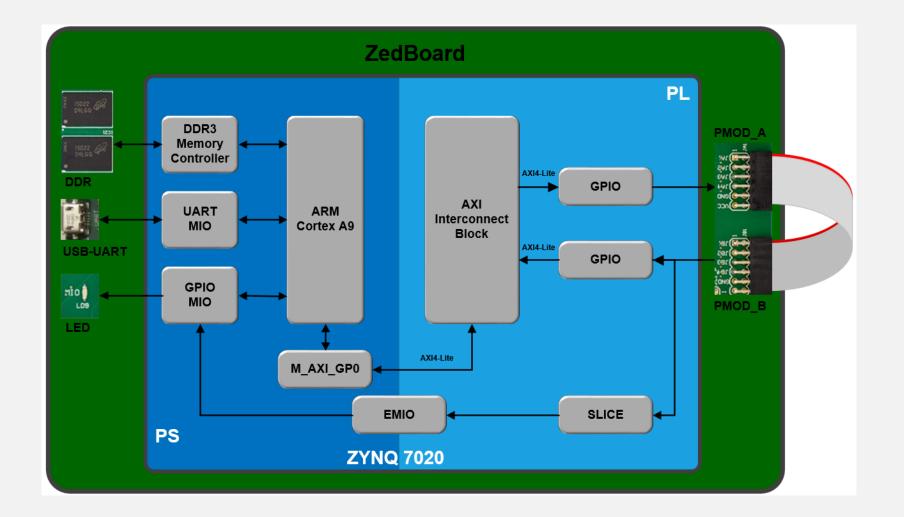

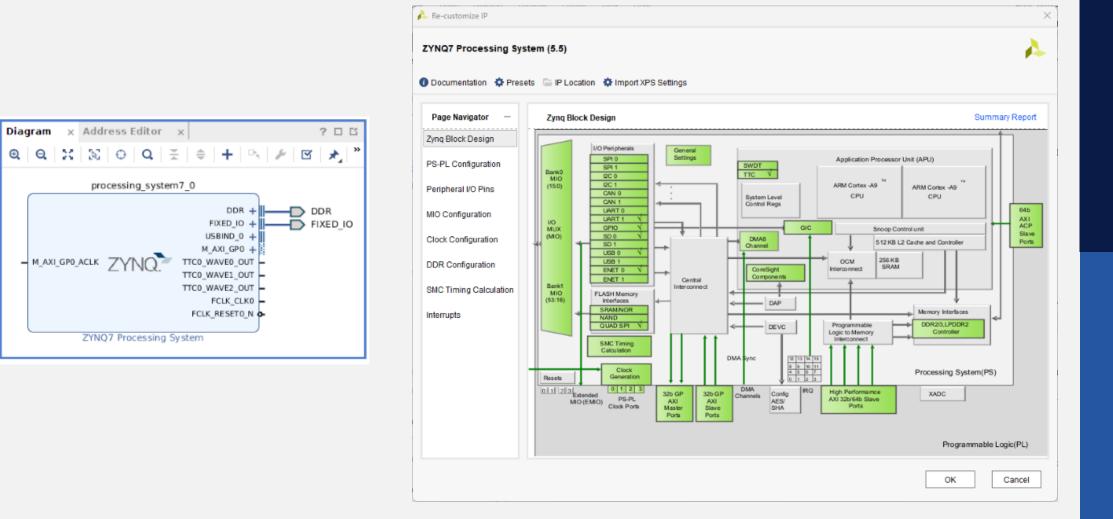

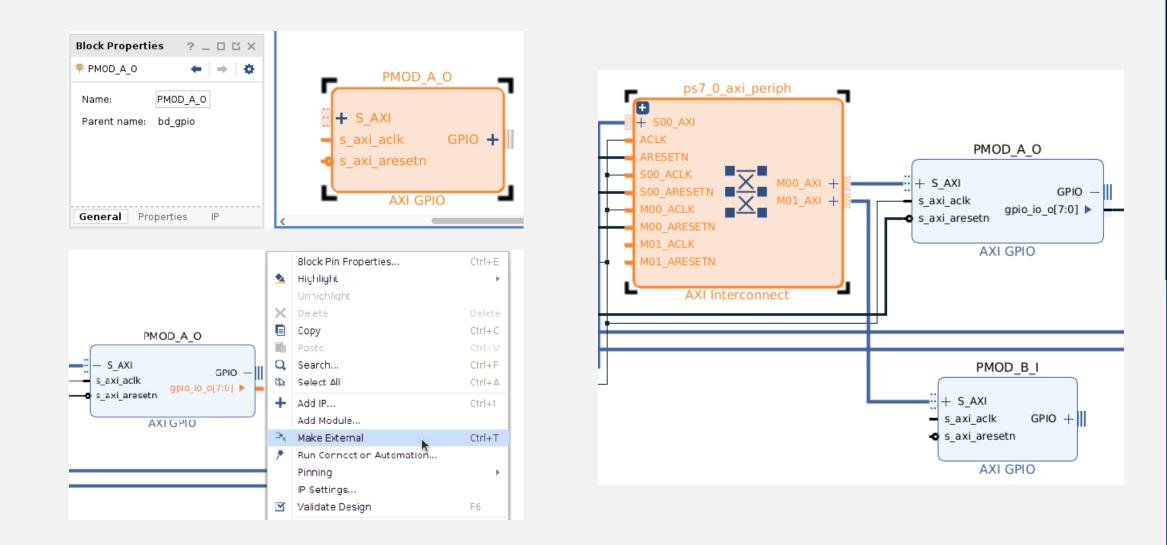

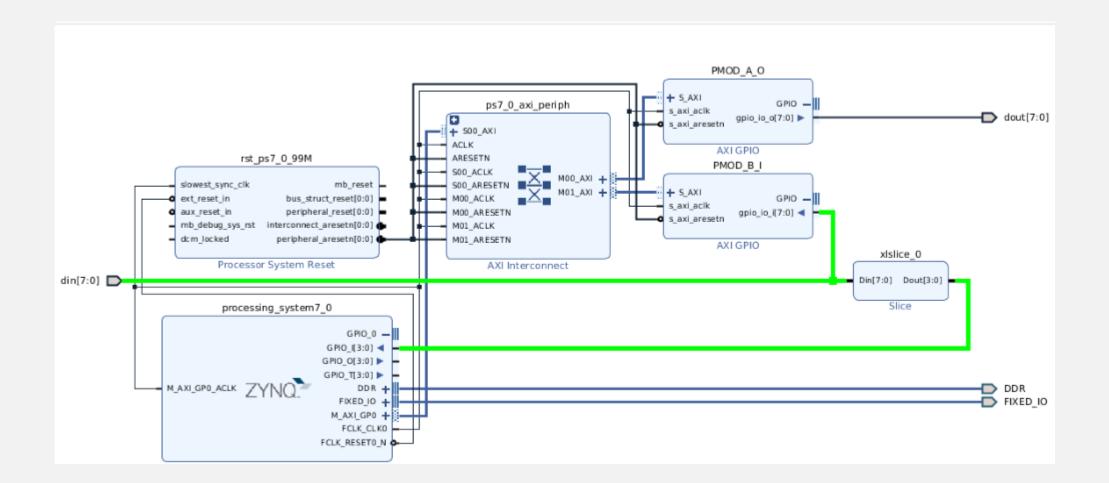

- Create the hardware to configure the FPGA part of the SoC, configure the PS instantiate the GPIO blocks and understand the communication between the different components of the design

- Create the 'C' application that will run on the PS to control the reading and the writing

of the generated hardware

- Test the complete design on the ZedBoard platform to verify the implementation.

## Labs 1: Design description

### Labs 1: Hardware

#### Labs 1: Steps

### Labs 1: Final Block Design

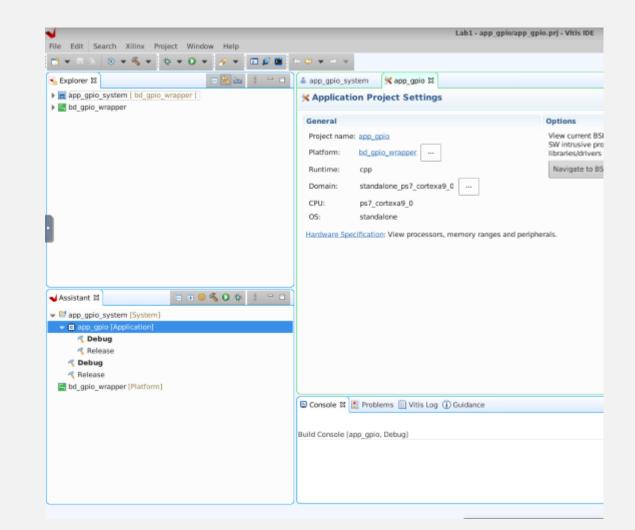

## Labs 1: Software

- Application project

- C program

- AXI Communication

😑 Console 🛱 💦 Problems 📗 Vitis Log (i) Guidance Build Console [app\_gpio, Debug] Building target: app\_gpio.elf Invoking: ARM v7 gcc linker arm-none-eabi-gcc -mcpu=cortex-a9 -mfpu=vfpv3 -mfloat-abi=hard -Wl,-build-i Finished building target: app gpio.elf Invoking: ARM v7 Print Size arm-none-eabi-size app gpio.elf |tee "app gpio.elf.size" hex filename text data bss dec 1184 22616 50821 27021 c685 app gpio.elf Finished building: app\_gpio.elf.size 16:39:16 Build Finished (took 645ms)

### Labs 1: Results

- PL Hardware

- PS program

- AXI Communication

- PMOD data transfer

- Optional:

- Challenge

| PMODA | Output: | 213, | PMODB | Receive: | 213 | PSGPIO | Receive | 13 |

|-------|---------|------|-------|----------|-----|--------|---------|----|

| PMODA | Output: | 214, | PMODB | Receive: | 214 | PSGPIO | Receive | 13 |

| PMODA | Output: | 215, | PMODB | Receive: | 215 | PSGPIO | Receive | 13 |

| PMODA | Output: | 216, | PMODB | Receive: | 216 | PSGPIO | Receive | 13 |

| PMODA | Output: | 217, | PMODB | Receive: | 217 | PSGPIO | Receive | 13 |

| PMODA | Output: | 218, | PMODB | Receive: | 218 | PSGPIO | Receive | 13 |

| PMODA | Output: | 219, | PMODB | Receive: | 219 | PSGPIO | Receive | 13 |

| PMODA | Output: | 220, | PMODB | Receive: | 220 | PSGPIO | Receive | 13 |

| PMODA | Output: | 221, | PMODB | Receive: | 221 | PSGPIO | Receive | 13 |

| PMODA | Output: | 222, | PMODB | Receive: | 222 | PSGPIO | Receive | 13 |

| PMODA | Output: | 223, | PMODB | Receive: | 223 | PSGPIO | Receive | 13 |

| PMODA | Output: | 224, | PMODB | Receive: | 224 | PSGPIO | Receive | 14 |

| PMODA | Output: | 225, | PMODB | Receive: | 225 | PSGPIO | Receive | 14 |

| PMODA | Output: | 226, | PMODB | Receive: | 226 | PSGPIO | Receive | 14 |

| PMODA | Output: | 227, | PMODB | Receive: | 227 | PSGPIO | Receive | 14 |

| PMODA | Output: | 228, | PMODB | Receive: | 228 | PSGPIO | Receive | 14 |

| PMODA | Output: | 229, | PMODB | Receive: | 229 | PSGPIO | Receive | 14 |

| PMODA | Output: | 230, | PMODB | Receive: | 230 | PSGPIO | Receive | 14 |

| PMODA | Output: | 231, | PMODB | Receive: | 231 | PSGPIO | Receive | 14 |

| PMODA | Output: | 232, | PMODB | Receive: | 232 | PSGPIO | Receive | 14 |

| PMODA | Output: | 233, | PMODB | Receive: | 233 | PSGPIO | Receive | 14 |

| PMODA | Output: | 234, | PMODB | Receive: | 234 | PSGPIO | Receive | 14 |

| PMODA | Output: | 235, | PMODB | Receive: | 235 | PSGPIO | Receive | 14 |

| PMODA | Output: | 236, | PMODB | Receive: | 236 | PSGPIO | Receive | 14 |

| PMODA | Output: | 237, | PMODB | Receive: | 237 | PSGPIO | Receive | 14 |

| PMODA | Output: | 238, | PMODB | Receive: | 238 | PSGPIO | Receive | 14 |

| PMODA | Output: | 239, | PMODB | Receive: | 239 | PSGPIO | Receive | 14 |

|       |         |      |       |          |     |        |         |    |

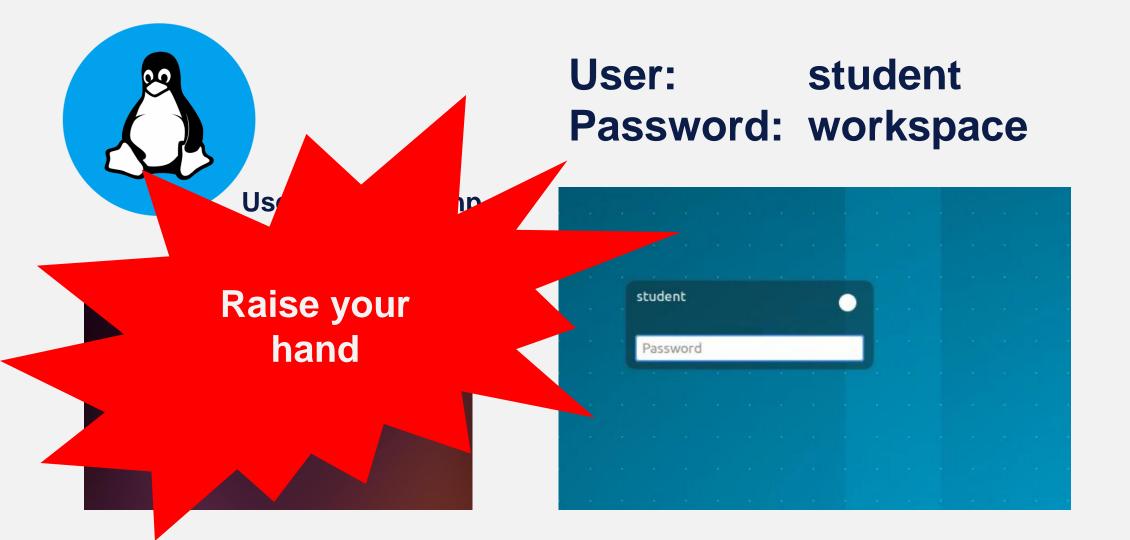

# User: student Password: workspace

WARNING: Limited space. Please handle the power supply connections, development boards, and computers with care.