1st Mesoamerican Workshop on Reconfigurable X-ray Scientific Instrumentation for **Cultural Heritage**

#### Hardware Ion Langua Reco Instrum

Cristian Sisterna

Senior Associate, ICTP-MLAB

Universidad Nacional San Juan- Argentina 🎱

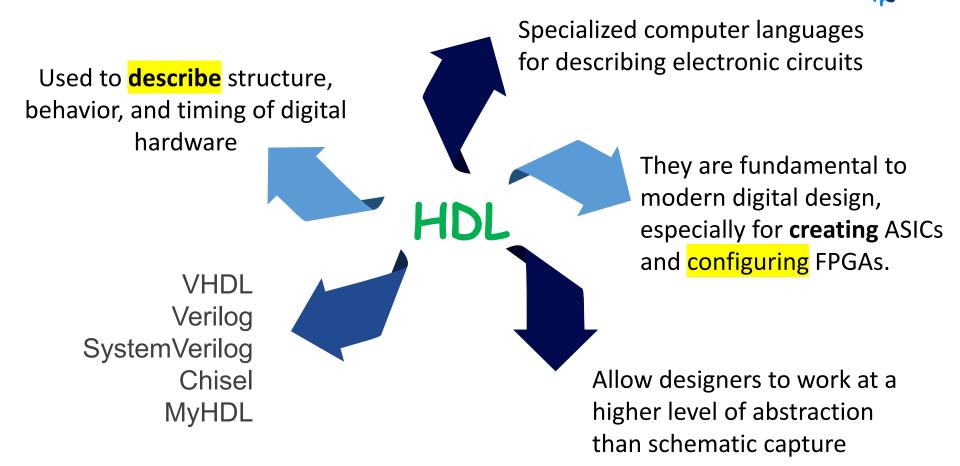

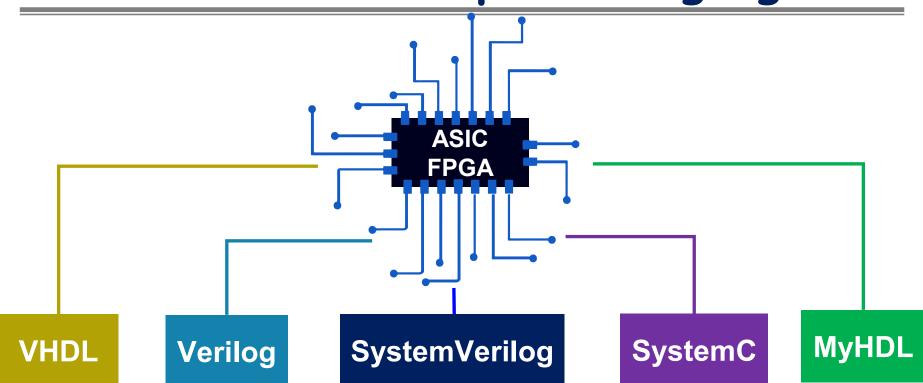

#### Hardware Description Languages

What are them ?

#### Hardware Description Languages

Developed under the U.S. DoD's VHSIC program.

Strongly typed

More verbose and formal (resembles Ada)

Started as a proprietary language.

Weakly typed.

Syntax similar to C programming language

#### Superset of Verilog.

Adds OOP, improved data types, assertions, interfaces.

Powerful for systemlevel verification. C++ libraries for systemlevel modeling.

Often used for Transaction-Level Modeling (TLM).

#### Python based HDL

# Why HDLs are keys in Digital Design?

#### Abstraction

Design complex circuits without low-level details

#### Verification

Simulate and test designs before fabrication (cost-saving)

#### Reusability

Create modular and reusable IP (Intellectual Property) blocks.

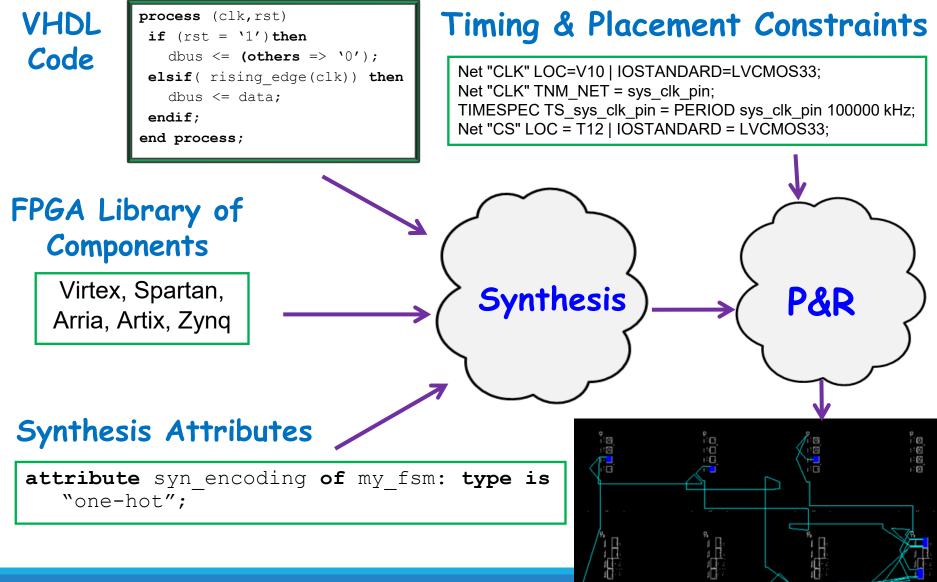

#### **Synthesis**

Automatically transform HDL into ASIC/FPGA's hardware components

#### Scalability

Enable design of very large and complex systems

HDLs

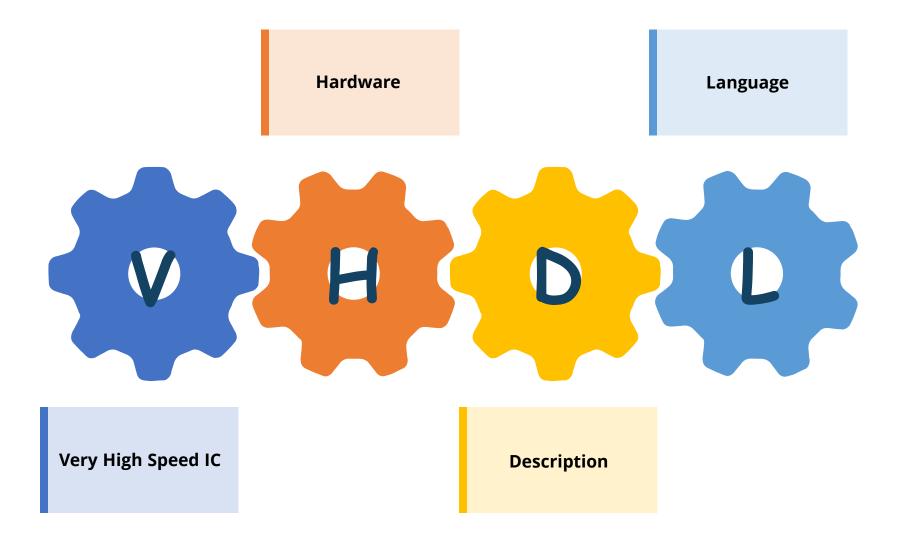

#### Introduction to VHDL

## Introduction to VHDL

#### High level of abstraction

```

if (reset='1') then

count <= 0;

elsif(rising_edge(clk)) then

count <= count+1;</pre>

end if;

```

Easy to debug

✓ Parameterized designs

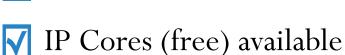

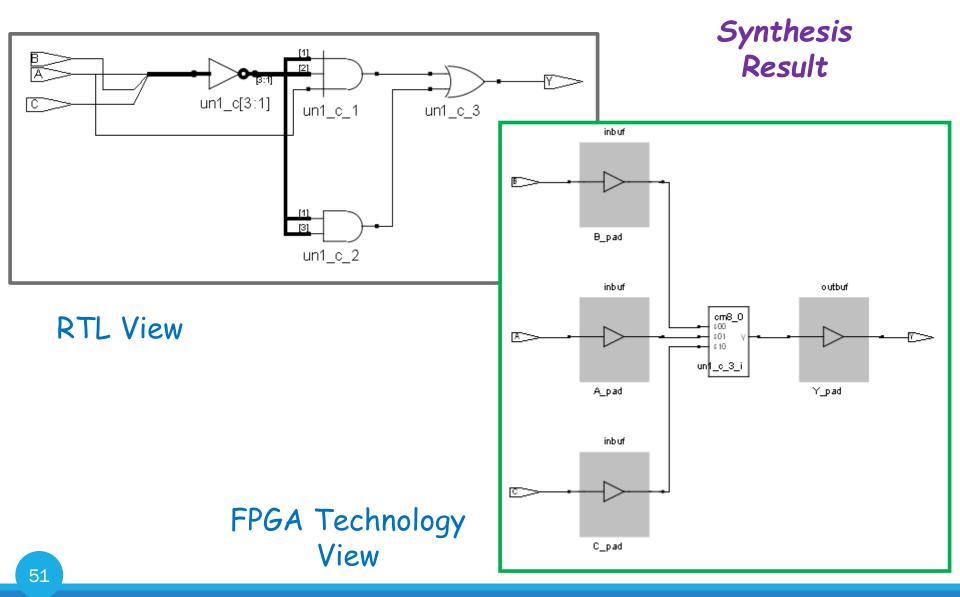

## **VHDL** Synthesis & Simulation

#### Synthesis versus Simulation

It's important to understand that VHLD is both, a *Synthesis* language and a *Simulation* language.

#### Synthesis

Small subset of the language is '*synthesizable*', meaning that it can be translated into logic gates, flip-flops, and other 'hardware' components.

Every line of VHDL code must have a direct translation into hardware.

Another subset of the language include many features for '*simulation*' or '*verification*', features that have **NO meaning in hardware**.

Simulation

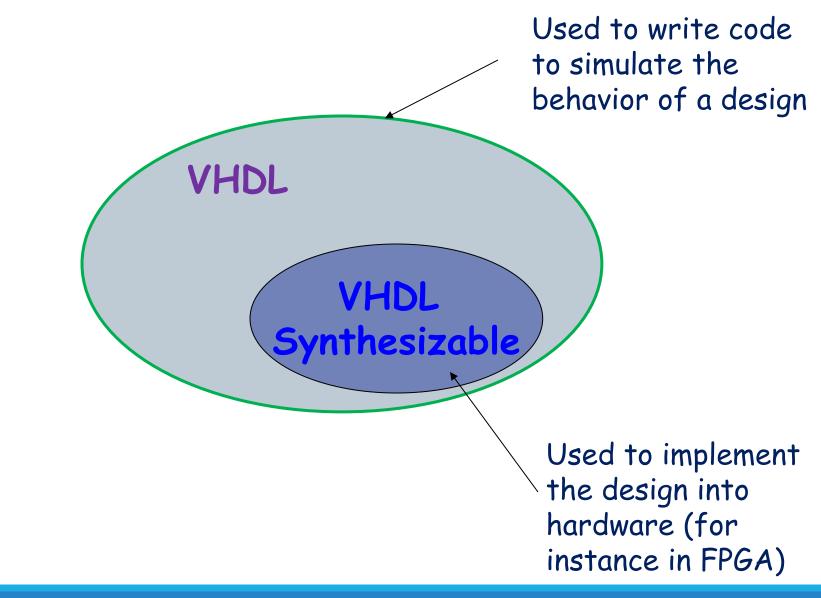

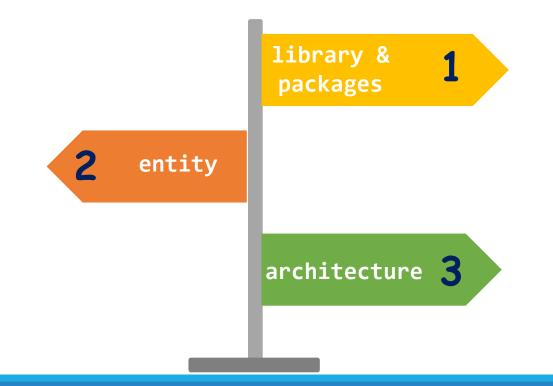

# VHDL -> Hardware Description

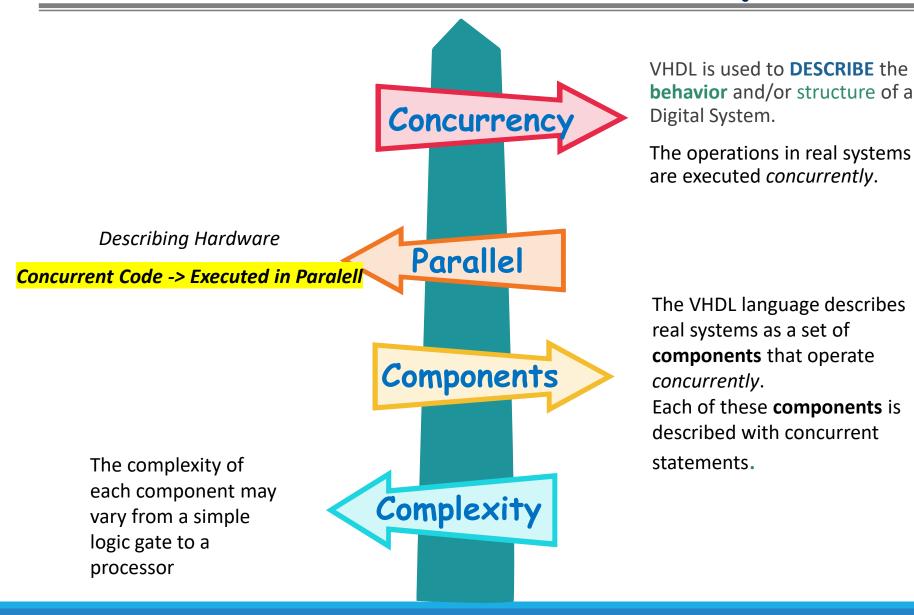

## VHDL 'Description' Examples

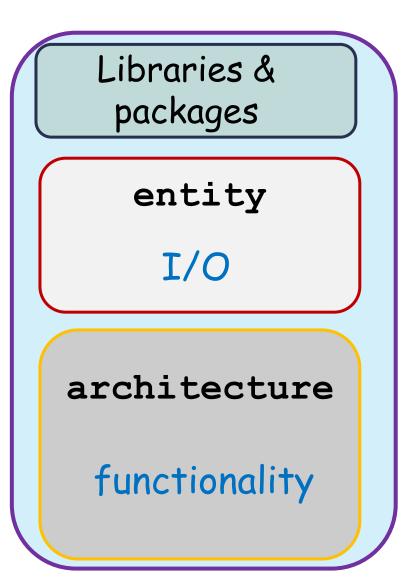

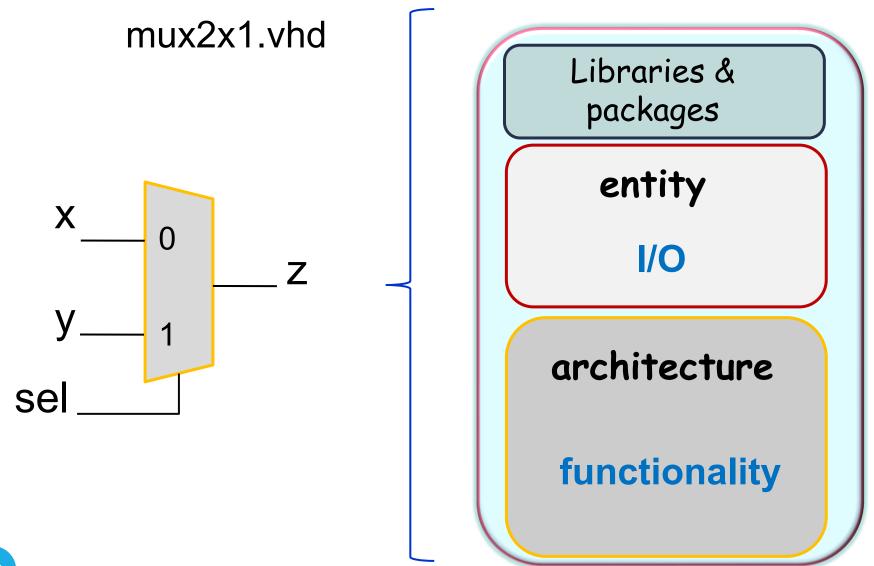

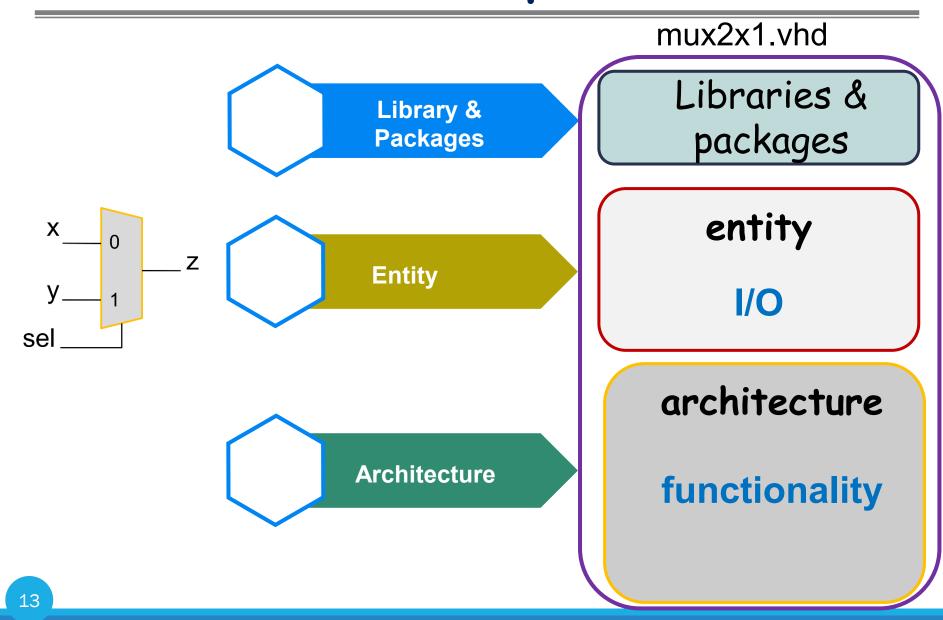

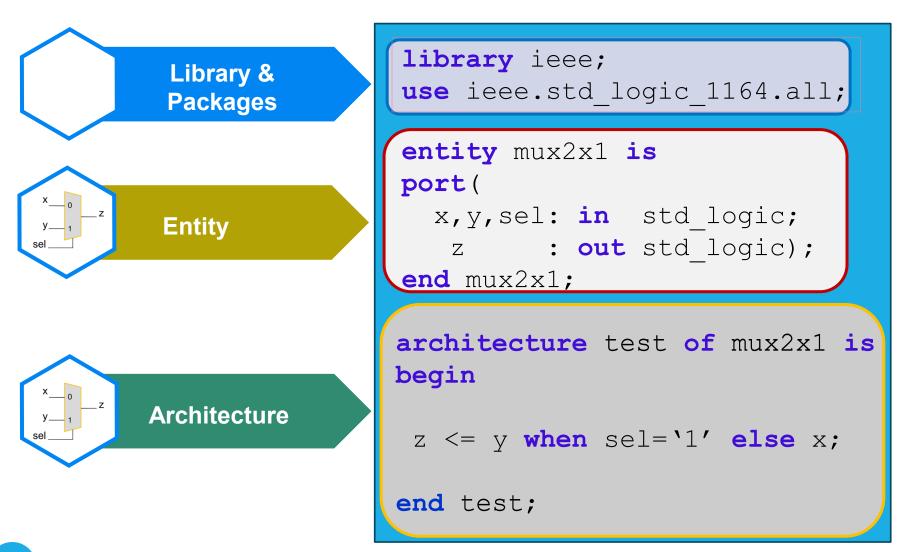

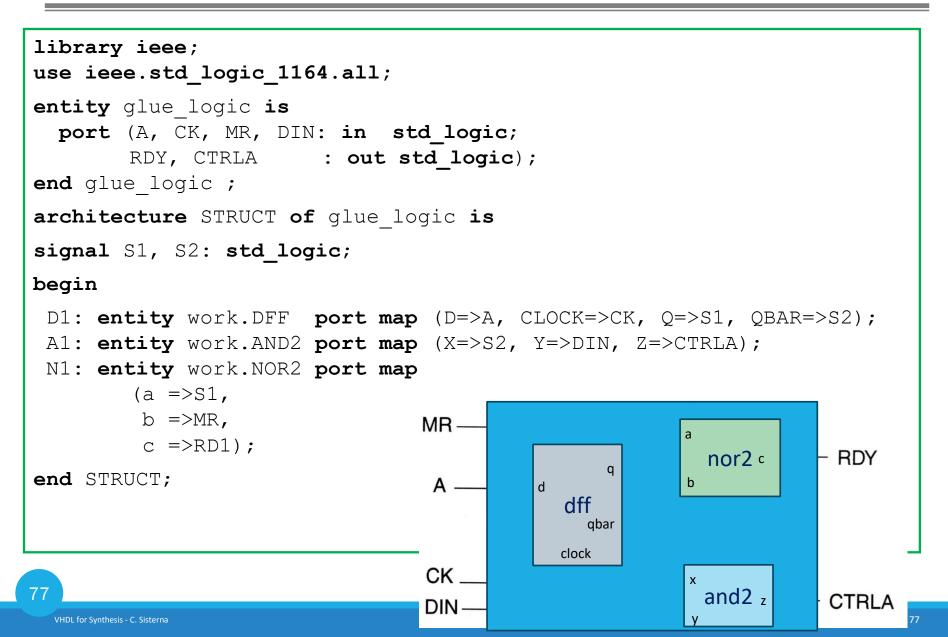

Libraries and packages provides the incorporation of external functions, data types and components to the component to be described

The **entity** defines the I/O ports as well as the name of the component.

Some times a constant(s) is defined (generic) to write parameterized VHDL code

The **architecture** it's where the hardware **behavior** and/or **structure** is described.

It can have from a couple of lines to thousands lines of VHDL code.

ALL CONCURRENTS !

| Library &<br>Packages                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | <pre>library ieee; use ieee.std_logic_1164.all;</pre>                                                                                             |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| x 0 y 1 Entity                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | <pre>entity mux2x1 is port(     x,y,sel: in std_logic;     z : out std_logic); end mux2x1;</pre>                                                  |

| tu<br>Marine Marine Marine<br>Marine Marine | <pre>architecture test of mux2x1 is begin process(x,y,sel) begin if(sel='1') then z &lt;= y; else z &lt;= x; end if; end process; end test;</pre> |

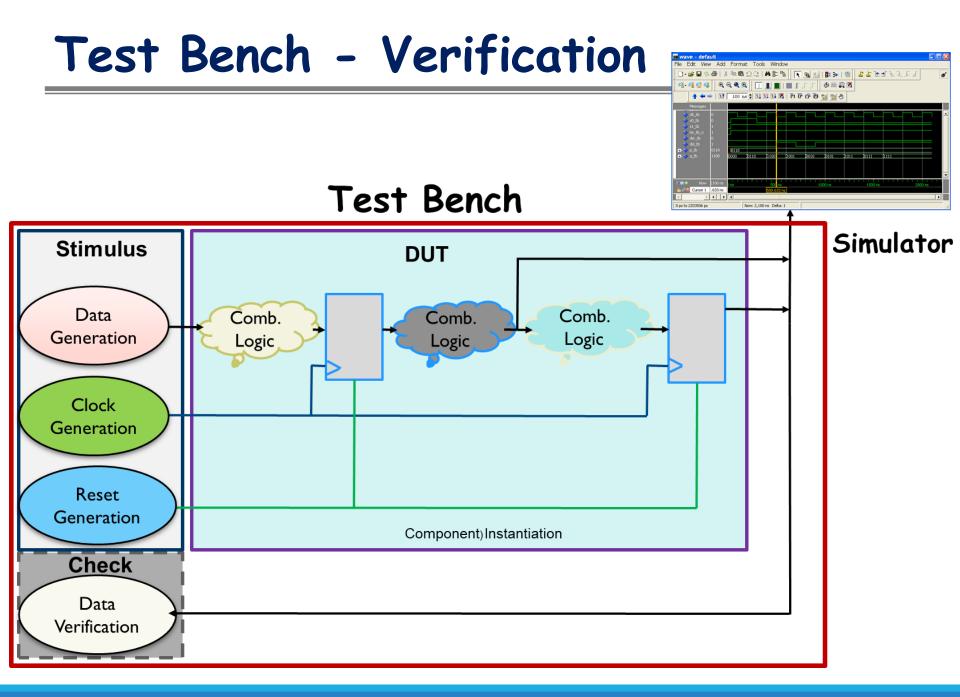

# Test Bench

#### VHDL Code - Is it really Works?

A **test bench** is a crucial part of the hardware design and verification process.

It's a separate VHDL entity that is used to **simulate and verify the functionality of a VHDL design** (known as the "Device Under Test" or "DUT") by providing it with input stimuli and observing its outputs

# Purposes of a test bench

It applies a sequence of input values (stimuli) to the DUT's input ports. These stimuli are designed to stimulate all the different operational modes and corner cases of the DUT.

It observes the DUT's output ports and compares them against expected values.

It determines whether the DUT behaves as intended: **Assertions:** Checking if certain conditions are met during simulation.

**Expected Value Comparison:** Directly comparing actual outputs with pre-calculated expected outputs. **Self-checking Test Benches:** More advanced test benches that automatically report pass/fail status.

When the DUT doesn't behave as expected, the test bench provides a controlled environment to isolate and debug issues.

## VHDL - Simulation / Verification

| Image: wave - defa         File       Edit         View         Image: wave - defa         Image: wa | v Add<br><i>∰</i>   ¥<br>] <b>Q</b> (      | . 🖻 🖻 |              | ₩. ₽<br>■    | - Þ          |      |      | 🜢 🛗 🌠 | 3 | · 占 1+ : | <b>→</b> | . <u>.</u> |       | ⊐× |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|-------|--------------|--------------|--------------|------|------|-------|---|----------|----------|------------|-------|----|--|

| Messages<br>clk_tb<br>clk_tb<br>s0_tb<br>s1_tb<br>mr_tb_n<br>dsr_tb<br>dsr_tb<br>+                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 0<br>0<br>1<br>1<br>0<br>1<br>0110<br>1100 |       | 0110         |              |              | 1001 | 0010 | 0101  |   | D111     |          |            |       |    |  |

| Now<br>Cursor 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2100 ns<br>.633 ns                         | ) ns  | Now: 2,100 r | 500<br>500.6 | Ins<br>33 ns |      |      | 0 ns  |   | 1500 ns  |          | 200        | )0 ns |    |  |

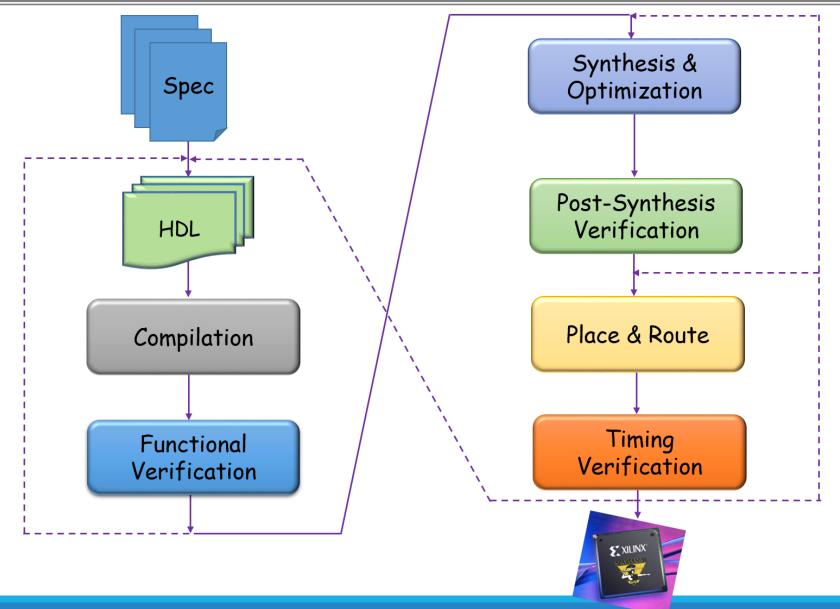

# VHDL-FPGA Design Flow

#### VHDL - FPGA Design Flow

22

#### FGPA - Hardware Design Flow

ICTP- MLAB

# VHDL Simple Example

#### Simple Example - VHDL

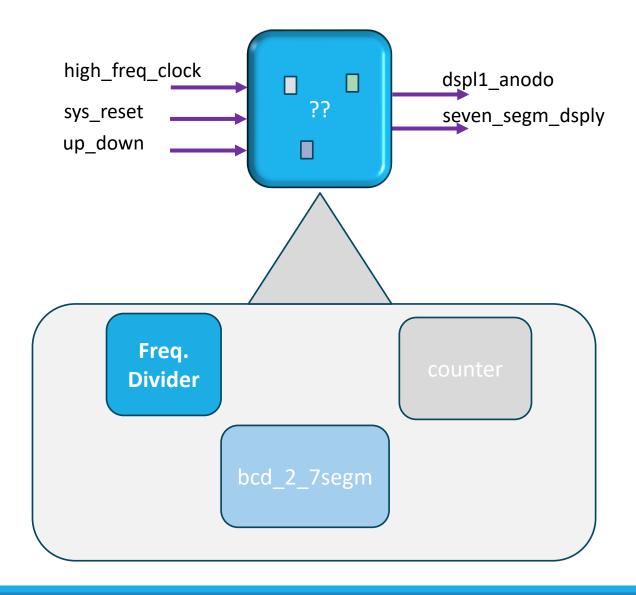

Design a BCD up-down counter. The count should be displayed in a 7-segment display.

The system has a high frequency clock and system reset as inputs.

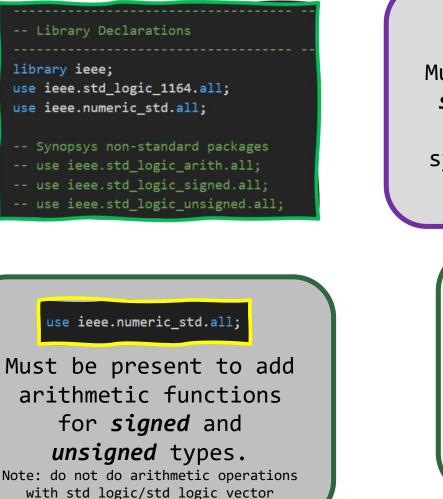

#### Libraries & Packages

library ieee; use ieee.std\_logic\_1164.all;

Must be present to use std\_logic type. That is, for ALL synthesisable designs.

-- Synopsys non-standard packages

-- use ieee.std logic\_arith.all;

-- use ieee.std\_logic\_signed.all;

-- use ieee.std\_logic\_unsigned.all;

DO NOT USE these

packages. There do not belong to the VHDL IEEE standard.

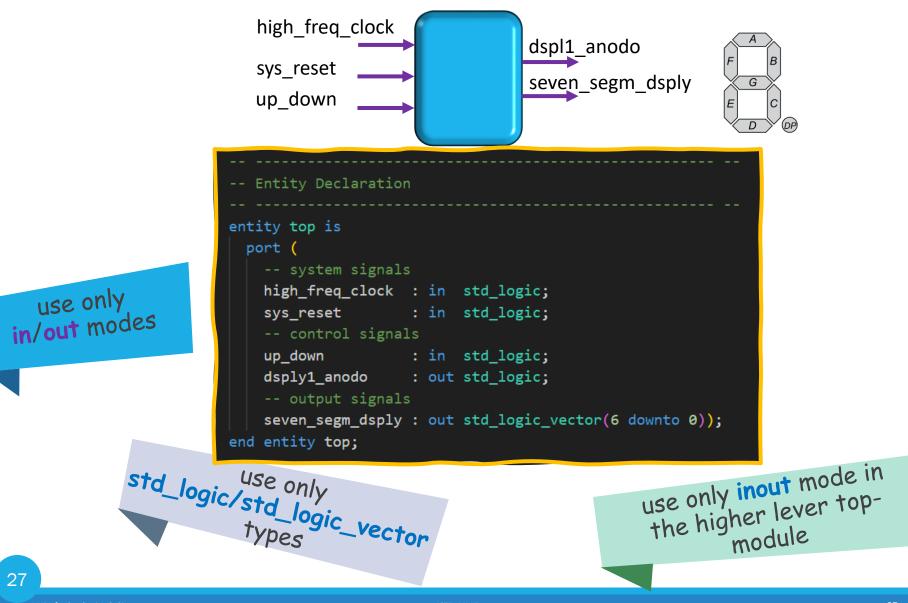

#### Signal/Port Declarations in the Entity

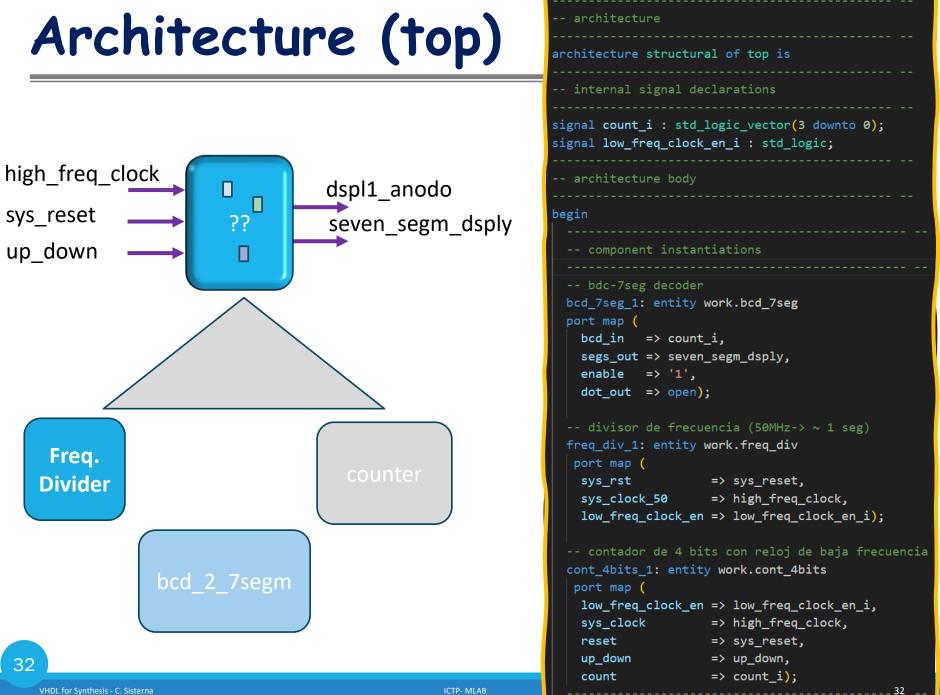

# Architecture (top)

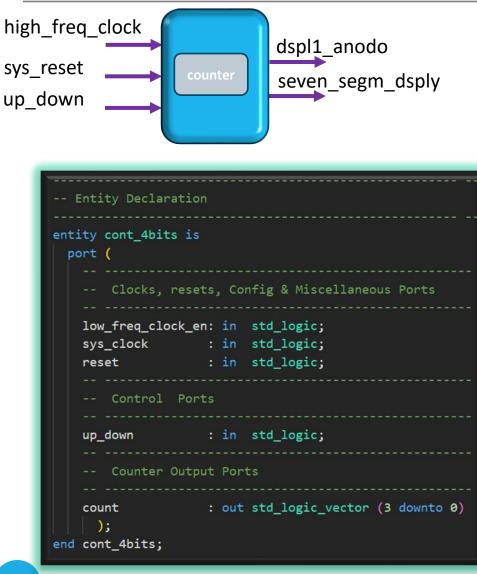

# Counter entity/arch.

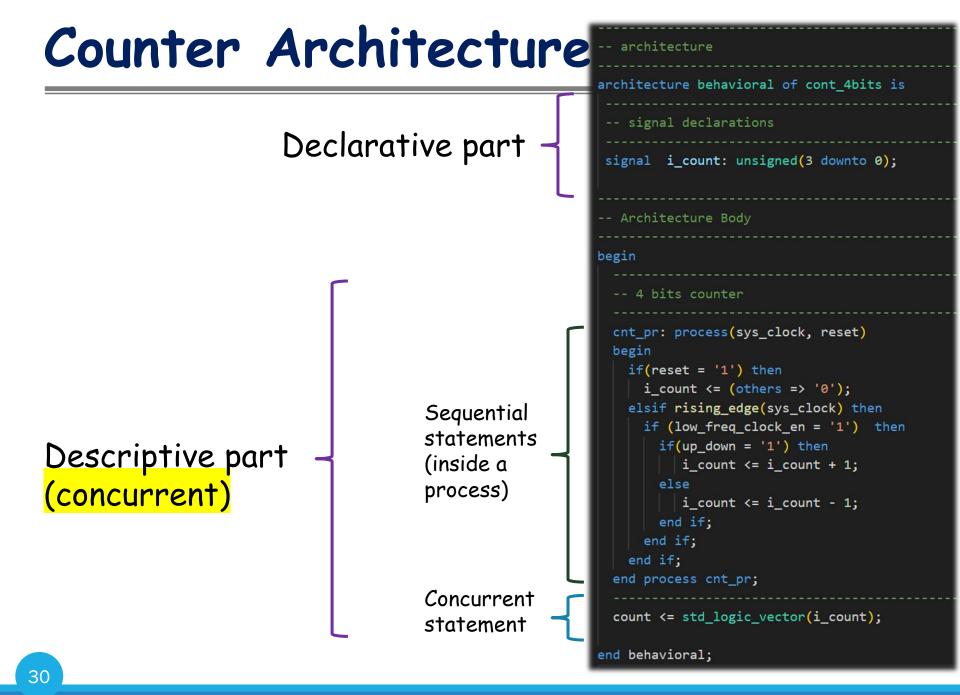

| - architecture                                                                 |

|--------------------------------------------------------------------------------|

| architecture behavioral of cont_4bits is                                       |

| signal declarations                                                            |

| <pre>signal i_count: unsigned(3 downto 0);</pre>                               |

| - Architecture Body                                                            |

| egin                                                                           |

| 4 bits counter                                                                 |

| <pre>cnt_pr: process(sys_clock, reset) begin</pre>                             |

| if(reset = '1') then                                                           |

| <pre>i_count &lt;= (others =&gt; '0'); elsif rising_edge(sys_clock) then</pre> |

| if (low_freq_clock_en = '1') then                                              |

| if(up_down = '1') then                                                         |

| i_count <= i_count + 1;                                                        |

| else<br>i_count <= i_count - 1;                                                |

| end if;                                                                        |

| end if;                                                                        |

| end if;                                                                        |

| end process cnt_pr;                                                            |

| <pre>count &lt;= std_logic_vector(i_count);</pre>                              |

| end behavioral;                                                                |

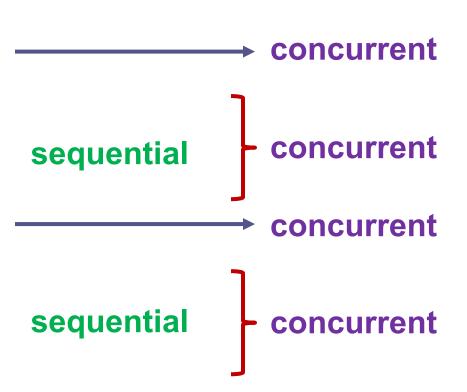

#### Understanding Concurrency

architecture example of entity\_ex is

-- architecture declarative part

#### begin

-- architecture descriptive part

signal assignment concurrent statement; signal assignment concurrent statement; process concurrent statement;

begin

signal assignment sequential statement; signal assignment sequential statement; end process; signal assignment concurrent statement; process concurrent statement; begin signal assignment sequential statement; signal assignment sequential statement; end process; end example;

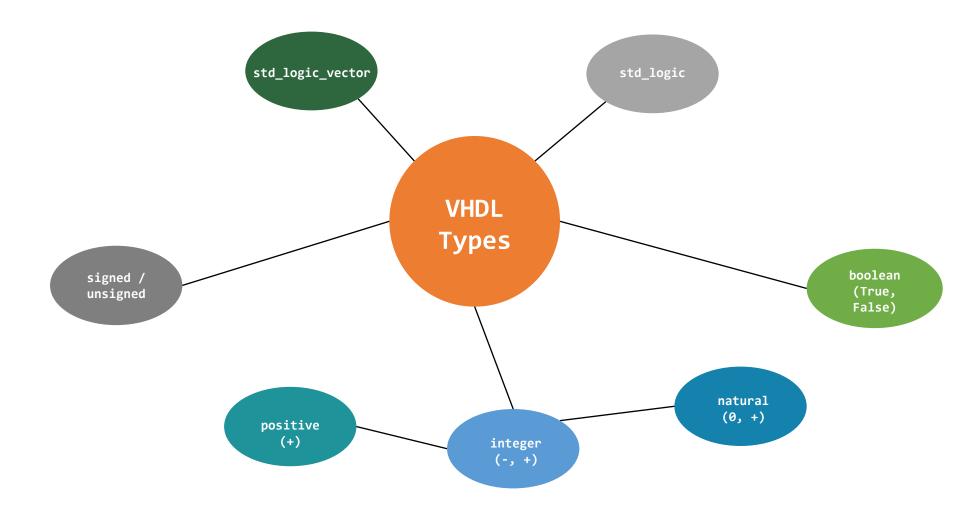

#### VHDL Types, Objects & Classes

#### VHDL Data Types

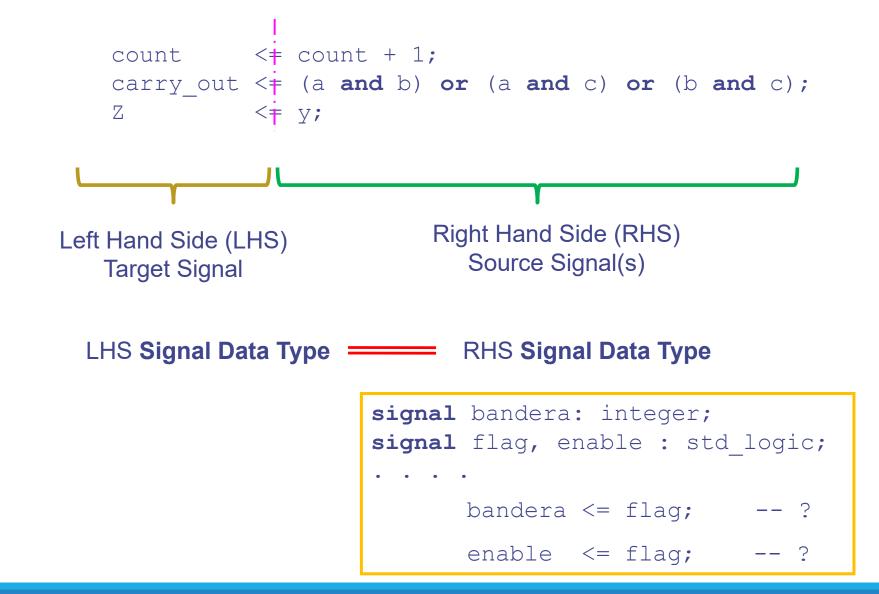

## Signal Assignment - strongly typed

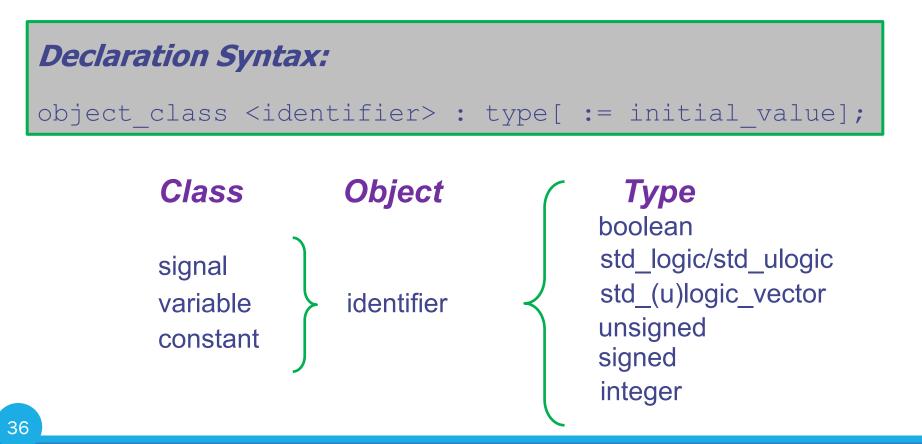

# VHDL Object

An **object** holds a value of some specified **type** and can be one of the three **classes**: **signal**, **variable**, **constant**

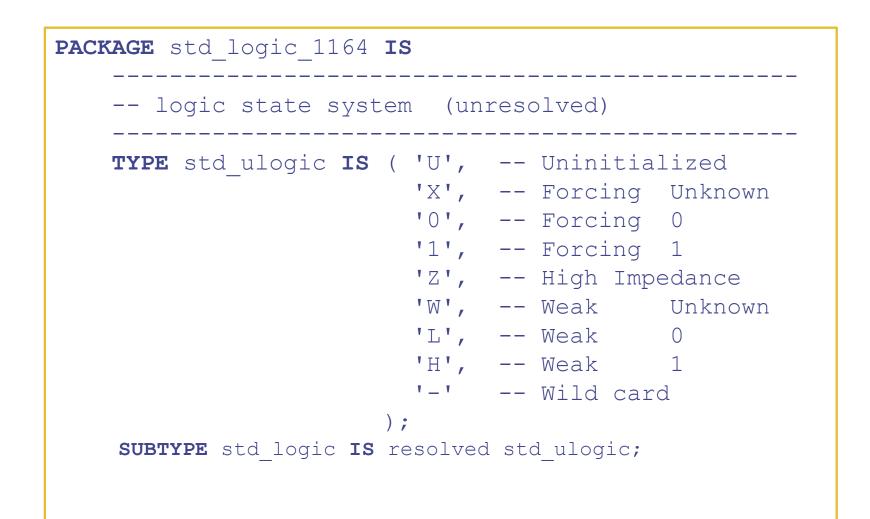

## std\_logic Type

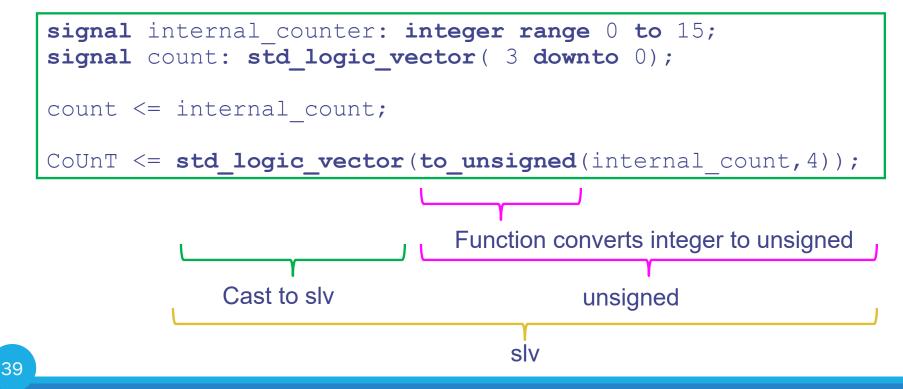

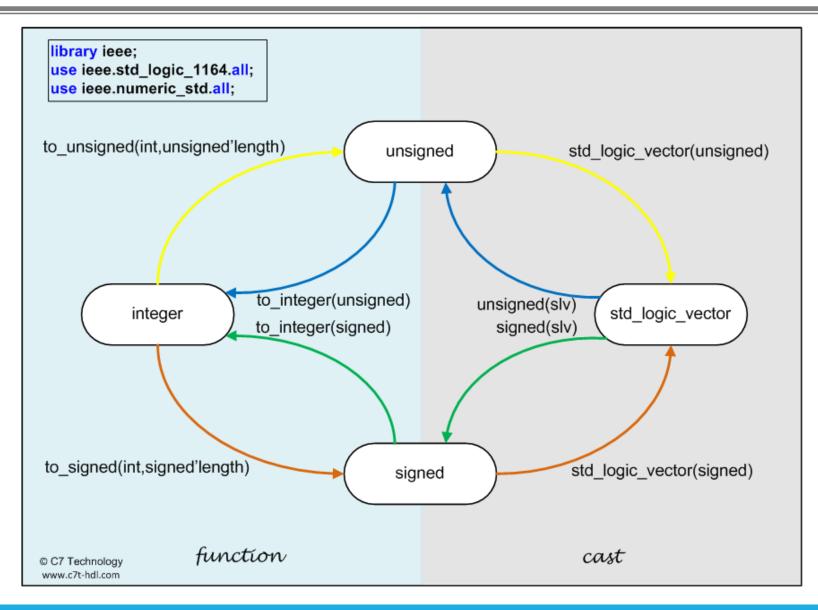

## **Type Conversion - Casting**

VHDL does allow restricted type of <u>CASTING</u>, that is converting values between related types

datatype <= type(data\_object);</pre>

```

signal max_rem: unsigned (7 downto 0);

signal more_t: std_logic_vector( 7 downto 0);

max_rem <= more_t;

max_rem <= unsigned(more_t);</pre>

```

unsigned and std\_logic\_vector are both vectors of the same element

type, therefore it's possible a direct conversion by casting. When

there is not type relationship a conversion function is used.

## **Type Conversion - Functions**

VHDL does have some built-in functions to convert some different data types (not all the types allow conversions)

datatype <= to\_type(data\_object);</pre>

## Type Conversion - Cast / Function

## **VHDL** Operators

| Operator                                                    | Description                                                                          | Data type<br>of a           | Data type<br>of b | Data type<br>of result |

|-------------------------------------------------------------|--------------------------------------------------------------------------------------|-----------------------------|-------------------|------------------------|

| a ** b                                                      | exponentiation                                                                       | integer                     |                   |                        |

| abs a                                                       | absolute value                                                                       | integer                     |                   |                        |

| not a                                                       | negation                                                                             | boolean, bit, bit_vector    |                   |                        |

| a * b, a / b,<br>a <b>mod</b> b, a <b>rem</b> b             | multiplication, division, modulo, remainder                                          | integer                     |                   |                        |

| +a, -a                                                      | identity, negation                                                                   | integer                     |                   | integer                |

| a + b, a - b                                                | addition, subtraction, concatenation                                                 | integer                     |                   |                        |

| a & b                                                       |                                                                                      | 1D array, element           |                   |                        |

| a sll b, a srl b,<br>a sla b, a sra b,<br>a rol b, a ror b  | shift-left (right) logical,<br>shift-left (right) arithmetic,<br>rotate left (right) | bit_vector                  | integer           | bit_vector             |

| a = b, a /= b,                                              |                                                                                      | any                         | same as a         | boolean                |

| a < b, a <= b,<br>a > b, a >= b                             |                                                                                      | scalar or 1D<br>array       | same as a         | boolean                |

| a and b, a or b,<br>a xor b, a nand b,<br>a nor b, a xnor b |                                                                                      | boolean, bit,<br>bit_vector | same as a         | same as a              |

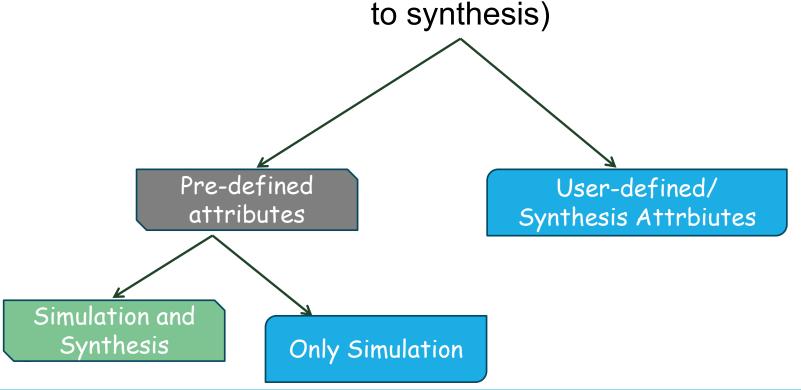

## **VHDL** Attributes

✓ It's a way of **extracting** information from a type, from the values of a type

✓ It's also a way to allow to assign additional information to objects in your design description (such as data related

## Array Attributes

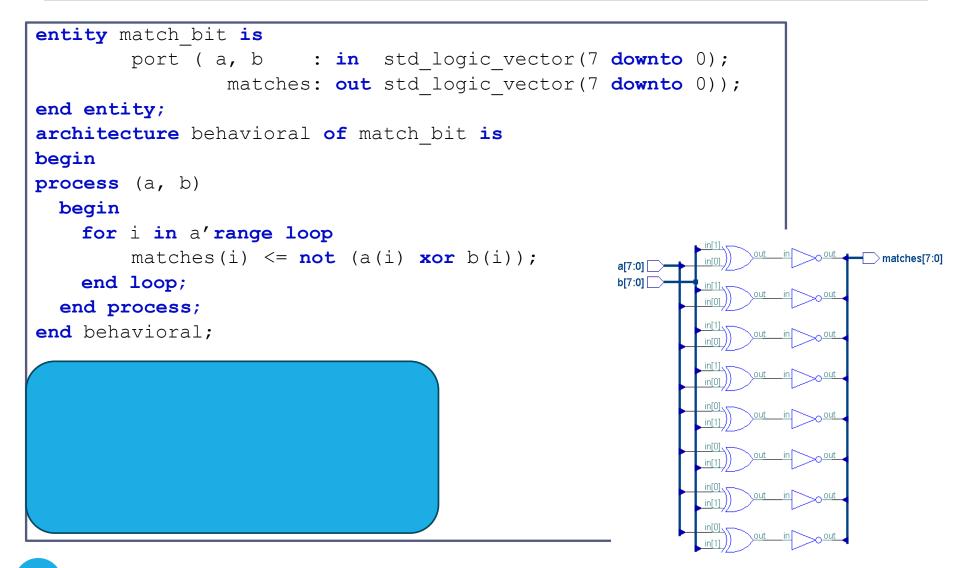

Array attributes are used to obtain information on the size, range and indexing of an array

✓ It's good practice to use attributes to refer to the size or range of an array. So, if the size of the array is change, the VHDL statement using attributes will automatically adjust to the change

| Array Attributes – Range Related |                                                  |  |  |

|----------------------------------|--------------------------------------------------|--|--|

| A'range                          | Returns the range value of a constrained array   |  |  |

| A'reverse_range                  | Returns the reverse value of a constrained array |  |  |

## Array Attributes

Use of the attributes *range* and *reverse\_range*

```

variable w_bus: std_logic_vector(7 downto 0);

then:

w_bus'range -- will return: 7 downto 0

while:

w_bus'reverse_range -- will return: 0 to 7

```

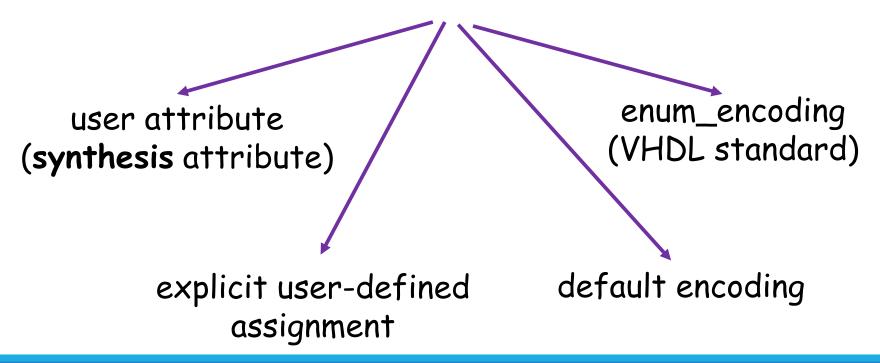

### User-defined/Synthesis Attributes

VHDL provides designers/vendors with a way of adding additional information to the system to be synthesized

- Synthesis tools use this features to add timing, placement, pin assignment, hints for resource locations, type of encoding for state machines and several others physical design information

- The bad side of synthesis attributes is that the VHDL code becomes synthesis tools/FPGA dependent, NO TRANSPORTABLE ....

### User-defined/Synthesis Attributes

Syntax

attribute attr\_name: type;

attribute attr\_name of data\_object: ObjectType is AttributeValue;

Example

attribute syn preserve: boolean;

attribute syn\_preserve of ff\_data: signal is true;

type my fsm state is (reset, load, count, hold);

attribute syn encoding: string;

attribute syn\_encoding of my\_fsm\_state: type is "gray";

### User-defined/Synthesis Attributes

Example:

# **VHDL** Statements

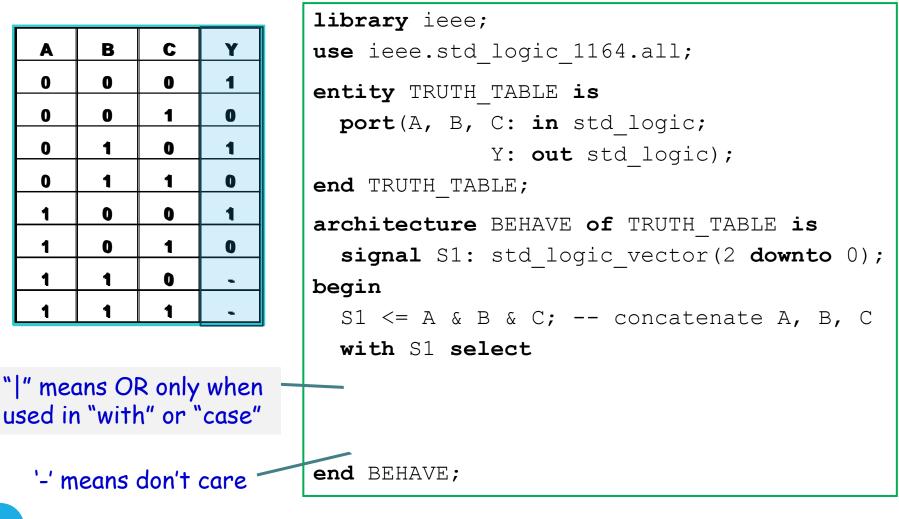

### Selective Signal Assignment Statement

### Syntax

###

A selective signal assignment describes logic based on mutually exclusive combinations of values of the selection signal

## Selective Signal Assignment Statement

#### **Example: Truth Table**

## Selective Signal Assignment Statement

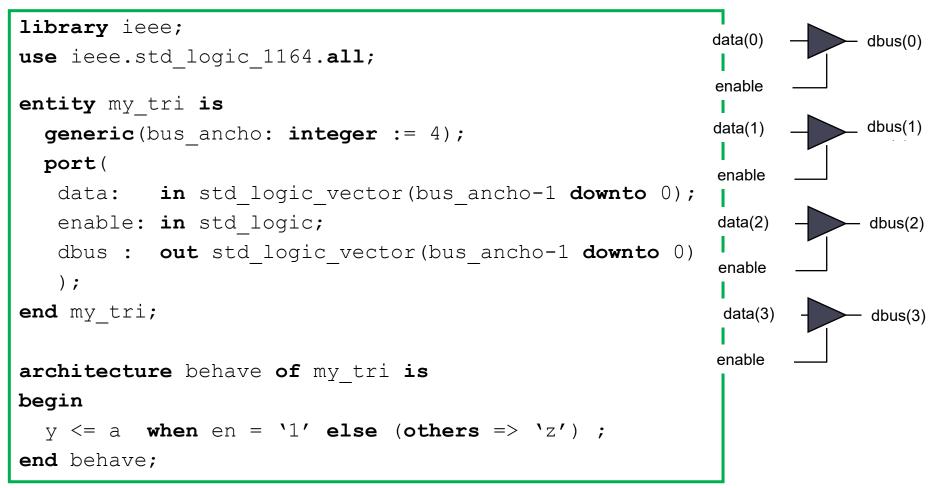

## **Conditional Signal Assignment**

#### Syntax

```

target_signal <=

<expression> when <boolean_condition> else

<expression> when <boolean_condition> else

....

<expression> when <boolean_condition>[else

<expression>];

```

A conditional signal assignment describes logic based on unrelated boolean\_conditions, the first condition that is true the value of expression is assigned to the target\_signal

## **Conditional Signal Assignment**

Main usage

dbus <= data when enable = '1' else 'Z';

#### dbus <= data when enable = '1' else (others=>'Z');

## **Conditional Signal Assignment**

#### Example

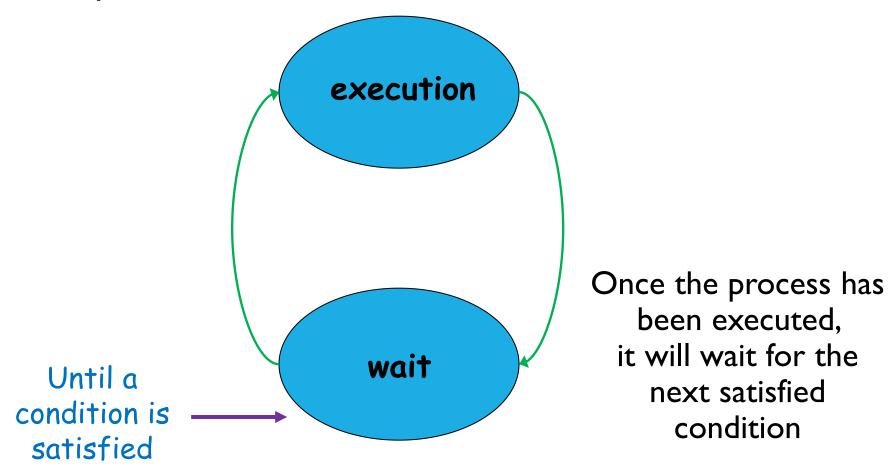

process Statement

A process is a concurrent statement, but it is the primary mode of introducing sequential statements

A process, with all the sequential

statements, is a simple concurrent

statement.

Multiple processes can be executed in

parallel

From the traditional programming view, a **process** is an *infinite loop*

### Process Statement

A process has two states: execution and wait

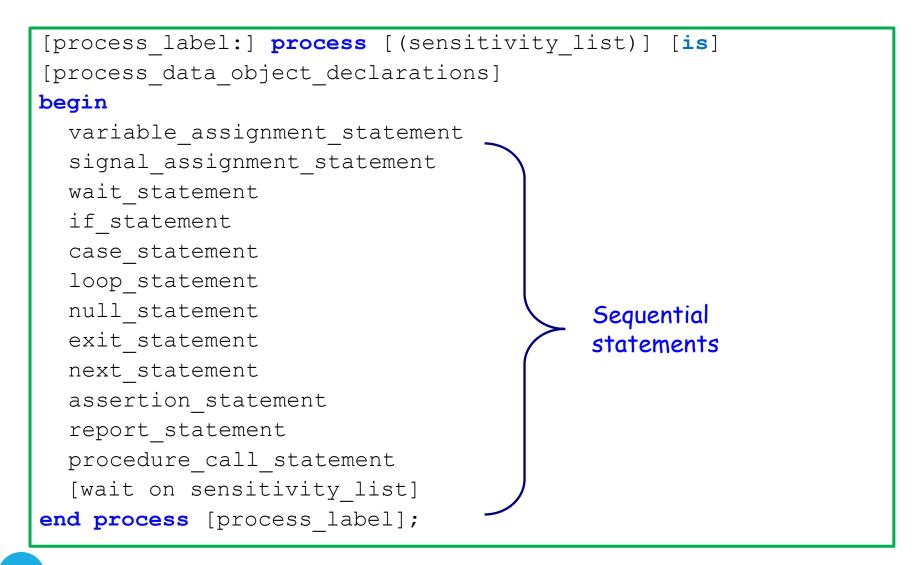

## process Statement Syntax

## Parts of the process statement

#### sensitivity\_list

• List of all the signals that are able to trigger the process

- Simulation tools monitor events on these signals

- Any event on any signal in the sensitivity list will cause to execute the process at least once

#### *declarations*

- Declarative part. Types, functions, procedures and variables can be declared in this part

- Each declaration is local to the process

#### sequential\_statements

All the sequential statements that will be executed each time that the process is activated

## Signal Behaviour in a process

While a process is running ALL the SIGNALS in the system remain unchanged -> Signals are in effect CONSTANTS during process execution, EVEN after a signal assignment, the signal will NOT take a new value

#### SIGNALS are updated at the end of a process

Signals are a mean of communication between processes -> VHDL can be seen as a network of processes intercommunicating via signals

## Variable Behavior in a process

While a process is running ALL the Variables in the system are updates **IMMEDIATELY** by a variable assignment statement

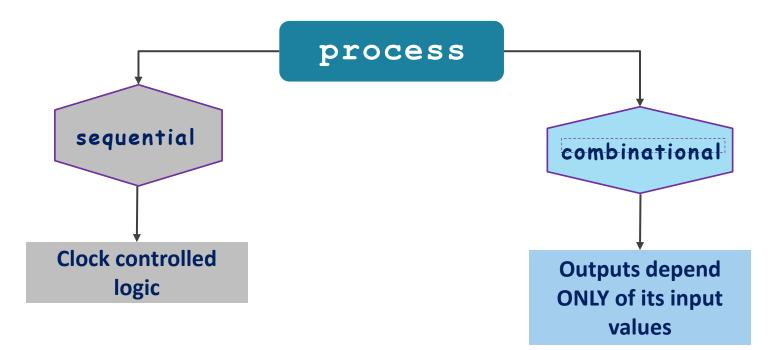

### process - Combinational/Sequential

When using processes, a key distinction is made between those that model sequential logic (controlled by a clock) and those that model combinational logic.

### process - Combinational/Sequential

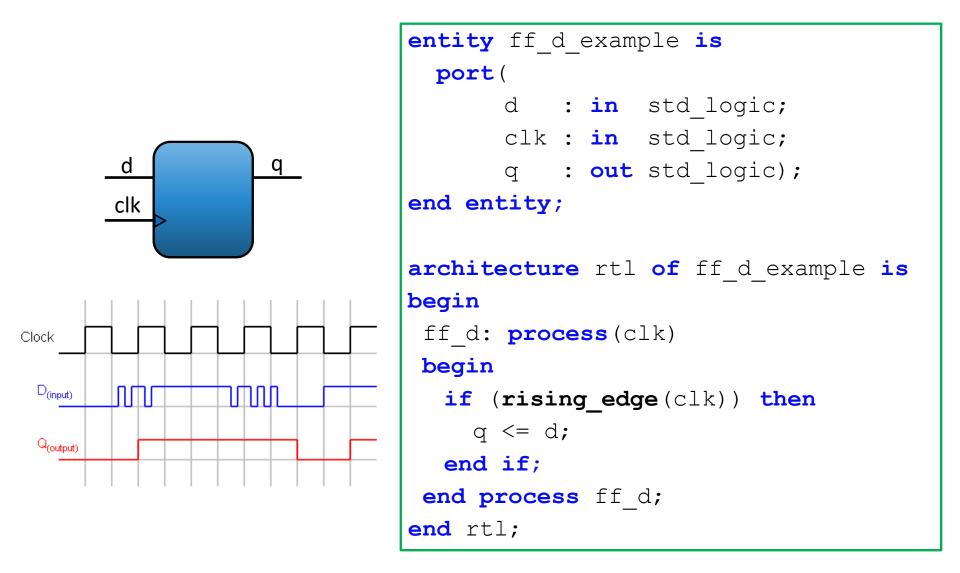

A clock-controlled process, also known as a **sequential process**, describes logic whose outputs change only at specific edges of a clock signal (e.g., rising edge or falling edge). This type of process is used to model sequential elements like flip-flops, registers, counters, and state machines, which have memory and store state.

#### **Key Characteristics:**

• It is **ONLY** sensitive to the **clock signal** and often a **reset signal**.

•It typically contains an IF statement that checks for a clock edge (e.g., rising\_edge(clk) or falling\_edge(clk)).

•Signal assignments inside the clock edge condition are implemented as some storage element (e.g., flip-flop, memory).

### process - Combinational/Sequential

A **combinational process** describes logic whose outputs depend *only* on the current values of its inputs. There is no memory or state involved; if the inputs change, the outputs change (after a propagation delay).

#### **Key Characteristics:**

Its sensitivity list must include all input signals that affect the process's outputs.

If an input changes, the process must re-evaluate to produce the correct output.

It does not contain clock edge detection (rising edge or falling edge).

•Signal assignments are typically **concurrent updates**, as outputs are directly derived from inputs.

•There should be **no unassigned** signals in all possible execution paths within the process; otherwise, the VHDL synthesizer will infer latches, which is generally undesirable for combinational logic. All outputs must be assigned a value for every possible combination of inputs.

## Sequential process example

```

library ieee;

use ieee.std_logic_1164.all;

```

```

entity D_FF is

port (

clk : in std_logic;

reset : in std_logic; -- Asynchronous reset input

D : in std_logic; -- Data input

Q : out std_logic -- Data output

);

end entity D_FF;

```

```

architecture Behavioral of D_FF is begin

```

- -- This process models the behavior of a D-Flip-Flop.

- -- It is a clock-controlled (sequential) process because its state

- -- (the value of Q) only changes on the rising edge of the clock (clk)

-- or asynchronously when reset is high.

process (clk, reset) -- Sensitivity list: Process re-evaluates if clk or reset begin

- -- Asynchronous reset: If reset is '1', Q is immediately set to '0'.

-- This takes precedence over the clock edge.

- if reset = '1' then

Q <= '0';

-- Synchronous operation: If reset is '0', check for a rising clock edge. elsif rising\_edge(clk) then

-- On the rising edge of the clock, the value of D is sampled and -- assigned to Q. This assignment happens after a delta delay.

Q <= D;

```

end if;

```

end process;

#### **Description**:

•The process (clk, reset) line defines the sensitivity list. This means the process will execute whenever there's an event (a change in value) on either the clk or reset signal.

•The **if reset = '1'** condition handles the asynchronous reset. If **reset** is active (high), Q is immediately set to '0'. This happens independently of the clock.

•The **elsif rising\_edge(clk)** condition means that if the reset is not active, the statements within this block will only execute when the clk signal transitions from '0' to '1'.

•Q <= D; inside the rising\_edge block indicates that the output Q will take on the value of the input D at that specific clock edge. This correctly describes the memory element of a Dflip-flop.

## Combinational process example

architecture Behavioral of MUX\_2\_to\_1 is

```

begin

```

library ieee;

```

-- This process models the behavior of a 2-to-1 Multiplexer.

-- It is a combinational process because its output (Y) depends solely

-- on the current values of its inputs (A, B, Sel).

process (A, B, Sel) -- Sensitivity list: Includes ALL inputs that determine Y

begin

-- If Sel is '0', output Y takes the value of A.

if Sel = '0' then

Y <= A;

-- If Sel is '1', output Y takes the value of B.

else -- Sel = '1'

Y <= B;

end if;

end process;

```

end architecture Behavioral;

#### Description

•The process (A, B, Sel) line defines the sensitivity list. The process will execute whenever there's an event on A, B, or Sel. This ensures that Y is always updated whenever any of its inputs change.

•There are no clock edge or reset conditions; the logic simply evaluates based on current inputs.

•The **if Sel = '0'** and **else** branches ensure that the output Y is <u>always</u> assigned a value, regardless of the **Sel** input. This is critical to avoid inferring a latch.

65

## if Statement - 3 to 8 Decoder

a(2:0) ?? b(

```

entity if decoder example is

b(7:0)

port(

a: in std logic vector(2 downto 0);

z: out std logic vector(7 downto 0);

end entity;

architecture rtl of if decoder example is

begin

if dec ex: process (a)

end process if dec ex;

end rtl;

```

## if Statement

Most common mistakes for describing combinatorial logic

```

entity example3 is

port ( a, b, c: in std logic;

z, y: out std logic);

end example3;

architecture beh of example3 is

begin

process (a, b)

begin

if c='1' then

z <= a;

else

y <= b;

end if;

end process;

end beh;

```

### case Statement

```

[case label:]case <selector expression> is

when <choice 1> =>

<sequential statements> -- branch #1

when <choice 2> =>

<sequential statements> -- branch #2

[when <choice n to/downto choice m > =>

<sequential statements>] -- branch #n

. . . .

[when <choice x | choice y | . . .> =>

<sequential statements>] -- branch #...

[when others =>

<sequential statements>]-- last branch

end case [case label];

```

### case Statement

```

entity mux4 is

port ( sel : in std ulogic vector(1 downto 0);

d0, d1, d2, d3 : in std ulogic;

: out std ulogic );

Z

end entity mux4;

architecture demo of mux4 is

begin

out select : process (sel, d0, d1, d2, d3) is

begin

case sel is

when "00" =>

z <= d0;

when "01" =>

z <= d1;

when "10" =>

z <= d2;

when others =>

z <= d3;

end case;

end process out select;

end architecture demo;

```

69

### case Statement with if Statement

```

mux mem bus :process

(cont_out, I_P0, I_P1, I_A0, I_A1, Q_P0, Q_P1, Q_A0, Q_A1)

begin

mux out <= I P0;</pre>

case (cont out) is

when "00" =>

if(iq bus = '0') then

mux out <= I P0;--I A0;</pre>

else

mux out <= Q P0;--Q A0;</pre>

end if;

when "01" =>

if(iq bus = '0') then

mux out <= I A0;--I P0;</pre>

else

mux out <= Q A0;--Q P0;</pre>

end if;

```

. . . . . .

## for loop-end loop Statement

[loop\_label]: for <identifier> in discrete\_range loop

<sequential\_statements>

end loop [loop\_label];

#### <identifier>

- The identifier is called loop parameter, and for each iteration of the loop, it takes on successive values of the discrete range, starting from the left element

- It is not necessary to declare the identifier

- By default the type is integer

- Only exists when the loop is executing

### for-loop Statement

#### for-loop Statement

```

library ieee;

use ieee.std logic 1164.all;

use ieee.numeric std.all;

entity count ??? is

port(vec: in std logic vector(15 downto 0);

count: out std logic vector (3 downto 0))

end count ones;

architecture behavior of count ???? is

begin

cnt ones proc: process(vec)

variable result: unsigned(3 downto 0);

begin

result:= (others =>'0');

for i in vec'range loop

if vec(i)='1' then

result := result + 1;

end if:

end loop;

count <= std logic vector(result);</pre>

end process cnt ones proc;

end behavior;

```

### The Role of Componentes in VHDL

#### **Hierarchy in VHDL**

Divide & Conquer

Each subcomponent can be designed and completely tested

Create library of components (technology independent if possible)

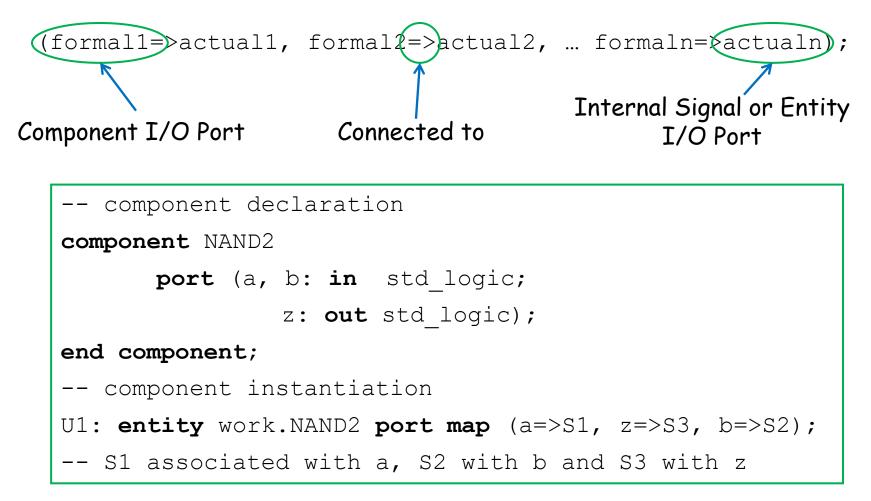

### **Component Instantiation**

Component instantiation is a concurrent statement that is used to connect a component I/Os to the internal signals or to the I/Os of the higher lever component

component\_label: entity work.component\_name

[generic map (generic\_assocation\_list)]

port map (port\_association\_list);

- component\_label it labels the instance by giving a name to the instanced

- generic\_assocation\_list assign new values to the default generic values (given in the entity declaration)

- port\_association\_list associate the signals in the top entity/architecture with the ports of the component. There are two ways of specifying the port map:

- Positional Association / Name Association

### Association By Name

In named association, an association list is of the form

### **Component Instantiation Example**

# VHLD for Sequential Logic Design

### D Flip-Flop - VHDL

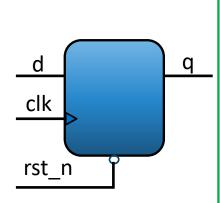

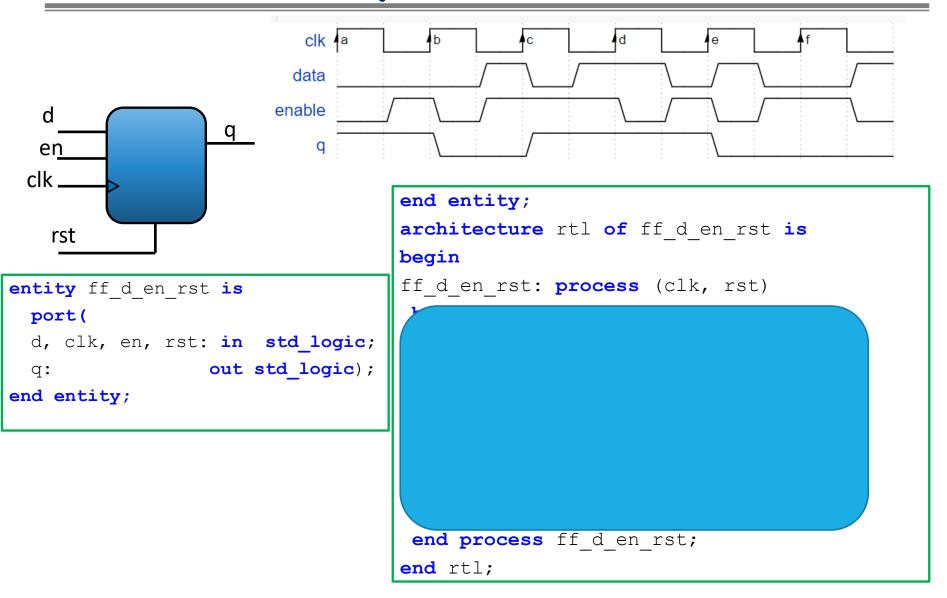

### D-ff with asynchronous reset

entity ff example is port( d, clk, rst n: in std logic; q: out std logic); end entity; architecture rtl of ff example is begin ff d rst: process (clk, rst n) end process ff d rst; end rtl;

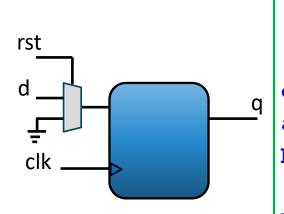

## D-ff with synchronous reset

entity ff d srst is port( d, clk, rst: in std logic; q: out std logic); end entity; architecture rtl of ff d srst is begin ff d srst: process (clk) begin

#### end process ff\_d\_srst;

```

end rtl;

```

### D-ff with async. reset and enable

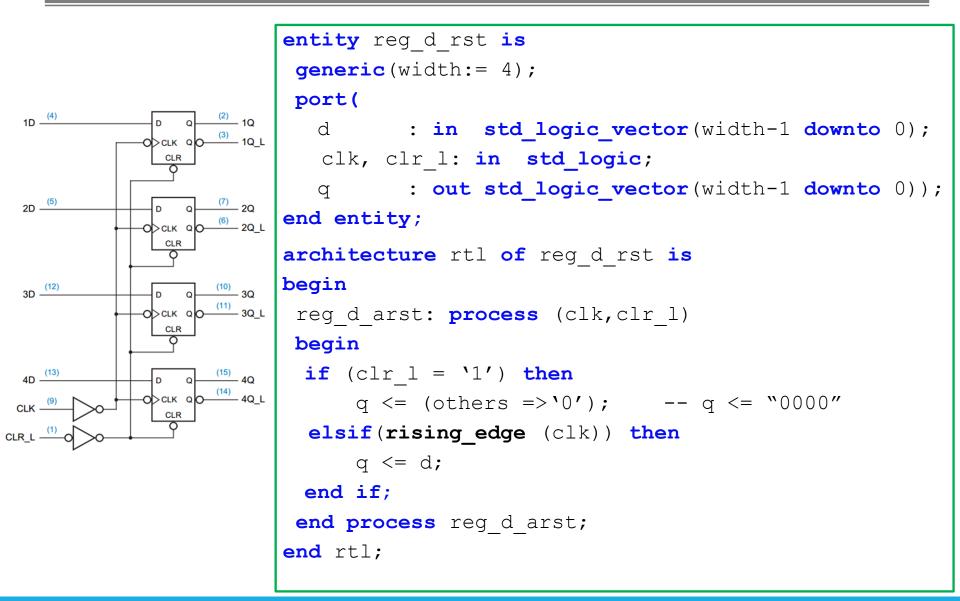

### Registers

### What is the implementation result??

```

library ieee;

use ieee.std logic 1164.all;

entity shift pi po x8 is

port(

clk, clr : in std logic;

serial in : in std logic;

data out : out std logic vector(7 downto 0);

end shift pi po x8;

architecture behav of shift si so x4 is

signal data out temp: std logic vector(3 downto 0);

begin

shift proc: process(clk, clr)

begin

if (clr = '0') then

data out temp <= others(=>'0');

elsif (rising edge(clk)) then

data out temp <= serial in & data out temp(3 downto 1);</pre>

end if;

end process shift proc;

data out <= data out temp;</pre>

end behave;

```

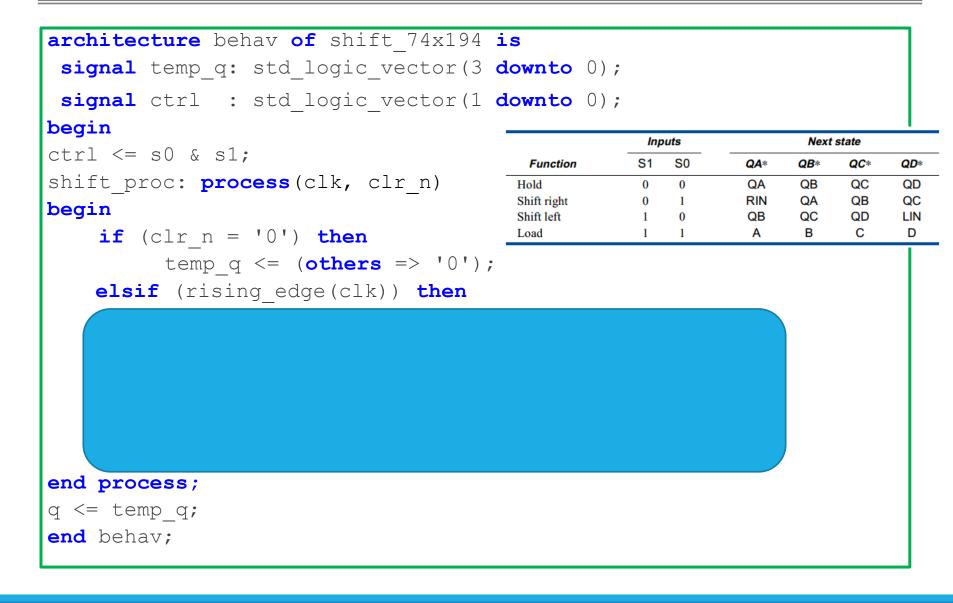

### Shift Register : 74x194

### Counter

| <pre>library ieee; use ieee.std_logic_1164.all; use ieee.numeric_std.all;</pre> |                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <pre>entity counter_nbits is<br/>generic(cnt_w: natural:= 4)<br/>port (</pre>   | <pre>architecture rtl of counter_nbits is<br/> signal declarations<br/>signal count_i: unsigned(cnt_w-1 downto 0);<br/>begin<br/>count_proc: process(clk, rst)<br/>begin<br/>if(rst='0') then<br/>count_i &lt;= (others =&gt; '0');<br/>elsif(rising_edge(clk)) then<br/>count_i &lt;= count_i + 1;<br/>endif;<br/>end process count_proc;<br/>count &lt;= std_logic_vector(count_i);<br/>end architecture rtl;</pre> |

### **Up/Down Counter**

```

library ieee;

use ieee.std logic 1164.all;

use ieee.numeric std.all;

entity counter ud is

generic(cnt w: natural:= 4)

port (

-- clock & reset inputs

clk : in std_logic;

architecture rtl of counter ud is

rst : in std logic;

-- signal declarations

-- control input signals

signal count i: unsigned(cnt w-1 downto 0);

up dw : in std logic;

-- ouptuts

begin

count : out std logic vector (c

count proc: process(clk, rst)

0));

begin

end counter ud;

if(rst='0') then

count i <= (others => '0');

elsif(rising edge(clk)) then

if(up dw = '1') then -- up

count i <= count i + 1;</pre>

-- down

else

count i <= count i - 1;

end if;

end if;

end process count proc;

count <= std logic vector(count i);</pre>

end architecture rtl;

```

## Up/Down Counter - Integers

```

architecture rtl of counter ud i is

begin

count proc: process(clk, rst)

variable count i: integer range 0 to 255;

begin

if(rst n = '0') then

count i := 0;

elsif(rising edge(clk)) then

if (count i = 255) then

count i := 0;

else

count i := count i + 1;

end if:

end if;

end process count proc;

count <= std logic vector(to unsigned(count i, 8));</pre>

end architecture rtl;

```

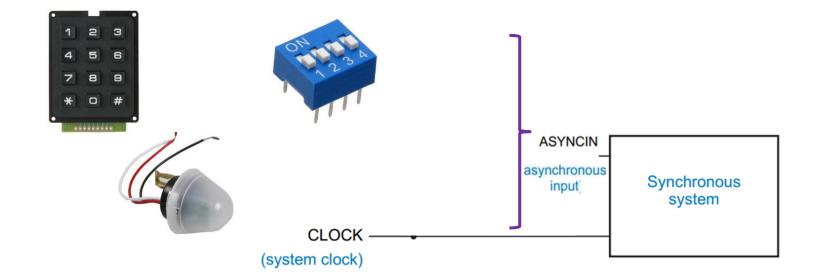

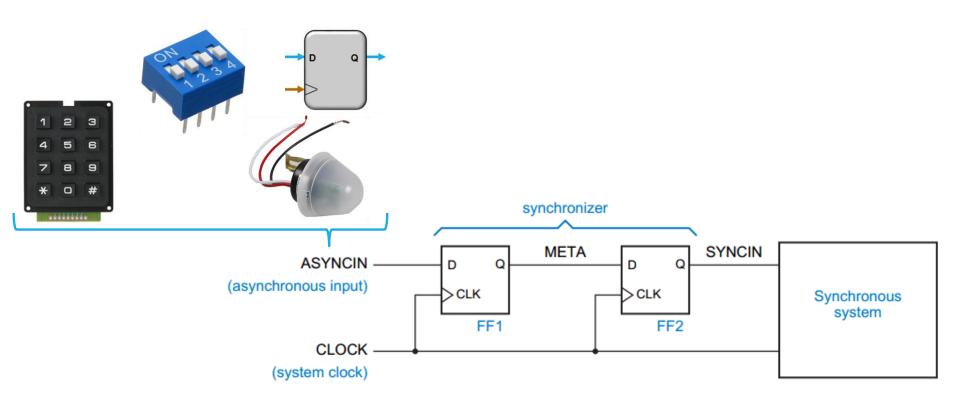

### Asynchronous Inputs

### Synchronizer

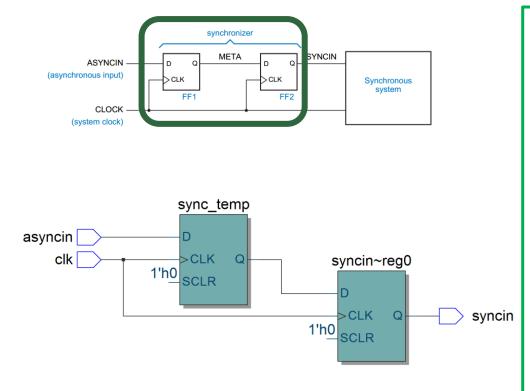

### Synchronizer

```

library ieee;

use ieee.std logic 1164.all;

entity synchronizer is

port(

: in std logic;

clk

asyncin : in std logic;

syncin : out std logic);

end synchronizer;

architecture behave of synchronizer is

signal sync temp: std logic;

begin

sync proc: process(clk)

begin

if (rising edge(clk)) then

sync temp <= asyncin;</pre>

syncin <= sync temp;</pre>

end if;

end process;

end behave;

```

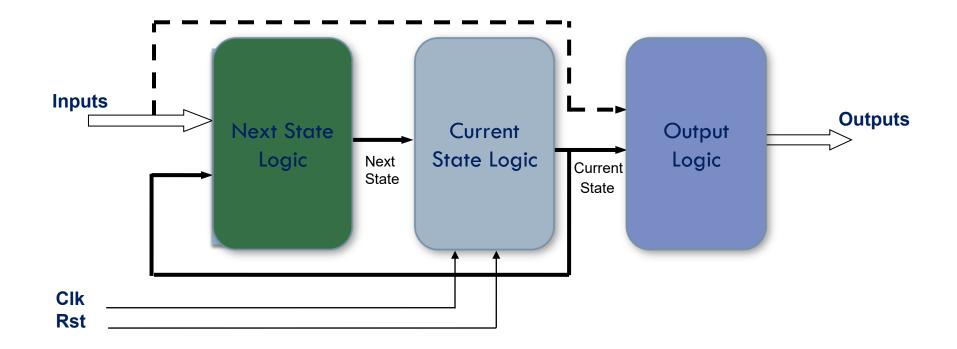

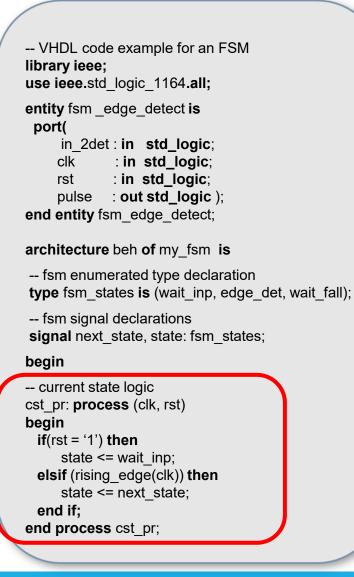

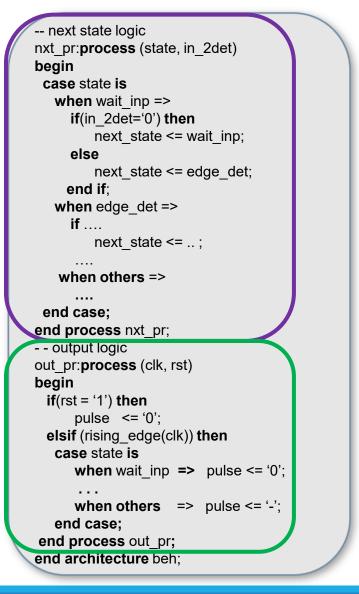

### FINITE STATE MACHINES (FSM) DESCRIPTION IN VHDL

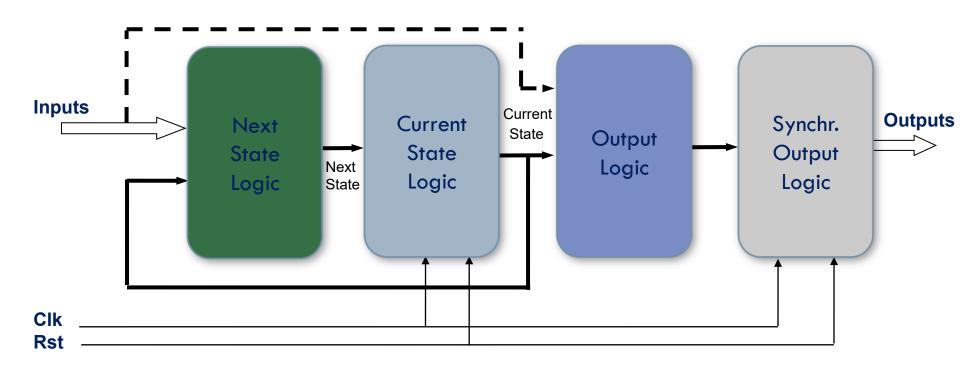

#### State Machine General Scheme 1

#### State Machine General Scheme 2

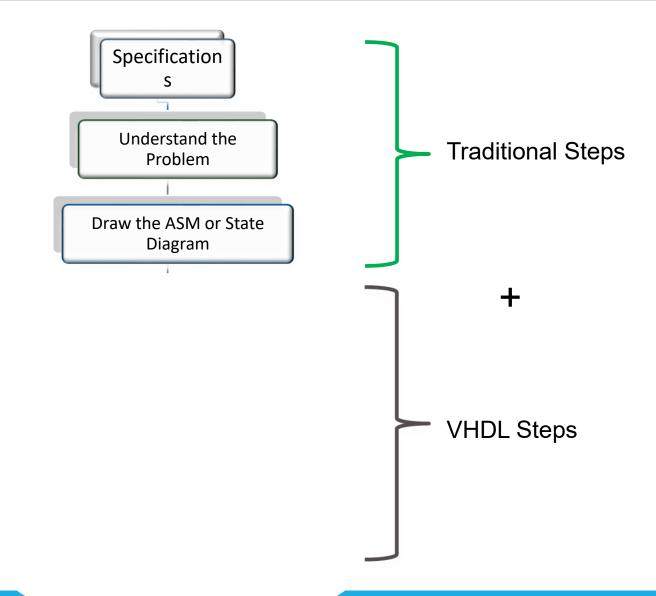

### FSM VHDL General Design Flow

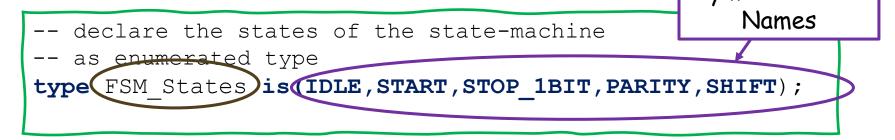

### FSM Enumerated Type Declaration

Declare an enumerated data type with values (names) that symbolize the states of the state machine Symbolic State

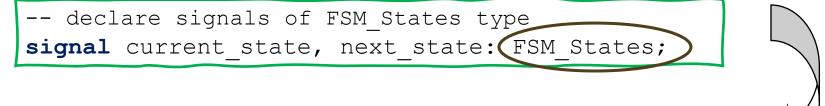

Declare the signals for the next state and current state of the state machine as signal of the enumerated data type already defined for the state machine

The only values that current\_state and next\_state can hold are: // IDLE, START, STOP\_1BIT, PARITY, SHIFT

### FSM Encoding Techniques

#### State Assignment

During synthesis each symbolic state name has to be mapped to a unique binary representation

type FSM\_States is(IDLE, START, STOP\_1BIT, PARITY, SHIFT);

signal current\_state, next\_state: FSM\_States;

- A good state assignment can *reduce* the circuit *size* and *increase* the *clock rate* (by reducing propagation delays)

- The hardware needed for the implementation of the next state logic and the output logic is *directly related* to the state assignment selected

### FSM Encoding Schemes

An FSM with n symbolic states requires at least  $[\log_2 n]$  bits to encode all the possible symbolic values

Commonly used state assignment schemes:

- Binary: assign states according to a binary sequence

- Gray: use the Gray code sequence for assigning states

- One-hot: assigns one 'hot' bit for each state

- Almost one-hot: similar to one-hot but add the all zeros code (initial state)

### FSM Encoding Schemes

|            | Binary | Gray | One-Hot | Almost One-hot |

|------------|--------|------|---------|----------------|

| idle       | 000    | 000  | 00001   | 0000           |

| start      | 001    | 001  | 00010   | 0001           |

| stop_1 bit | 010    | 011  | 00100   | 0010           |

| parity     | 011    | 010  | 01000   | 0100           |

| shift      | 100    | 110  | 10000   | 1000           |

### **Encoding Schemes in VHDL**

#### During synthesis each symbolic state name has to be mapped to a unique binary representation

#### **Results for Different Encoding Schemes**

19 states, state machine

|                                     | One-hot<br>safe | One-hot | Gray   | Gray-Safe | Binary | Johnson |

|-------------------------------------|-----------------|---------|--------|-----------|--------|---------|

| Total<br>combinational<br>functions | 556             | 523     | 569    | 566       | 561    | 573     |

| Dedicated<br>logic registers        | 215             | 215     | 201    | 201       | 201    | 206     |

| Max. frq.                           | 187.3           | 175.22  | 186.39 | 180.6     | 197.63 | 186.22  |

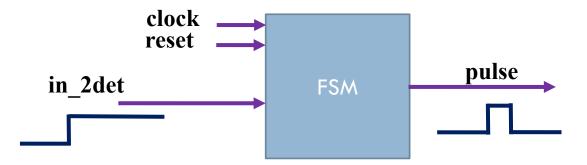

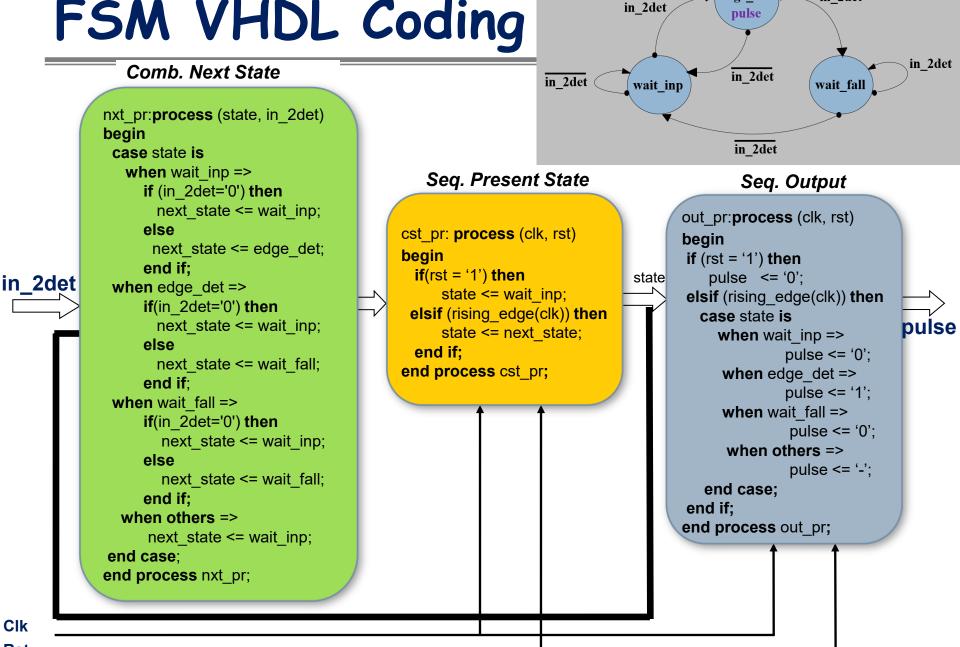

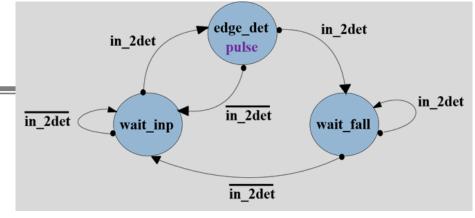

### State Machine VHDL Coding - Example

Describe in VHDL an FSM that generate a pulse per each rising edge of the input.

### FSM VHDL Coding

Clk Rst edge det

in 2det

#### State Machine VHDL Coding (complete)

### **FSM Simulation**

#### 🛛 🖨 🔳 🖉 🖉

<u>File Edit View Add Format Tools Bookmarks Window Help</u>

| <u>File Edit View</u>                | Add Fo      | rmat <u>T</u> o  | oois B   | oo <u>k</u> mark | ks <u>W</u> ine | dow <u>F</u> | leip   |       |          |        |       |               |              |             |    |      |      |         |          |         |            |     |     |      |          |   |

|--------------------------------------|-------------|------------------|----------|------------------|-----------------|--------------|--------|-------|----------|--------|-------|---------------|--------------|-------------|----|------|------|---------|----------|---------|------------|-----|-----|------|----------|---|

| 📰 Wave - Default 🛛                   |             |                  |          |                  |                 |              |        |       |          |        |       |               |              |             |    |      |      |         |          |         |            |     |     |      | * 4      | × |

| ] 🖹 - 📽 🔒 🛸                          | 🖨   🎖       | ( 🖻 🛍            | 20       | ~~   📀           | • 🏟 🗎           | = ] (        | 👂 🖄 i  | 🖞 🛺 🖹 | <b>G</b> | 1 🗭    | ••••• | <b>≧†</b> 1   | 00000 F      | •<br>▼      |    | 1    | 8    |         | <b>1</b> |         | <b>†</b> a | • • |     | - 6  | <b>)</b> |   |

| - <b></b> - 🤧 -                      | i - 🥵       | N Q              | <u>ي</u> | 1 11             | ₽ .             | 발도           | ` →    | `₹₹.  | £ ⊒      | ] 3⊷ • | €-:   | <b>}-</b>   ! | Search:      |             |    |      | ▼ ↓  | (d) (d) | <b>*</b> | ] ⊕     | Q          | ٩   | R R | 8    | ,        |   |

|                                      | l J         |                  |          |                  |                 |              |        |       |          |        |       |               |              |             |    |      |      |         |          |         |            |     |     |      |          |   |

| <b>4</b>                             | Msg         | s                |          |                  |                 |              |        |       |          |        |       |               |              |             |    |      |      |         |          |         |            |     |     |      |          |   |

| ── Clk ^ Rst ──                      | 0<br>0<br>1 |                  |          |                  |                 |              |        |       |          |        |       |               |              |             |    |      |      |         |          |         |            |     |     |      |          |   |

| ◆ pulse<br>→ FSM States —<br>◆ state | 1           |                  | np       |                  |                 |              |        | edge  | det      | wai    | t inp |               |              |             |    | edge | det  |         | , wai    | it_fall |            |     |     |      |          |   |

| nxt_state                            |             | et <u>wait i</u> |          |                  |                 |              |        | wait  |          | Xwait_ | inp   | X             | <u>(ed</u>   | <u>ie_d</u> | et | wait | fall |         |          |         |            |     |     |      |          |   |

| 💼 🎤 😑 Cursor 1                       |             |                  |          |                  |                 | 200          | 000 ps |       |          |        | 40000 |               | ' '<br>83 ps |             |    | 60   | 0000 | ) ps    |          |         | 1          | 1   | 80  | 0000 | ) ps     |   |

| 0 ps to 840 ns                       |             |                  | Outp     | ut Pulse         |                 |              |        |       |          |        |       |               |              |             |    |      |      |         |          |         |            |     |     |      |          | 1 |

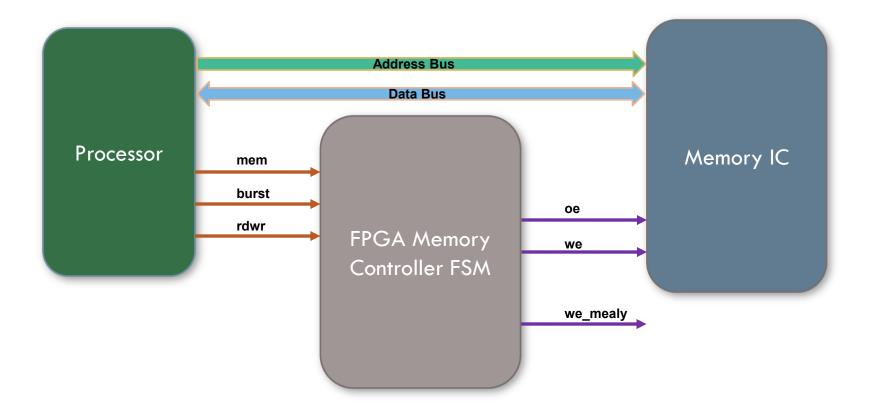

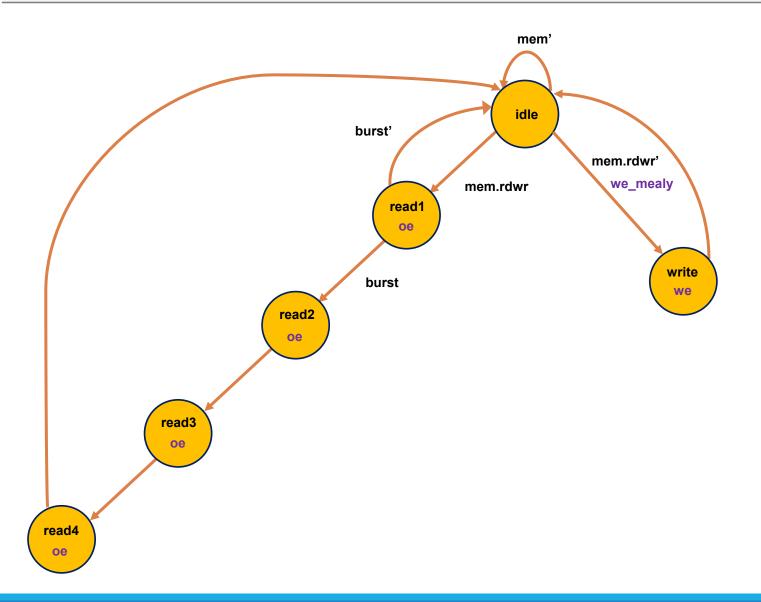

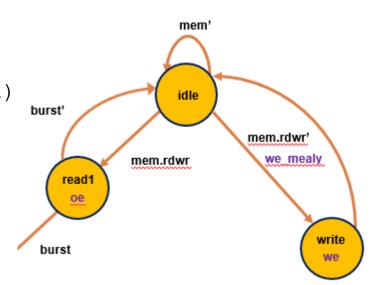

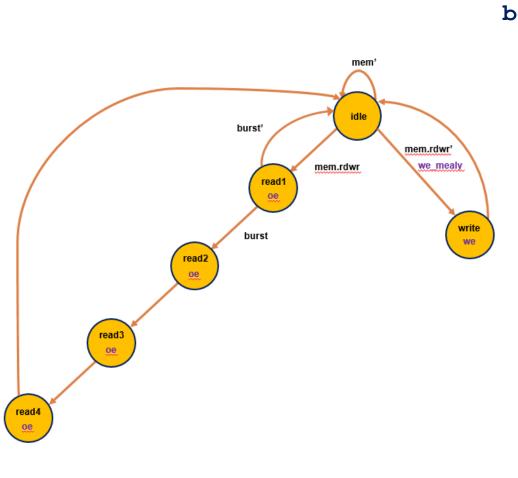

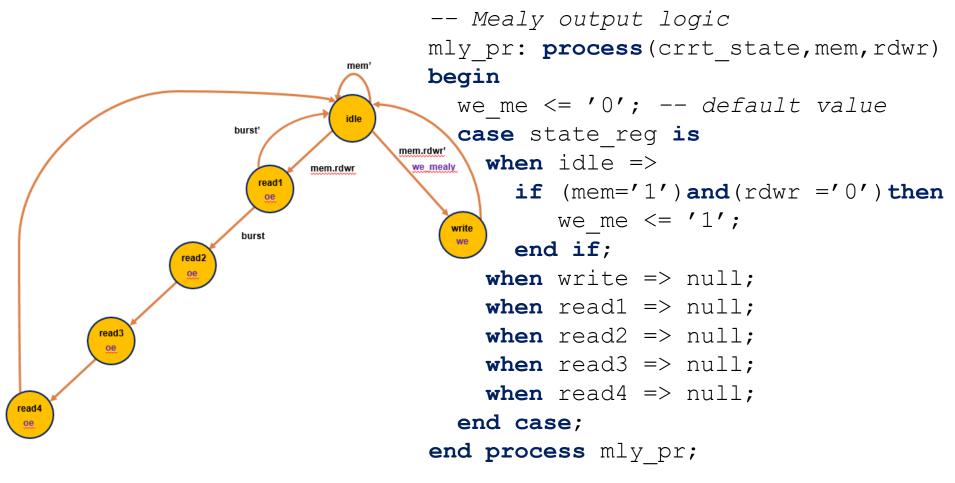

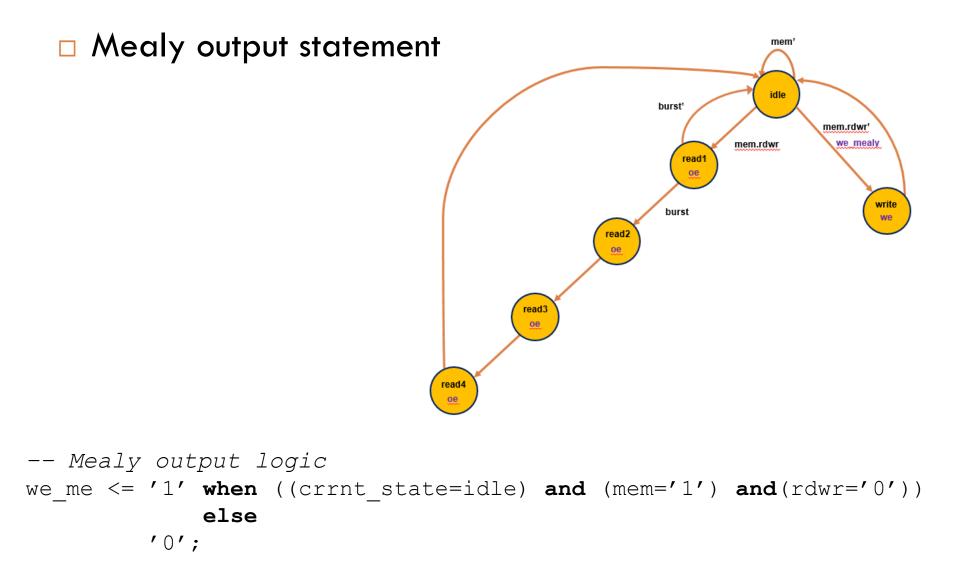

### Another Ex.: Memory Controller FSM

Let's try to obtain an state diagram of a hypothetical memory controller FSM that has the following specifications:

The controller is between a processor and a memory chip, interpreting commands from the processor and then generating a control sequence accordingly. The commands, *mem*, *rw* and **burst**, from the processor constitute the input signals of the FSM. The **mem** signal is asserted to high when a memory access is required. The *rdwr* signal indicates the type of memory access, and its value can be either '1' or '0', for memory read and memory write respectively. The burst signal is for a special mode of a memory read operation. If it is asserted, four consecutive read operations will be performed. The memory chip has two control signals, oe (for output enable) and we (for write enable), which need to be asserted during the memory read and memory write respectively. The two output signals of the FSM, oe and we, are connected to the memory chip's control signals. For comparison purpose, let also add an artificial Mealy output signal, we\_mealy, to the state diagram. Initially, the FSM is in the idle state, waiting for the mem command from the processor. Once *mem* is asserted, the FSM examines the value of *rdwr* and moves to either the *read1* or the *write* state. The input conditions can be formalized to logic expressions, as shown below:

• *mem'* : represents that *n*o memory operation is required (mem='0')

- *mem.rdwr*: represents that a memory read operation is required (mem=rdwr='1').

- *mem.rdwr*': represents that a memory *write* operation is required (mem='1'; rdwr='0')

Based on an example from the "RTL Hardware Design Using VHDL" book, By Pong Chu

### Memory Controller FSM

### Memory Controller FSM

```

library ieee ;

use ieee.std logic 1164.all;

entity mem ctrl is

port (

clk, reset : in std logic;

mem, rdwr, burst: in std logic;

oe, we, we mealy: out std logic

);

end mem ctrl ;

architecture mult seg arch of mem ctrl is

type fsm states type is

(idle, read1, read2, read3, read4, write);

signal crrnt state, next state: fsm states type;

begin

```

```

-- current state process

cs_pr: process (clk, reset)

begin

if(reset = '1') then

crrnt_state <= idle ;

elsif(rising_edge(clk))then

crrnt_state <= next_state;

end if;

end process cs_pr;</pre>

```

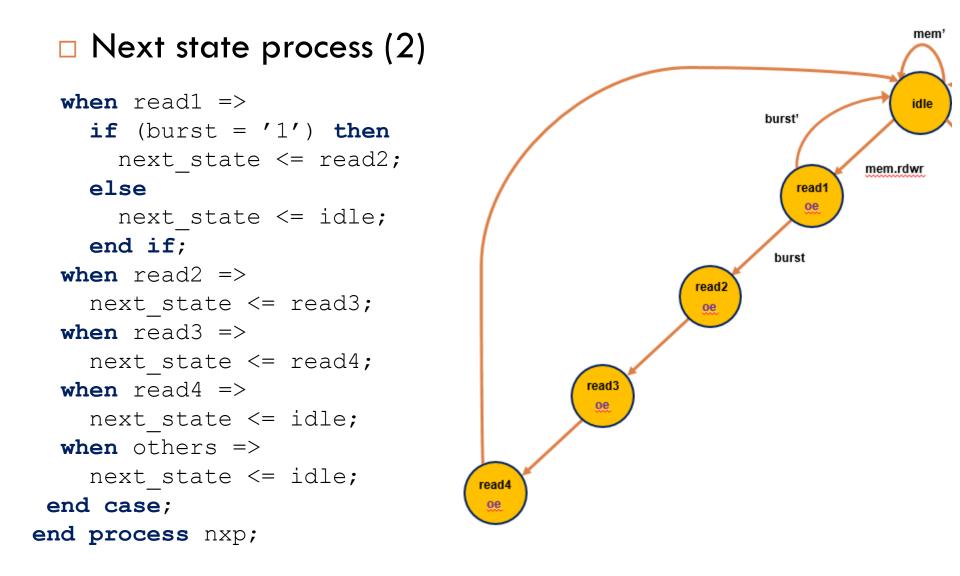

#### Next state process (1)

```

-- next-state logic

nxp:process(crrnt state,mem,rdwr,burst)

begin

case crrnt state is

when idle =>

if mem = '1 ' then

if rdwr = '1' then

next state <= read1;</pre>

else

next state <= write;</pre>

end if;

else

next state <= idle;</pre>

end if;

when write =>

next state <= idle;</pre>

```

Moore outputs process

-- Moore output logic moore\_pr: process (crrnt\_state) begin

we  $\leq 10'$ ; -- default value  $oe \leq '0'; -- default value$ case crrnt state is when idle => null; when write => we <= '1'; **when** read1 => oe <= '1'; when read2 => oe <= '1'; **when** read3 => oe <= '1'; **when** read4 => oe <= '1'; when others => null; end case ; end process moore pr;

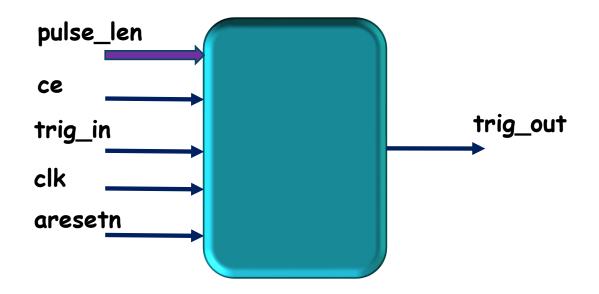

# VHDL Code to be used in the Labs

The purpose of the module **oneShotTimer** is to generate a single output pulse of a predefined duration (**pulse\_len**) every time it receives a rising edge on its **trig\_in** input.

| 27 | entity oneShotTime           | er is                       |                                                                        |

|----|------------------------------|-----------------------------|------------------------------------------------------------------------|

| 28 | Generic <mark>(</mark>       |                             |                                                                        |

| 29 | DATA_BUS_I                   | WIDTH : NATURAL := 16 Cor   | nfigurable width for the pulse_len input                               |

| 30 | );                           |                             |                                                                        |

| 31 | Port <mark>(</mark>          |                             |                                                                        |

| 32 | clk                          | : in std_logic;             | Clock input (for synchronous operations)                               |

| 33 | aresetn                      | : in std_logic;             | Asynchronous active-low reset input                                    |

| 34 | се                           | : in std_logic;             | Clock Enable (not used in the provided code, but declared)             |

| 35 | trig_in                      | : in std_logic;             | Input trigger signal (rising edge detected)                            |

| 36 | pulse_len                    | : in std_logic_vector(DATA_ | _BUS_WIDTH - 1 downto 0); Duration of the output pulse in clock cycles |

| 37 | trig_out                     | : out std_logic             | Output pulse                                                           |

| 38 | );                           |                             |                                                                        |

| 39 | <pre>end oneShotTimer;</pre> |                             |                                                                        |

#### •generic(DATA\_BUS\_WIDTH : NATURAL := 16):

•generic is a way to pass constant values into an entity from its instantiation.

•DATA\_BUS\_WIDTH defines the bit width of the **pulse\_len** input. It defaults to 16 bits, meaning **pulse\_len** can specify a pulse length from 0 to 65535 clock cycles.

•Port (...): Defines the input and output signals of the block:

•clk: Standard clock input. All internal state changes occur on its rising edge.

•aresetn: Asynchronous active-low reset. When aresetn is '0', the timer is reset.

•ce: Clock Enable. Note: This port is declared but not used yet.

•trig\_in: The input signal that, upon a rising edge, initiates the one-shot pulse.

•pulse\_len: An input vector that defines the desired duration of the output pulse in terms of clock cycles.

•trig\_out: The output signal that generates a pulse (goes high) for the specified pulse\_len duration.

| 41 | architecture Behavioral of oneShotTimer is                                |

|----|---------------------------------------------------------------------------|

| 42 |                                                                           |

| 43 | Internal signal to store the previous state of trig_in for edge detection |

| 44 | signal lastTrig_in : std_logic;                                           |

| 45 | Internal counter to track the pulse duration                              |

| 46 | signal counter : integer range 0 to 2**DATA_BUS_WIDTH - 1;                |

| 47 |                                                                           |

| 48 | begin                                                                     |

•architecture Behavioral of oneShotTimer is: Defines the behavior or implementation of the oneShotTimer entity.

#### •signal lastTrig\_in : std\_logic;

•Declares an internal signal named lastTrig\_in.

•This signal is crucial for **rising edge detection** of **trig\_in**. It will store the value of **trig\_in** from the *previous* clock cycle.

#### •signal counter : integer range 0 to 2\*\*DATA\_BUS\_WIDTH - 1;

•Declares an internal signal named **counter**.

•It's declared as an INTEGER with a specified range, from 0 up to the maximum value that can be represented by DATA\_BUS\_WIDTH bits (e.g., if DATA\_BUS\_WIDTH is 16, the range is 0 to 65535). This counter tracks the duration of the output pulse.

| 50 | process(clk, aresetn)                                                          |

|----|--------------------------------------------------------------------------------|

| 51 | begin                                                                          |

| 52 | Asynchronous Reset                                                             |

| 53 | if aresetn = '0' then                                                          |

| 54 | <b>lastTrig_in &lt;= '0';</b> Reset lastTrig_in to '0'                         |

| 55 | <pre>counter &lt;= 0; Reset counter to 0 (trig_out will be '0')</pre>          |

| 56 | Synchronous operations on rising edge of clock                                 |

| 57 | <pre>elsif rising_edge(clk) then</pre>                                         |

| 58 | Store current trig_in to lastTrig_in for the next clock cycle's edge detection |

| 59 | <b>lastTrig_in &lt;= trig_in;</b> This creates a 1-cycle delay for trig_in     |

•process(clk, aresetn): This is a sequential (clock-controlled) process.

•It's sensitive to **clk** and **aresetn**. This means the code inside the process will execute whenever **clk** or **aresetn** changes value.

•if aresetn = '0' then ...: This handles the asynchronous reset. If aresetn goes low, both lastTrig\_in and counter are immediately forced to '0'. This initializes the timer to an inactive state.

•elsif rising\_edge(clk) then ...: This block executes only on the rising edge of the clock, after checking the reset condition. All the logic inside this elsif is synchronous.

•lastTrig\_in <= trig\_in; On each rising clock edge, the current value of trig\_in is stored into lastTrig\_in. This is the standard way to create a one-clock-cycle delayed version of a signal for edge detection.

| 60   |                                                                                                    |

|------|----------------------------------------------------------------------------------------------------|

| 61   | Check for a rising edge on trig_in (current trig_in is '1' and lastTrig_in was '0')                |

| 62 🗸 | <pre>if(lastTrig_in = '0' and trig_in = '1') then Trigger condition met</pre>                      |

| 63   | <b>counter &lt;= 1;</b> Start the counter from 1 (the pulse length is counted from 1 to pulse_len) |

| 64   | If the counter is still running (not zero and less than the target pulse_len)                      |

| 65 🗸 | elsif((counter < to_integer(unsigned(pulse_len))) and (counter /= 0)) then                         |

| 66   | <pre>counter &lt;= counter + 1; Increment the counter</pre>                                        |

| 67   | If the counter has reached or exceeded pulse_len, or if it's already zero (not active)             |

| 68 🗸 | else                                                                                               |

| 69   | counter <= 0; Reset counter to 0, ending the pulse                                                 |

| 70   | end if;                                                                                            |

| 71   |                                                                                                    |

| 72   | end if;                                                                                            |

| 73 e | end process;                                                                                       |

•if(lastTrig\_in = '0' and trig\_in = '1') then -- Trigger condition:

•This is the **rising edge detection** logic. It checks if **trig\_in** was '0' in the *previous* clock cycle (**lastTrig\_in**) and is '1' in the *current* clock cycle (**trig\_in**).

• If a rising edge is detected, **counter <= 1**; initializes the counter. This makes the **trig\_out** go high starting from the next clock cycle (because trig\_out is 1 when counter /= 0).

elsif((counter < to\_integer(unsigned(pulse\_len))) and (counter /= 0)) then: The counting phase.</li>

to\_integer(unsigned(pulse\_len)): Converts the STD\_LOGIC\_VECTOR pulse\_len into an INTEGER so it can be compared with counter. unsigned() treats the vector as an unsigned number.

counter < ...: Checks if the counter has not yet reached the desired pulse length.</li>

•counter /= 0: Ensures that the counter is actually active (has been triggered).

If both conditions are true, counter <= counter + 1; increments the counter, continuing the pulse.</li>

else counter <= 0;: This is the default case.</li>

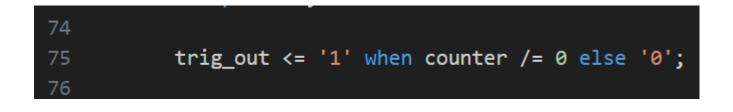

•This is a **concurrent signal assignment statement**. It is outside the process block, meaning it's continuously evaluated.

#### •trig\_out <= '1' when counter /= 0 else '0';</pre>

- •The **trig\_out** signal will be '1' whenever the counter is *not equal to* 0.

- •Otherwise (when counter is 0), trig\_out will be '0'.

- •This effectively means that **trig\_out** is high for the duration that counter is counting (from 1 up to **pulse\_len**), and low when the timer is idle or reset.

How it Works Together:

- 1. Idle State: counter is 0, trig\_out is '0'.

- 2. Trigger: A rising edge on trig\_in is detected.

- **3. Start Pulse:** On the next rising **clk** edge after the **trigger**, **counter** is set to 1. **trig\_out** immediately becomes '1'.

- **4.** Pulse Duration: For subsequent clock cycles, if counter is less than pulse\_len and not 0, counter increments. **trig\_out** remains '1'.

- 5. Pulse End: When counter becomes equal to pulse\_len (meaning pulse\_len clock cycles have passed since the trigger), in the *next* clock cycle, the elsif condition (counter < to\_integer(unsigned(pulse\_len))) becomes false. The else branch executes, resetting counter to 0.</p>

- 6. Output Low: As counter becomes 0, trig\_out immediately reverts to '0', ending the pulse.

- Reset: If aresetn goes low at any point, counter and lastTrig\_in are reset to 0, forcing trig\_out to '0' and stopping any ongoing pulse.

This design creates a reliable, retriggerable one-shot timer with a configurable pulse length, synchronized to the system clock.

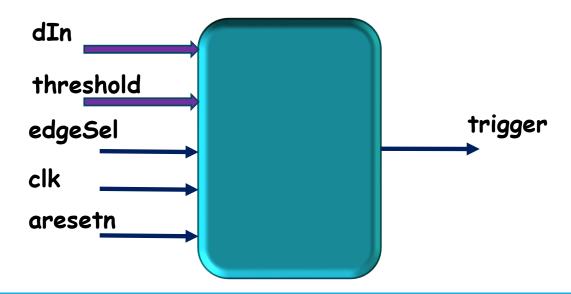

Its purpose is to detect when an input data value, **dln**, crosses a specified **threshold** value, specifically looking for either a positive-going (rising) edge crossing or a negative-going (falling) edge crossing, depending on the **edgeSel** input.

The output, **trigger**, will be set to '1' during one clock cycle whenever a trigger event is detected

| 28 | entity crossLevelTriggerBlock is                                                     |

|----|--------------------------------------------------------------------------------------|

| 29 | Generic <mark>(</mark>                                                               |

| 30 | DATA_BUS_WIDTH : NATURAL := 14 Configurable width for data and threshold             |

| 31 | );                                                                                   |

| 32 | Port (                                                                               |

| 33 | <pre>clk : in STD_LOGIC; Clock input (for synchronous operations)</pre>              |

| 34 | <pre>aresetn : in STD_LOGIC; Asynchronous active-low reset input</pre>               |

| 35 | dIn : in STD_LOGIC_VECTOR (DATA_BUS_WIDTH - 1 downto 0); Input data                  |

| 36 | threshold : in STD_LOGIC_VECTOR (DATA_BUS_WIDTH - 1 downto 0); Threshold value       |

| 37 | edgeSel : in STD_LOGIC; Edge selection: '0' for Positive Edge, '1' for Negative Edge |

| 38 | trigger : out STD_LOGIC Output: '1' when a trigger condition is met, '0' otherwise   |

| 39 | );                                                                                   |

| 40 | end crossLevelTriggerBlock:                                                          |

- generic(DATA\_BUS\_WIDTH : NATURAL := 14):

- ✓ Generic is a way to pass constant values into an entity from its instantiation.

- DATA\_BUS\_WIDTH is a generic parameter defining the width of the **dln** and threshold buses. It's set to a

default value of 14 bits. This makes the design <u>reusable for different data widths without modifying the core code</u>.

- Port (...): Defines the input and output signals of the block:

- clk: Standard clock input. All internal state changes will occur on its edge.

- **aresetn**: Asynchronous active-low reset. When aresetn is '0', the circuit is reset. The n suffix typically indicates active-low.

- ✓ **dIn**: Input data bus, DATA\_BUS\_WIDTH bits wide.

- ✓ **threshold**: Reference value for comparison, DATA\_BUS\_WIDTH bits wide.

- edgeSel: A single bit to select the type of trigger: '0' for positive-going edge (crossing threshold from below), '1' for negative-going edge (crossing threshold from above).

- trigger: A single-bit output that goes '1' when a trigger condition is detected.

| 42 | architecture Behavioral of crossLevelTriggerBlock is                       |

|----|----------------------------------------------------------------------------|

| 43 | declare an internal signal to store the previous value of dIn              |

| 44 | <pre>signal lastVal : std_logic_vector(DATA_BUS_WIDTH - 1 downto 0);</pre> |

| 45 | begin                                                                      |

•architecture Behavioral of crossLevelTriggerBlock is: Defines the behavior or implementation of the crossLevelTriggerBlock entity.

•signal lastVal : std\_logic\_vector(DATA\_BUS\_WIDTH - 1 downto 0);

• Declares an internal signal named last **lastVal**.

- •lastVal is a STD\_LOGIC\_VECTOR of the same width as dln and threshold.

- •This signal is crucial for detecting *edge* crossings: it stores the value of **dln** from the *previous* clock cycle.

```

process(clk, aresetn)

begin

-- Asynchronous Reset

if (aresetn = '0') then

trigger <= '0'; -- Reset trigger output to '0'

-- Synchronous operations on rising edge of clock

52

elsif (rising_edge(clk)) then

-- Store current dIn to lastVal for the next clock cycle's comparison

lastVal <= dIn;</pre>

-- Positive slope cross-level trigger

if (edgeSel = '0') then

-- Condition for positive edge crossing:

-- Previous value was BELOW threshold AND Current value is AT or ABOVE threshold

if (unsigned(lastVal) < unsigned(threshold) and unsigned(dIn) >= unsigned(threshold)) then

trigger <= '1'; -- Activate trigger</pre>

else

trigger <= '0'; -- Deactivate trigger</pre>

64

end if:

-- Negative slope cross-level trigger

-- Condition for negative edge crossing:

-- Previous value was ABOVE threshold AND Current value is AT or BELOW threshold

if (unsigned(lastVal) > unsigned(threshold) and unsigned(dIn) <= unsigned(threshold)) then

trigger <= '1'; -- Activate trigger</pre>

else

trigger <= '0'; -- Deactivate trigger</pre>

end if:

74

end if:

end if;

75

end process;

```

| 47 | process(clk, aresetn)                                              |

|----|--------------------------------------------------------------------|

| 48 | begin                                                              |

| 49 | Asynchronous Reset                                                 |

| 50 | if (aresetn = '0') then                                            |

| 51 | trigger <= '0'; Reset trigger output to '0'                        |

| 52 | Synchronous operations on rising edge of clock                     |

| 53 | <pre>elsif (rising_edge(clk)) then</pre>                           |

| 54 | Store current dIn to lastVal for the next clock cycle's comparison |

| 55 | lastVal <= dIn;                                                    |

•process(clk, aresetn): This is a sequential (clock-controlled) process.

•It's sensitive to **clk** and **aresetn**. This means the code inside the process will execute whenever **clk** or **aresetn** changes value (aka, an event on one of those signals).

•if (aresetn = '0') then trigger <= '0'; This handles the asynchronous reset. If aresetn goes low, the output trigger is immediately forced to '0', <u>regardless of the clock</u>. This is common for initial circuit states.

•elsif (rising\_edge(clk)) then: This block executes only on the rising edge of the clock, after checking the reset condition. All the logic inside this elsif is synchronous.

•lastVal <= dln;</pre>

•This is a synchronous assignment. On each rising clock edge, the current value of **dln** is stored into **lastVal**.

•This means **lastVal** will always hold the value of **dIn** from the *previous* clock cycle, allowing for edge detection.

| 56 | Positive slope cross-level trigger                                                                          |

|----|-------------------------------------------------------------------------------------------------------------|

| 57 | if (edgeSel = '0') then                                                                                     |

| 58 | Condition for positive edge crossing:                                                                       |

| 59 | Previous value was BELOW threshold AND Current value is AT or ABOVE threshold                               |

| 60 | <pre>if (unsigned(lastVal) &lt; unsigned(threshold) and unsigned(dIn) &gt;= unsigned(threshold)) then</pre> |

| 61 | trigger <= '1'; Activate trigger                                                                            |

| 62 | else                                                                                                        |

| 63 | trigger <= '0'; Deactivate trigger                                                                          |

| 64 | end if;                                                                                                     |

**if (edgeSel = '0') then** -- Positive slope cross-level trigger:

• If **edgeSel** is '0', the block is configured to detect a positive-going (rising) edge crossing.

if (unsigned(lastVal) < unsigned(threshold) and unsigned(dln) >= unsigned(threshold))

then: This is the core detection logic for a positive edge.

•unsigned(): cast that converts STD\_LOGIC\_VECTOR signals to UNSIGNED type for *numerical comparison*.

•The condition checks if the *previous* data value (**lastVal**) was strictly **less than** the **threshold**, **AND** the *current* data value (dln) is greater than or equal to the **threshold**. This accurately defines a *positive cross-level event*.

•If this condition is met, **trigger** is set to '**1**'.

•else trigger <= '0'; Otherwise, trigger is '0'. This ensures trigger is only '1' for one clock cycle when the condition is met.

| 65 | Negative slope cross-level trigger                                                         |

|----|--------------------------------------------------------------------------------------------|

| 66 | else edgeSel = '1'                                                                         |

| 67 | Condition for negative edge crossing:                                                      |

| 68 | Previous value was ABOVE threshold AND Current value is AT or BELOW threshold              |

| 69 | if (unsigned(lastVal) > unsigned(threshold) and unsigned(dIn) <= unsigned(threshold)) then |

| 70 | trigger <= '1'; Activate trigger                                                           |

| 71 | else                                                                                       |

| 72 | trigger <= '0'; Deactivate trigger                                                         |

| 73 | end if;                                                                                    |

| 74 | end if;                                                                                    |

| 75 | end if;                                                                                    |

| 76 | end process;                                                                               |

|    |                                                                                            |

else -- Negative slope cross-level trigger (edgeSel = '1'):

• If edgeSel is '1', the block is configured to detect a negative-going (falling) edge crossing.

•if (unsigned(lastVal) > unsigned(threshold) and unsigned(dln) <= unsigned(threshold)) then: This is the core detection logic for a negative edge.

•The condition checks if the *previous* data value (**lastVal**) was strictly **greater than** the **threshold**, AND the *current* data value (**din**) is **less than or equal to** the **threshold**. This defines a negative cross-level event.

- •If this condition is met, trigger is set to '1'.

- •else trigger <= '0';: Otherwise, **trigger** is '**0**'.

#### In Summary:

This **crossLevelTriggerBlock** VHDL design acts as a programmable level-crossing detector:

- 1. It stores the previous sample of the input data (**dIn**) in **lastVal** synchronously on each clock edge.

- 2. On *each clock edge*, it compares the current **dln** and the previous **lastVal** against a **threshold**.

- 3. Based on the **edgeSel** input, it determines if a positive-going or negative-going level crossing has occurred.

- 4. If a crossing is detected, the **trigger** output goes *high for one clock cycle*.

- 5. It also includes an asynchronous active-low reset to initialize the trigger output to '0'.

This type of module is common in digital signal processing or control systems where events need to be detected based on signal levels crossing certain thresholds