## Intelligent FPGA-based Data Acquisition System

#### Igor Konorov

Institute for Hadronic Structure and Fundamental Symmetries (E18)

TUM Department of Physics

Technical University of Munich

Advanced Workshop on FPGA based System-on-Chip for Scientific Instrumentation and Reconfigurable Computing ICTP Trieste

## **DAQ Elements**

□ Front-end electronics, detector specific

- Conversion of detector analog signal to digital form

- Derandomization

- Data processing: signal detection, extraction of signals' parameters Time and/or Amp...

- □ Trigger Logic

- reduce amount of stored data

- define time when something interesting happen

- □ Trigger Distribution system => Time Distribution System

- Slow Control System

- Control and monitoring of PS, Gas system, Temperature, Humidity,...

- Programming of Front-ends

- □ Acquisition System => Event builder

- Data acquisition moving data from FE to PCs

- Data flow control

- Real time Software

- Run control

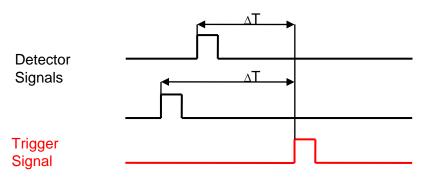

## Few words about time measurements

Classical method:

- TRIGGER is a reference

- SIGNAL time is measured respectively to TRIGGER signal

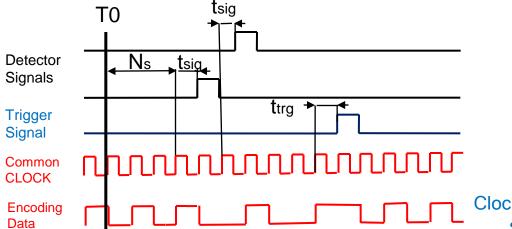

### Alternative method for big experiments:

- Distribute CLOCK , why clock?

- Easier to distribute with very low jitter

- Measure absolute time respectively to CLOCK phase

Tsig = Ns Tclk+ tsig Ttrg = Nt Tclk+ ttrg

Clock and Data are encoded and transmitted from single source to multiple destinations

### NA48, LHC->TTC, COMPASS->TCS

## Л

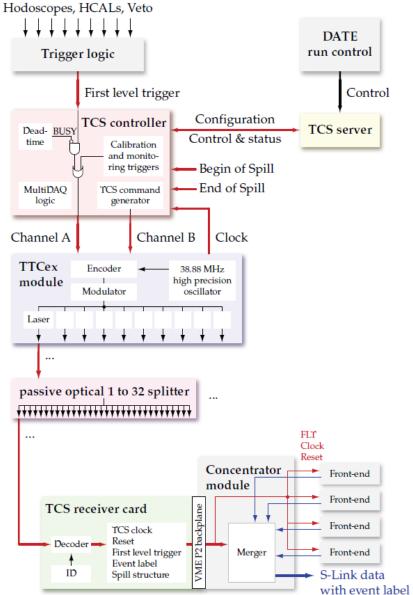

# Time Distribution System

Trigger Control System

Features:

- Optical network

- Star-like topology with single source and multiple destinations

- Active fan out 1:16

- Passive fan out using optical splitters 1:32

- Unidirectional transmission

- Speed 155 Mbaud

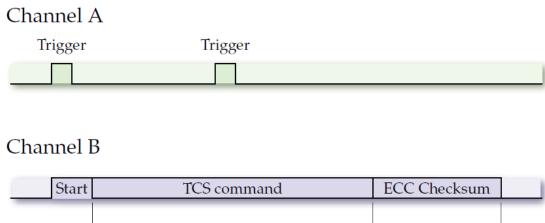

- Two independent channels A and B

- A-trigger

- B commands and trigger Number

- TCS controller and TCS receiver are implemented in FPGA

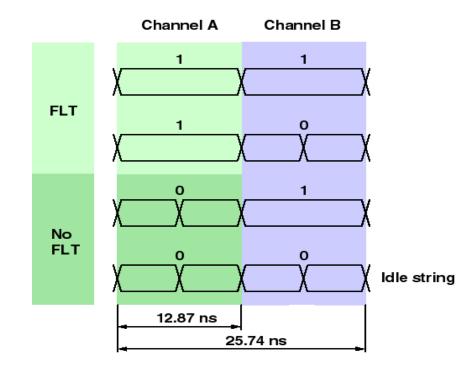

# Encoding

## **Biphase mark and Time-Division-Multiplexed encoding**

- 155.52 Mbaud link speed

- 77.76 Mb/sec can be used

- 2 independent channels

- speed of one channel 38.88 Mb/sec

- channel A for FLT(first level trigger)

- channel B for data

# **Command Format**

| Start | TCS command | ECC Checksum |

|-------|-------------|--------------|

|       | 20 bits     | 6 bits       |

**Broadcast command:**

- reset, beginning of spill, end of spill

- event number , spill number, trigger type

- pre trigger command for calibration/monitoring trigger

**Addressed command:**

- enabling/disabling TCS receivers

- configuration of TCS receiver

Instrumentation

## ТЛП

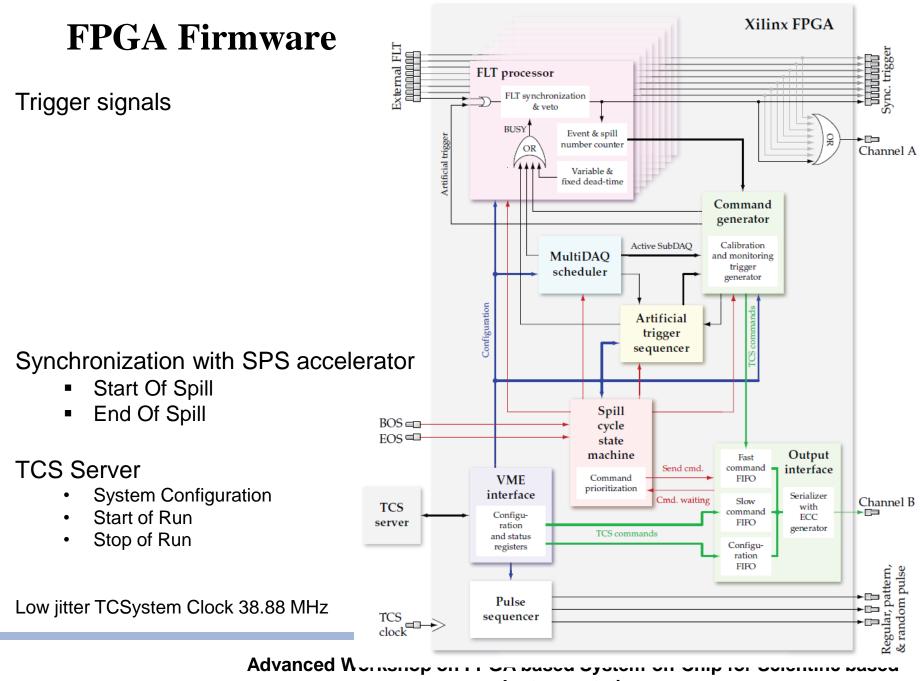

## **TCS** Controller

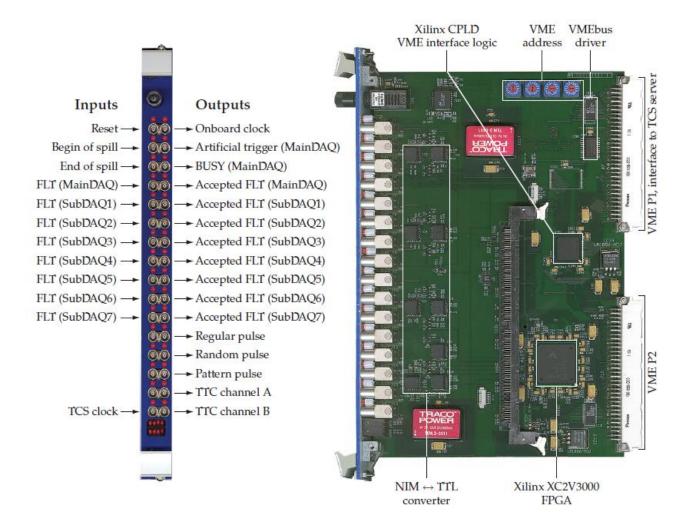

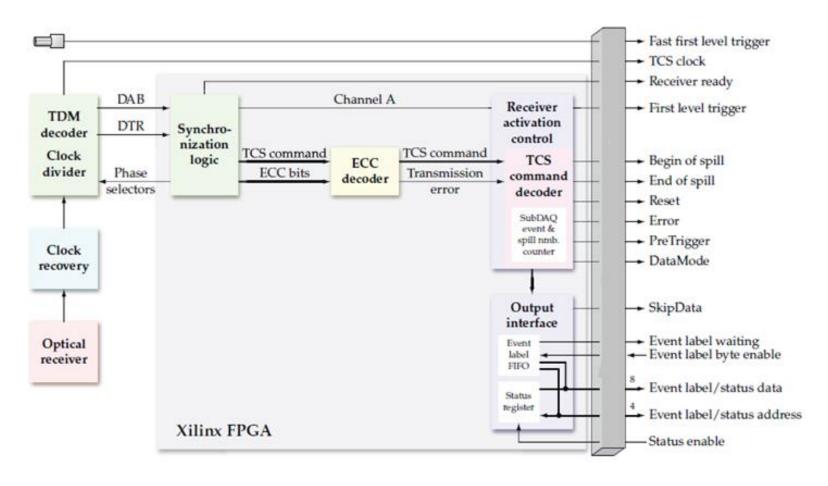

## **TCS** Receiver

## **EVENT BUILDING**

## **Readout Links of LHC Experiments**

|             | SLINK                | Optical: 160 MB/s ≈ 1600 Links<br>Receiver card interfaces to PC.                                                                                              | Flow Control<br>Yes |

|-------------|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|

|             | SLINK 64             | LVDS: 400 MB/s (max. 15m) ≈ 500 links<br>(FE on average: 200 MB/s to readout buffer)<br>Receiver card interfaces to commercial NIC (Network<br>Interface Card) | yes                 |

|             | DDL                  | Optical 200 MB/s ≈ 500 links<br>Half duplex: Controls FE (commands,<br>Pedestals,Calibration data)<br>Receiver card interfaces to PC                           | yes                 |

|             | TELL-1<br>& GbE Link | Copper quad GbE Link ≈ 400 links<br>Protocol: IPv4 (direct connection to GbE switch)<br>Forms "Multi Event Fragments"<br>Implements readout buffer             | no                  |

| Ch. Schwick |                      | CERN / CMS / CMD                                                                                                                                               | 12                  |

## LHC experiments, Run1

Slide from ISOTDAQ

**High Level Trigger**

| ATLAS | No.Levels | <b>Lvl 0,1,2</b><br>Rate (Hz)     | Event<br>Size (Byte) | Evt Build.<br>Bandw.(GB/s) | HLT Out<br>MB/s (Event/s)             |

|-------|-----------|-----------------------------------|----------------------|----------------------------|---------------------------------------|

|       | 3         | LV-1 105<br>LV-2 3x103            | 1.5 MB               | 4.5                        | <b>300</b> (200)                      |

| CMS   |           | LV-1 <b>105</b><br>Pb-Pb 1500MB/s | 1.0 MB               | 100                        | <b>300</b> (200)                      |

| LHCb  | 2         | LV-0 <b>106</b>                   | 30 kB                | 30                         | 60 (2 kHz)                            |

| ALICE |           | <sub>РЬ-РЬ</sub> 500<br>р-р 103   | 70 MB<br>2 MB        | 25                         | <b>1250</b> (100)<br><b>200</b> (100) |

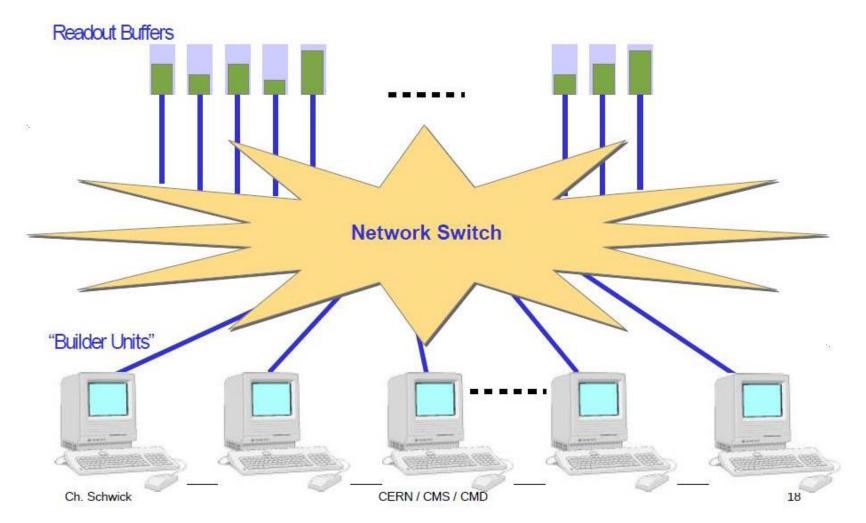

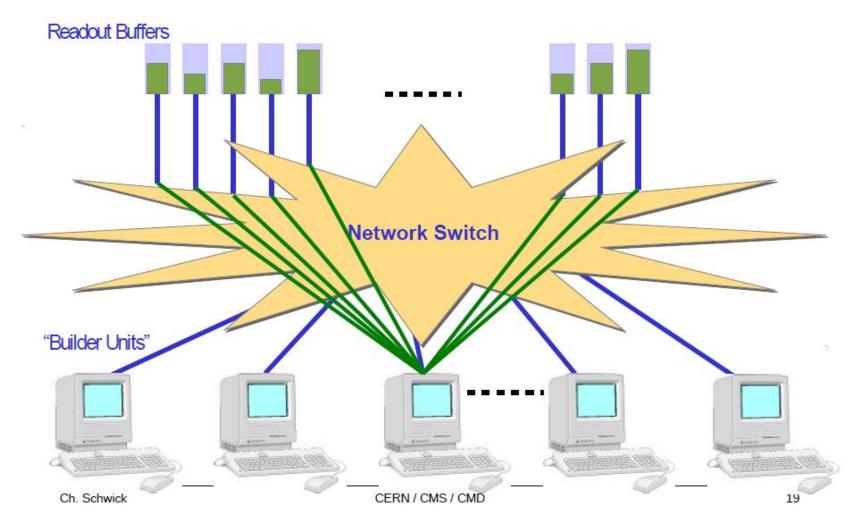

## **Event Building Challenges I**

## **Event Building Challenges II**

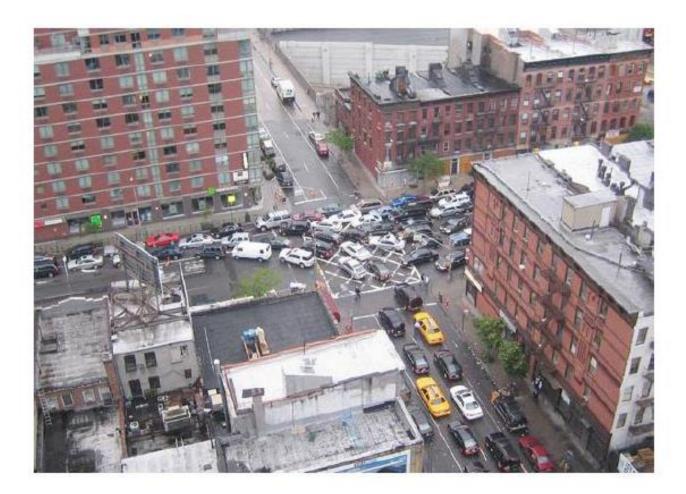

## Traffic Pattern Causes Congestion Problem

## Commercial Switches for DAQ

Commercial switches aim for high bandwidth and low latency

How to use switches

- Shaping Data Traffic data flow manager

- Employing Switches with back pressure and big internal memory (expensive)

- Employing switches with significantly bigger bandwidth than needed to minimize congestion

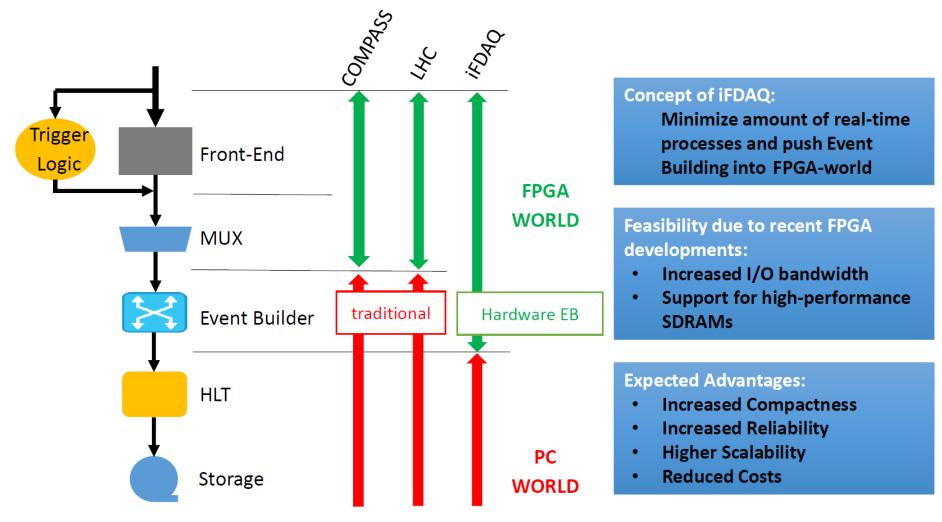

## Novel iFDAQ Architecture

## intelligent FPGA-based DAQ

## Motivation for iFDAQ

### **Progress of FPGA technology**

| Chip                                                     | Manufacturer | Technology | Transistor count |

|----------------------------------------------------------|--------------|------------|------------------|

| Duo-core + GPU Iris <u>Core i7</u><br><u>Broadwell-U</u> | Intel        | 14 nm      | 1 900 000 000    |

| 22-core Xeon Broadwell-E5                                | Intel        | 14 nm      | 7 200 000 000    |

| Virtex 7                                                 | Xilinx       | 28 nm      | 6 800 000 000    |

| Virtex Ultra Scale                                       | Xilinx       | 20 nm      | 20 000 000 000   |

- □ High bandwidth of serial links: 3000 Gbps per single FPGA

- □ High bandwidth of external memory interfaces 10 GB/s per single FPGA

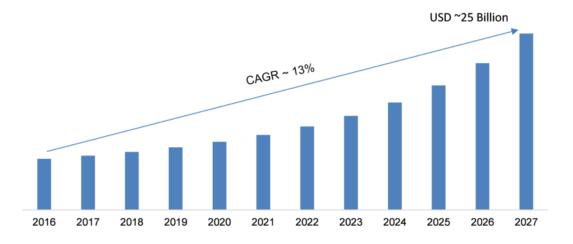

# **FPGA Market Expectation**

https://www.marketresearchfuture.com/reports/field-programmable-gate-array-market-1019

# FPGA technology advantages

- Emerging technology, rapidly extends application fields

- Highly parallel architecture

- Enormous IO bandwidth

- Low cost

- Long development time => Software tools for a moment behind complexity of HW technology

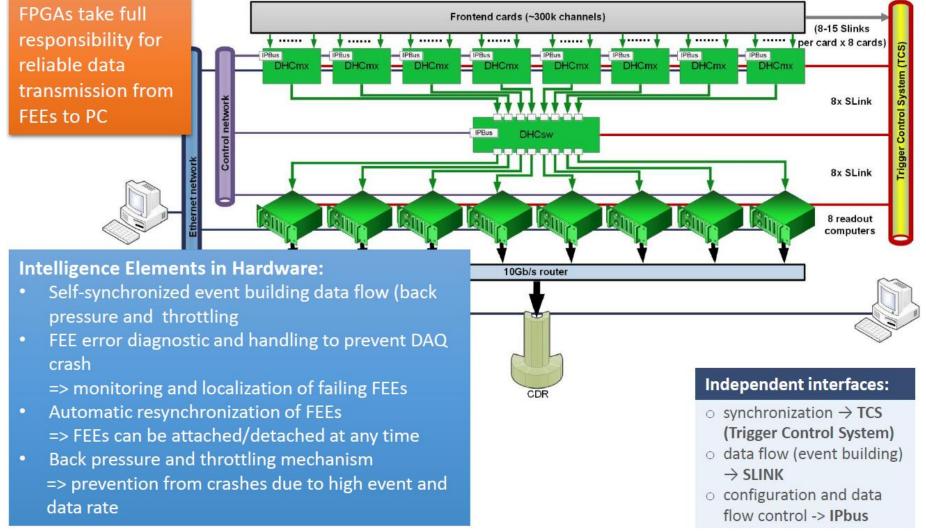

## FPGA is ideal technology

# for development reliable, high performant, low cost DAQ system

## iFDAQ (intelligent FPGA DAQ)

Reliability achieved by smart recovery algorithms included in FPGA

## **Different DAQ Architectures**

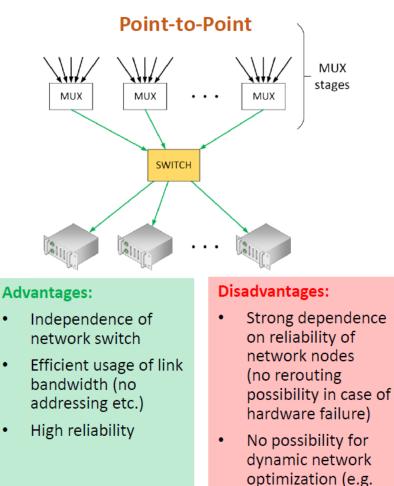

## General Network vs Point to Point

load balancing)

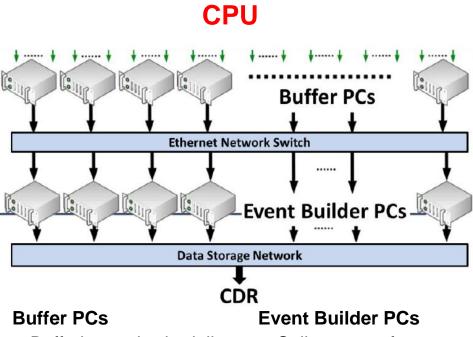

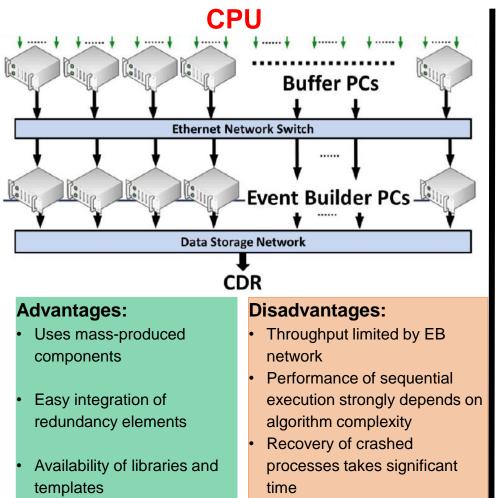

# Event Building : CPU vs FPGA

- Buffering and scheduling data transmission Event Builder PC

- Replicated over computers to fit performance needs

- Collect event fragments and combines them into complete event

- Replicated over computers to fit through put requirements

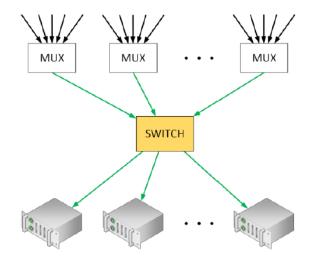

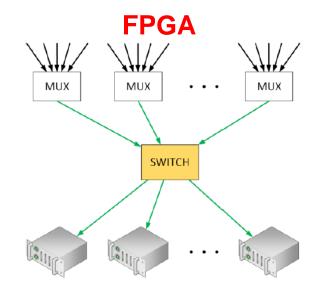

## **FPGA**

#### MUX

- Reduction of number of links

- Buffering and subevent building for efficient usage of serial interfaces

#### SWITCH

- Parallel execution of event building processes

- Distribution of complete events to different compute nodes

## Event Building CPU vs FPGA

#### Advantages:

- Only FPGA allows to build real real-time system

- High scalability

- High reliability

- Low cost

#### Disadvantages:

- Long firmware development progress: high level simulation tools like System Verilog and OSVVM

- $\Rightarrow$  Motivation

- Minimize real time SW processes

- Development of highly automotized and reliable DAQ

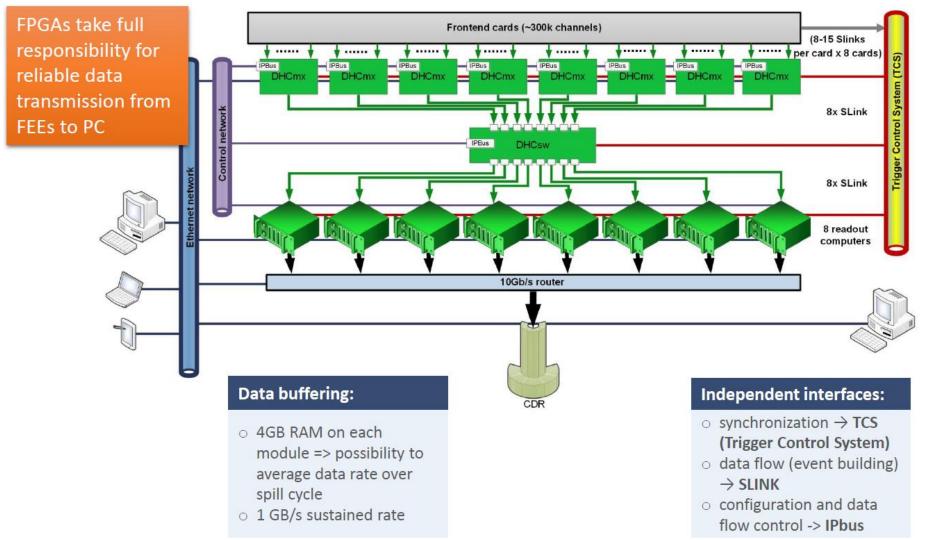

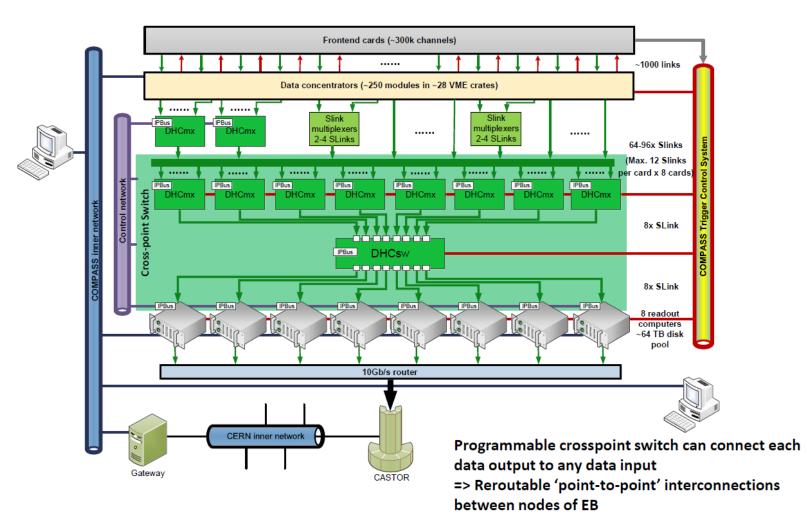

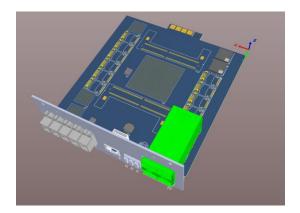

## Data Handling Card

| AMC standard                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Virtex6 XC6VLX130T                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 4 GB DDR3 SDRAM                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| <ul> <li>DHCmx 12:1 multiplexer [1]</li> <li>DHCsw 8x8-switch</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Absolute limit<br>Absolute limit |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

#### VME carrier card

| o form factor: | 6 U VME                                                                                                                                                                                                  |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ○ interfaces:  | <ul> <li>TCS (Trigger Control System) receiver</li> <li>1 Gb Ethernet for control network<br/>(IPbus)</li> <li>16 serial data links (SLINK)</li> <li>JTAG for backup programming of<br/>FLASH</li> </ul> |

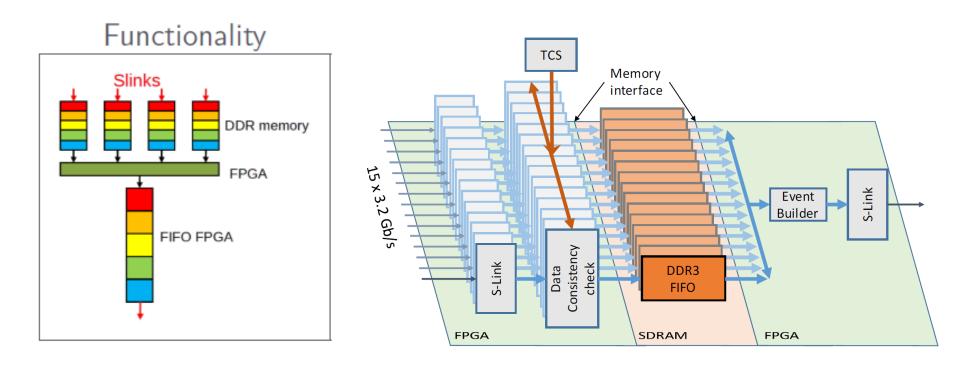

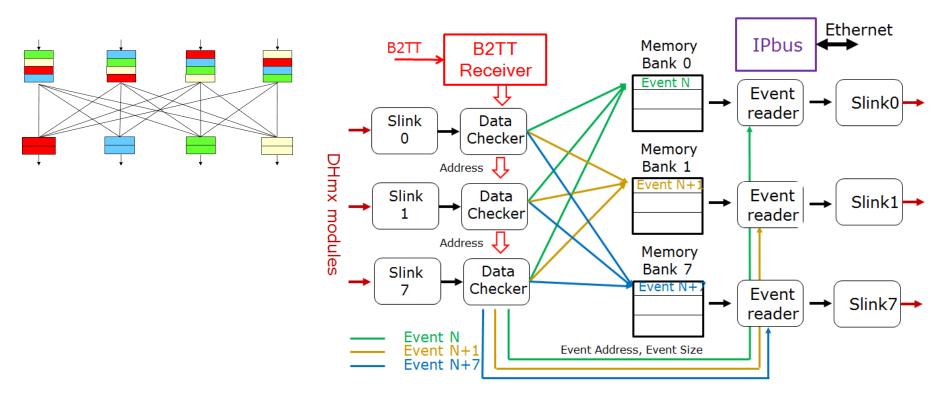

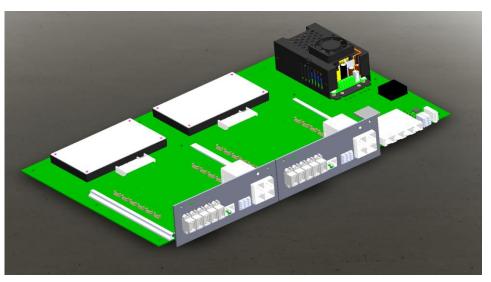

## DHMultiplexer

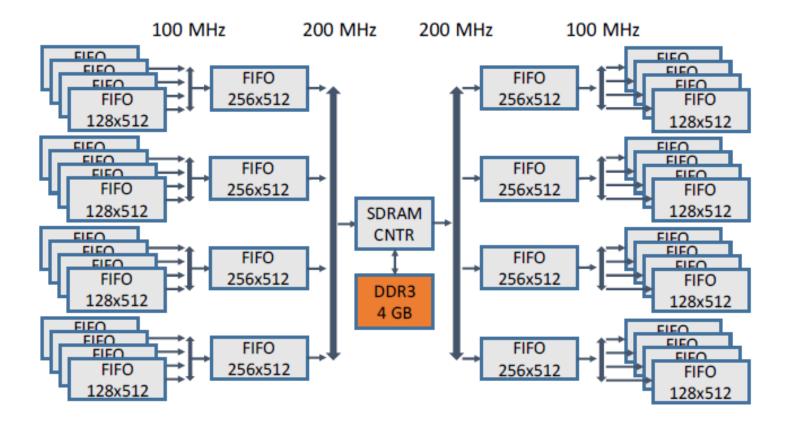

# DDR3 memory controller

- 16 independent FIFO like memories blocks of 256 MB each

- 200 MB/s/port write performance

- 3 GB/s throughput

# FPGA Switch 8x8(event builder)

- Events are processed simultaneously and buffered in DDR, no congestion

- Events distributed between outgoing links in round robin manner

- 2.5GB/s (modern FPGA 10 GB/s) throughput

- One FPGA => Event builder for 2.5(10) GB/s throughput

## iFDAQ Architecture

## iFDAQ Architecture

## ТШП

## iFDAQ

Compact : Before : 30 online PCs Now : one VME 6U crate + 1 rack (8 computers)

Hardware Event Builder

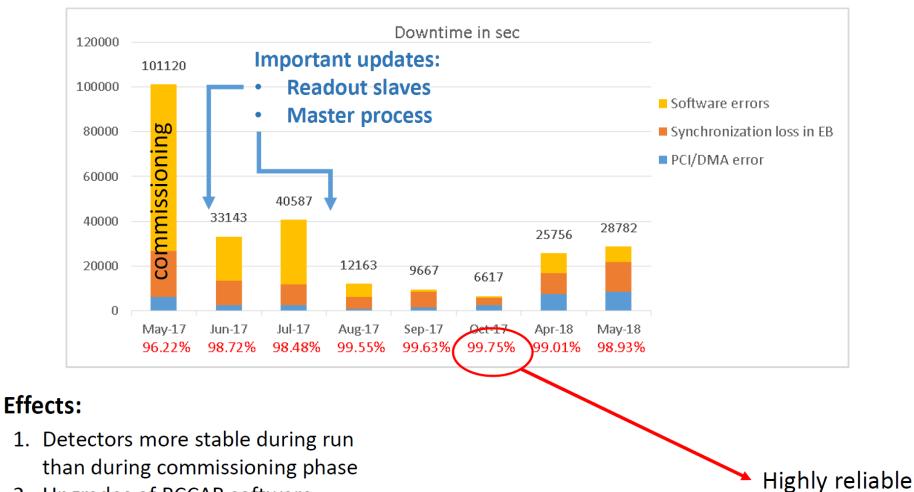

## Performance : Up Time in 2017

2. Upgrades of RCCAR software

Protocol for slow control in FPGA

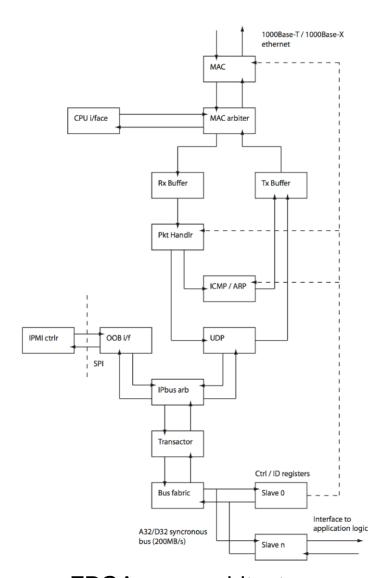

# lpbus

developed for CMS experiment

C.G. Larrea, K. Harder, D. Newbold, D. Sankey, A. Rose, A. Thea, T.Williams, IPbus: a flexible Ethernet-based control system for xTCA hardware Journal of Instrumentation 10, C02019 (2015)

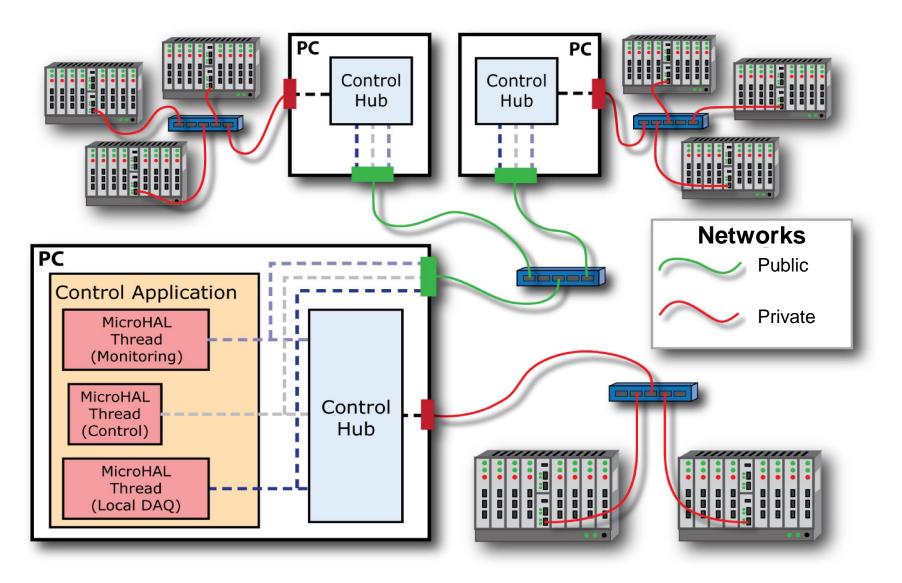

## **IPbus Topology**

## **IPbus FPGA Core and protocol**

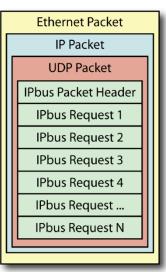

UDP based protocol Mimics microprocessor interface

- Master runs in software on PC

3 types of transactions

- read

- write

- read-modify-write

- for accessing bitfields

Ipbus frame

### Interface to Slaves

```

ipbus_package.vhd

22 -- The signals going from master to slaves

23

type ipb wbus is

24

record

25

ipb addr

: std logic vector(31 downto 0);

26

ipb wdata

: std logic vector(31 downto 0);

ipb strobe

: std logic;

27

: std_logic;

28

ipb write

29

end record:

30

31 -- The signals going from slaves to master

32

type ipb_rbus is

33

record

34

ipb rdata

: std logic vector(31 downto 0);

: std logic;

35

ipb ack

ipb err

: std logic;

36

ipb timeout : std logic vector (15 downto 0);

37

38

end record:

```

Synchronous microprocessor like interface • Wishbone-compatible (open bus for systems-on-a-chip) **ipb\_strobe** signal indicates access to a slave (not address)

# **Available Slaves**

Standard:

- Synchronous R/W register (ipbus\_reg.vhd)

- Static register (ipbus\_static.vhd)

- RAM (ipbus\_ram.vhd)

Non standard:

- I2C (Opencores: i2c\_master\_top.vhd, ... )

- Dynamic Reconfiguration Port for FPGA components (drp.vhd)

- Asynchronous R/W register (ipbus\_asynchreg.vhd)

- Block RAM interface (ipbus\_bram.vhd)

- FIFO, depth 512, 4096, 65536 words (ipbus\_rwfifo.vhd)

- Parallel NOR Flash programmer

Advanced Workshop on EPGA based System-on-

# Software

тлп

Software available as RPMs for SL6/7 and as source code

- https://svnweb.cern.ch/trac/cactus/wiki/uhalQuickTutorial

- µHAL: c++ framework

- Pycohal: python bindings

- Controlhub: software multiplexer

- XML configuration files

- connection.xml: defines connection type (UDP/TCP) and addresses of the hardware

- address.xml: register map

Advanced Workshop on EPGA based System-on-

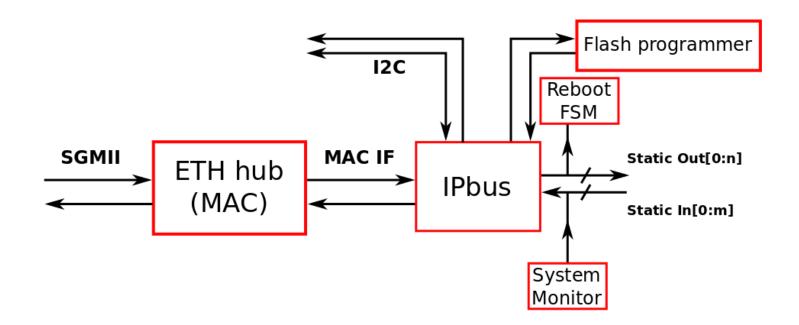

### **Firmware Layout**

Basic firmware for COMPASS DAQ FPGA boards (Virtex-

6)

### monitoring

- rebooting

- flash programming

# New Developments

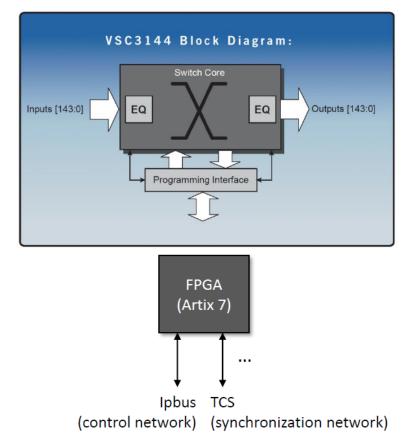

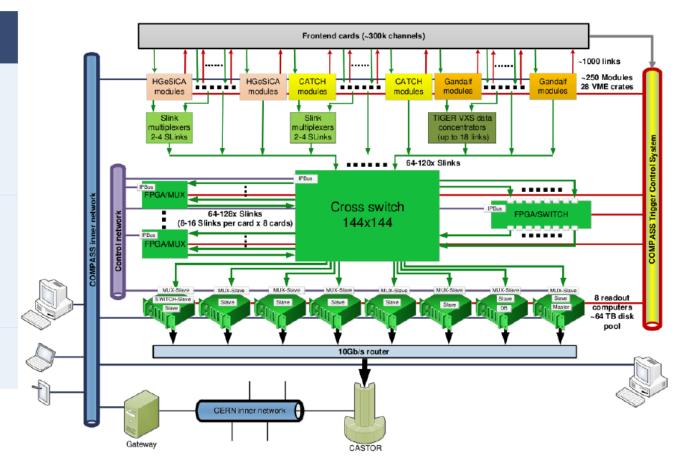

### **Cross-Point Switch**

### Hardware : Vitesse VSC3144

- 144 x 144 strictly non-blocking cross-point switch

- Up to 6.5 Gbps bandwidth per port

- No registers used in data path i.e. asynchronous data path => no restrictions on the phase, frequency, or signal pattern of any input (protocol independent)

- 45mm x 45mm 1072-pin BGA package

- Core programming on port-by-port basis OR simultaneous issuing of multiple queued assignments (low latency: ns)

### **Crosspoint Switch – Hardware Design**

#### **Crosspoint Switch Components**

#### o interfaces:

- 12 x 12 channel CXP transceiver (MPO fiber connectors)

- Ethernet for IPbus

- JTAG

- TCS (Trigger Control System) receiver

#### $\odot$ Switching and Control:

- Vitesse VSC3144-02 fully configurable 144x144, asynchronous, 6.5 Gbps crosspoint switch

- Xilinx Artix-7 FPGA for switch control and monitoring

#### Interface FPGA – Crosswitch:

- 90 MHz, 11-bit parallel data bus

- Multiple program assignments can be queued and issued simultaneously ⇒ fast programming (<< 1us)</li>

## Development System Redundancy

- □ Automatic identification of malfunctioning hardware parts

- Reconfiguration of crosspoint switch to substitute faulty module by spare one. Executed by software

- Upgrade if Time Distribution System (TCS) to bidirectional PON (passive optical network) with use of Universal Communication Framework developed at TUM for on-the-fly reconfiguration of interconnections

- Minimizing of real-time software processes

=> Direct writing of data onto SSD

### **Crosspoint Switch**

#### **Crosspoint Switch**

#### o connects:

- FE electronics

- DHCmx modules

- DHCsw module

- Spillbuffers

#### o purpose:

- Ease of load balancing

- System redundancy to compensate hardware failures

- ⇒ provides fully customizable network topology

### New FPGA Module

- Kintex XCKU095T FPGA

- Custom case design Interfaces

- 60x12Gb/s links

- IPBUS

- TCS

Memory

2x16GB DDR4

Module will be available in October 2018

# **Unified Communication Protocol**

### Developed by Dominic Gaisbauer PhD student of TUM The work received first student award at RT2016 conference

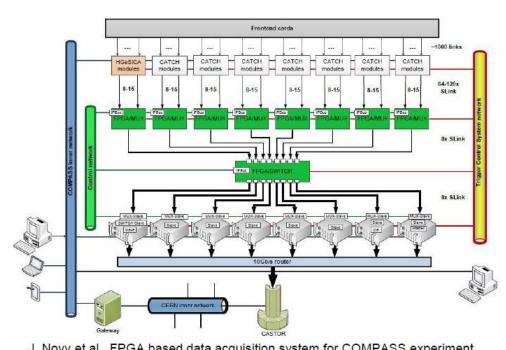

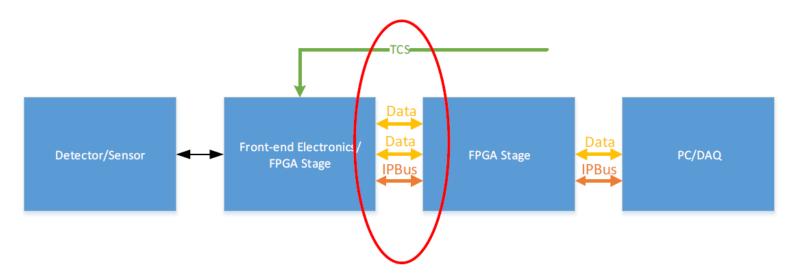

# **COMPASS** Experiment Topology

- One link for TCS messages ٠

- One link for IPBus messages ٠

- Multiple data links •

- Underlying principle the same . in many other experiments

- Why not combing data, TCS, and data in a single link?

J. Novy et al., FPGA based data acquisition system for COMPASS experiment

# Unified Communication Framework (UCF)

- Originates from the SODA time distribution system

- Single high-speed serial link for data, slow control, trigger, and timing information

- Up to 64 different communication channels

- Unidirectional determined latency for a one channel

- Fully configurable ipcore via single VHDL package file

- Link speed depends only on FPGA resources

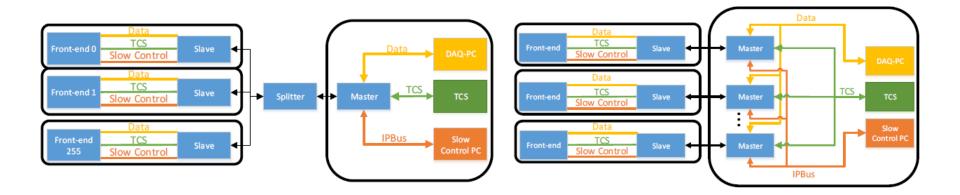

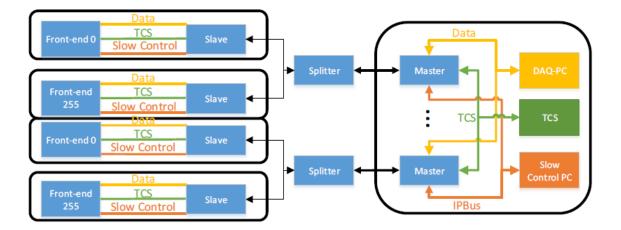

## UCF – Example Topologies

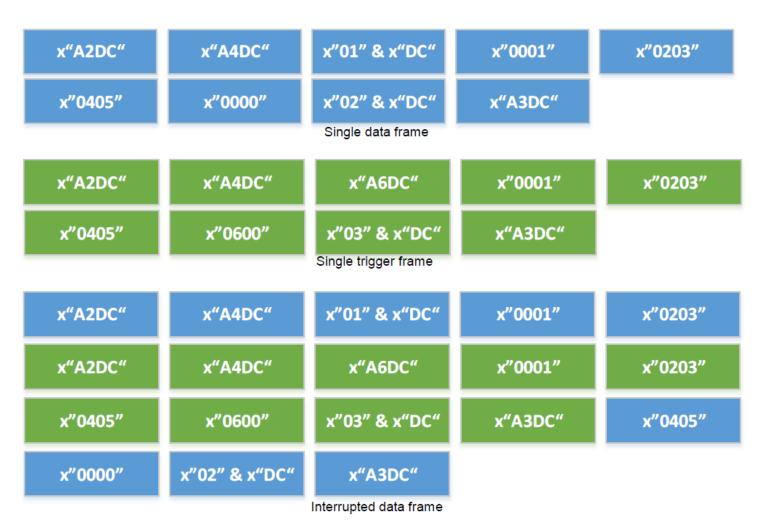

# UCF - Low Layer Protocol

- Backbone of UCF

- Handles communication and initialization

- 8b/10b encoding scheme

- Internal data width of 16b/20b (32b/40b) for the protocol

- 10b K-characters for control and synchronization

- Fixed phase synchronization by sequence of two defines K-characters (x"BCDC")

- Unique IDs and IPs by FPGA DNA

## UCF – Priority Handling

# ТШП

### UCF – User Interface and Configuration

- All channels can be addressed via the standardized ARM AMBA AXI interface

- Leads to easy integration and connection to other ipcores

- Easy configuration of all important parameters within one file:

- Link speed

| - [ | Торо | logy |

|-----|------|------|

|     |      |      |

- Data width

- Device type

- ...

|   | use IEEE.STD_LOGIC_1164.all; C                            |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|---|-----------------------------------------------------------|-------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

|   |                                                           | ation file that has to be mod | ified by the user according CRLF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|   | ! to his requirements@RLF<br>package ConfigUCF ucf isCRLF |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| Э | constant strDeviceType                                    | : string                      | := "Virtex6";                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

|   | constant stdActivateP2P                                   |                               | understation := •1•; destation dataset                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|   | constant stdCardPurpose                                   | : std logic                   | encererences := . • 1 • ; • • • • • • • • • • • • • • • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|   | constant intTransceivers                                  | integer                       | แของสมาความหลุ่มข้า <mark>: = :1</mark> ; เป็นแห่งแก่แขนแขงหลุ่มเองหน                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

|   | constant intInterfaces                                    | : integer                     | overenerener, <mark>:</mark> ≣s <mark>1;</mark> besondeterenerenereneren.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |

|   | constant intCylcesMin                                     | : integer                     | = 8; = 8; = 10, = 0, = 0, = 0, = 0, = 0, = 0, = 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|   | !Data width settings for User@RLF                         |                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|   | constant intDataWidthUsr                                  | : integer                     | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |

|   | constant intByteWidthUsr                                  | : integer                     | $u_{11}u_{12}u_{13}u_{13}u_{13}u_{14}u_{14}u_{14}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{15}u_{1$ |  |  |

|   | constant intSerials                                       | : integer                     | andrinaallanaan := 1; kataallan inaan kahama                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

|   | type dna type                                             | is array (integer rang        | ge <>) of std logic vector(63 downto 0);                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |

|   | constant DNAs :                                           | dna_type(intSerials do        | ownto 0) :=(( x"0000000000000000),<br>(x"00C0426EBA540890"));                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

### UCF – Tests and Measurements

- Star-like topology with 12 slaves and 1 master

- 1.25 Gbit/s link speed

- Spartan 6 FPGA as slave and Virtex 6 as master

- Switching time of 16 µs

- Long term stability test with 99 % link utilization for two weeks

- JTAG chain possible with up to 100 kHz frequency

- IPBus over UCF implemented

| Transmission<br>Time [µs] | Efficiency<br>[%] |

|---------------------------|-------------------|

| 25000                     | 99,93             |

| 10000                     | 99,84             |

| 1000                      | 98,42             |

| 500                       | 96,90             |

| 100                       | 86,20             |

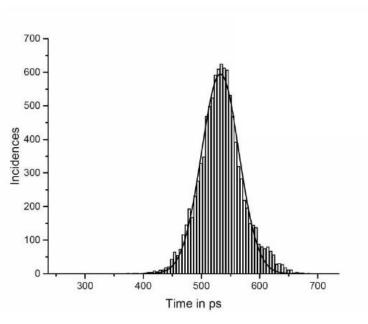

### UCF – Tests and Measurements

- Point-to-Point topology with 1 slave and 1 master

- · 2.5 Gbit/s link speed

- Virtex 6 as slave and master

- Recovered clock jitter of 23 ps

- Long term stability test with 99 % link utilization for two weeks

- IPBus over UCF implemented

# UCF - Conclusion

- Developed ipcore providing unified communication of up to 64 channels via a single optical link

- One channel has deterministic latency in one direction from master to slave

- Standard ARM AMBA AXI interface for user

- 1:N or multiple 1:1 connection possible

- 98-99 % link utilization efficiency depending on the architecture

- 16 µs switching time in star-like topology

- 23 ps jitter of the recovered clock

- Implemented JTAG over UCF with 100 kHz frequency

- Implemented IPBus over UCF

- Employed in Belle2 and PENeLOPE experiments

# THANK YOU