# **SoC FPGAs: Opportunities and Challenges**

Advanced Workshop on Modern FPGA Based Technology for Scientific Computing

Nizar Abdallah May 2019

© 2018 Microsemi, a wholly owned subsidiary of Microchip Technology Inc.

- A short bio...

- What will we be talking about?

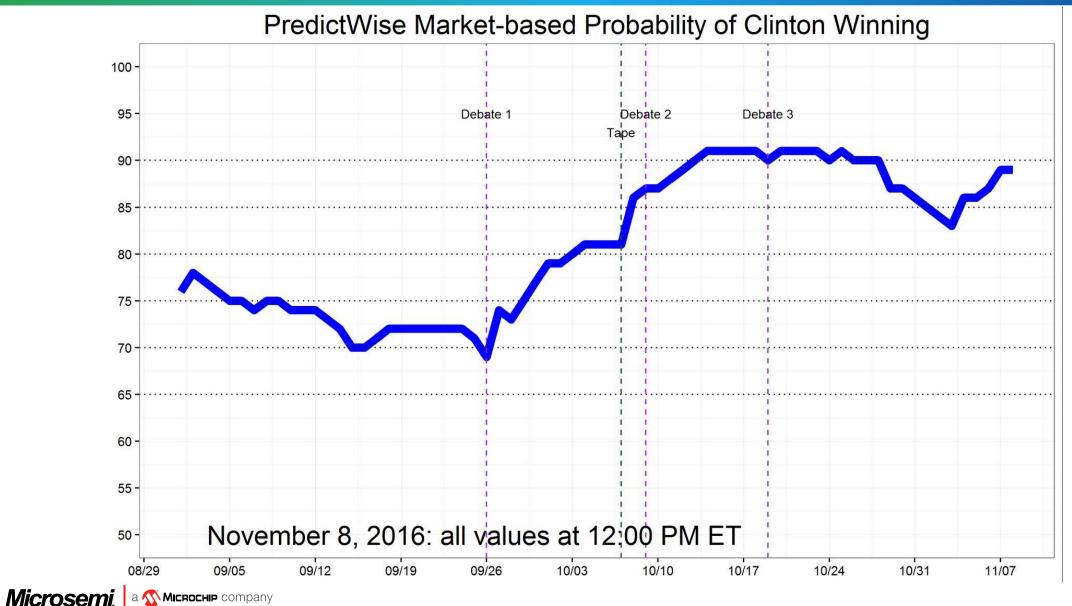

#### **Disclaimer-On Our Ability to Predict the Future**

© 2018 Microsemi 3

#### **Disclaimer-On Our Ability to Predict the Future**

| Firm                        | Dates        | Sample   | Clinton | Trump | Spread       |

|-----------------------------|--------------|----------|---------|-------|--------------|

| P Poll Average              |              |          | 47.0    | 43.8  | Clinton +3.2 |

| Economist/YouGov            | 11/4 - 11/7  | 3669 LV  | 49      | 45    | Clinton +4   |

| Bloomberg                   | 11/4 - 11/6  | 799 LV   | 46      | 43    | Clinton +3   |

| Monmouth<br>Jniversity      | 11/3 - 11/6  | 748 LV   | 50      | 44    | Clinton +6   |

| ABC/Wash Post<br>Tracking   | 11/3 - 11/6  | 2220 LV  | 49      | 46    | Clinton +3   |

| FOX News                    | 11/3 - 11/6  | 1295 LV  | 48      | 44    | Clinton +4   |

| BD/TIPP Tracking            | 11/3 - 11/6  | 1026 LV  | 43      | 42    | Clinton +1   |

| CBS News                    | 11/2 - 11/6  | 1426 LV  | 47      | 43    | Clinton +4   |

| Reuters/Ipsos               | 11/2 - 11/6  | 2196 LV  | 44      | 39    | Clinton +5   |

| NBC News/SM                 | 10/31 - 11/6 | 30145 LV | 51      | 44    | Clinton +7   |

| LA Times/USC<br>Tracking    | 10/31 - 11/6 | 2935 LV  | 43      | 48    | Trump +5     |

| NBC News/Wall<br>St Journal | 11/3 - 11/5  | 1282 LV  | 48      | 43    | Clinton +5   |

| McClatchy/Marist            | 11/1 - 11/3  | 940 LV   | 46      | 44    | Clinton +2   |

| CBS News/New<br>York Times  | 10/28 - 11/1 | 1333 LV  | 47      | 44    | Clinton +3   |

|                             |              |          |         |       |              |

Microsemi. a Wicrochip company

#### Introduction

#### JAN 2017

5

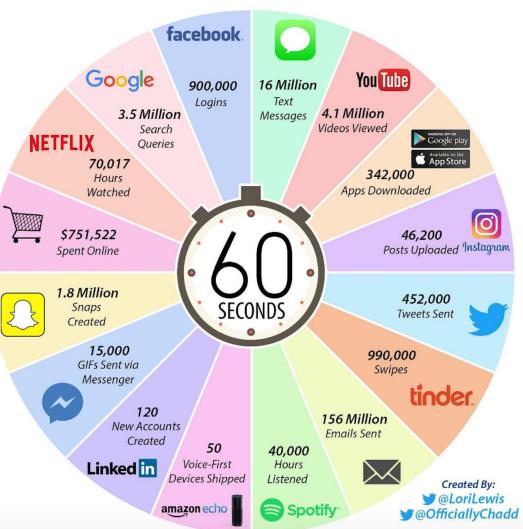

# **GLOBAL DIGITAL SNAPSHOT**

KEY STATISTICAL INDICATORS FOR THE WORLD'S INTERNET, MOBILE, AND SOCIAL MEDIA USERS

SOURCES: FORMATION UNITED NATIONE; U.S. CENSUS BUREAU: INTERNET: INTERNETWORIDITATE: ITU: INTERNETURESTATE: CIA WORLD FACTROOK; FACEBOOK; NATIONAL REGULATORY AUTHORITEE: SOCIAL MEDIA AND MOREE SOCIAL MEDIA: FACEBOOK; TENGENT, VICONTAKTE: LIVEINTERNET, PU; KAKAO; NAVER; NRI AGH4E1: CAFEBAZAAR IR: SIMILARWEB: DING: EXTRAPOLATION OF THE DATA; MORLE: GEMA INTELLIGENCE: EXTRAPOLATION OF EMARKETER AND ERICESON DATA. 🖱 Hootsuite - 🖉

#### 2017 This Is What Happens In An Internet Minute

### **More Intelligence in Every System**

### **Society's Top Challenges and Trends**

- IoT => distributed intelligence & interconnectivity

- Data explosion, processing (AI & ML) => computation, response time

- Energy needs => decentralized processing at end points + reconfigurability

- Environmental sustainability (product as a service) => cloud storage, response time, adaptability

- Social sustainability => cost & access

- Security => response time

- Well being (robotics, medical, comfort) => response time, adaptability, portability

- Theoretical research: space exploration => reliability

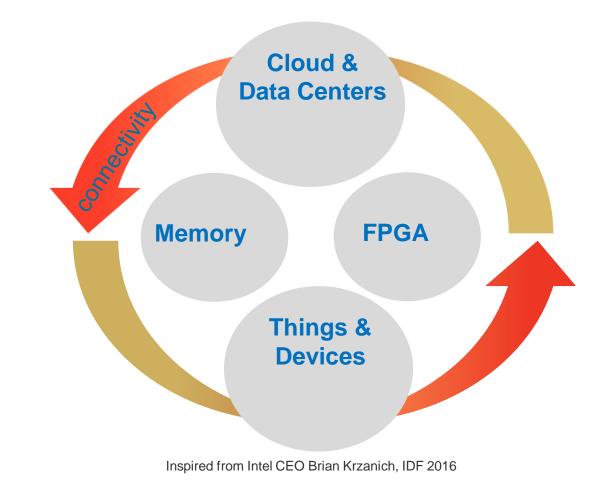

## At the Center of the Digital Transformation

- Everything we do has a digital component

- Push to the cloud

- Run analytics

- Push back to the source

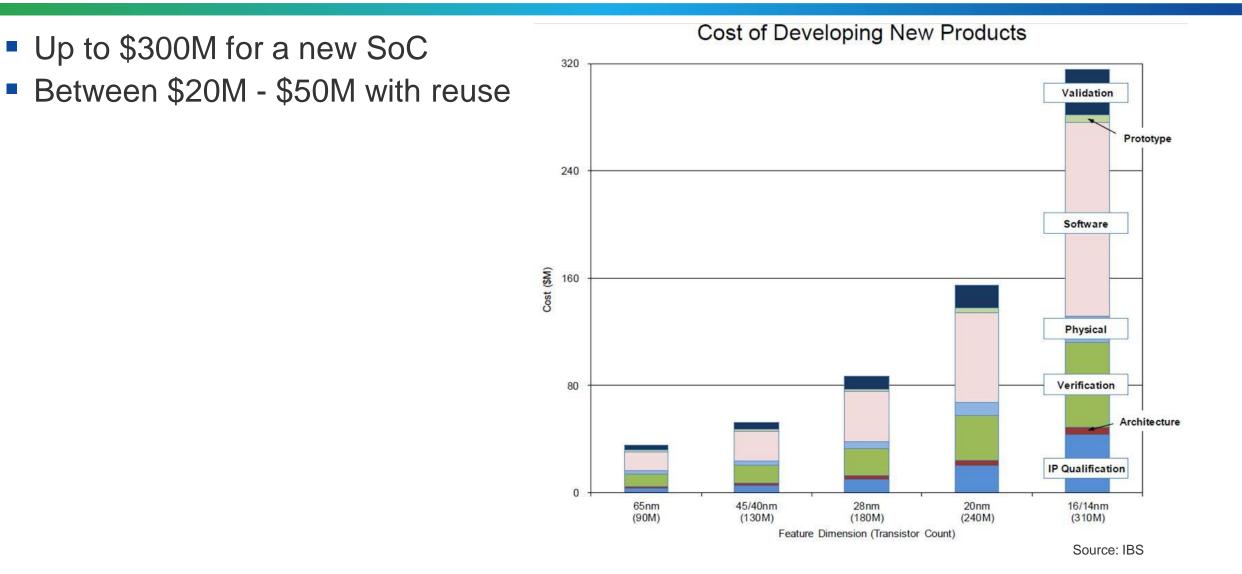

### **Design Cost**

Microsemi. а Фміскоснір company

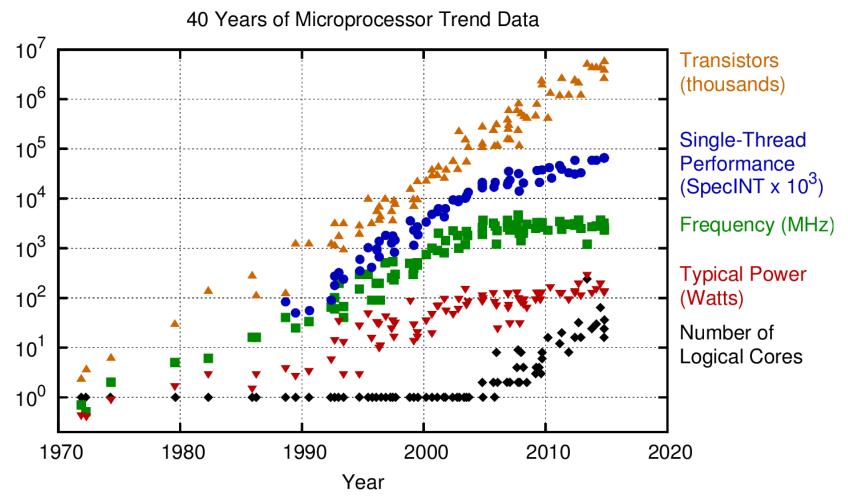

### **Performance Improvement Trend**

Original data up to the year 2010 collected and plotted by M. Horowitz, F. Labonte, O. Shacham, K. Olukotun, L. Hammond, and C. Batten New plot and data collected for 2010-2015 by K. Rupp

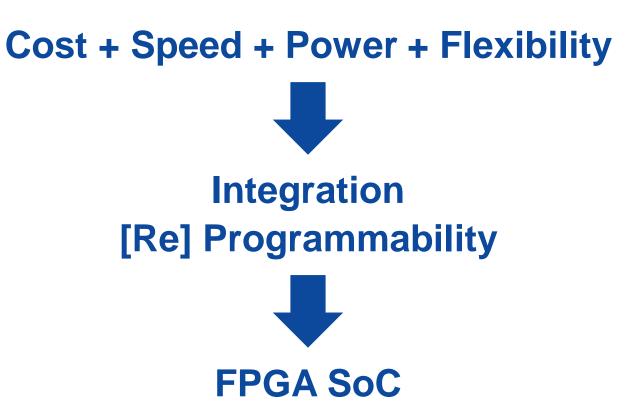

#### **Key Requirements**

#### **FPGA Economics**

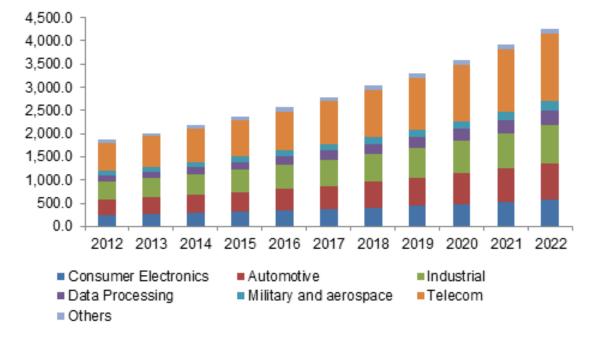

Asia-Pacific FPGA market growth. Source: Global Market Insights

U.S. FPGA market Growth. Source: Grand View Research

Microsemi. a <sup>Microchip</sup> company

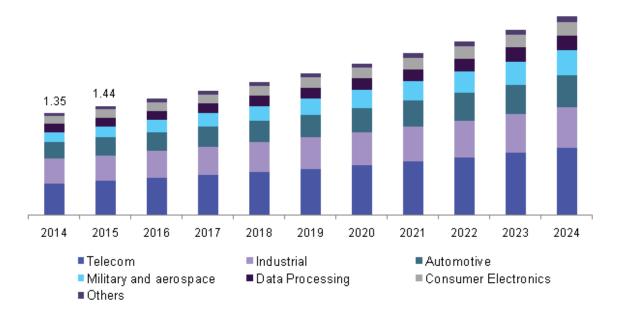

#### **FPGA Basics**

# **Programmable Logic Basics**

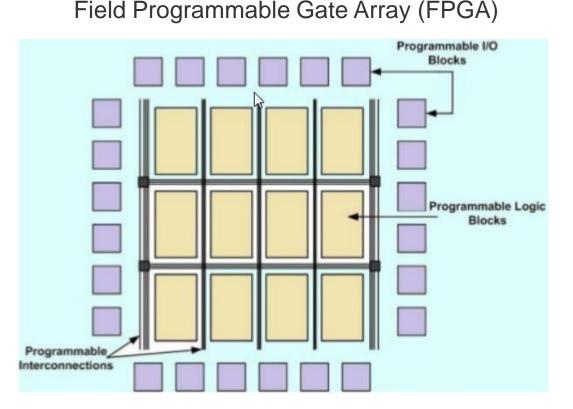

#### Complex Programmable Logic Device (CPLD)

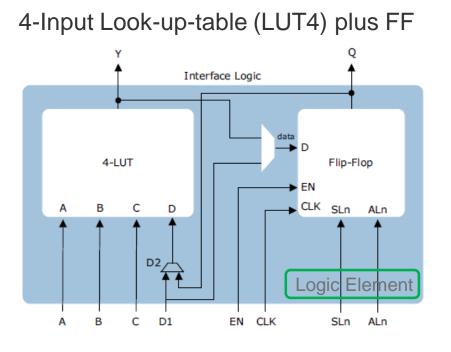

- Flexible architecture with virtually no restrictions any pin to any logic block. <u>LUT4 + FF = an LE</u>

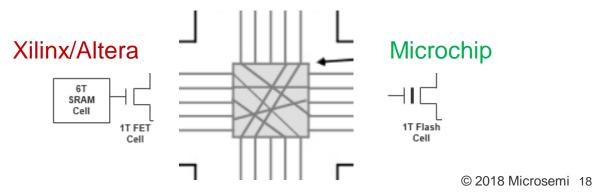

- Large Density, High pin count SRAM based or Flash

- Highly integrated with memory, DSP, transceivers

- Variable timing dependent on routing

- Microsemi. a Wicrochip company

- Less flexible architecture with routing limitations uses Macrocell blocks to build functions

- Low density EEPROM based but with fixed timing

- Great for simple logic functions

- No investment being made in this technology

# Why Did FPGAs Become So Popular?

- FPGAs are "field" re-programmable which gives them many advantages over traditional custom ASICs

- Great deal of application flexibility

- Quick time to market

- Low risk

- Field upgrade-ability

- They are much higher density and have a more flexible architecture than CPLDs

- FPGAs use either SRAM memory or Flash memory to provide their re-programmability

- The ability to conceive of a logic function and realize that function in silicon within weeks or even days was a revolutionary concept that fundamentally changed how digital systems are developed today

- Furthermore, the capability of being able to upload a "bug-fix" to a fielded FPGA-based product was something that designers had only dreamed about

- Using an internet connection to the fielded product, a configuration flash memory can be programmed and then the FPGA instructed to load the new image

- With the great growth of the FPGA market over the last 20 years (now at ~\$5.5B), ASICs have been relegated to only very high volume applications

### **FPGA Architecture**

20Kbit Large SRAM (LSRAM)

#### A ADDR<13:0> B ADDR<13:0> A DIN<19:0> B DIN<19:0> A\_WEN A DOUT<19:0> B\_WEN B\_DOUT<19:0> A\_REN DB\_DETECT Large SRAM B\_REN SB CORRECT ECC\_EN DEBUG\_BUSY A\_BLK\_EN<2:0> B BLK EN<2:0> DEBUG BUSY FDBK A\_CLK B\_CLK

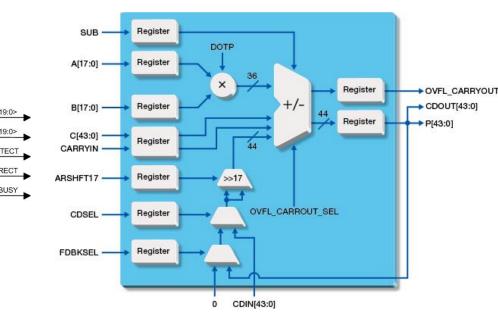

#### 18x18 Multiply Math Block

- All FPGAs have some combination of these building blocks and switch matrices

- Other blocks that are becoming more popular within FPGAs are

- Transceiver Blocks from 5G to 25G+

- Analog PLLs, crypto processors, DDR controllers, ADCs

- Embedded processors (Arm and RISCV)

- Nicrosemi. a 🍄 Міскоснір company

#### **Routing Switch Matrix**

### How Do FPGAs Work?

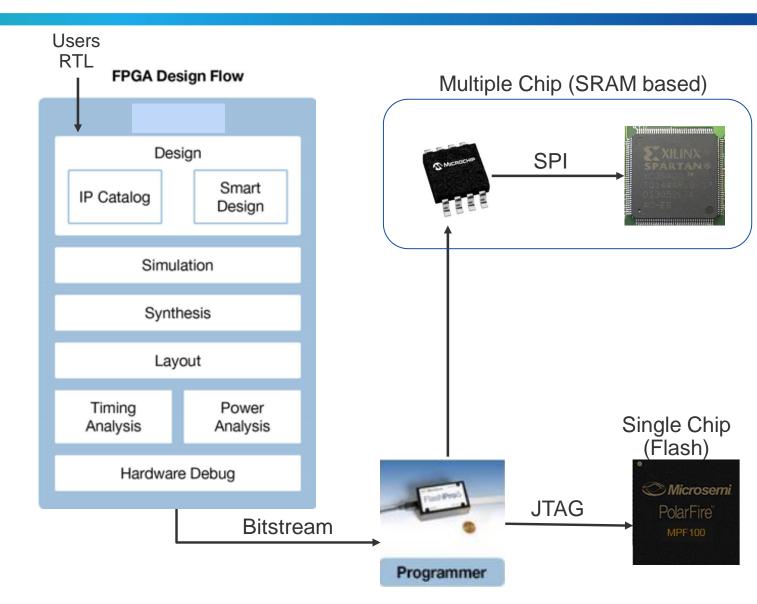

- The designer describes his design in

- RTL (VHDL or Verilog)

- Uses IP blocks (UART or SPI for example)

- Simulates the RTL using Modelsim

- Synthesizes the design using Synplify from Synopsys

- This converts the RTL into an edif netlist

- After place and route, timing and power analysis is performed

- Programming takes place using a USB dongle to

- Program a SPI flash or NAND flash for Xilinx and Altera

- Once the chip is told to re-program, it "re-boots" itself with the new image

- Program our FPGA directly since the FPGA is flash based (no "boot" prom needed)

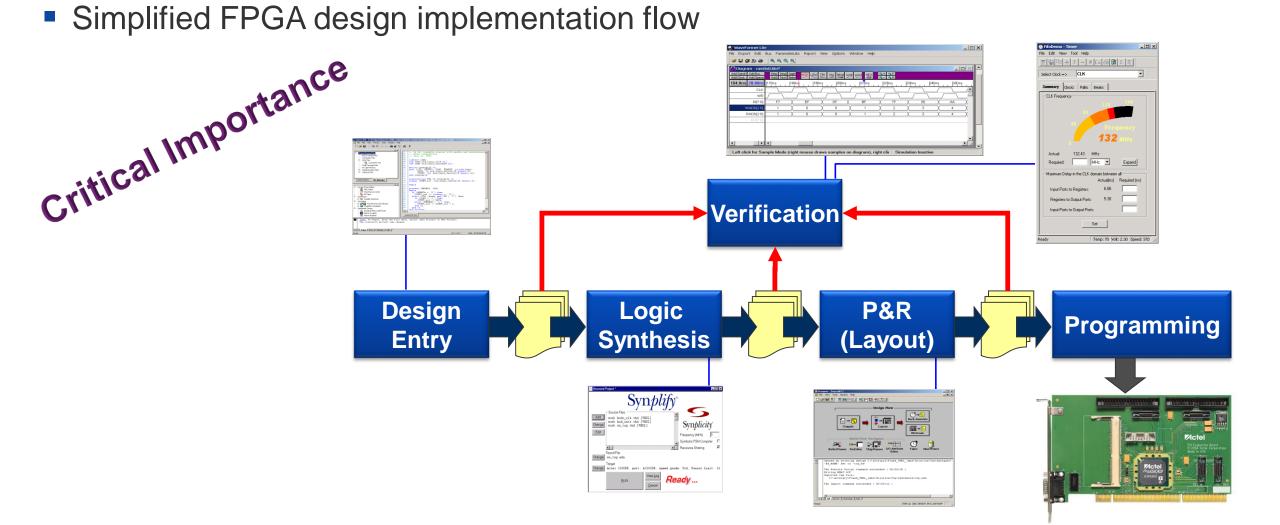

# [FPGA] Design Methodology

# **FPGA Implementation Flow**

.

Microsemi. a SMicrochip company

### **System Validation Flow**

- Simulation

- Bus Functional Model (BFM)

- Mixed language HDL simulation

- Hardware Prototype for system validation

# "Every circuit is considered guilty until proven innocent"

Microsemi. a Wicrochip company

### **Example of a FPGA Family Table (PolarFire)**

|                   | Footunoo                              | PolarFire FPGA                                                 |                    |                    |                    |  |

|-------------------|---------------------------------------|----------------------------------------------------------------|--------------------|--------------------|--------------------|--|

|                   | Features                              | MPF100                                                         | MPF200             | MPF300             | MPF500             |  |

| FPGA Fabric       | Logic Elements (4LUT + DFF)           | 109K                                                           | 192K               | 300K               | 481K               |  |

|                   | Math Blocks (18x18 MACC)              | 336                                                            | 588                | 924                | 1480               |  |

|                   | LSRAM Blocks (20 kbit)                | 352                                                            | 616                | 952                | 1520               |  |

|                   | uSRAM Blocks (64x12)                  | 1008                                                           | 1764               | 2772               | 4440               |  |

|                   | Total RAM (Mbits)                     | 7.6 Mbits                                                      | 13.3 Mbits         | 20.6 Mbits         | 33 Mbits           |  |

|                   | uPROM (kbits)                         | 297 Kbits                                                      | 297 Kbits          | 459 Kbits          | 513 Kbits          |  |

|                   | User DLL's/PLL's                      | 8 each                                                         | 8 each             | 8 each             | 8 each             |  |

| High Speed<br>I/O | 250 Mbps -12.7 Gbps Transceiver Lanes | 8                                                              | 16                 | 16                 | 24                 |  |

|                   | PCIe Gen2 Endpoints/Root Ports        | 2                                                              | 2                  | 2                  | 2                  |  |

| Total I/O         | Total User I/O                        | 296                                                            | 364                | 512                | 584                |  |

| Packaging         | Type / Size / Pitch                   | Total User I/O (HSIO / GPIO) GPIO CDRs / XCVRs                 |                    |                    |                    |  |

|                   | FCSG325 (11x11, 11x14.5*, 0.5 mm)     | 170(84/86) 8/4                                                 | 170(84/86) 8/4*    |                    |                    |  |

|                   | FCSG536 (16x16, 0.5 mm)               |                                                                | 300(120/180) 15/4  | 300(120/180) 15/4  |                    |  |

|                   | FCVG484 (19x19, 0.8 mm)               | 284(120/164) 14/4                                              | 284(120/164)14/4   | 284(120/164) 14/4  |                    |  |

|                   | FCG484 (23x23, 1.0 mm)                | 244(96/148) 13/8                                               | 244(96/148) 13/8   | 244(96/148) 13/8   |                    |  |

|                   | FCG784 (29x29, 1.0 mm)                |                                                                | 364(132/232) 20/16 | 388(156/232) 20/16 | 388(156/232) 20/16 |  |

|                   | FCG1152 (35x35, 1.0 mm)               |                                                                |                    | 512(276/236) 24/16 | 584(324/260) 24/24 |  |

|                   |                                       | Devices in the same package and family type are pin compatible |                    |                    |                    |  |

Extended Commercial (0°C-100°C) and Industrial (-40°C-100°C) Temperature Support for all Die Package Combinations - RoHS only

Additional Temp Grade: Military (-55°C-125°C) - Leaded packages only

**Містозеті**. а **Міскосні**р сотралу

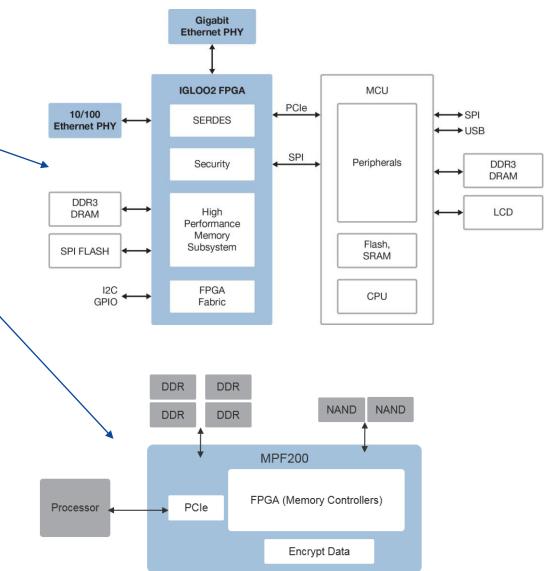

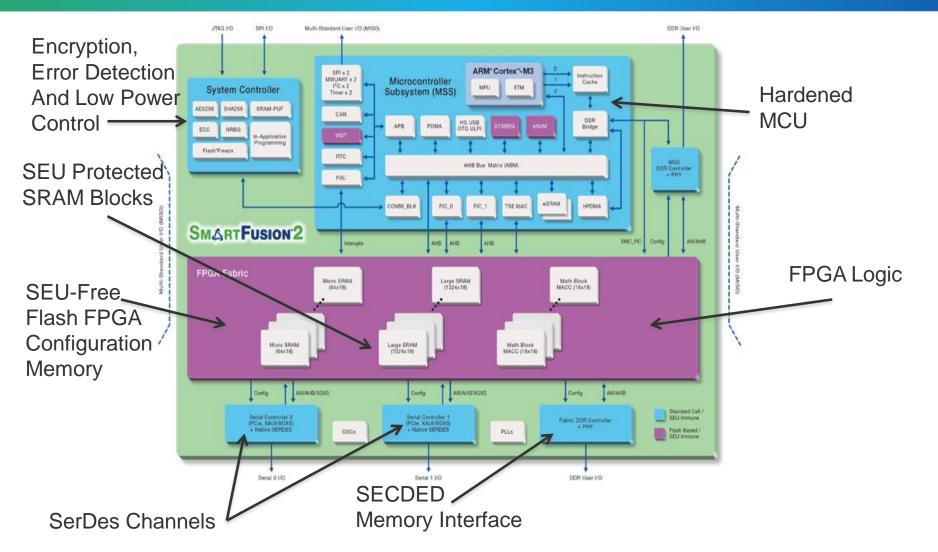

# Where FPGAs Fit Within Electronic Systems?

- A common application for an FPGA is as an companion chip to a CPU

- Functions could range from interface expansion, to DSP offload algorithms, to motor control, to image processing, to NVDIMM controllers

- High-end FPGAs are used in many communications data-path designs

- Microchip FPGAs fit better in the control plane

- With the advent of embedded processors on FPGAs, a new class of applications is emerging where the entire System is On a Chip (SOC)

- SmartFusion2 (M3) and Zynq/Cyclone 5 (dual A9 CPUs

- Military and Space applications

- Mil Avionics, missile guidance, soldier hand held

- Nasa based space programs and military communications programs

- Higher volume new space applications RT plastic Microsemi a Microchip company

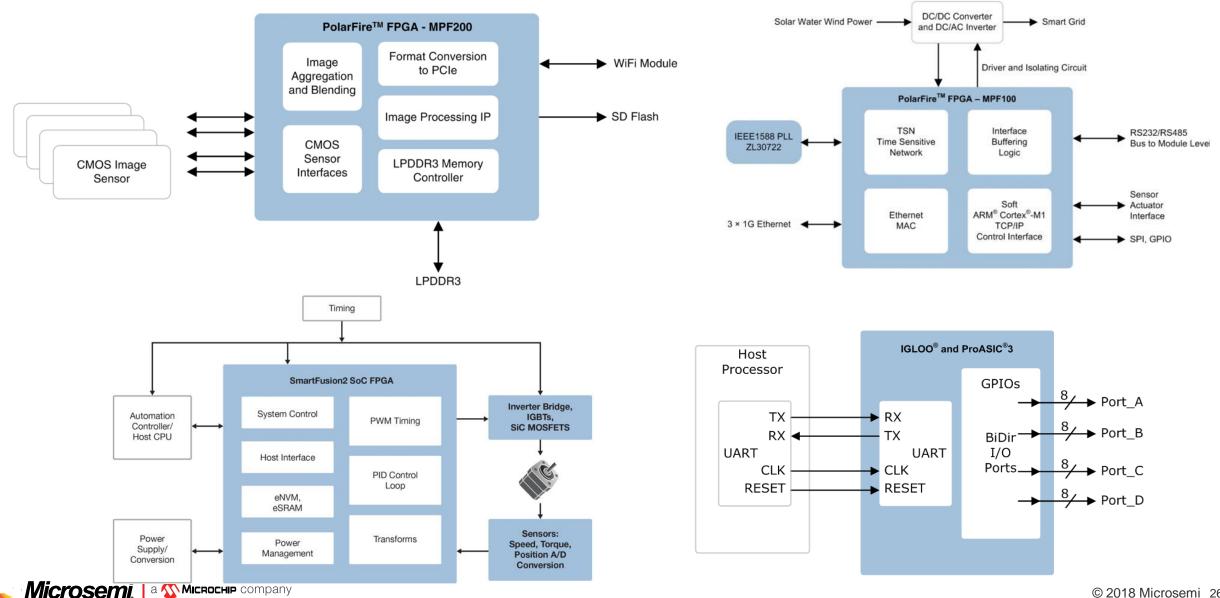

### **Additional Application Examples**

© 2018 Microsemi 26

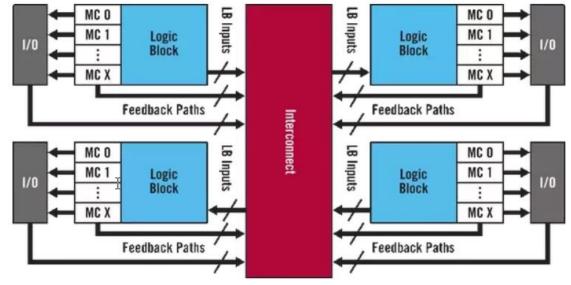

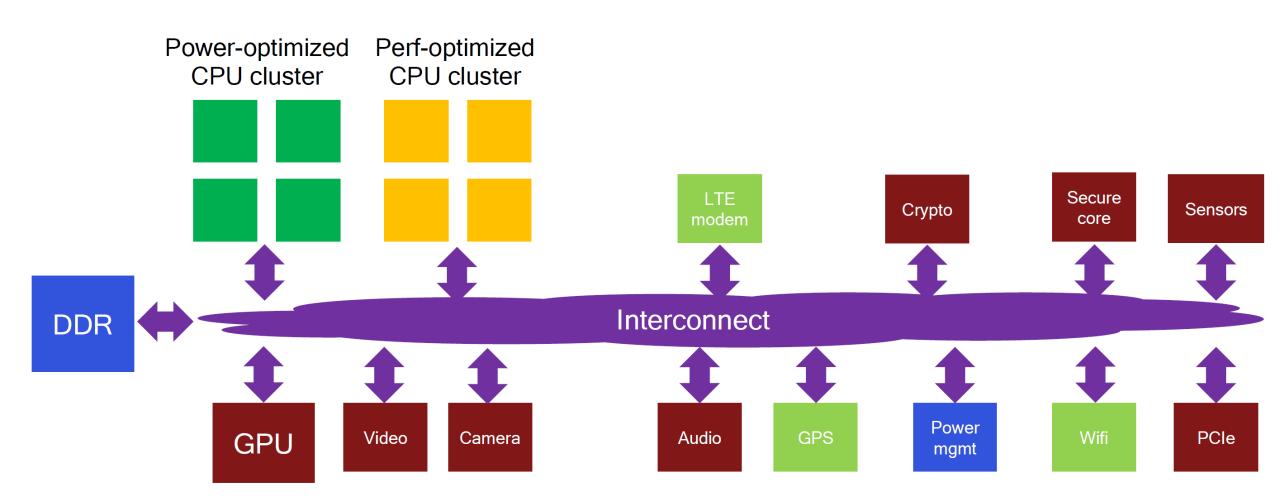

### SoC and SoC FPGA

#### FPGA

- Field Programmable Gate Array

- Plenty of I/O options

- Extremely parallel architecture

- Programmable hardware

#### SoC

- System on Chip

- CPU Core + Peripherals

- Programmable software

- SoC FPGA

- SoC & FPGA on a single chip

- Connected through on-chip bus

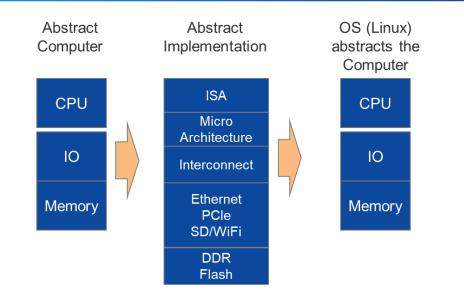

#### **SoC Overview**

Microsemi. a SMicrochip company

#### **SoC Overview**

Source: Greg Wright - RISC-V Summit December 2018

# **Very Complex System**

- Many CPUs = Many ISAs + Many SW Stacks

- Multiple clock domains

- Multiple power domains

- Multiple third party IPs

- Different development cycles for each component type

- Multiple skills required

- A validation nightmare

# Why SoC FPGA?

- Reduce size => Reduce overall system cost

- Increase performance

- Lower power consumption

- Increase system reliability

- Need for special bus interface for a CPU

- Need for obscure amount of IOs

- Need for extra CPU power for your FPGA

- Need for extra FPGA speedup for your CPU functions

# **RISC-V: The Opportunity**

#### Homogenization

- Common base (and frozen)

- Shared frameworks and libraries

- Rich ecosystem (and growing)

#### Customization

- Mix-and-match extensions

- Domain specific features

- Proprietary extensions

- Freedom in implementing

Microsemi. a Wicrochip company

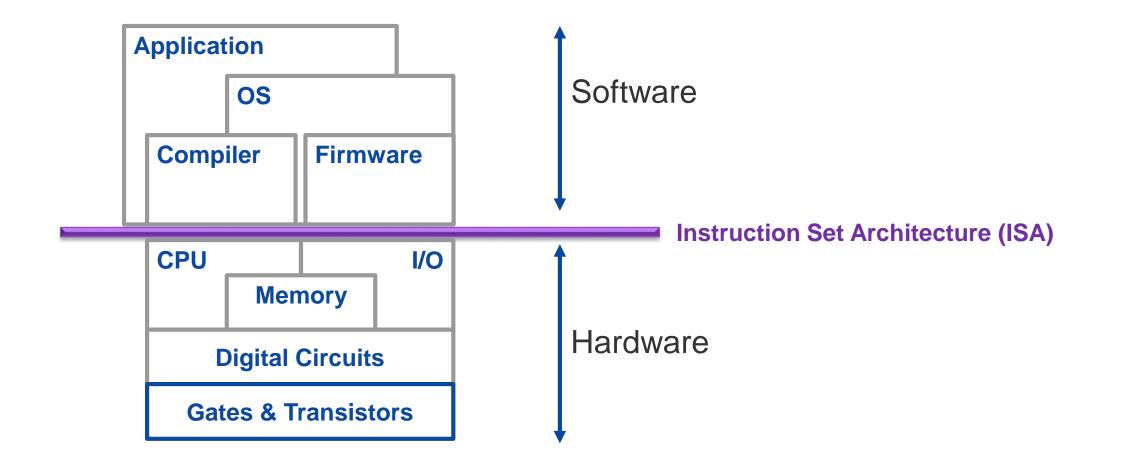

#### **Instruction Set Architecture (ISA)**

Microsemi. a Microchip company

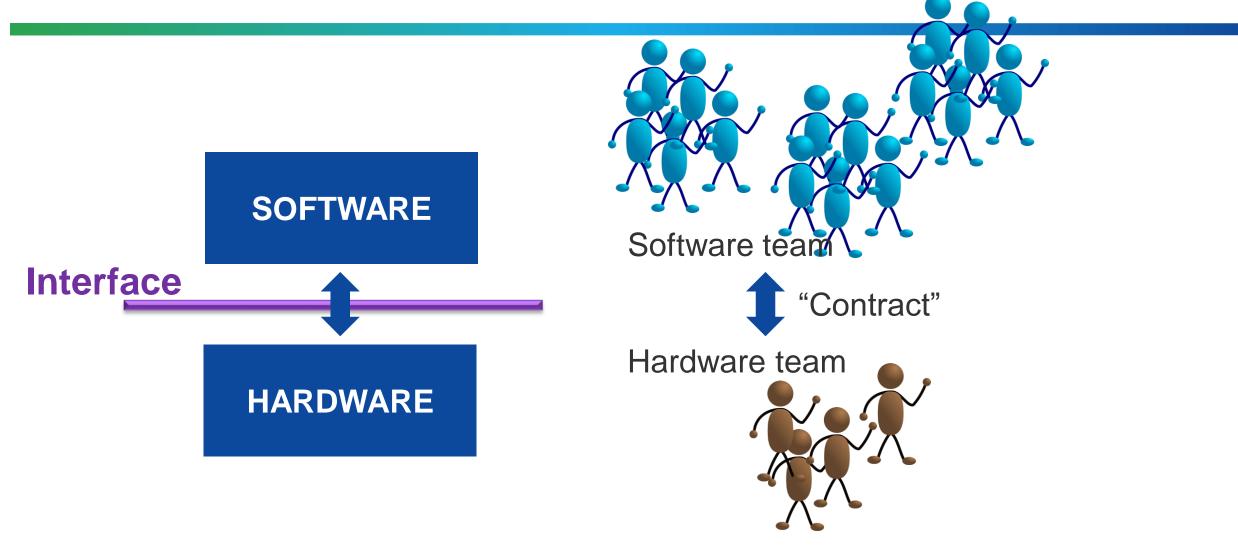

#### **Instruction Set Architecture (ISA)**

- A well-defined hardware/software interface

- The "contract" between software and hardware

- Functional definition of operations, modes, and storage locations supported by hardware

- Precise description of how to invoke, and access them

- Not in the "contract": non-functional aspects

- How operations are implemented

- Which operations are fast and which are slow and when

- Which operations take more power and which take less

#### **Instruction Set Architecture (ISA)**

### Why RISC-V for a SoC FPGA?

- The RISC-V ISA is Open. Open ISAs allow for …

- Low cost migration to ASICs, royalty free usage

- Innovation for custom architectures free "architectural license" doesn't restrict usage to fixed architectures

- The RISC-V ISA is simple. Simplicity ...

- Allows for a low power implementation

- Lower cost of ownership easier to learn, customize and debug

- Simple architectures are easier to secure against threats

#### **Open, Lowest Power, Cost Optimized, Programmable SoC**

### When does it make sense?

- Consider the following scenarios:

- 1. The existing design uses an FPGA and a separate microprocessor?

- Comparable functionality and performance, but lower board space, power, and cost by as much as 50% less

- 2. The current generation uses a proprietary ASIC that includes a microprocessor?

- No expensive mask charges or minimum purchase requirements

- Faster time to market with lower risk

- Adapt to changing markets requirements and emerging standards

- 3. A microprocessor being used today, but would benefit from a peripheral set more tailored to the application?

- If forced to accept compromises due to the lack of off-the-shelf processor derivatives

- The design can be differentiated both in hardware and software, making it more difficult for competitors to copy or emulate

## **Architecture Matters**

### **Criteria for Choosing an SoC FPGA**

- Design considerations & engineering trade-off decisions

- The selection criteria centers on the following areas:

- Existing ecosystem (legacy IPs, Software...)

- System performance

- System reliability

- System flexibility

- System cost

- Power consumption

- Continuity (product roadmap)

- Quality of the software solution (development tools)

### **System Performance**

- Industrial Example: Motor Control

- The processing must be deterministic (i.e. complete within a given window in time, every time)

### **System Performance**

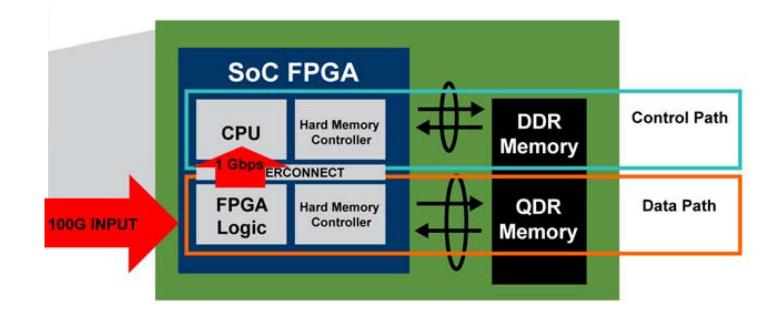

- The processor performance

- The fabric performance

- The interconnect between fabric and processor

- Memory bandwidth

Data transfer between the memory, FPGA fabric, processor, and peripherals

Microsemi. | а 🍄 Місвоснір company

Question: Does the interconnect support high throughput path?

Microsemi. a Microchip company

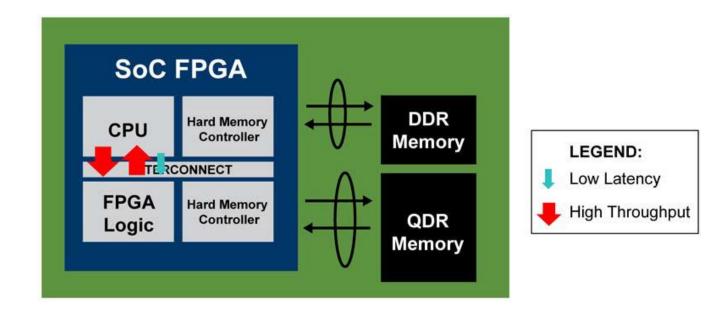

If needed, a low latency non-blocking bridge for allowing control access to the FPGA

- Hardware acceleration example: When the acceleration results are needed by the processor

- In this case, in the other direction: Does the architecture include an Accelerator Coherency Port (ACP)?

ARM Cortex-A9-based SoC FPGAs include a feature called an Accelerator Coherency Port (ACP). Through the ACP, new data produced by an FPGA-based hardware accelerator is transferred directly to the processor's L2 cache via a low-latency direct connection—not just quickly but coherently

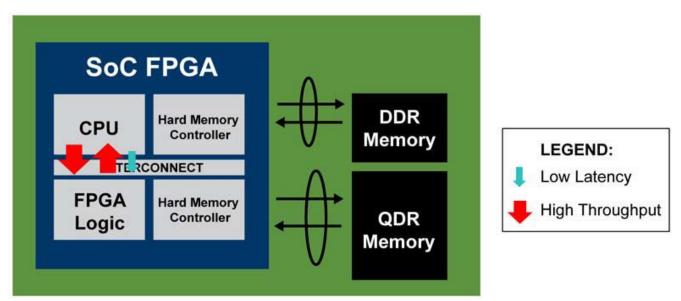

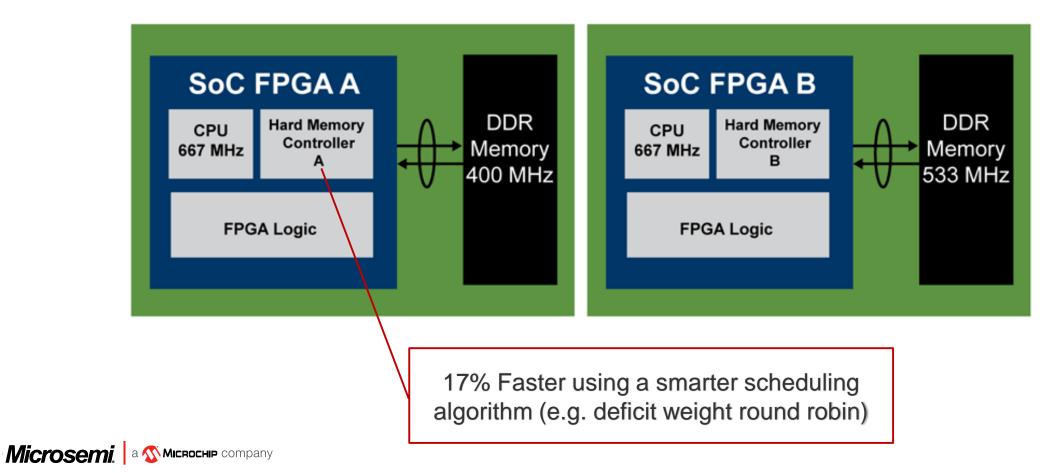

### System Performance Memory bandwidth

- Memory controllers are as important as the memory speed

- Question: Do you have separate hard memory controllers?

- Question: How smart is the memory controller?

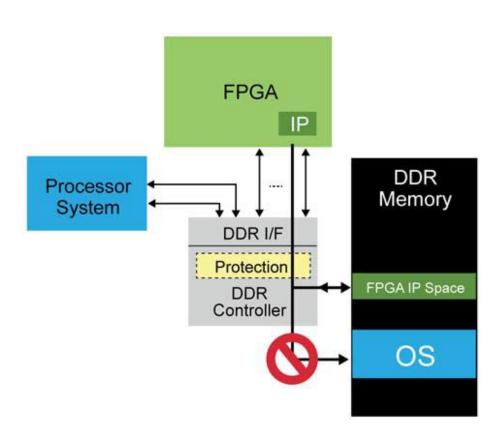

### **System Reliability**

- Supporting ECC Memory for content protection

- On-Chip RAM

- External DDR Memory Controller

- L1 Cache & L2 Cache

- SPI Controller

. . .

- DMA Controller

- 10/100/1G Ethernet Controller

- USB 2.0 OTG Controller

- Protection for shared memory

- Arm has the concept of "trust zone"

S Microsemi, a Microchip company

### **System Flexibility**

Extending the flexibility to the system level

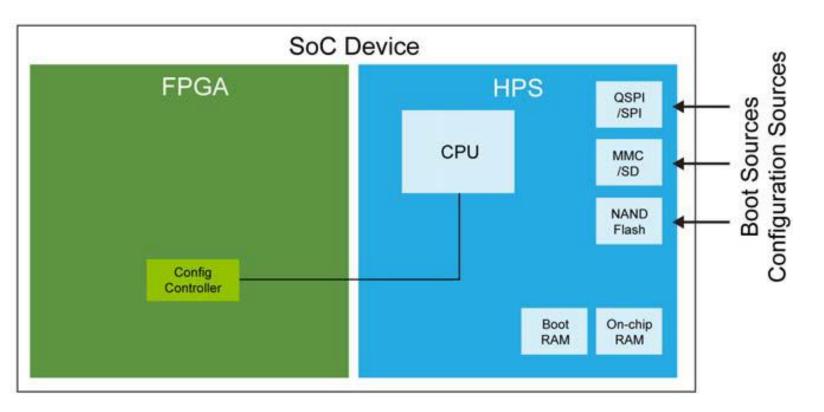

#### Processor boots first, then configures the FPGA

Service All A S

### **System Flexibility**

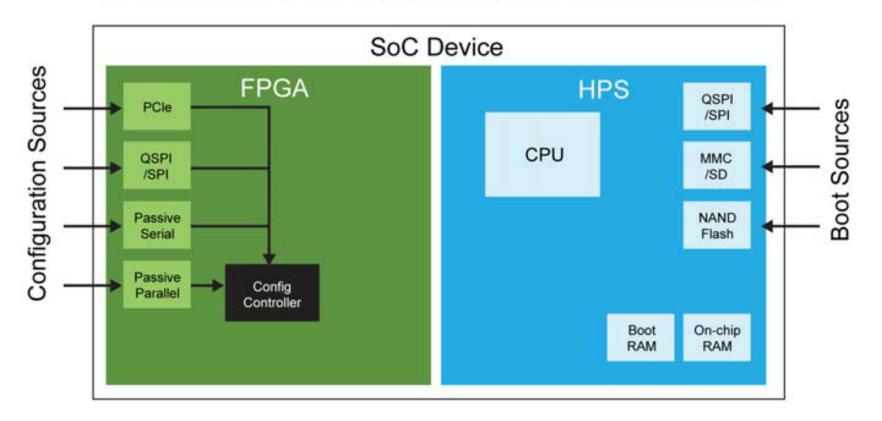

Extending the flexibility to the system level

#### Independent FPGA configuration and processor boot

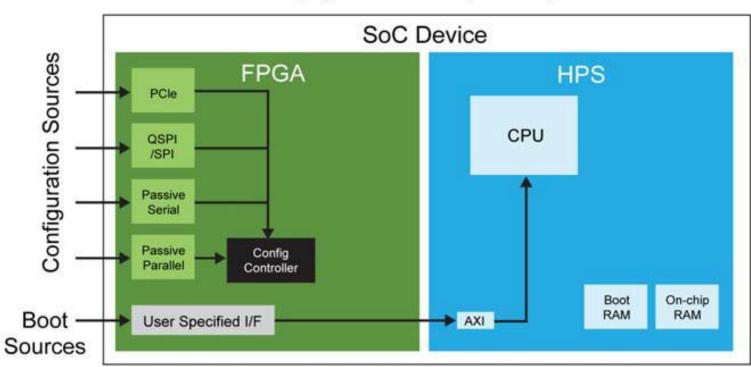

### **System Flexibility**

Extending the flexibility to the system level

FPGA configures first, CPU boot through FPGA logic

(e.g. custom backplane I/F)

### **Criteria for Choosing an SoC FPGA**

- Design considerations & engineering trade-off decisions

- The selection criteria centers on the following areas:

- Existing ecosystem (legacy IPs, Software...)

- System performance

- System reliability

- System flexibility

- System cost

- Power consumption

- Continuity (product roadmap)

- Quality of the software solution (development tools)

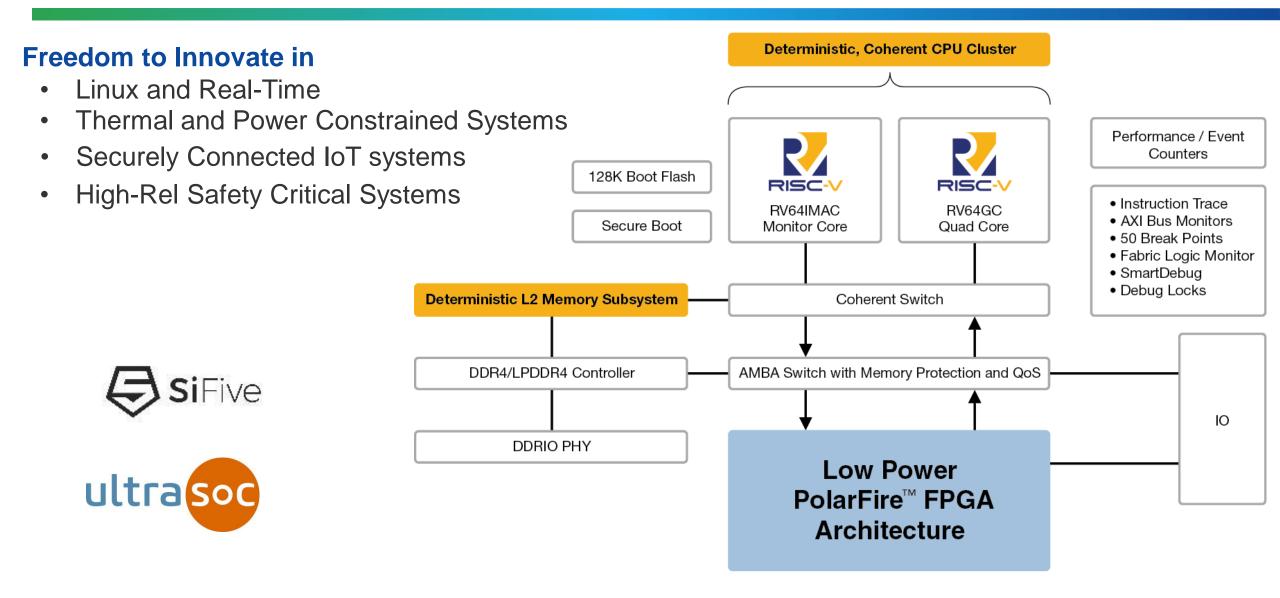

### **PolarFire SoC FPGA Architecture**

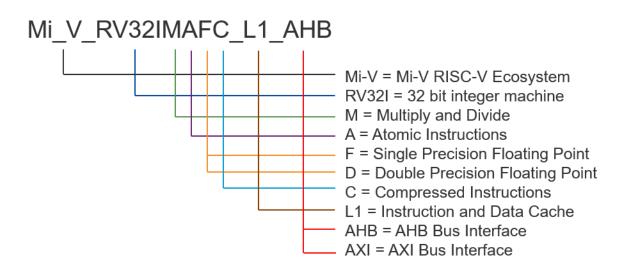

Mi-V: Microsemi's RISC-V Processor

### **PolarFire SoC FPGA**

Industry's First RISC-V SoC FPGA Architecture Brings Real-Time to Linux, Giving Developers the Freedom to Innovate in Low-Power, Secure and Reliable Designs

- First SoC FPGA with deterministic, coherent CPU cluster and a deterministic L2 memory subsystem enabling Linux + real-time applications

- First SoC FPGA architecture integrating a RISC-V processor subsystem and low-power FPGA technology

- PolarFire SoC FPGA with a mid-range low-power SoC FPGA and high levels of security and reliability

### **Freedom to implement RISC-V in hardware**

### Award Winning PolarFire FPGA as an SoC platform

#### Lowest Power

- Low static power technology •

- Power optimized transceivers ightarrow

- Up to 50% lower than SRAM **FPGAs**

10G Bridging & Aggregation

**Control Plane**

FPGA

- **Proven Security**

- Defense-grade security  $\bullet$

- DPA safe Crypto coprocessor  $\bullet$

- Built-in anti-tamper ightarrow

Video & Image Processing

C Microsemi

**POLARFIRE**

FPGA

Power Matters."

Signal Processing

Hardware Acceleration

**Low Power Optics**

#### **Exceptional Reliability**

- SEU immune configuration •

- Block RAM with ECC  $\bullet$

Microsemi | a 🏠 Microchip company

Extended temperatures

> **Portable** Equipment

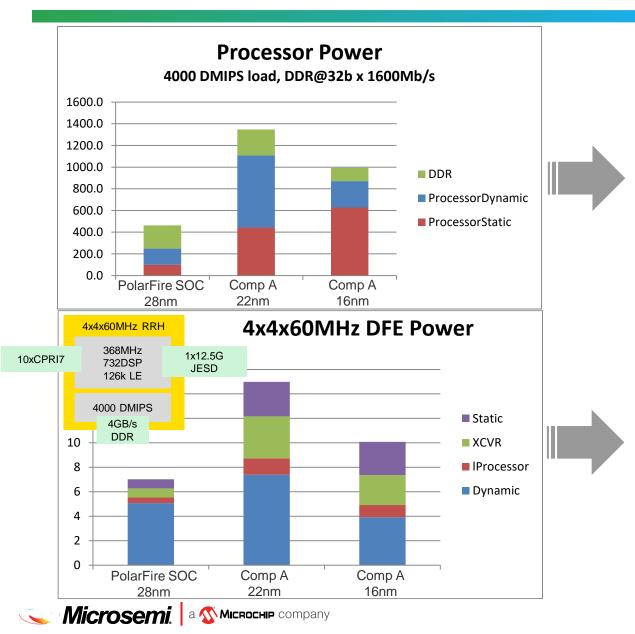

### Low Power: RISC-V MSS vs. Alternatives

#### **Low Power MSS**

Low power RISC-V micro-architecture 2MB L2 cache: increases cache hit/miss ratio 0.5-0.9W lower power Power-optimized transceivers

#### **LTE Digital Front End Application**

3-7W lower power for 60MHz 4x4 MIMO implementation

### **Security Ready for IoT**

- PolarFire SoC inherits <u>best in class</u> PolarFire FPGA Security

- DPA resistant bitstream programming

- Anti-tamper

- Cryptographical bound supply chain assurance

- Physically unclonable function

- True random number generator

- Side channel resistant crypto coprocessor

### PolarFire SoC has:

- + Secure Boot

- + Spectre and Meltdown immunity

- + Physical memory protection

- + SECDED on all memories (single-error correction and double-error detection)

### **Real-time Linux?**

- Wide spread Linux adoption

- Rich OS with thousands of applications to choose from

- Requirements still exist for real-time while running Linux

- Safety critical

- The ability to deterministically monitor the execution environment.

- Real-time system control

- Completing tasks deterministically, on time every time.

- Securing the IoT

- Execute a trusted execution environment deterministically for consistent results.

- Working with SiFive

Microsemi. | a SMicrochip company

- We have been able to architect a complex SoC FPGA that provides

- Determinism and a rich OS within the same multi-core CPU cluster

© 2018 Microsemi 59

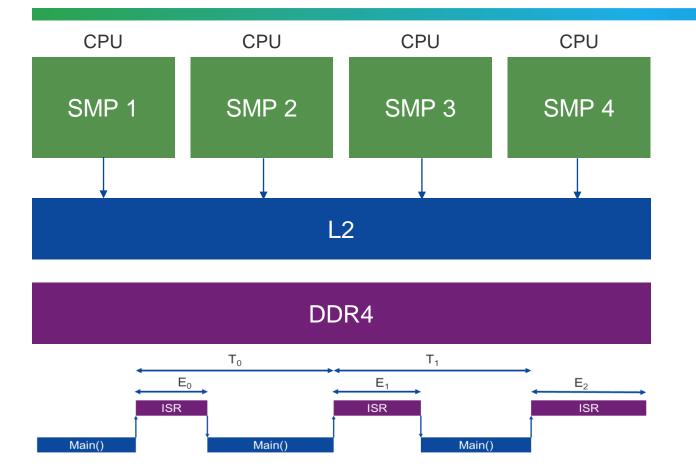

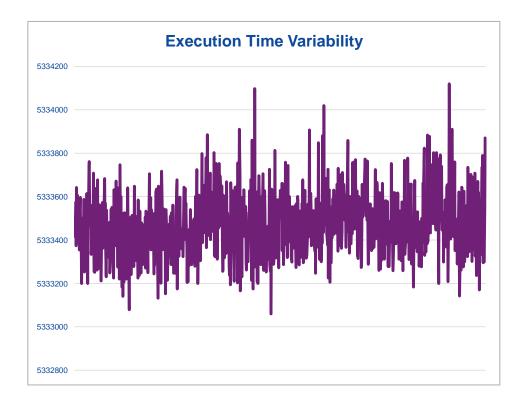

## **Variable Execution Time in Typical Application Processors**

- Periodic Interrupts

- $T_0 = T_1$

- Inconsistent Execution Times

- E<sub>0</sub> != E<sub>1</sub> != E<sub>2</sub>

Branch predictors, cache misses and lack of coherency affect determinism negatively

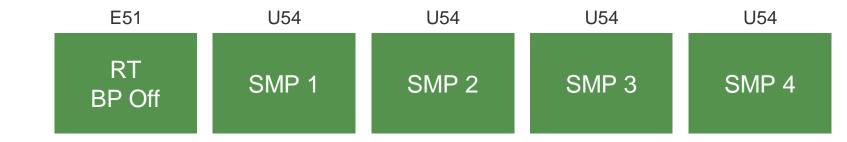

Turn off the CPU branch predictors

- Turn off the CPU branch predictors

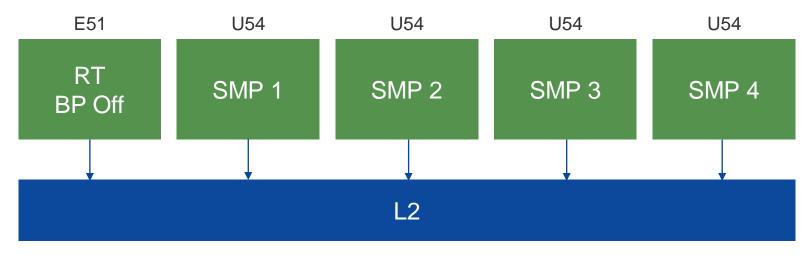

- Make sure all cores coherent to the memory subsystem

- Turn off the CPU branch predictors

- Make sure all cores coherent to the memory subsystem

- Make the memory system deterministic

DDR4

- Turn off the CPU branch predictors

- Make sure all cores coherent to the memory subsystem

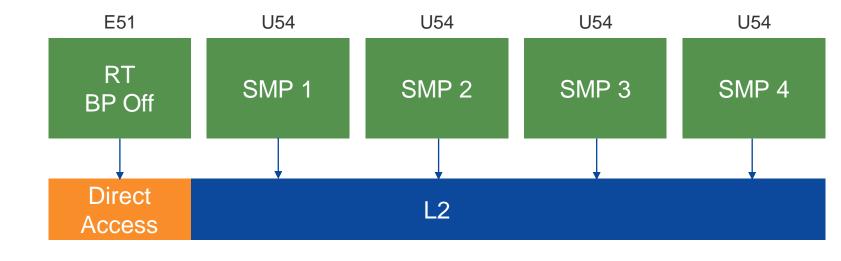

- Make the memory system deterministic

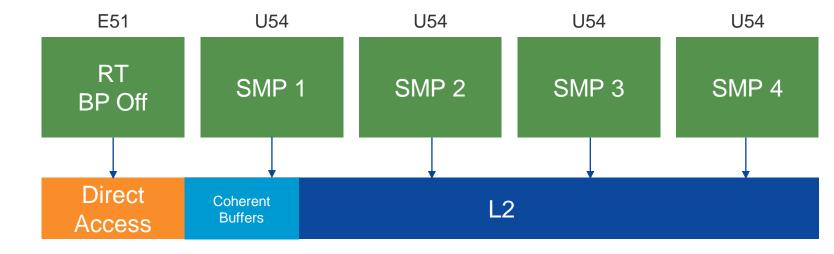

- Share coherent memory for message passing

- Turn off the CPU branch predictors

- Make sure all cores coherent to the memory subsystem

- Make the memory system deterministic

- Share coherent memory for message passing

- Linux and real time in a coherent memory subsystem

| RESULT                                        | E51              | U54                 | U54   | U54   | U54                 |  |

|-----------------------------------------------|------------------|---------------------|-------|-------|---------------------|--|

| No Execution Time Variability 5724000 5723800 | RT<br>BP Off     | SMP 1               | SMP 2 | SMP 3 | SMP 4               |  |

| 5723600                                       |                  |                     |       |       |                     |  |

| 5723400<br>5723200<br>5723000                 | Direct<br>Access | Coherent<br>Buffers | L2    |       |                     |  |

| 5722800                                       |                  |                     |       |       |                     |  |

| 5722600                                       |                  |                     |       | DDR4  |                     |  |

| міскоснір сотрапу                             |                  |                     |       |       | © 2018 Microsemi 65 |  |

### **PolarFire SoC - RISC-V enabled innovation platform**

Signal Alterochip company a 🔊 Міскоснір company

### **PolarFire SoC Summary**

- PolarFire FPGA Award Winning Features

- 30-50% Lower power

- Defense grade security

- Exceptional reliability

- Smallest, lowest power, secure form factors 11x11, 16x16, 19x19

- PolarFire Microprocessor Subsystem

- Linux and real time in a deterministic, coherent CPU cluster

- 30-50% Lower power

- Defense grade secure boot

- Spectre/Meltdown immune

- SECDED on all memories

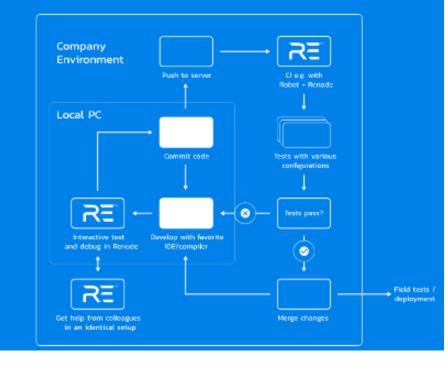

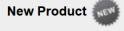

### Freedom to start software development

#### RENODE-BASED CONTINUOUS INTEGRATION WORKFLOW

# RENODE

- Free Rapid Software Development and Debug Capabilities Without Hardware

- Complete PolarFire SoC Processor Subsystem Model

Available now!

### Freedom to begin hardware development

#### **PolarFire SoC Embedded Experts Development Kit**

#### **HiFive Unleashed Expansion Board**

**HiFive Unleashed Development Board**

### Freedom to engage with the Mi-V Ecosystem

**New Mi-V Embedded Experts Network**

### **RISC-V CPUs**

| RISC-V Soft CPU              | LE'S | CoreMark Score | Cache Size | Mul/Div | Floating Point   | Availability |

|------------------------------|------|----------------|------------|---------|------------------|--------------|

| CORE_RISCV_AXI4*             | 10K  | 2.01           | 8K I and D | Yes     | N/A              | Now          |

| <u>Mi_V_RV32IMAF_L1_AHB*</u> | 26K  | 2.01           | 8K I and D | Yes     | Single Precision | Now          |

| <u>Mi_V_RV32IMA_L1_AHB</u> * | 10K  | 2.01           | 8K I and D | Yes     | N/A              | Now          |

| Mi_V_RV32IMA_L1_AXI*         | 10K  | 2.01           | 8K I and D | Yes     | N/A              | Now          |

\*Click the RISC-V Soft CPU to download the Handbook

Microsemi. a Microchip company

### **Summary**

- PolarFire SoC gives designers the freedom to create innovative low power systems by enabling Linux and deterministic architectures in novel ways

- First SoC FPGA with deterministic, coherent CPU cluster and a deterministic L2 memory subsystem enabling Linux + real-time applications

- First SoC FPGA architecture integrating a RISC-V processor subsystem and low-power FPGA technology

- PolarFire SoC addresses the industry's need for a mid-range low-power SoC FPGA with high levels

of security and reliability

- Developers can begin development today

- antmicro Renode platform for software development

- PolarFire SoC Embedded Experts Development Kit for hardware development

- New Mi-V Embedded Experts Network

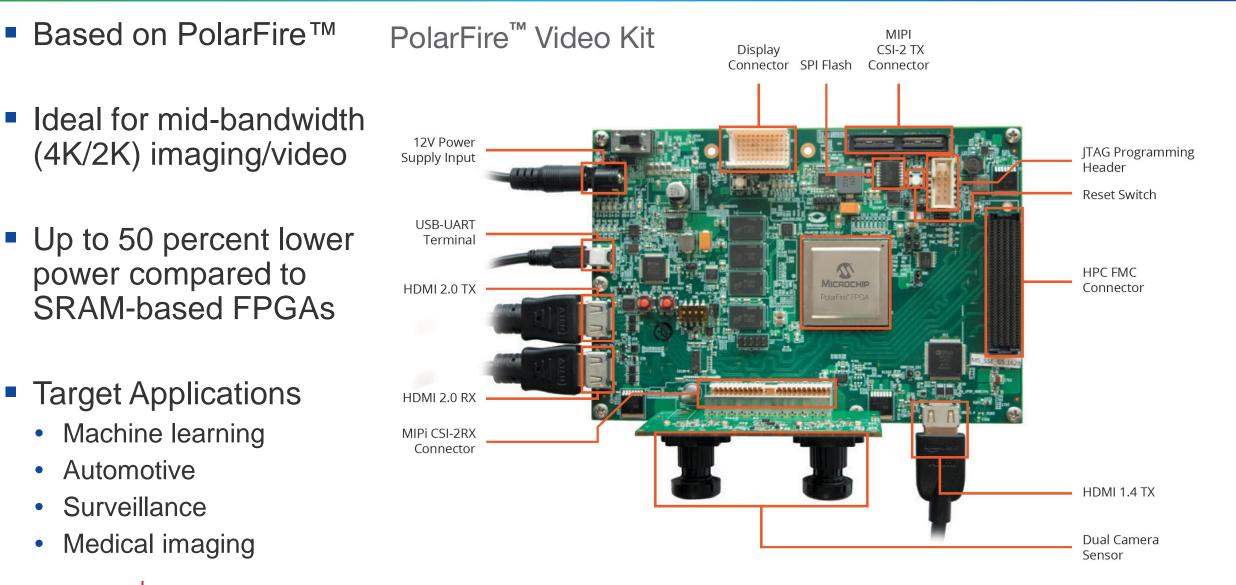

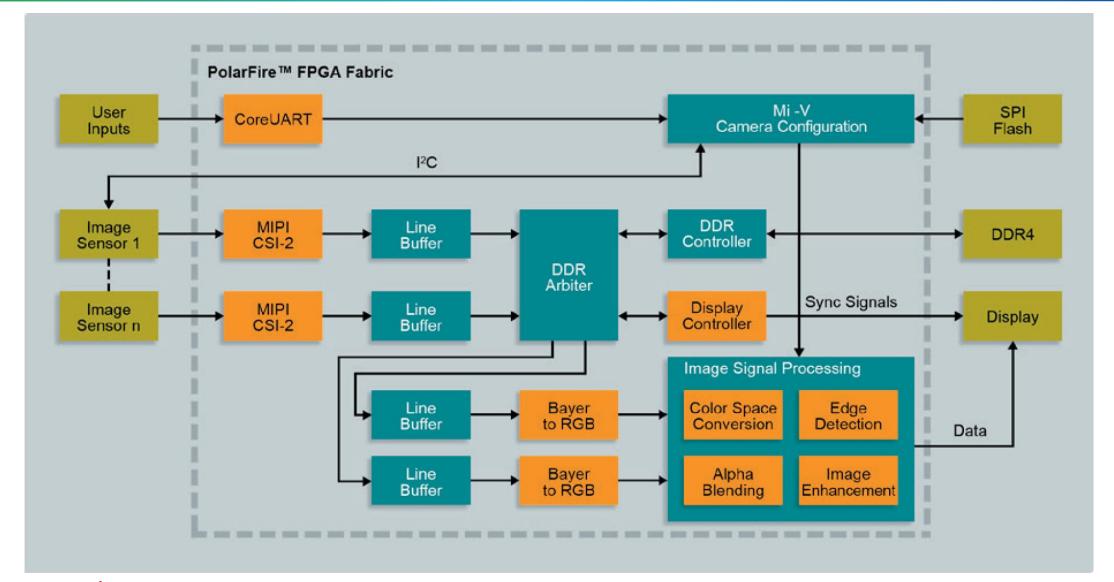

#### **PolarFire Dual Camera Video Kit**

Example using a soft RISC-V

### Imaging and Video Solutions for Smart Embedded Vision

Microsemi. a 🐼 Microchip company

| Feature                 | PolarFire <sup>™</sup>                                                                                              |  |

|-------------------------|---------------------------------------------------------------------------------------------------------------------|--|

| Performance             | <ul> <li>Tranceivers@12.7G, DDR4@1.6G, CSI-2 Rx@1.0G, LVDS@1.6G</li> <li>1657 GMAC/s Max DSP Performance</li> </ul> |  |

| Resolution              | Up to 4K (3840 x2160)<br>MIPI CSI-2 (RX, TX),HDMI 2.0 ,3G SDI,DSI                                                   |  |

| Protocol Support        |                                                                                                                     |  |

| Speed and Frame<br>Rate | <ul> <li>MIPI: RX at 4.8 Gbps (4 x 1.0 Gbps), TX at 3.2 Gbps (4x 800 Mbps)</li> <li>4K @ 30 fps</li> </ul>          |  |

#### **Board Components and Operations**

PF\_Dual\_Camera\_Video\_Kit\_Demo\Microsemi\_PolarFire\_FPGA\_Video\_Kit\_User Guide\_UG0856\_V1.pdf

| Product Overview                   |                                         | Price & Procurement                                                             |                            |     |  |

|------------------------------------|-----------------------------------------|---------------------------------------------------------------------------------|----------------------------|-----|--|

| Digi-Key Part Number               | 1100-1299-ND                            | Quantity                                                                        | 1                          |     |  |

| Quantity Available                 | 11<br>Can ship immediately              | 1100-129                                                                        | 99-ND                      | ~   |  |

| Manufacturer                       | Microsemi Corporation                   | Customer                                                                        | Customer Reference         |     |  |

| Manufacturer Part Number           | MPF300-VIDEO-KIT                        |                                                                                 | Add to C                   | art |  |

| Description                        |                                         |                                                                                 | 6                          |     |  |

| Manufacturer Standard Lead<br>Time | 8 Weeks                                 | Price Bre                                                                       | ak Unit Pric<br>1,078.8000 |     |  |

| Detailed Description               | MPF300 PolarFire™ FPGA Evaluation Board | Submit a <u>request for quotation</u> on quantice greater than those displayed. |                            |     |  |

| Documents & Media |                                                                                                                                                                                    |  |  |  |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Datasheets        | PolarFire FPGA Video Kit Guide<br>Imaging, Video Solutions for Smart Embedded Vision<br>PolarFire Dual Camera Video Kit Demo Guide<br>PolarFire Video, Imaging Kit Quickstart Card |  |  |  |

| Featured Product  | MPF300-VIDEO-KIT Imaging Kit                                                                                                                                                       |  |  |  |

| Online Catalog    | PolarFire Evaluation Kits                                                                                                                                                          |  |  |  |

#### How do you make a design with a Mi-V

### How do you make a design with a Mi-V

- The design suite is called Libero SoC

- You can run through a full design flow, from synthesis to programming your device

- Libero includes the firmware catalog to create drivers for IP cores

# How do you write a program and run it on the Mi-V

- Softconsole Eclipse IDE required for the development

- Runs on Windows and Linux

- Eclipse-based IDE (Integrated Development Environment)

- Uses OpenOCD and GDB for debugging

- Comes bundled with several sample projects

- Most common demo is called "Blinky" which demos UART, GPIO and Interrupts

- If running correctly, the LEDs on the device should blink on and off, and when the project is first run, it will send a "hello" message over UART

- Softconsole has a built-in terminal emulator

- Resources at github.com/riscv-on-Microsemi-fpga

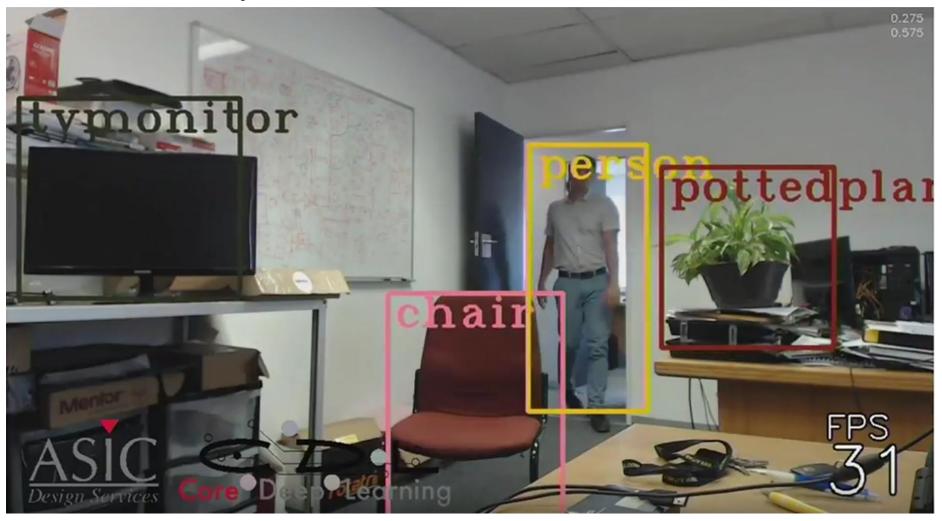

# **Another Example (ASIC Design Services)**

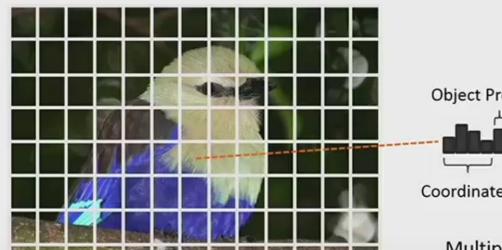

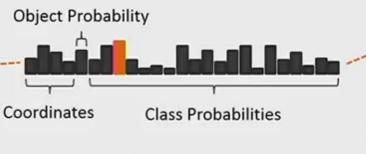

#### Tiny-YOLOv2

- Fully Convolutional Neural Network 9 Convolutional Layers

- convolution operation + batch normalisation + activation + pooling

- Trained end-to-end on Pascal VOC dataset

- Quantized and finetuned from provided base network by Joseph Redmon

- Tiny YOLO @ https://pjreddie.com/darknet/yolo/

#### Core Deep Learning an embedded FPGA solution

Multiple predictions per grid location

# **Another Example (ASIC Design Services)**

#### PolarFire + Mi-V in Tiny Yolo Video