Advanced Workshop on Modern FPGA-Based Technology for Scientific Computing

# Vivado Design Flow for SoC

Cristian Sisterna

Universidad Nacional de San Juan

Argentina

### Why Vivado Design Suite?

#### Larger FPGAs lead to more difficult design issues

- Users integrating more functionality into the FPGA

- Use of multiple hard logic objects (block RAMs, GTs, DSP slices, and microprocessors, for example)

- I/O and clock planning critical to FPGA performance

- Higher routing and utilization density

- Complex timing constraints with designs that have multiple clock domains

#### FPGA designs are now looking like ASIC platform designs

- Assembled from IP cores—commercial or developed in-house

- Maintaining place and route solutions is very important (this is resolved with the use of partitions)

- Bottom-up design methodology

- Team design flows becoming a necessity

Vivado Design Suite provides solution to all of the above

#### Vivado IDE Solution

#### Interactive design and analysis

Timing analysis, connectivity, resource utilization, timing constraint analysis

#### RTL development and analysis

- Elaboration of HDL

- Hierarchical exploration

- Schematic generation

#### **XSIM** simulator integration

Synthesis, implementation and simulation in one package

#### I/O pin planning

Interactive rule-based I/O assignment

Hierarchical Design Analysis and Implementation Environment

#### Vivado Visualization Features

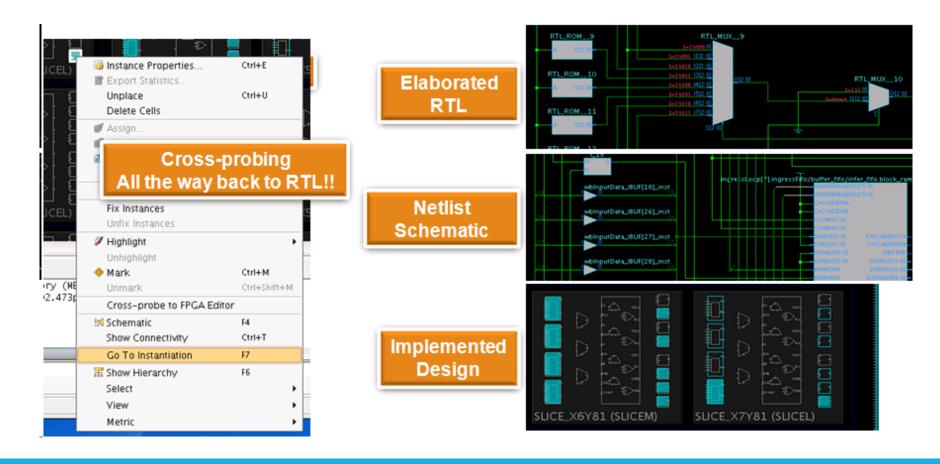

#### Visualize and debug a design at any flow stage

Cross-probing between netlist/schematic/RTL

## Gain Faster Timing Closure

#### Analyze multiple implementation results

- Highlight failing timing paths from post-route timing analysis

- Quickly identify and constrain critical logic path

#### Connectivity display

I/Os, net bundles, clock domains

#### Hierarchical floorplanning

Guide place & route toward better results

#### Utilization estimates

- All resource types shown for each Pblock

- Clocks or carry chains

### Tool Command Line (.tcl) Features

- \* Tcl Console enables the designer to actively query the design netlist

- Full Tcl scripting support in two design flows

- Project-based design flow provides easy project management by the Vivado IDE

- Non-project batch design flow enables entire flow to be executed in memory

- Journal and log files can be used for script construction

# Vivado Design Suite Introduction

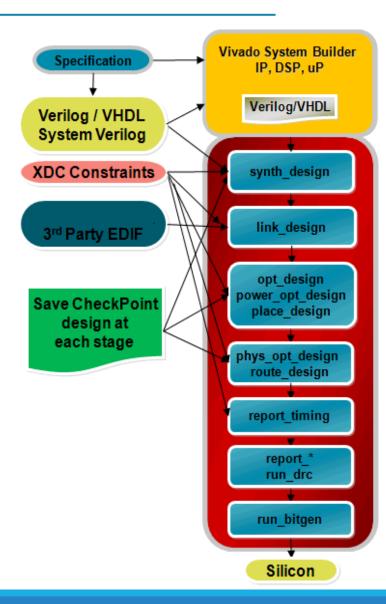

# Typical vs Vivado Design Flow

- ✓ Interactive IP plug-n-play environment

- ✓ AXI4, IP\_XACT

- ✓ Common constraint language (XDC) throughout flow

- √ Apply constraints at any stage

- ✓ Reporting at any stage

- ✓ Robust Tcl API

- ✓ Common data model throughout the flow

- √"In memory" model improves speed

- ✓ Generate reports at all stages

- **✓** Save checkpoint designs at any stage

- ✓ Netlist, constraints, place and route results

System Planning and HDL Design

**RTL Synthesis**

Netlist Linking and Constraints

Packing, Placement, Optimization

Routing, Post-Route Optimization

> Static Timing Analysis

DRC and Bitstream Generation

### Project Data and Directories

All project data is stored in a *project\_name* directory containing the following directories

- project\_name.xpr file: Object that is selected to open a project (Vivado IDE project file)

- project\_name.runs directory: Contains all run data (synthesis, implementation)

- project\_name.srcs directory: Contains all imported local HDL source files, netlists, and XDC files

- project\_name.data directory: Stores floorplan and netlist data

### Journal and Log Files

#### Journal file (vivado.jou)

Contains just the Tcl commands executed by the Vivado IDE

#### Log file (vivado.log)

Contains all messages produced by the Vivado IDE, including Tcl commands and results, info, warning, error messages, etc.

#### Location

- Linux: directory where the Vivado IDE is invoked

- Windows via icon: %APPDATA%\Xilinx\Vivado or

C:\Users\<user\_name>\AppData\Roaming\Xilinx\Vivado

10

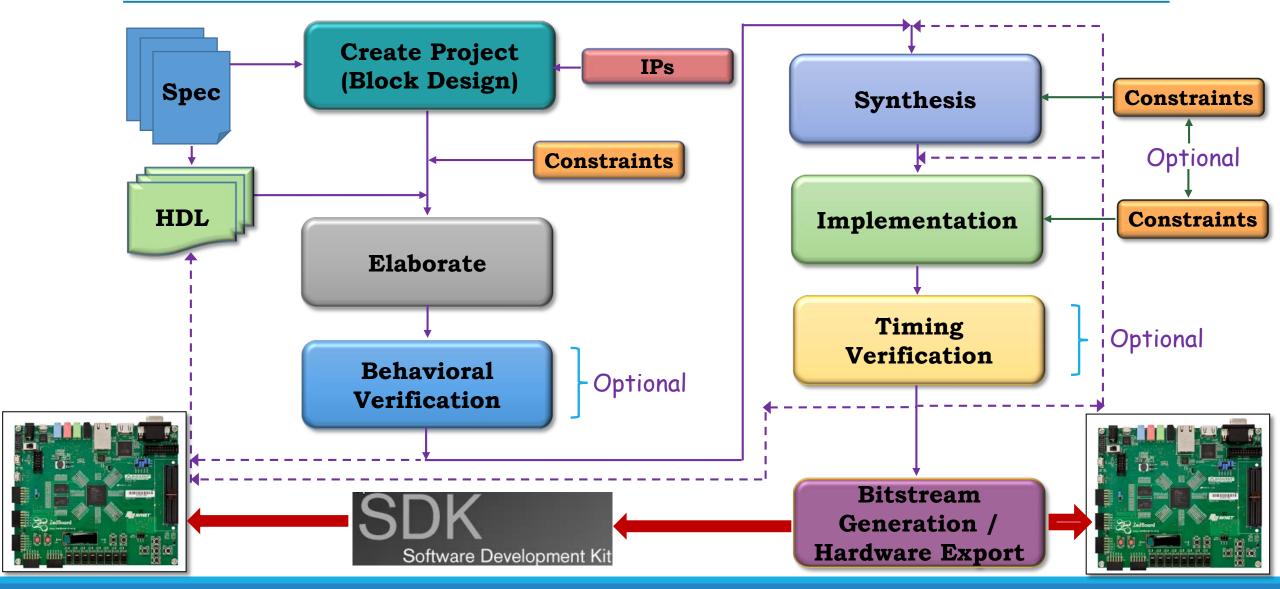

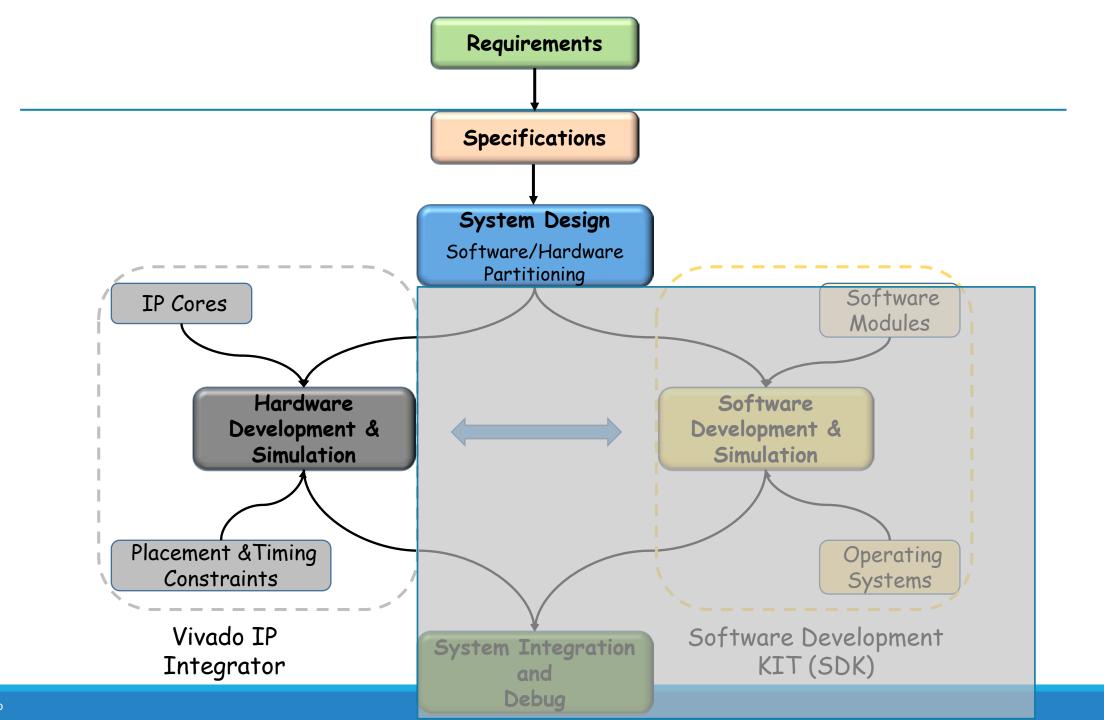

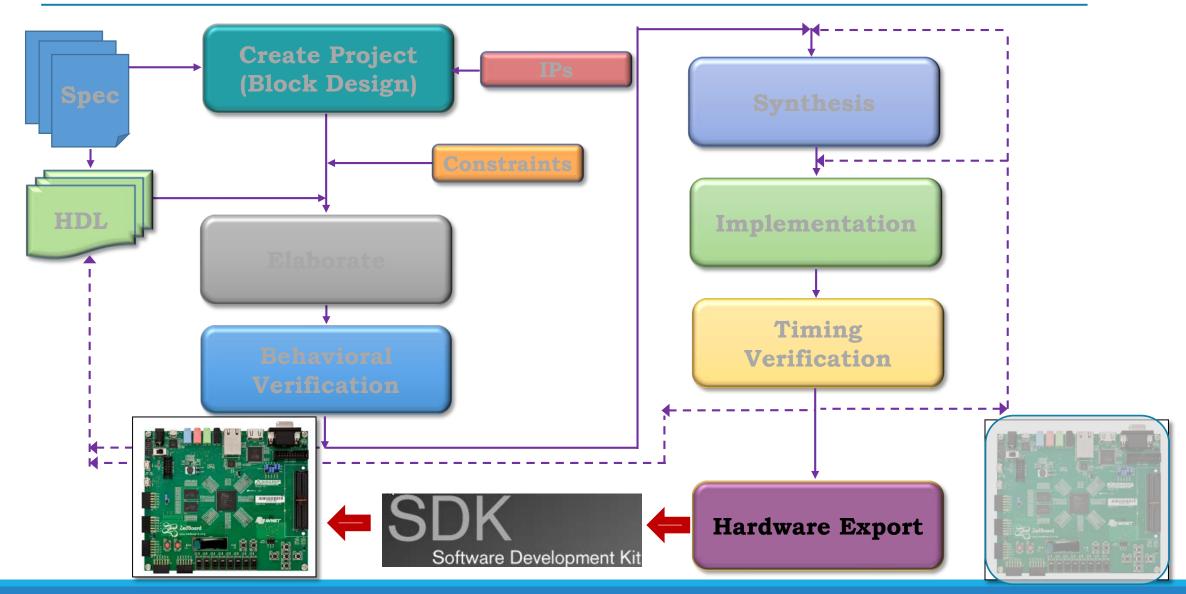

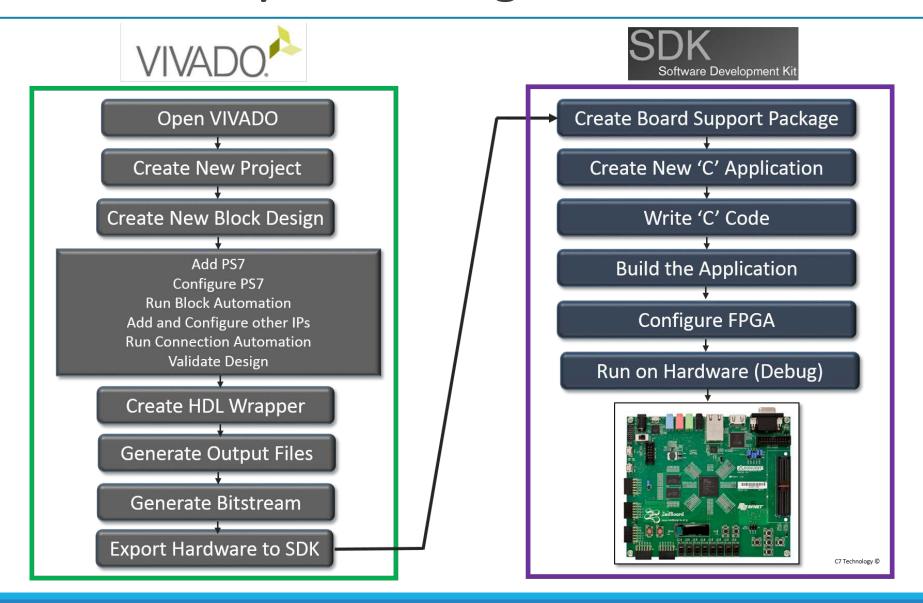

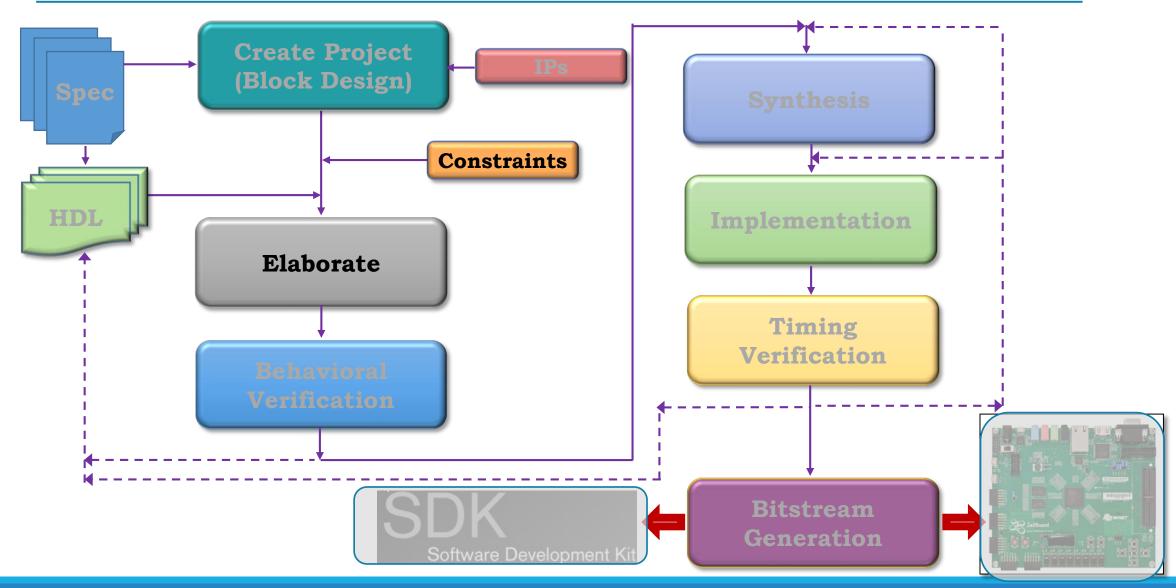

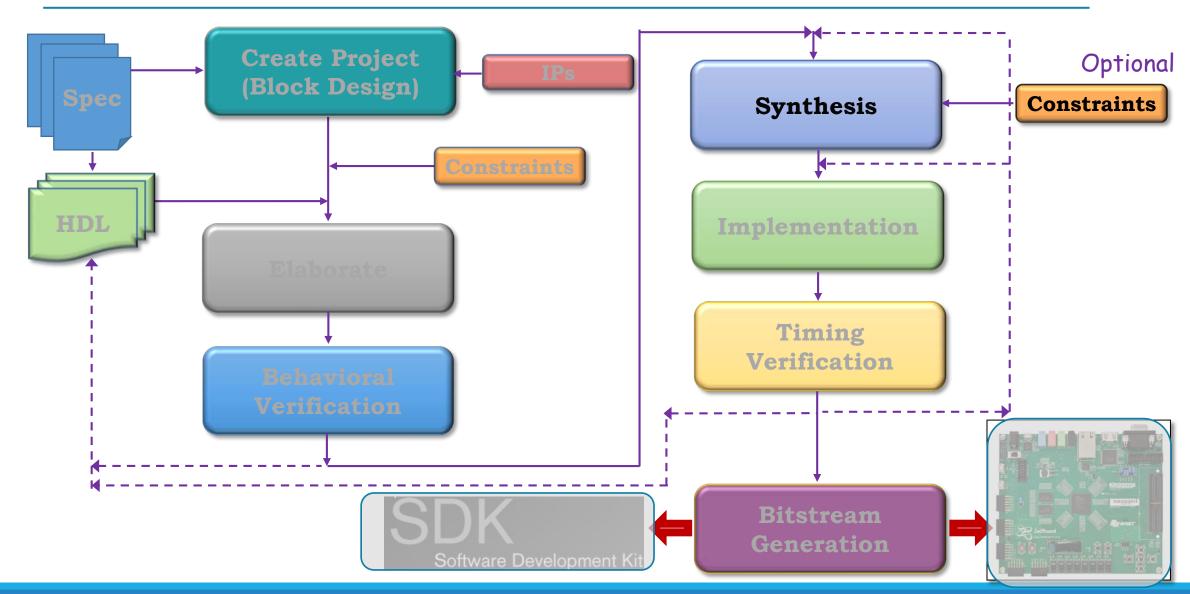

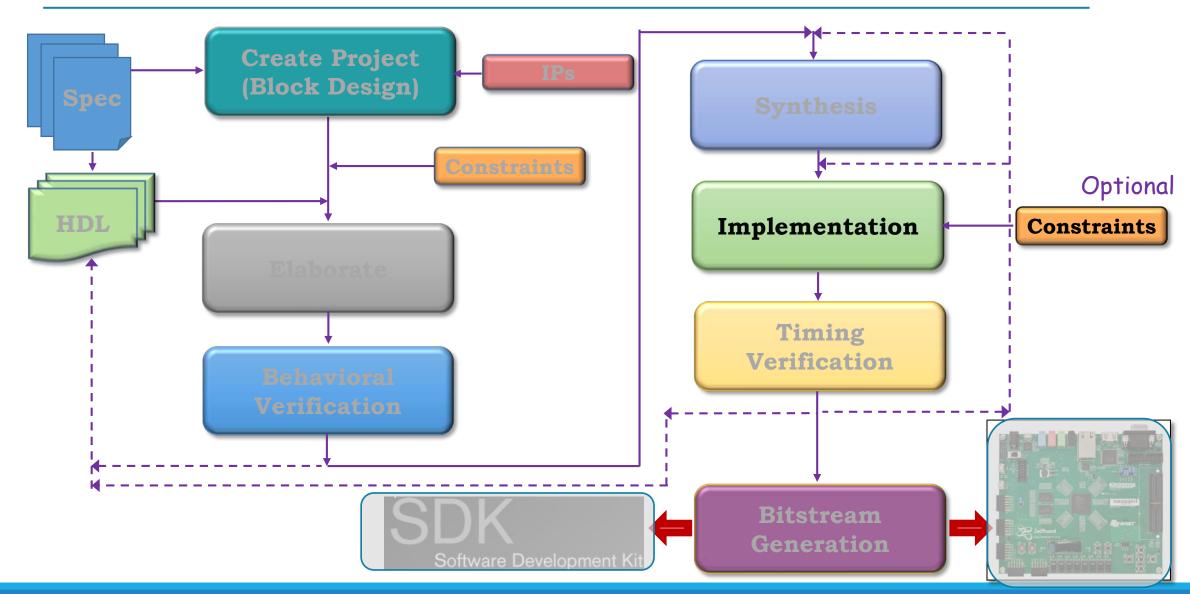

### Embedded System Design – Vivado Flow

# Vivado Flow Practical Steps

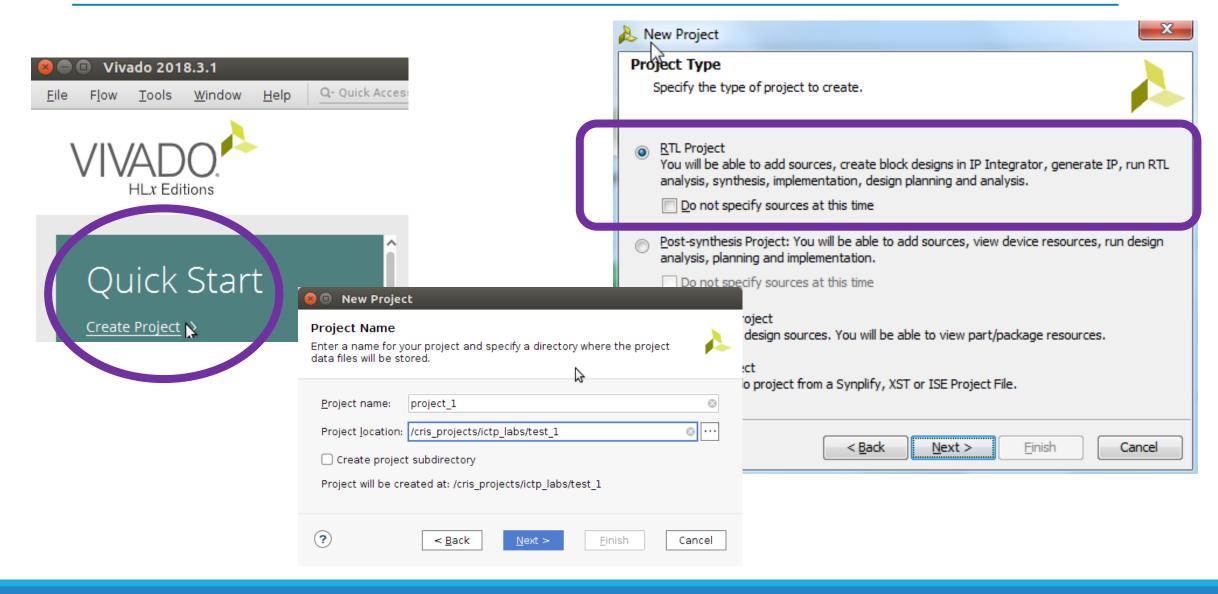

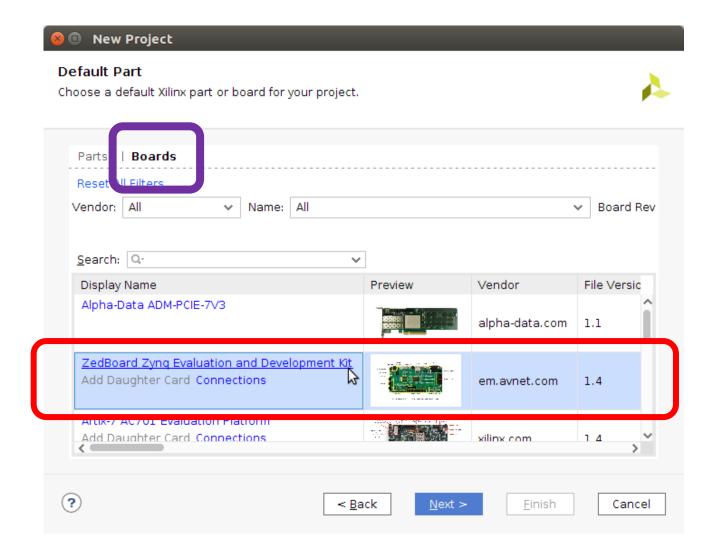

### Creating a Project

### Creating a Project

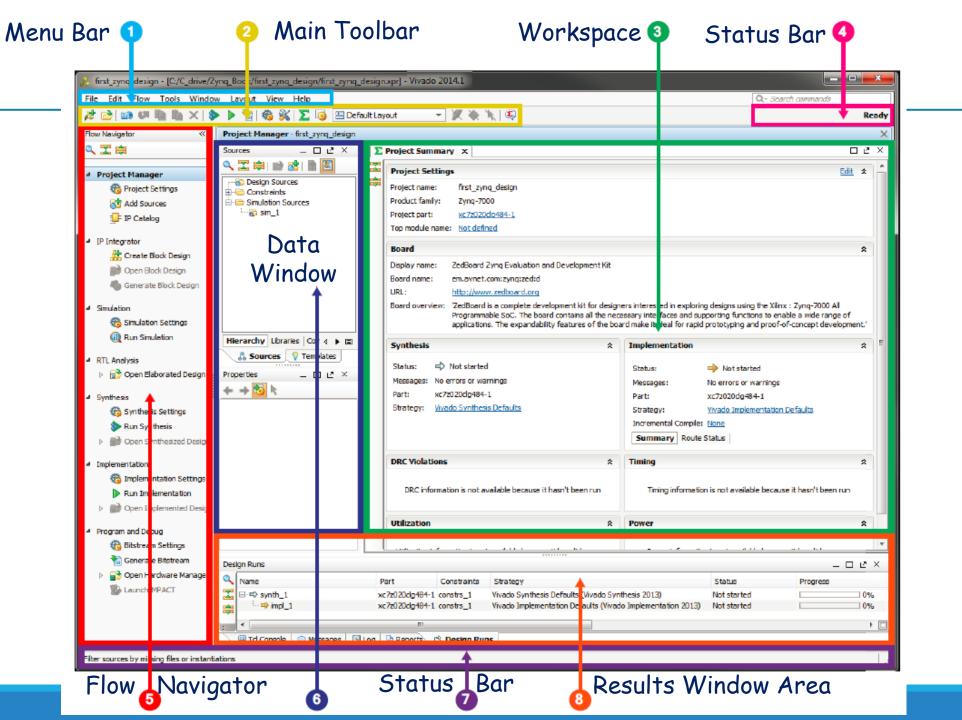

### Main Components of the Project Navigator

- 1. Menu Bar: Vivado IDE commands

- 2. Main Toolbar: Access to the most commonly used Vivado IDE commands

- **3. Workspace**: area for schematic panel, device panel, package panel, text editor panel.

- 4. Project Status Bar: displays the status of the currently active design

- **5. Flow Navigator**: provide easy access to the tools and commands necessary to guide the design from start to finish.

- **6. Data Window Pane**: by default displays information that relates to design data and sources, such as Property Window, Netlist Window, and Source Window

- **7. Status Bar**: displays information about menu bar and toolbar commands; task progresses

- **8. Results Window Area**: there are a set of windows, such as Messages, showing message for each process, Tcl Console, Tcl commands of each activity, Reports, reports generated throughout the design flow, Desing Runs, display the different run for the current project

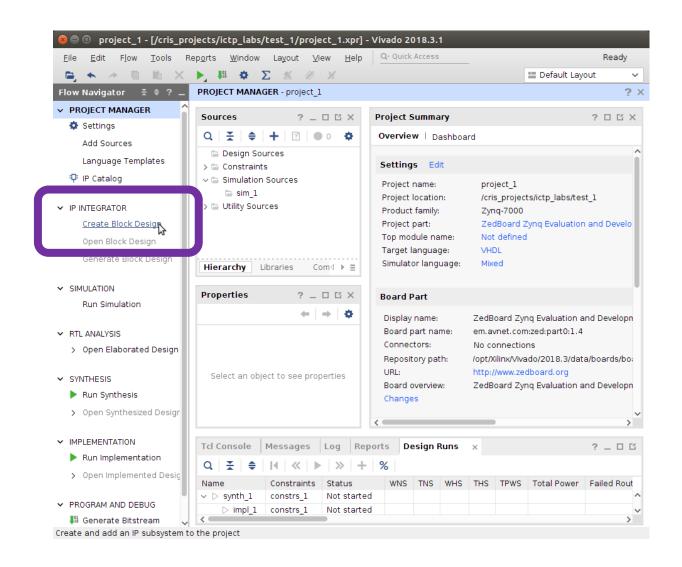

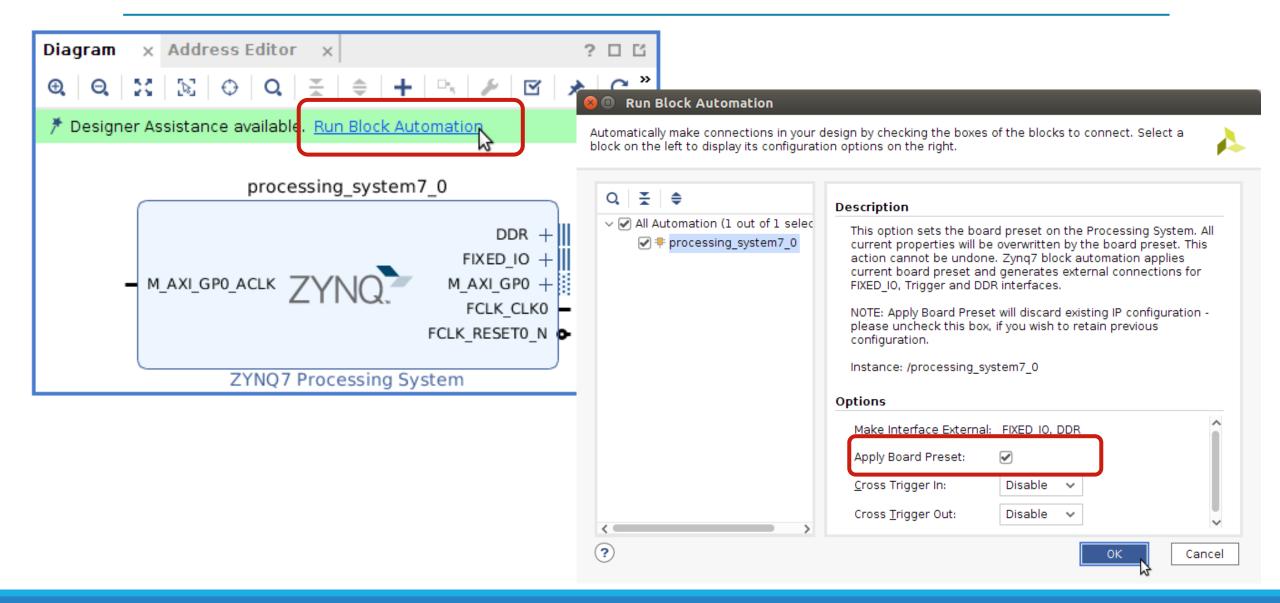

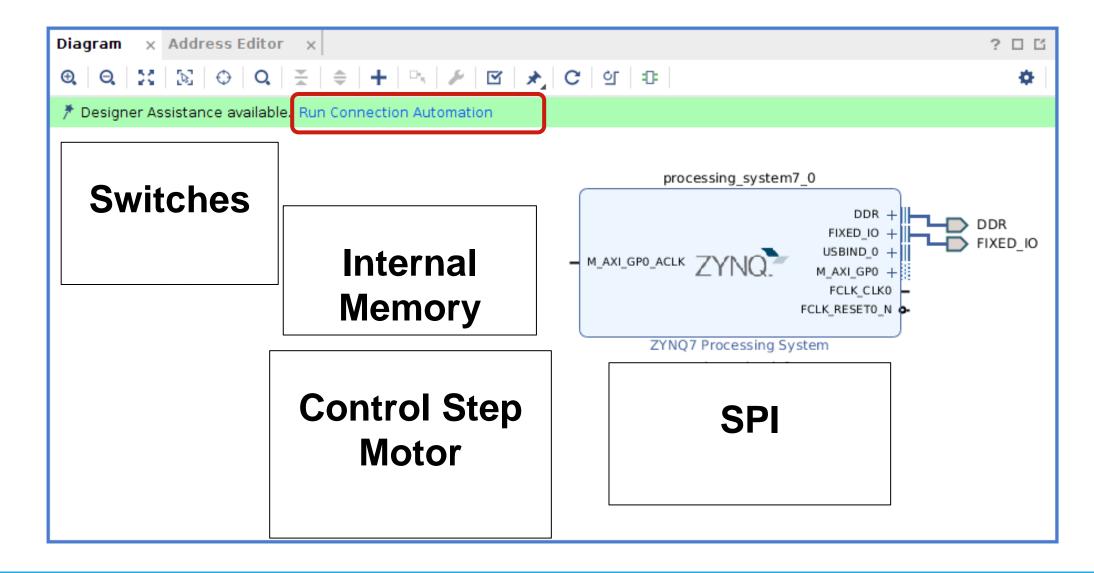

### Create a Block design

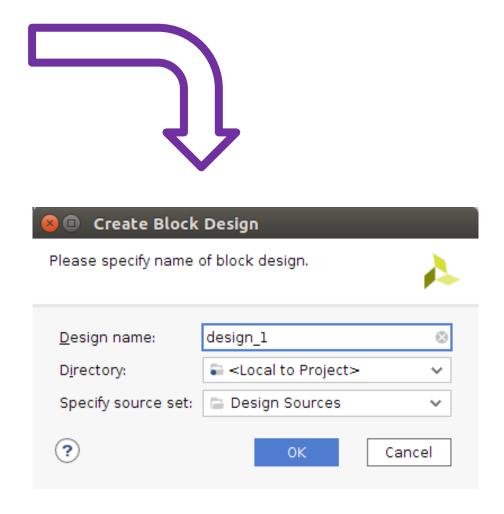

## Adding IP Modules to the Design Canvas

desired IP (Ctrl+Click) and press the Enter key.

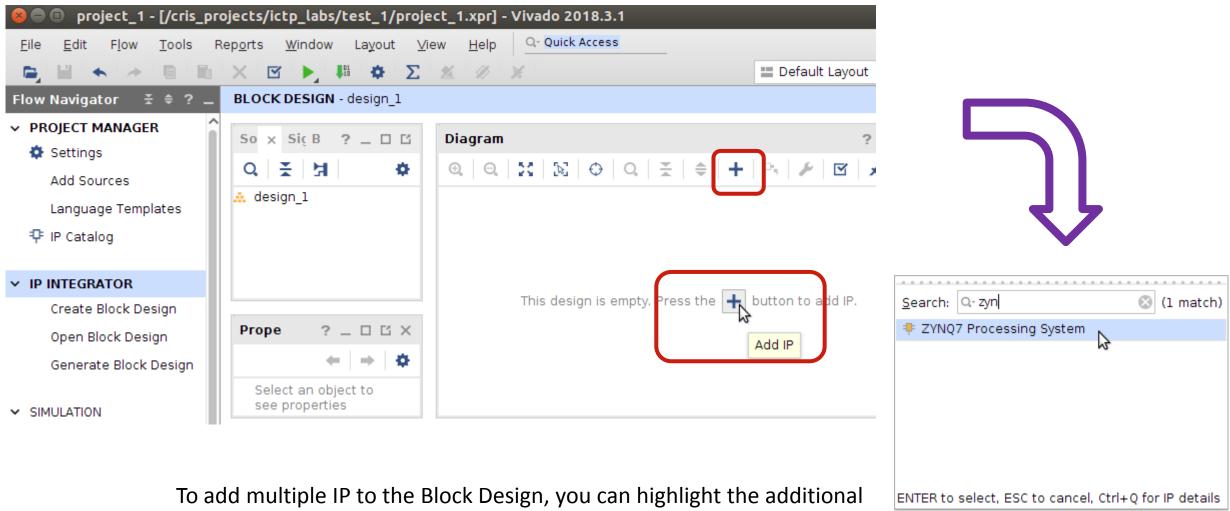

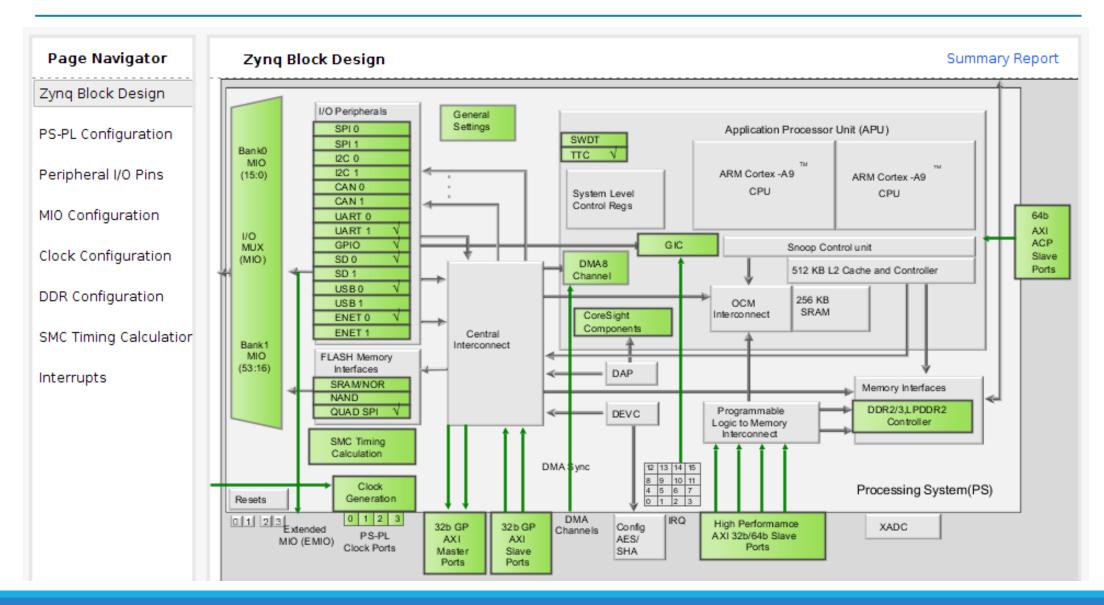

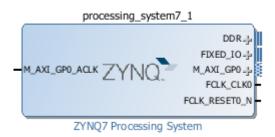

## Processing System (PS)

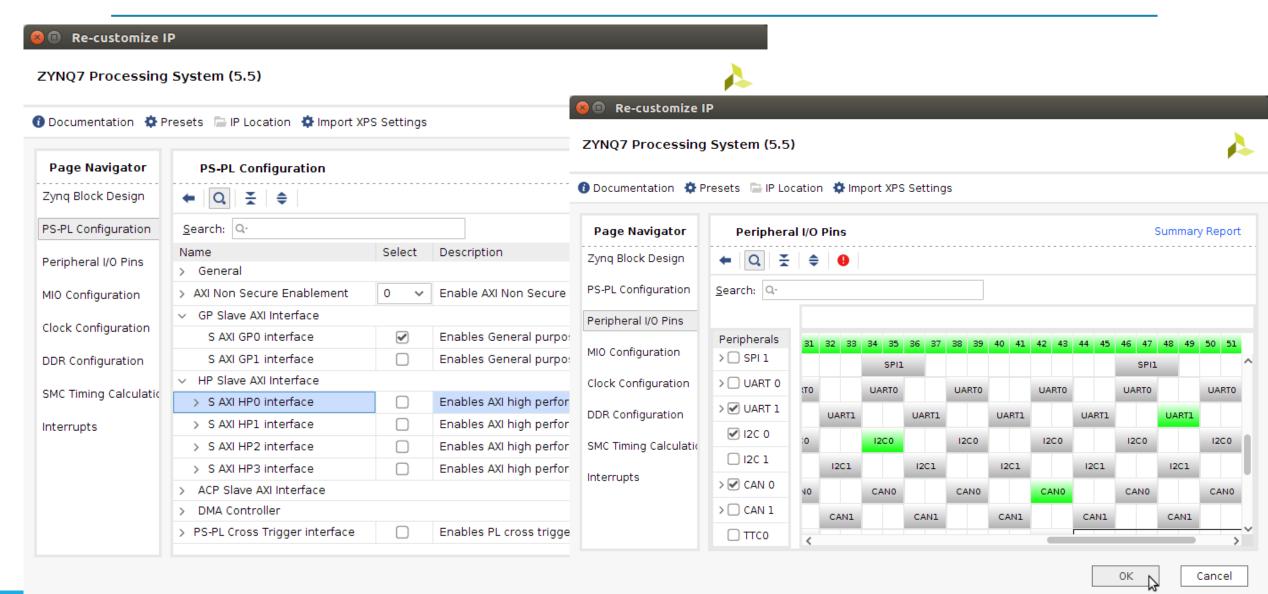

# Configuring the PS

## Configuring the PS

22

## Making Up the System

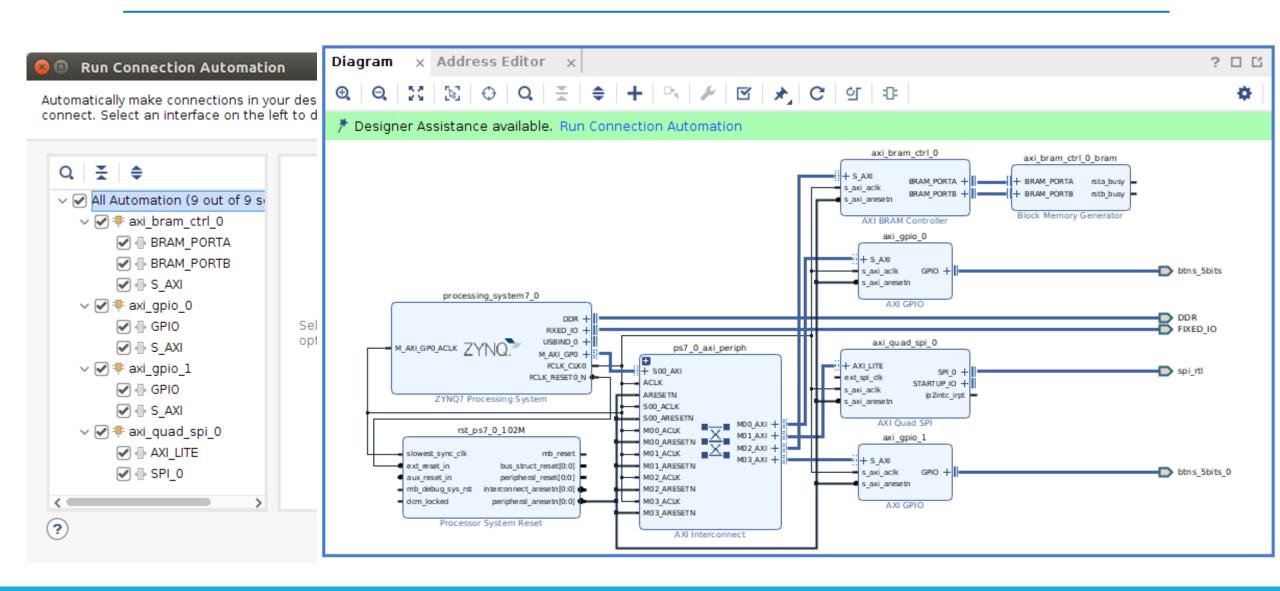

## **Running Connection Automation**

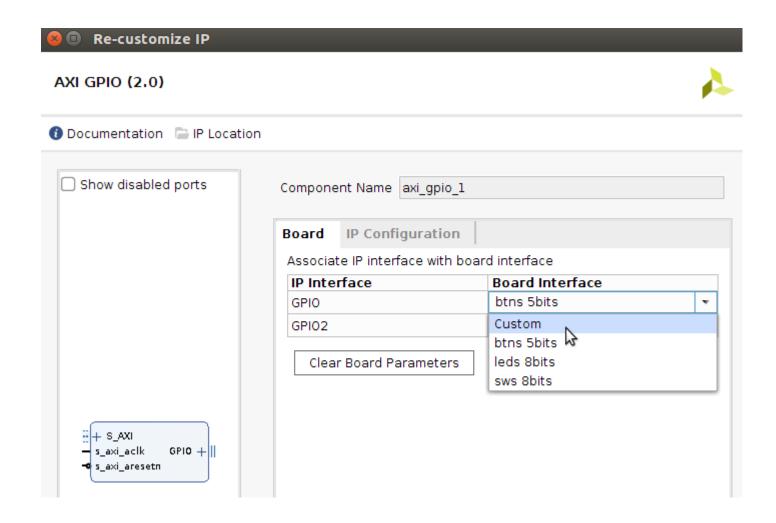

#### **Custom GPIO**

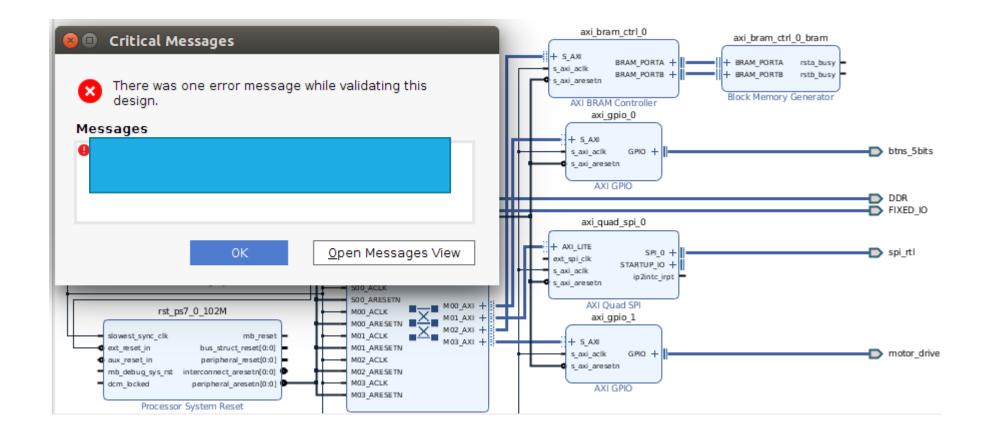

## DRC (Desing Rule Check) Design Validation

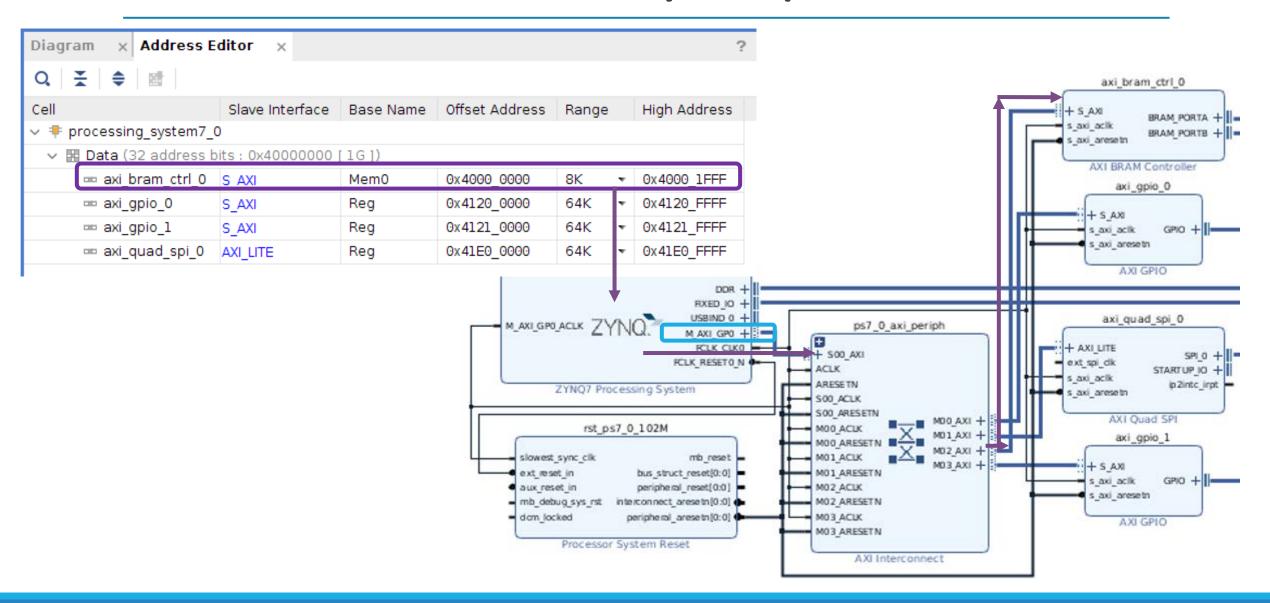

### Memory Map

27

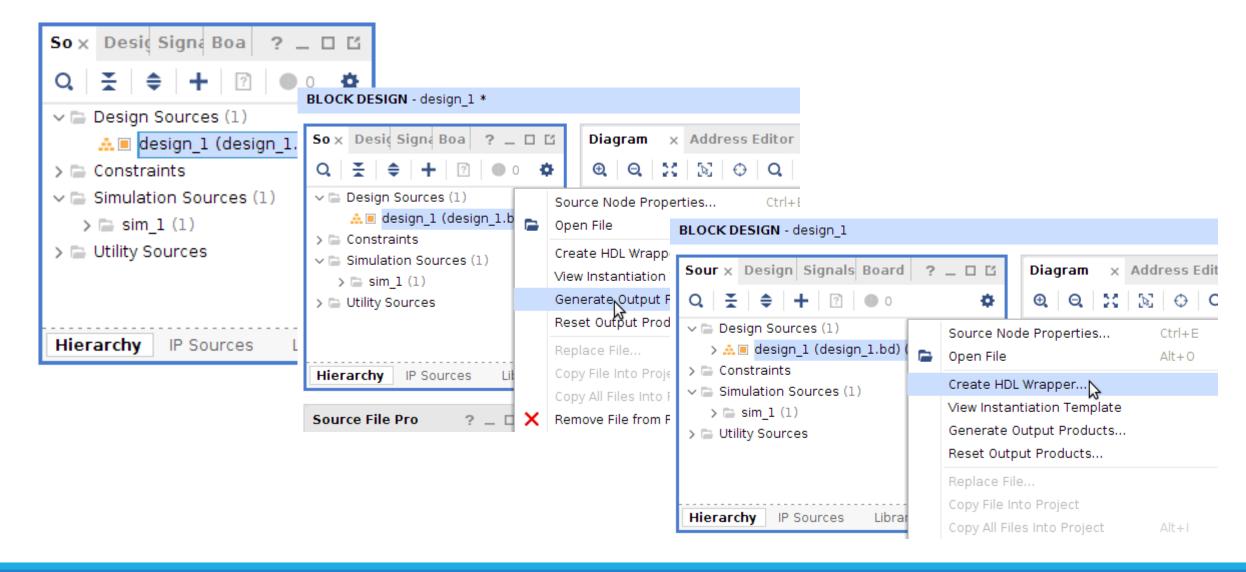

### Getting the System Ready to be Implemented

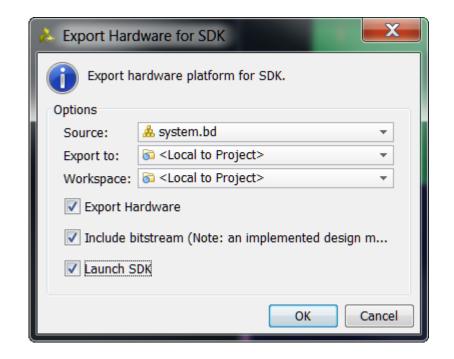

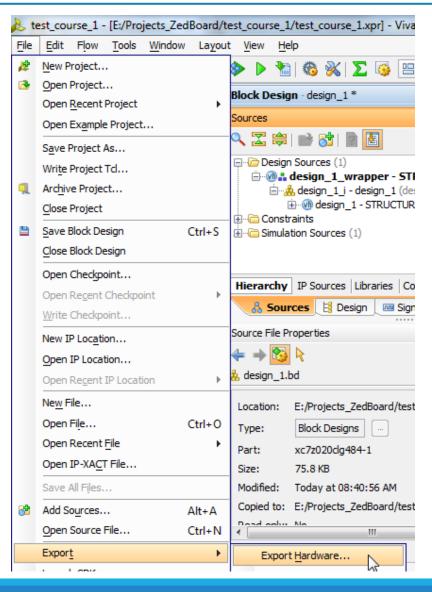

### **Export Hardware Design to SDK**

Software development is performed with the Xilinx Software Development Kit tool (SDK)

The design must be opened if a bitstream of the design is generated

The Block design must be open before the design can be exported

An XML description of the hardware is imported in the SDK tool

- The hardware platform is built on this description

- Only one hardware platform for an SDK project

The SDK tool will then associate user software projects to hardware

# Software Development Kit (SDK)

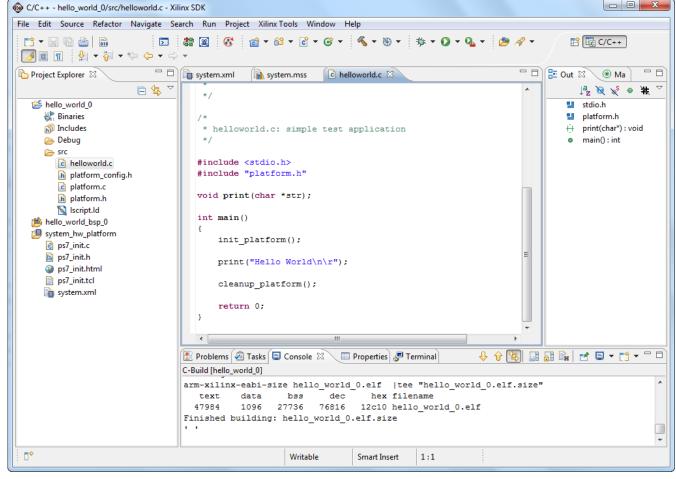

#### Embedded System Design – Vivado-SDK Flow

#### Embedded System Design – Vivado-SDK Flow

### Embedded System Tools: Software

#### Eclipse IDE-based Software Development Kit (SDK)

- Board support package creation : LibGen

- GNU software development tools

- C/C++ compiler for the ARM Cortex-A9 processor (gcc)

- Debugger for the ARM Cortex-A9 processor (gdb)

#### Board support packages (BSPs)

- Stand-alone BSP

- Free basic device drivers and utilities from Xilinx

- NOT an RTOS

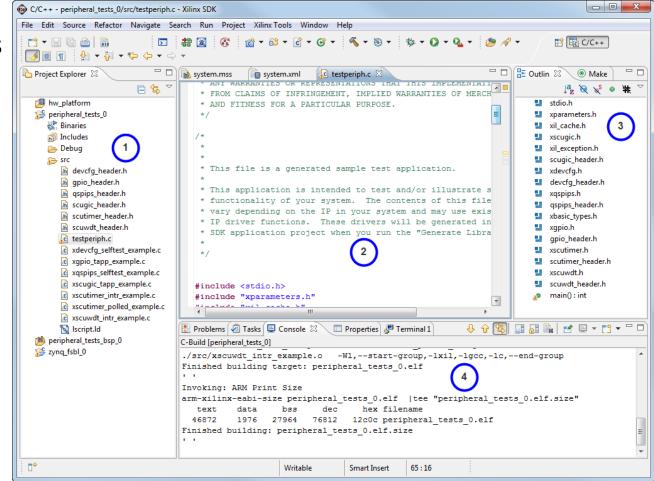

#### **SDK Workbench Views**

- C/C++ project outline displays the elements of a project with file decorators (icons) for easy identification

- C/C++ editor for integrated software creation

- 3 Code outline displays elements of the software file under development with file decorators (icons) for easy identification

- Problems, Console, Properties views list output information associated with the software development flow

## **Build Software Application in SDK**

- Create software platform

- System software, board support package

- LibGen program

- Create software application

- Optionally, create linker script

- Build project

- Compile, assemble, link output file <app\_project>.elf

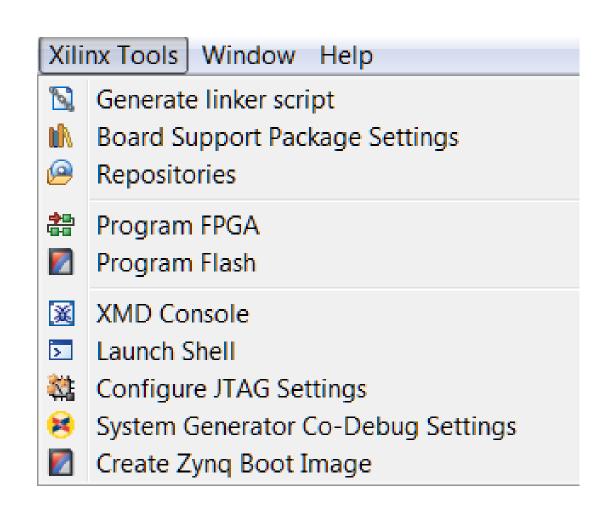

# Software Management Settings

# Software is managed in three major areas

- Compiler/Linker Options

- Application program

- Software Platform Settings

- Board support package

- Linker Script Generation

- Assigning software to memory resources

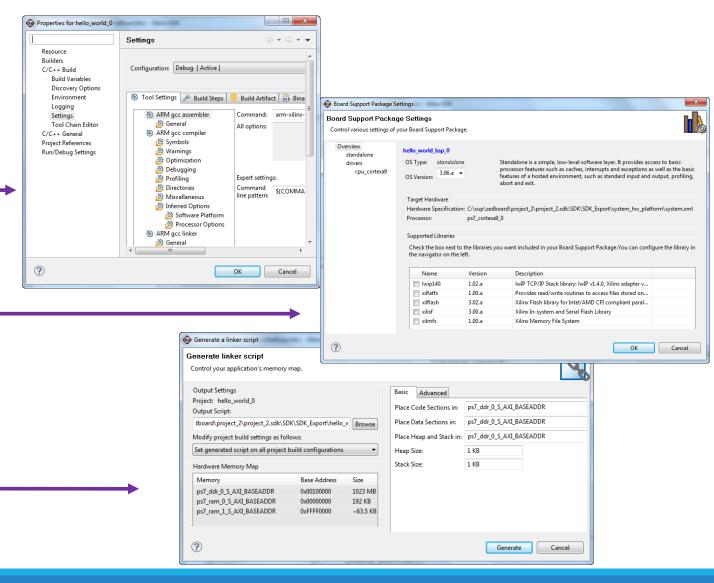

#### Integrated Xilinx Tools in the SDK

#### Xilinx additions to the Eclipse IDE

- BSP Settings

- Software Repositories

- Generate Linker Script

- Program the programmable logic

- Bitstream must be available

- Create Zynq Boot Image

- Program Flash Memory

- Launch XMD Console

- Launch Shell

- Configure JTAG Settings

- SysGen Co-Debug Settings

# Apendix

## Vivado Design Suite Elaboration Process

### Embedded System Design – Vivado Flow

#### Elaboration

- Elaboration is the RTL optimization to an FPGA technology

- Vivado IDE allows designers to import and manage RTL sources

- Verilog, System Verilog, VHDL, NGC, or testbenches

- Create and modify sources with the RTL Editor

- Cross-selection between all the views

- Sources view

- Hierarchy view: Display the modules in the design by hierarchy

- Libraries view: Display sources by category

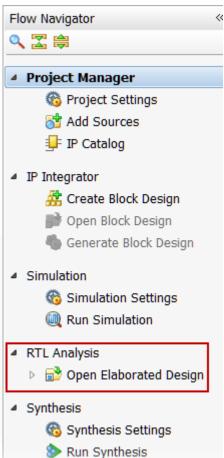

#### Elaborated Design

Accessed through the Flow Navigator by selecting Open Elaborated Design

Representation of the design before synthesis

- Interconnected netlist of hierarchical and generic technology cells

- Instances of modules/entities

- Generic technology representations of hardware components

- AND, OR, buffer, multiplexers, adders, comparators, etc...

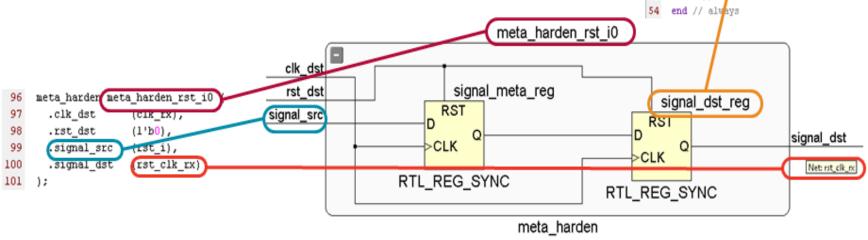

#### Object Names in Elaborated Design

#### Object names are extracted from RTL

- Instance and pin names of hierarchical objects

- Inferred flip-flops from underlying reg/signal/logic

- Suffix \_reg is added

- Nets from underlying reg/signal/logic when it makes sense

```

else // if /rst dst

signal meta <= signal src;

sigmal #st <= sigmal meta;

end // always

signal_dst_reg

RSI

signal dst

Net: rst_clk_rx

RTL_REG_SYNC

```

signal neta;

sigmal dst;

always @(posedge clk dst)

sigmal\_meta/<= l'b0; signal dst/ <= 1'b0;

if (rst\_dst)

### Elaboration and Analysis

In a RTL based design, elaboration is the first step

Click on the Open Elaborated Design under RTL Analysis to

Compile the RTL source files and load the RTL netlist for interactive analysis

You can check RTL structure, syntax, and logic definitions

Analysis and reporting capabilities include:

- RTL compilation validation and syntax checking

- Netlist and schematic exploration

- Design rule checks

- Early I/O pin planning using an RTL port list

- Ability to select an object in one view and cross probe to the object in other views, including instantiations and logic definitions within the RTL source files

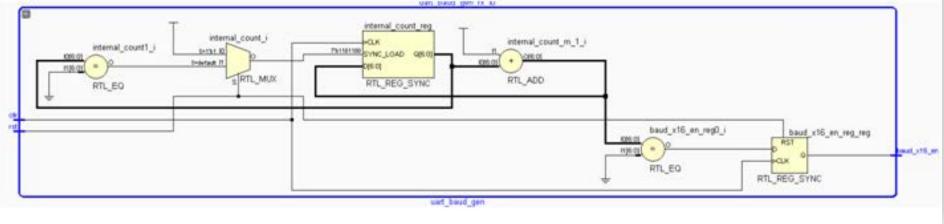

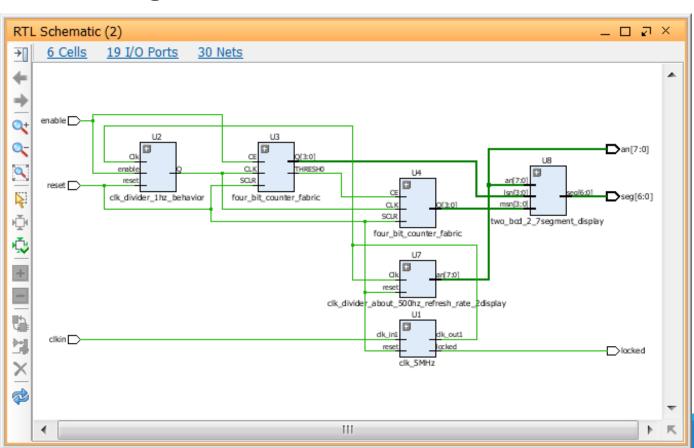

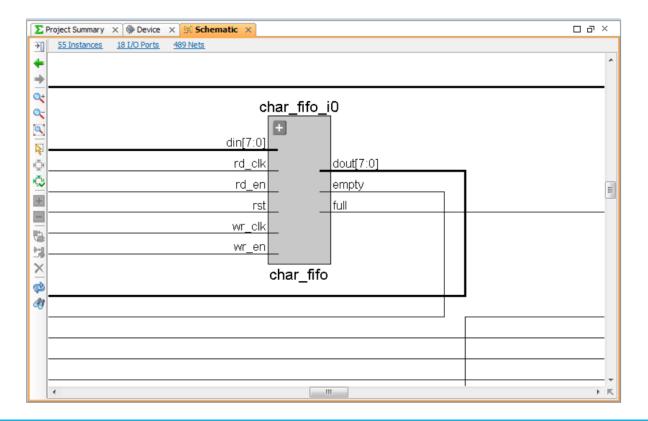

#### Schematic View of an Elaborated Design

When Schematic is clicked under the Elaborated Design, the schematic is opened showing the hierarchical blocks

Note that no IO buffers are inferred at this stage

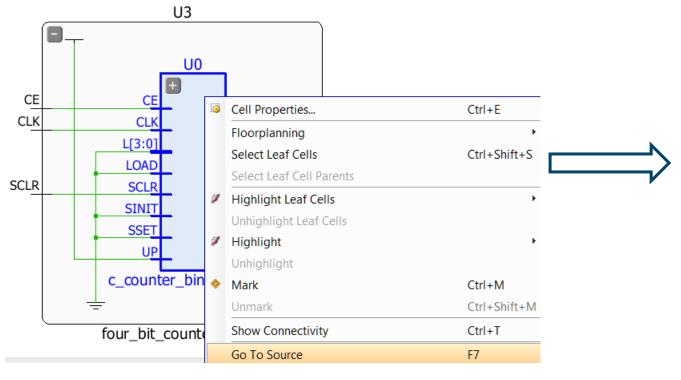

#### **Cross Probing**

Select an object in the schematic, right-click, and select Go To Source to view where the object is defined in the source file

```

114 BEGIN

10 : c counter_binary_v12_0

115

116

GENERIC MAP (

C IMPLEMENTATION => 0,

117

C VERBOSITY => 0,

118

119

C XDEVICEFAMILY => "artix7",

C WIDTH => 4,

120

C HAS CE => 1,

121

C_HAS_SCLR => 1,

C RESTRICT COUNT => 1,

123

C_COUNT_TO => "1001",

124

125

C COUNT BY => "1",

126

C COUNT MODE => 0,

127

C THRESHO VALUE => "1001",

128

C CE OVERRIDES SYNC => 0,

129

C HAS THRESHO => 1,

130

C HAS LOAD => 0,

C LOAD LOW => 0,

131

C LATENCY => 1,

132

133

C FB LATENCY => 0,

134

C AINIT VAL => "0",

C_SINIT_VAL => "0",

135

C SCLR OVERRIDES SSET => 1,

C HAS SSET => 0,

137

C HAS SINIT => 0

138

139

```

# Vivado Design Suite Synthesis Process

#### Embedded System Design – Vivado Flow

#### Vivado IDE Synthesis

- Applicable only for RTL (HDL) design flows

- EDIF is black boxed and linked after synthesis

- Synthesis tool uses XDC constraints to drive synthesis optimization

- Design must first be synthesized without timing constraints for constraints editor usage

- XDC file must exist

- Synthesis settings provide access to additional options

#### Logic Optimization and Mapping to Device Primitives

Synthesis of an RTL design not only optimizes the gate-level design but also maps the netlist to Xilinx primitives (sometimes called technology mapping)

#### Synthesized Design

Accessed through the Flow Navigator by selecting Open Synthesized Design

#### Representation of the design after synthesis

- Interconnected netlist of hierarchical and basic elements (BELs)

- Instances of modules/entities

- Basic elements

- LUTs, flip-flops, carry chain elements, wide MUXes

- Block RAMs, DSP cells

- Clocking elements (BUFG, BUFR, MMCM, ...)

- I/O elements (IBUF, OBUF, I/O flip-flops)

Object names are the same as names in the elaborated netlist when possible

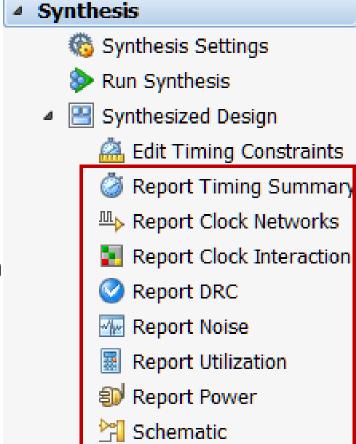

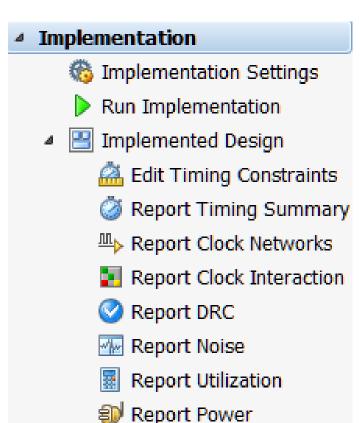

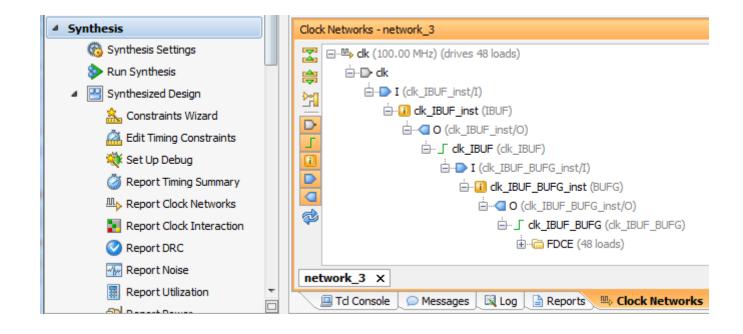

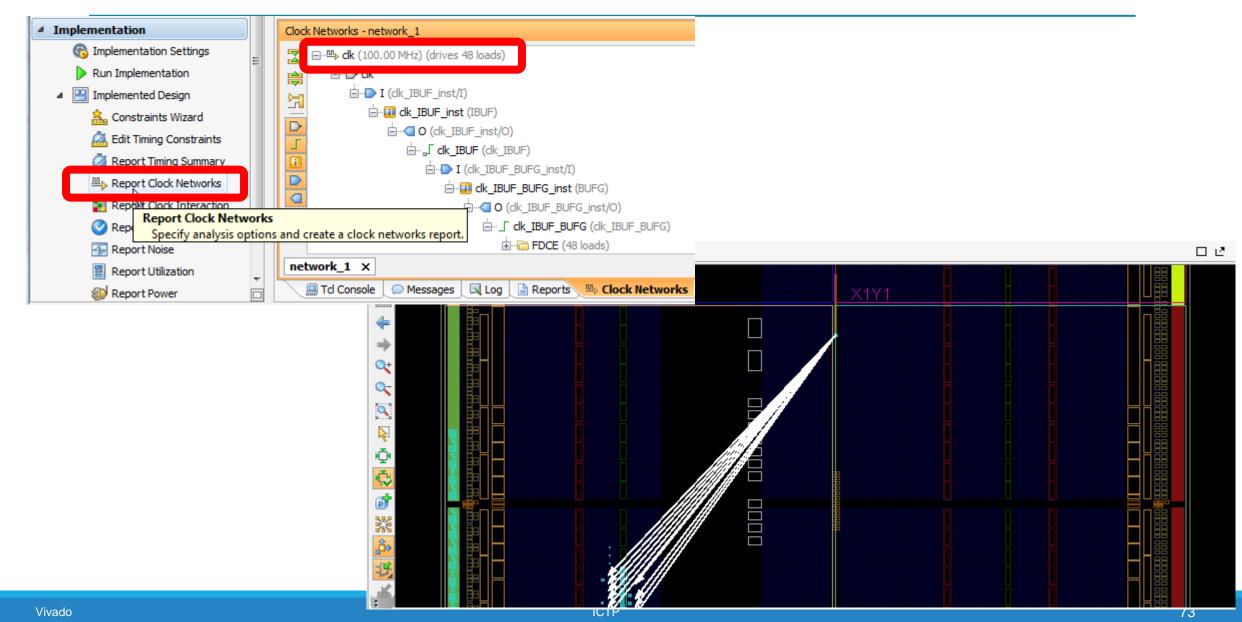

#### Commands Available After Synthesis

Flow Navigator is optimized to provide quick access to the options most frequently used after synthesis

- Report Timing Summary: Generate a default timing report

- Report Clock Networks: Generates a clock tree for the design

- Report Clock Interaction: Verifies constraint coverage on paths between clock domains

- Report DRC: Performs design rule check on the entire design

- Report Noise: Performs an SSO analysis of output and bidirectional pins in the design

- Report Utilization: Generates a graphical version of the Utilization Report

- Report Power: Detailed power analysis reports that can be customized for the power supply and application environment

- Schematic: Opens the Schematic viewer

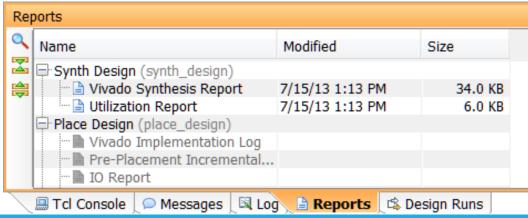

### Synthesis Reports

While the Flow Navigator points to the most important reports, the Reports tab contains several other useful reports

- Vivado Synthesis Report shows

- HDL files synthesized, synthesis progress, timing constraints read, and RTL primitives from the RTL design

- Timing optimization goals, technology mapping, removed pins/ports, and final cell usage (technology-mapped cell usage)

- Utilization Report shows

- Technology-mapped cell usage in an easy-to-read tabular format

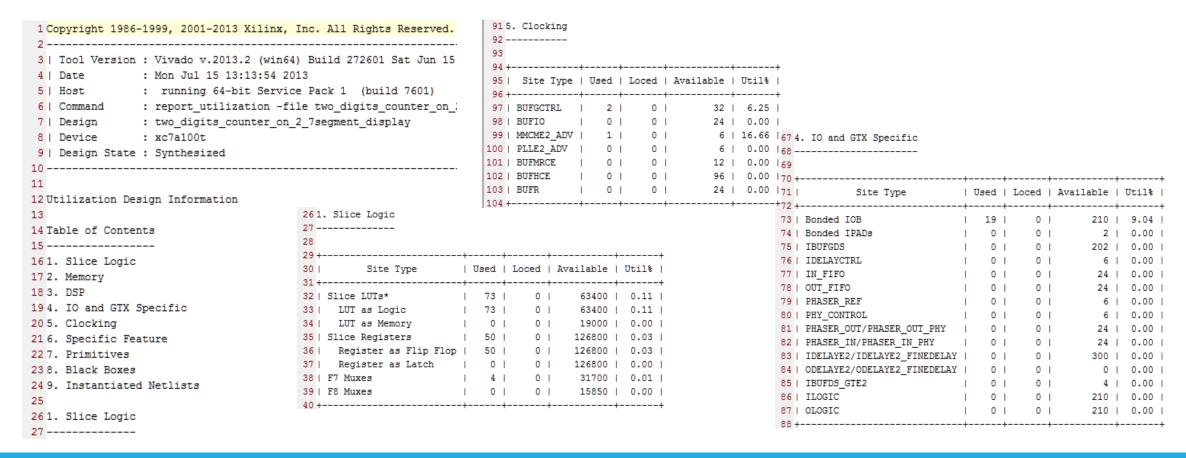

#### Synthesis Utilization Report

Reports slice logic, memory, DSP slice, IO, clocking, and other resources used by the design

# Vivado Design Suite Implementacion Process

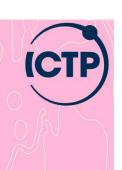

#### Embedded System Design – Vivado Flow

#### Vivado Implementation Sub-Processes

Vivado Design Suite Implementation process transform a logical netlist (generated by the synthesis tool) into a placed and routed design ready for bitstream generation

#### Opt design

Optimizes the logical design to make it easier to fit onto the target FPGA

#### Place design

Places the design onto the FPGA's logic cells

#### Route design

Routing of connections between the FPGA's cells

#### Using Design Constraints for Guiding Implementation

There are two types of design constraints, <u>physical constraints</u> and <u>timing constraints</u>.

Physical Constraints: define a relationship between logic design objects and device resources

- Package pin placement

- Absolute or relative placement of cells:

- Block RAM

- DSP

- LUTs

- Filp-Flops

- Floorplanning constraints that assign cells to general regions of an FPGA

**Timing Constraints**: define the frequency requirements for the design. Without timing constraints, Vivado Design Suite optimizes the design solely for wire length and routing congestion and makes no effort to asses or improve design performance

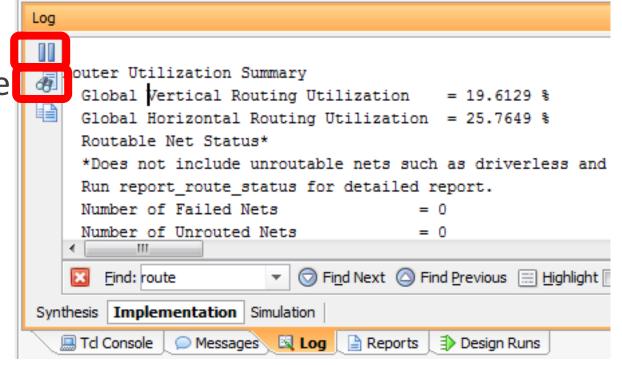

## Implementation Log Messages

#### Viewing the Log in the Log Window

The Log window opens in the Vivado

IDE after you launch a run. It shows the standard output messages. It also displays details about the progress of each individual implementation process, such as place\_design and route\_design.

#### After Implementation

- Sources and Netlist tabs do not change

- Now as each resources is selected, it will show the exact placement of the resource on the die

- Timing results have to be generated with the Report Timing Summary

- As each path is selected, the placement of the logic and its connections is shown in the Device view

- This is the cross-probing feature that helps with static timing analysis

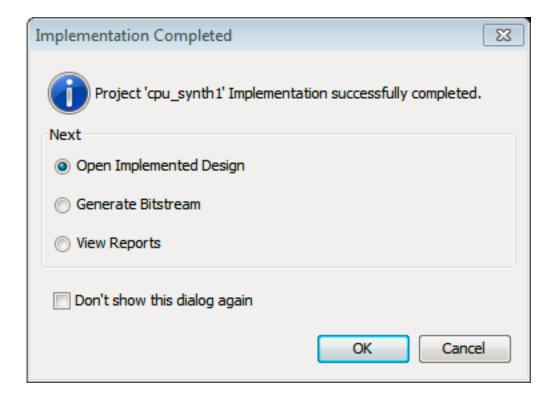

#### After Completing Implementation

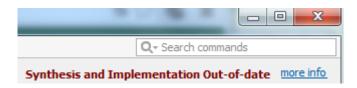

## Implementation Out-of-Date Message

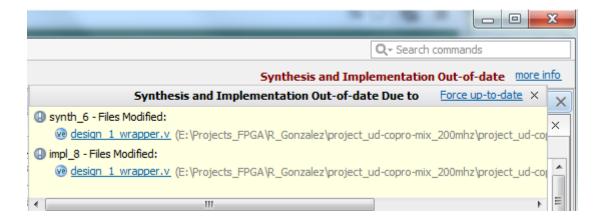

#### **Exporting a Hardware Description**

#### **Export Hardware Design to SDK**

Software development is performed with the Xilinx Software Development Kit tool (SDK)

The design must be opened if a bitstream of the design is generated

The Block design must be open before the design can be exported

An XML description of the hardware is imported in the SDK tool

- The hardware platform is built on this description

- Only one hardware platform for an SDK project

The SDK tool will then associate user software projects to hardware

#### Exporting IP Integrator Design to SDK – Main Files

| File                    | Description                                                                                                                                                                                                                                               |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| system.xml              | This file opens by default when you launch SDK and displays the address map of your system                                                                                                                                                                |

| ps7_init.c<br>s7_init.h | The ps7_init.c and ps7_init.h files contain the initialization code for the Zynq Processing System and initialization settings for DDR, clocks, PLLs and MIOs. SDK uses these settings when initializing the PS so applications can run on top of the PS. |

| ps7_init.tcl            | This is the Tcl version of the <i>init</i> file                                                                                                                                                                                                           |

| ps7_init.html           | This <i>init</i> file describes the initialization data.                                                                                                                                                                                                  |

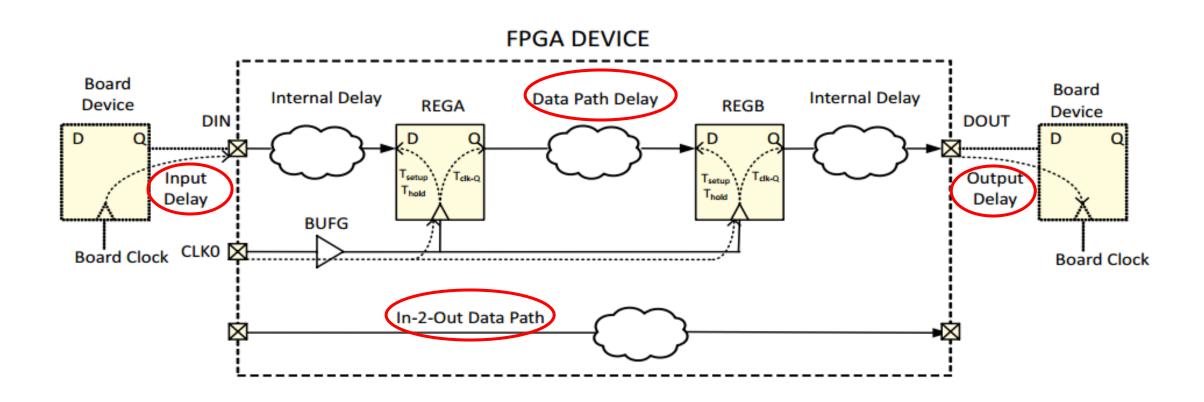

## Vivado Design Suite Basic Static Timing Constraints

#### **Basic Timing Constraints**

There are three basic timing constraints applicable to a sequential machine

- Period

- Paths between synchronous elements clocked by the reference clock net

- Synchronous elements include flip-flops, latches, synchronous RAM, and DSP slices

- Use create\_clock to create the constraint

- Input Delay

- Paths between input pin and synchronous elements

- Use set\_input\_delay to create the constraint

- Output delay

- Paths between synchronous elements and output pin

- Use set\_output\_delay to create the constraint

## Timing Paths Example

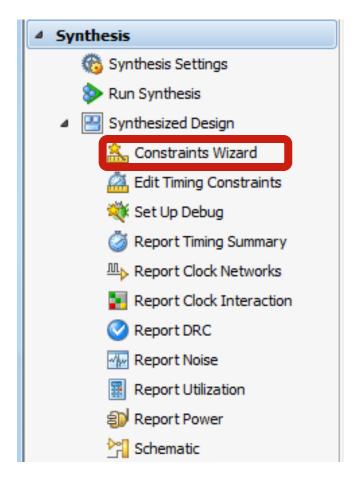

#### Creating Basic Timing Constraints in Vivado IDE

- 1. Run Synthesis

- 2. Open the synthesized design

- 3. Invoke constraints editor

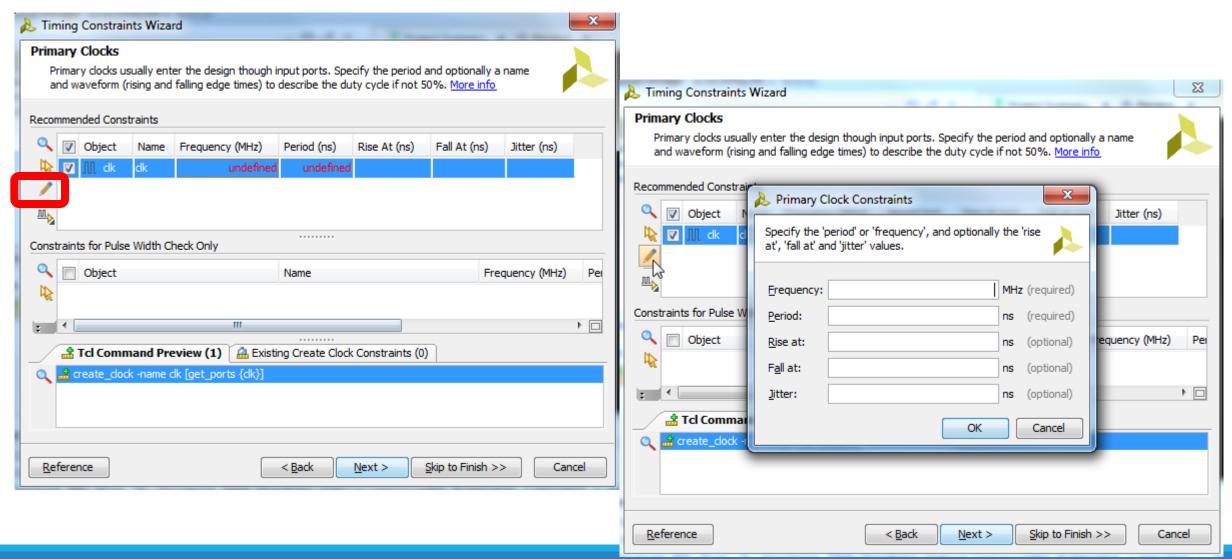

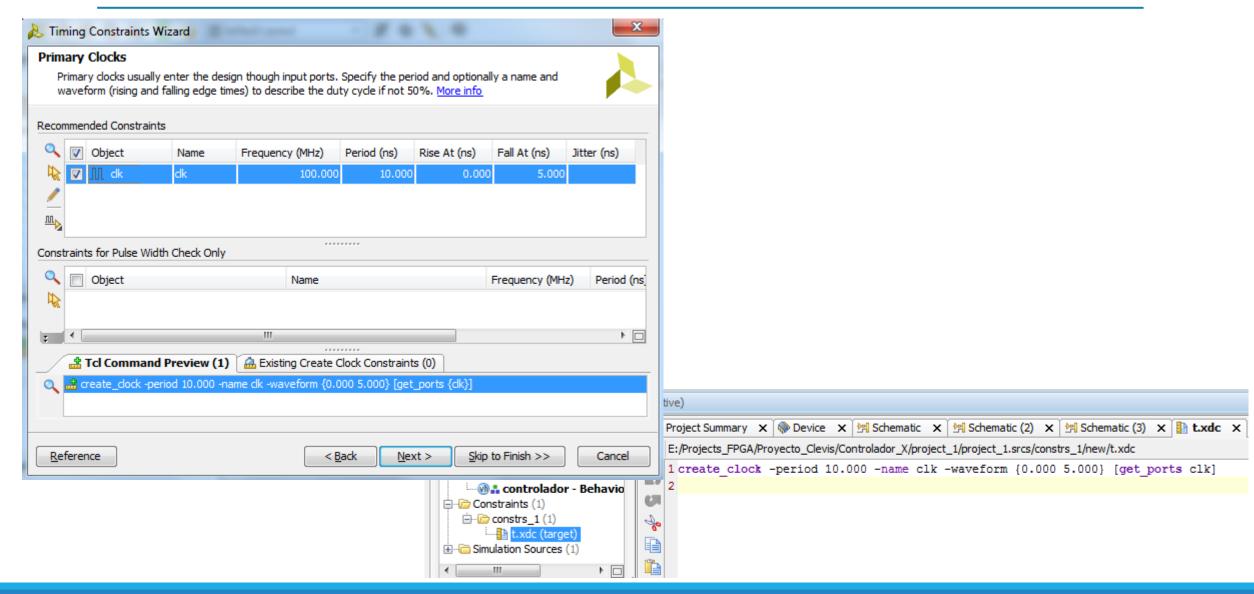

## **Clock Constraint Setting**

## **Clock Constraint Setting**

#### Clock Network Report

# Clock Network Report and Visualization

# Vivado Design Suite Generate Bit Stream Process Configuring FPGA Process

# Steps to Configure only the PL

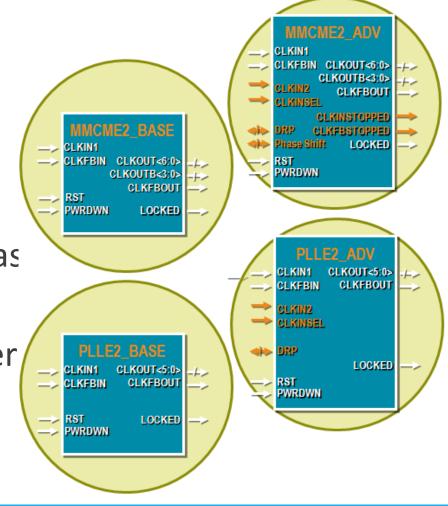

## Clocking Resources: MMCM and PLL

Up to 24 CMTs per device

One MMCM and one PLL per CMT

Two software primitives (instantiation)

\*\_BASE has only the basic ports

\*\_ADV provides access to all ports

PLL is primarily intended for use with the I/O phas for high-speed memory controllers

The MMCM is the primary clock resource for user

## Inference

## Clock networks are represented by nets in your RTL design

The mapping of an RTL net to a clock network is managed by using the appropriate clock buffer to generate that net

#### Certain resources can be inferred

- A primary input net (with or without an IBUF instantiated) will be mapped to a global clock if it drives the clock inputs of clocked resources

- The BUFG will be inferred

- BUFH drivers will be inferred whenever a global clock (driven by a BUFG) is required in a clock region

- BUFHs for each region required will be inferred

### BUFIO, BUFR, and BUFMR cannot be inferred

Instantiating these buffers tells the tools that you want to use the corresponding clock networks

#### PLLs and MMCMs cannot be inferred

## Instantiation

All clocking resources can be directly instantiated in your RTL code

- Simulation models exist for all resources

- Refer to the Library Guide for HDL Designs

- Use the Language Templates ( ) tab

PLLs and MMCMs have many inputs and outputs, as well as many attributes

- Optimal dividers for obtaining the desired characteristics may be hard to derive

- The Clocking Wizard via the IP Catalog

- Only \* ADV available

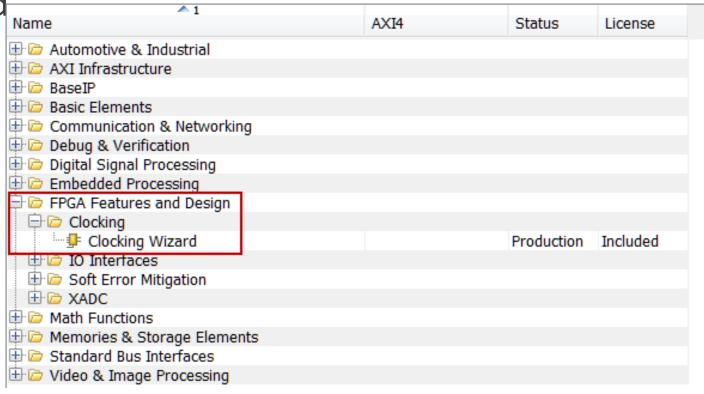

# **Invoking Clocking Wizard**

Click on the IP Catalog

Expand FPGA Features and Design > Clocking

Double-click on Clocking Wizard

The Clocking Wizard walks you through the generation of complete clocking subsystems

79

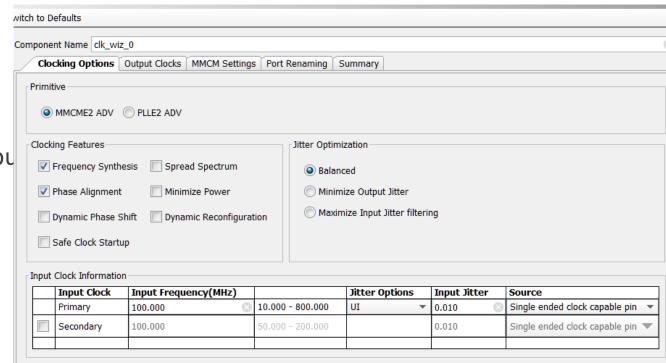

# The Clocking Wizard: Clocking Options

Select Primitives to be used

- MMCME2\_ADV

- PLLE2\_ADV

Specify the primary input frequency and source type

Optionally, select and specify secondary input

Select clocking features

- Frequency synthesis

- Phase alignment

- Dynamic phase shift

0

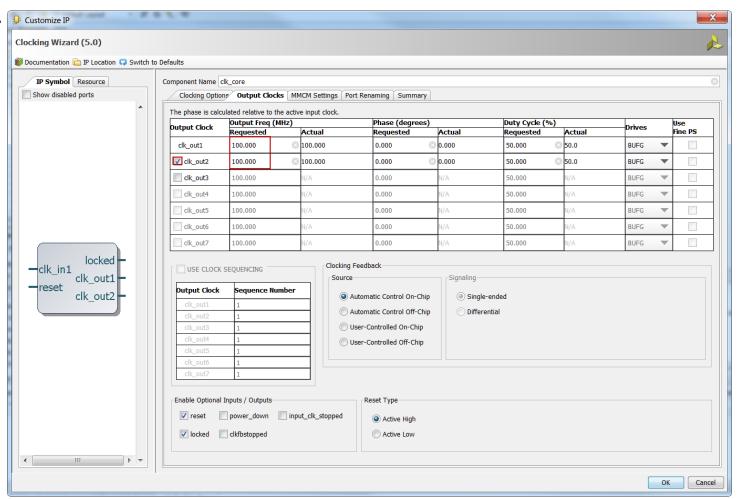

# The Clocking Wizard: Output Clocks

- Select the desired number of output clocks

- Set the desired output frequencies

- Select optional ports

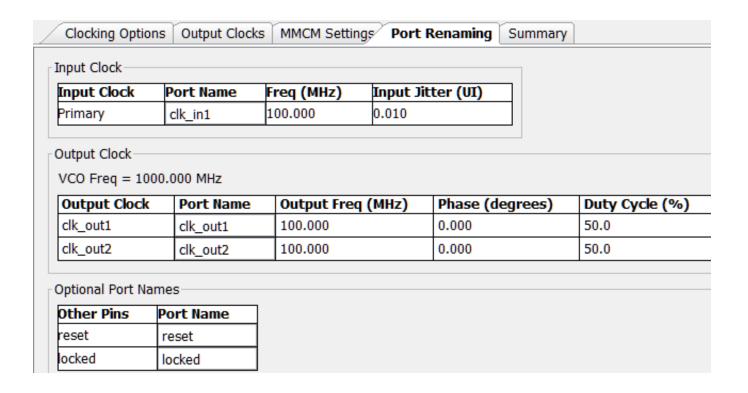

# The Clocking Wizard: Port Renaming

Change input/output port names

Change optional port names

# The Clocking Wizard: Summary

Shows the input, output frequencies

Other attributes depending on the selections made

| Clocking Options Output Clock | ks MMCM Settings | Port Renaming Summary |

|-------------------------------|------------------|-----------------------|

| Attribute                     | N                | /alue                 |

| Input Clock (MHz)             | 1                | 100.000               |

| Phase Shift                   | 1                | Vone                  |

| Divide Counter                | 1                | L                     |

| Mult Counter                  | 1                | 10.000                |

| CLKOUT0 Divider               | 1                | 10.000                |

| CLKOUT1 Divider               | 1                | 10                    |

| CLKOUT2 Divider               | (                | OFF                   |

| CLKOUT3 Divider               | (                | OFF                   |

| CLKOUT4 Divider               | (                | OFF                   |

| CLKOUT5 Divider               | (                | OFF                   |

| CLKOUT6 Divider               | (                | OFF                   |

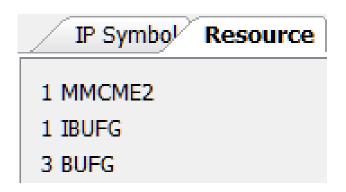

The Resource tab on the left provides summary of type and number of resources used

# Reset and Clock Topology

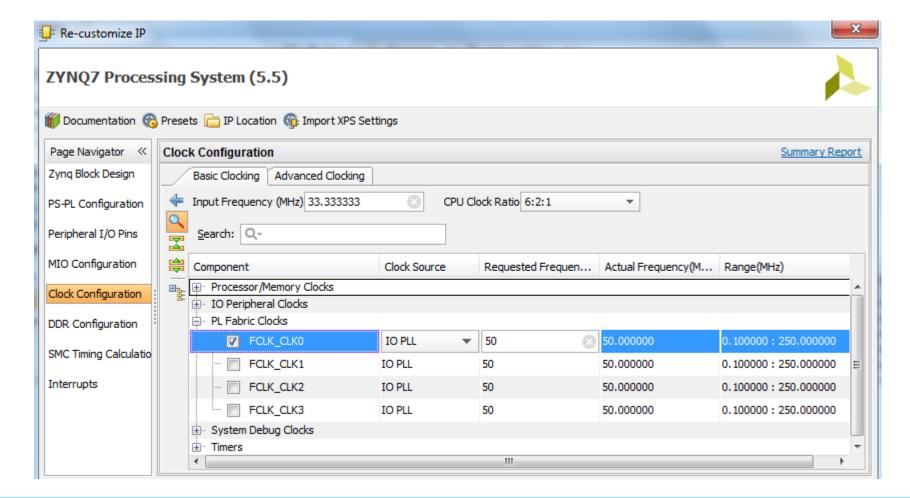

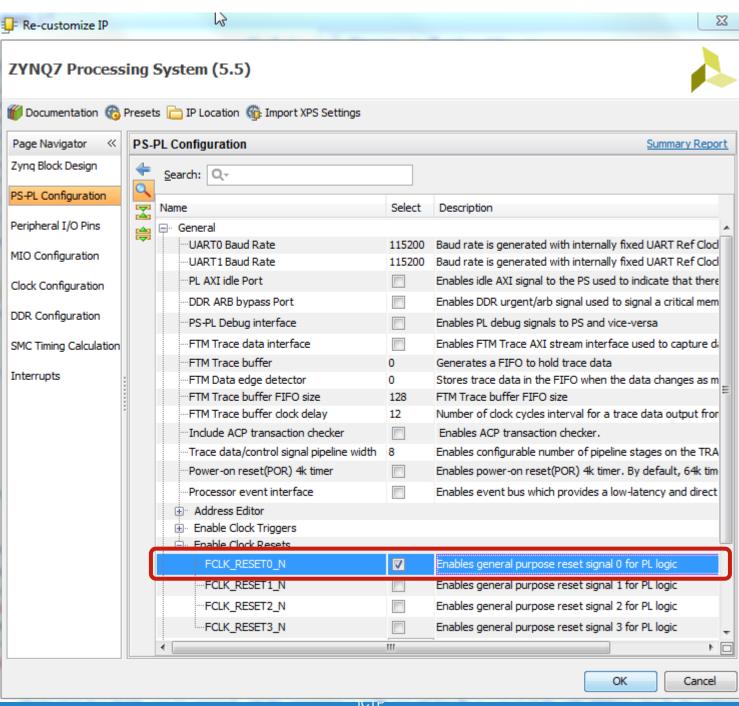

# **Enabling Clock for PL**

Vivado 86

# **SDK Compilers**

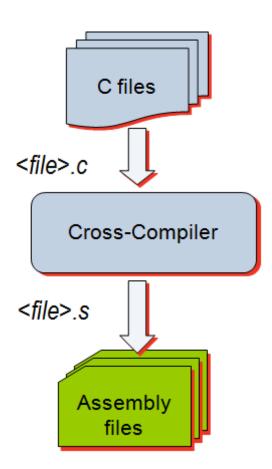

## **GNU Tools: GCC**

GCC translates C source code into assembly language

GCC also functions as the user interface, passing options to GNU assembler and to the GNU linker, calling the assembler and the linker with the appropriate parameters

Supported cross-compilers

ARM processor compiler

- GNU GCC (arm-xilinx-eabi-gcc)

- GNU Linux GCC (arm-xilinx-linux-eabi-gcc)

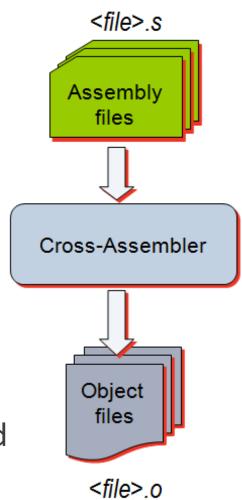

## **GNU Tools: AS**

Input: assembly language files

File extension: .s

Output: object code

File extension: .o

#### Contains

- Assembled piece of code

- Constant data

- External references

- Debugging information

Typically, the compiler automatically calls the assembler

Use the -Wa switch if the source files are assembly only and use gcc

-89

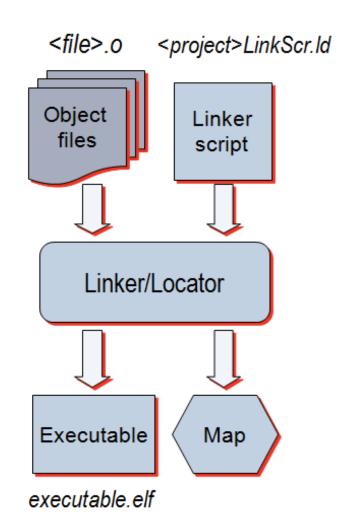

# GNU Tools: Linker (LD)

## Inputs

- Several object files

- Archived object files (library)

- Linker script (\*.ld)

## **Outputs**

- Executable image (ELF)

- Map file

# **Timing Reports**

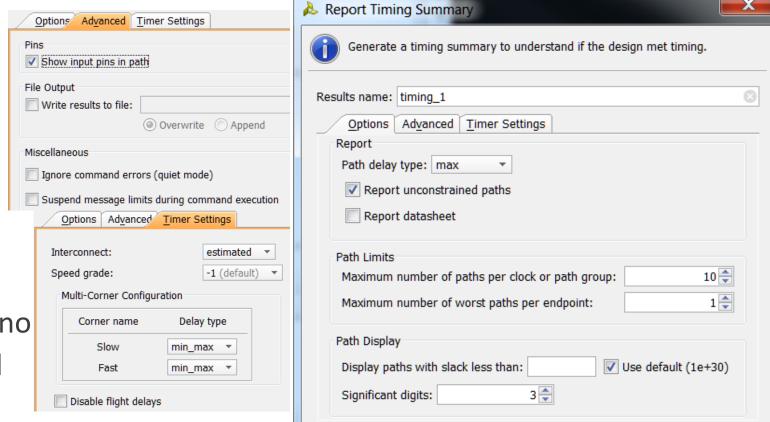

# Report Timing Summary

# Synthesis Synthesis Settings Run Synthesis Synthesized Design Edit Timing Constraints Report Timing Summary Report Clock Networks

## Tcl command: report\_timing\_summary

report\_timing\_summary -delay\_type max -report\_unconstrained -check\_timing\_verbose -max\_paths 10 -input\_pins -name timing\_1

#### Vivado IDE

## Options tab

Maximum number of paths

### Advanced tab

Write to a file

## **Timer Settings**

- Interconnect delay can be igno

- Flight delays can be disabled

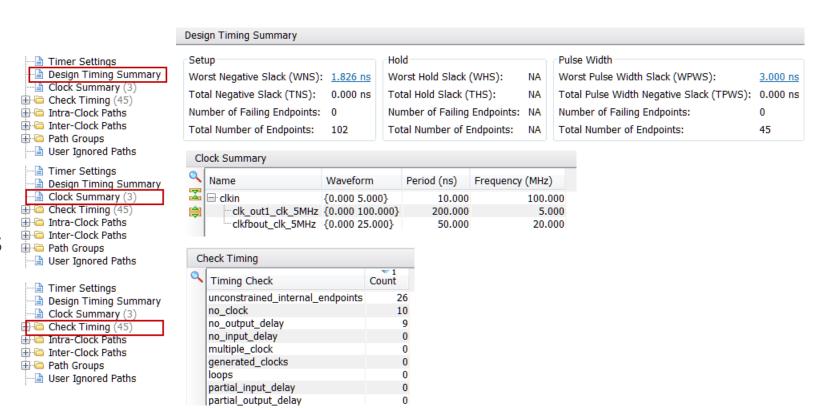

## Report Timing Summary

## **Design Timing Summary**

WNS, TNS, total number of endpoints are of interest

## **Clock Summary**

Primary and derived clocks

## **Check Timing**

Number of unconstrained internal endpoints