#### The New Generation of Intelligent FPGA-based DAQ Architectures

#### Igor Konorov

Institute for Hadronic Structure and Fundamental Symmetries (E18)

Technical University of Munich

**Department of Physics**

Joint ICTP-IAEA School on FPGA-based SoC and its Applications for Nuclear and Related Instrumentation 25 January – 19 February

Unrenturm der TVM

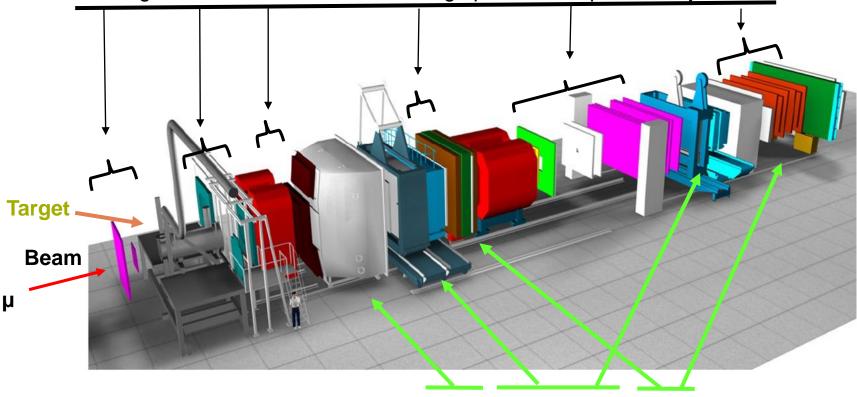

#### Particle Physics Experiment (COMPASS)

Tracking detectors : coordinates of charge particles => particle trajectories

Particle identification detectors : RICH, Calorimeters, Muon Detectors

300 000 detector channels

Joint ICTP-IAEA School on FPGA-based SoC and its Application 2021

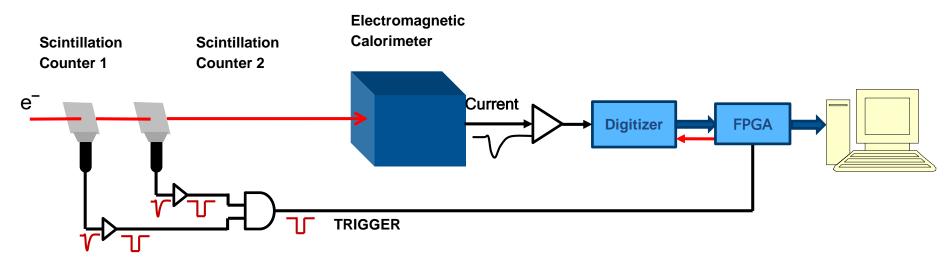

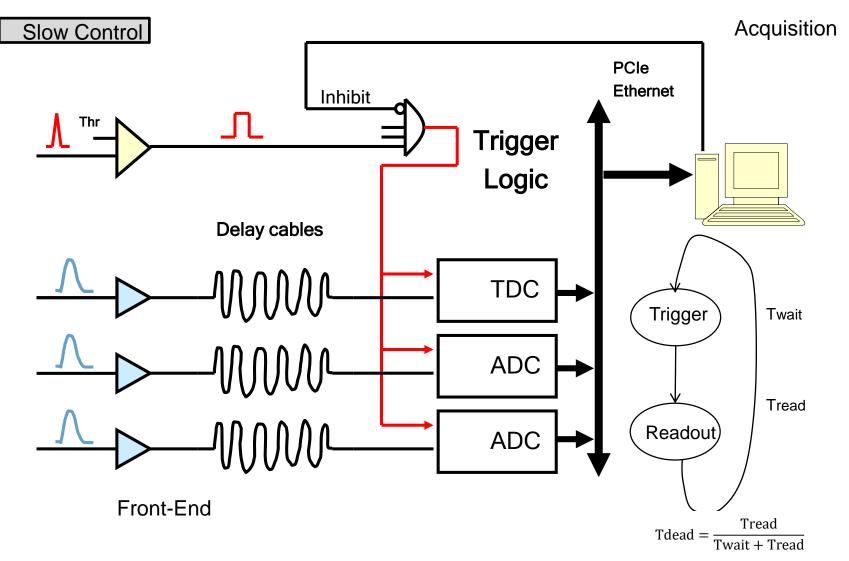

#### Experiment : Electron Energy Measurement

TRIGGER – define time when detector signal to be measured

Why read only when trigger and not continuously?

- Not feasible to measure continuous data flow

- Not feasible to transmit such amount of data

- Not feasible to sore such amount of data

# ПΠ

#### **DAQ** Tasks

- Time reference system ; system CLOCK, Trigger together with event ID

- Acquire data from detectors readout by Front-Ends

- Collect data and Event Building if multiple FEE cards

- Data storage

- Configuration and Monitoring. Is everything OK?

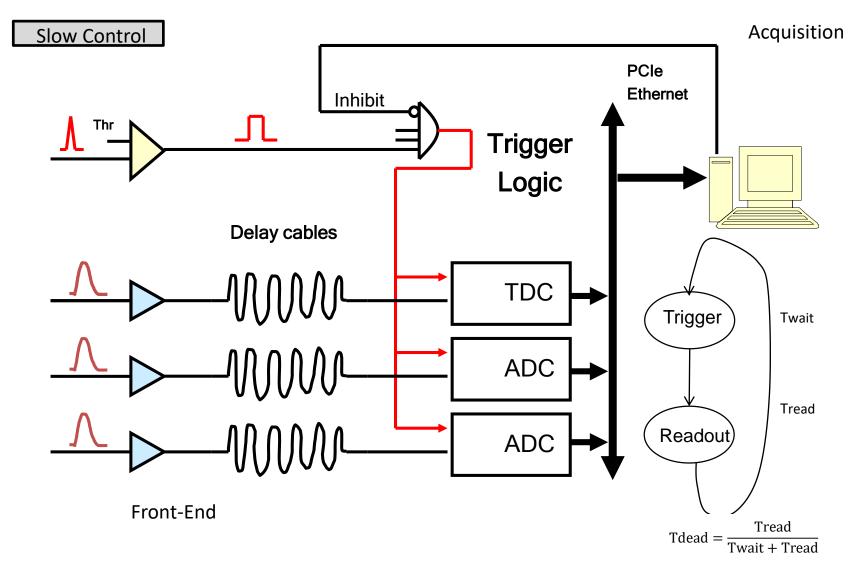

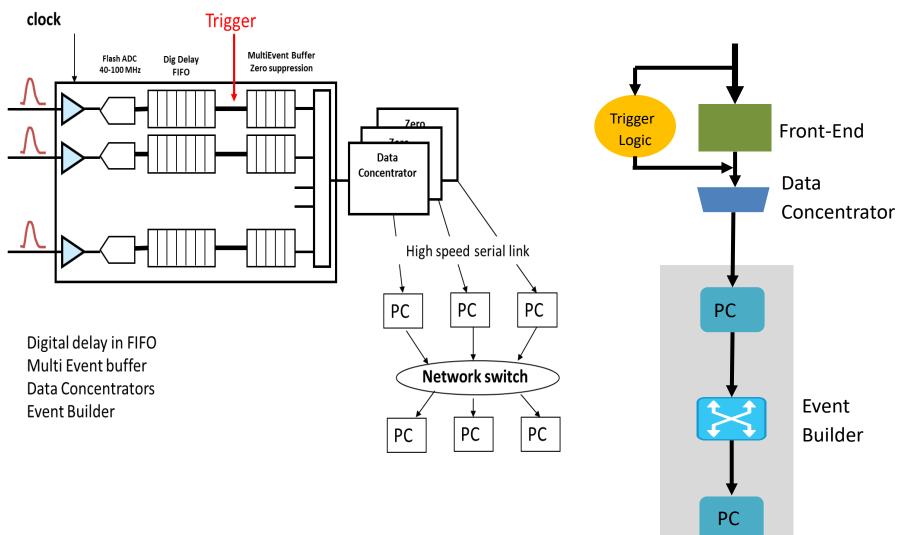

#### DAQ Architecture in Particle Physics

#### **DAQ Architecture in Particle Physics**

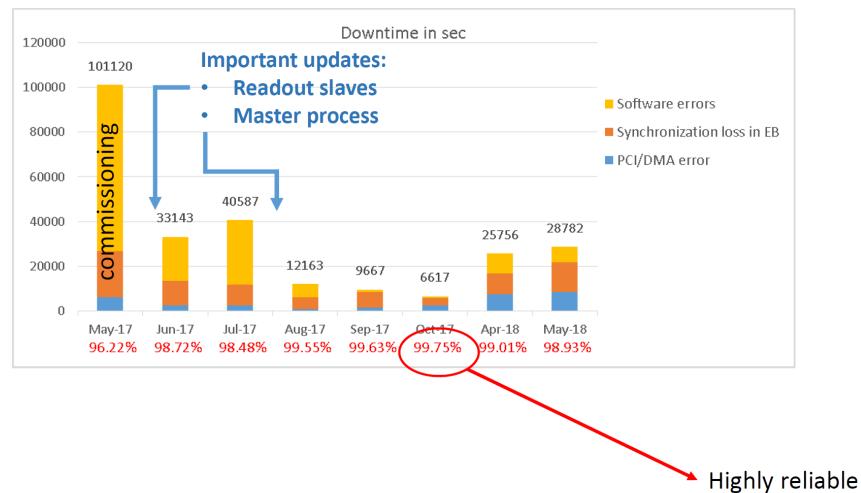

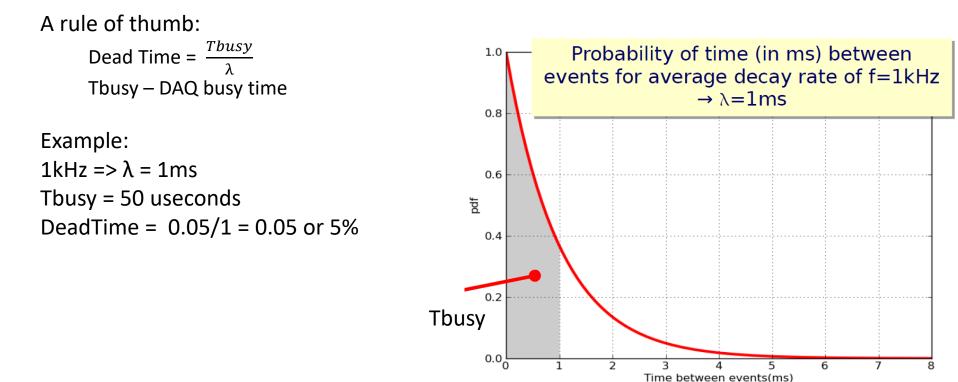

#### **Data Taking Efficiency**

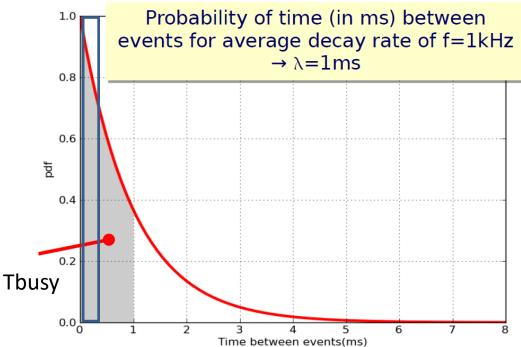

Probability for uncorrelated events described by Poisson distribution

$$q(t) = e^{-t/\lambda}$$

$\lambda$  – average time between events

#### **Data Taking Efficiency**

Probability for uncorrelated events described by Poisson distribution

$$q(t) = e^{-t/\lambda}$$

$\lambda$  – average time between events

A rule of thumb: Dead Time =  $\frac{Tbusy}{\lambda}$ Tbusy – DAQ busy time Example: 1kHz =>  $\lambda$  = 1ms Tbusy = 100 useconds DeadTime = 0.2/1 = 0.2 or 20% 20% of events are lost !!!

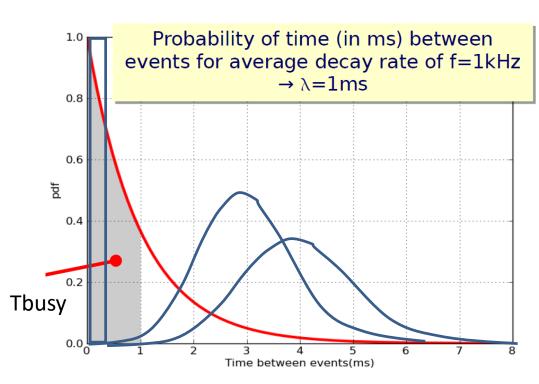

#### **Data Taking Efficiency**

Probability for uncorrelated events described by Poisson distribution

$$q(t) = e^{-t/\lambda}$$

$\lambda$  – average time between events

A rule of thumb: Dead Time =  $\frac{Tbusy}{\lambda}$ Tbusy – DAQ busy time

Example:  $1kHz \Rightarrow \lambda = 1ms$ Tbusy = 100 useconds DeadTime = 0.2/1 = 0.2 or 20% 20% of events are lost !!!

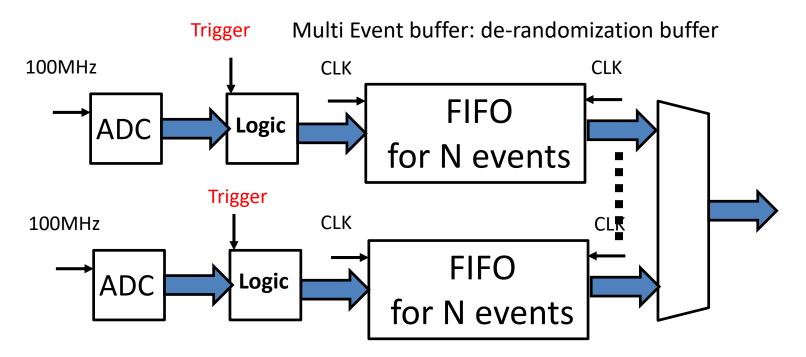

Solution: Store N events before Readout

# **Pipe Line Front Ends**

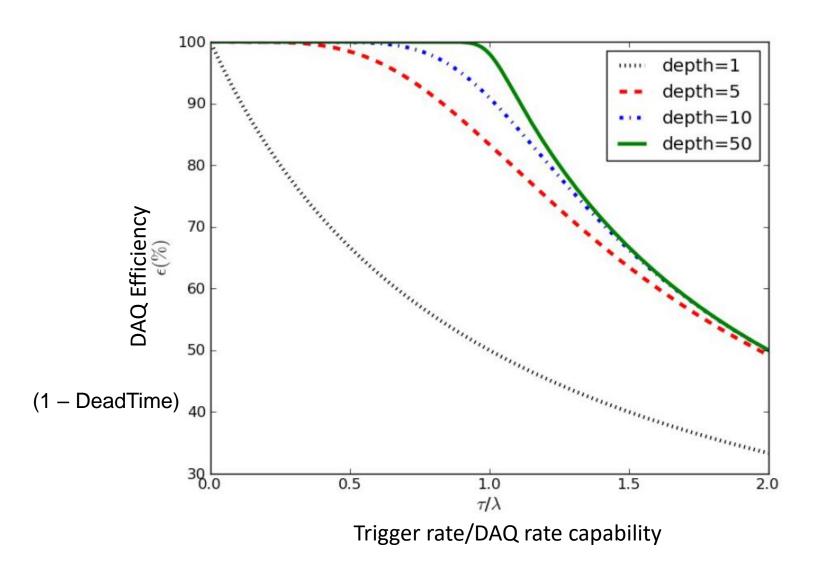

Input : Poisson distribution Output : more like a Gaussian centered around average value

# DAQ efficiency vs FIFO Depth

# **Multi Channel Data Flow**

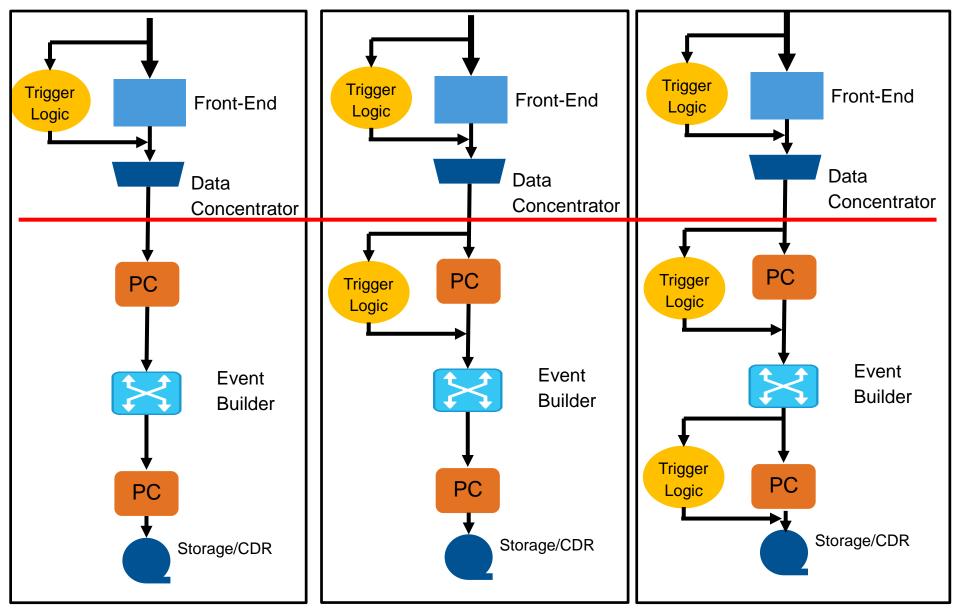

## **Multiple Trigger Levels**

### **DAQ** Architectures

#### ТШ

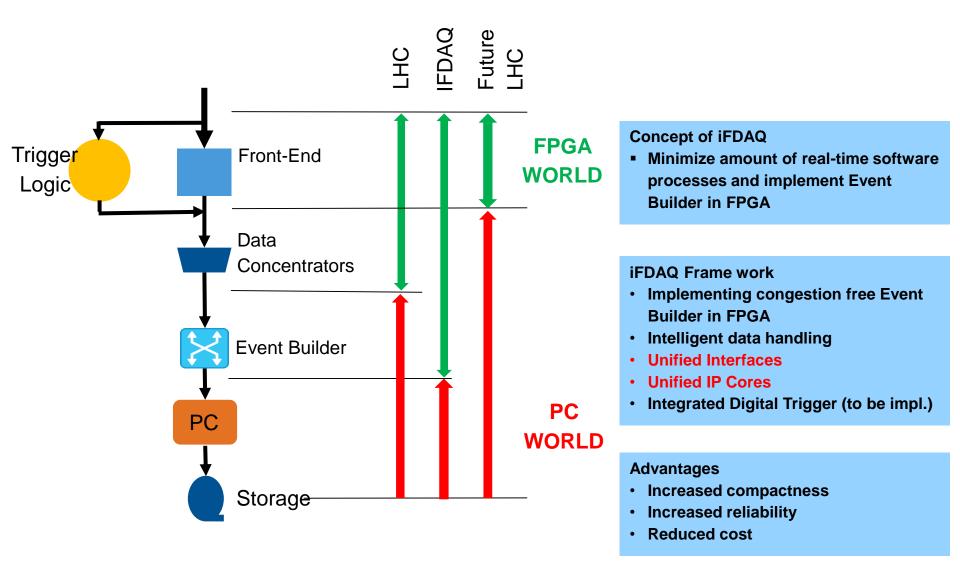

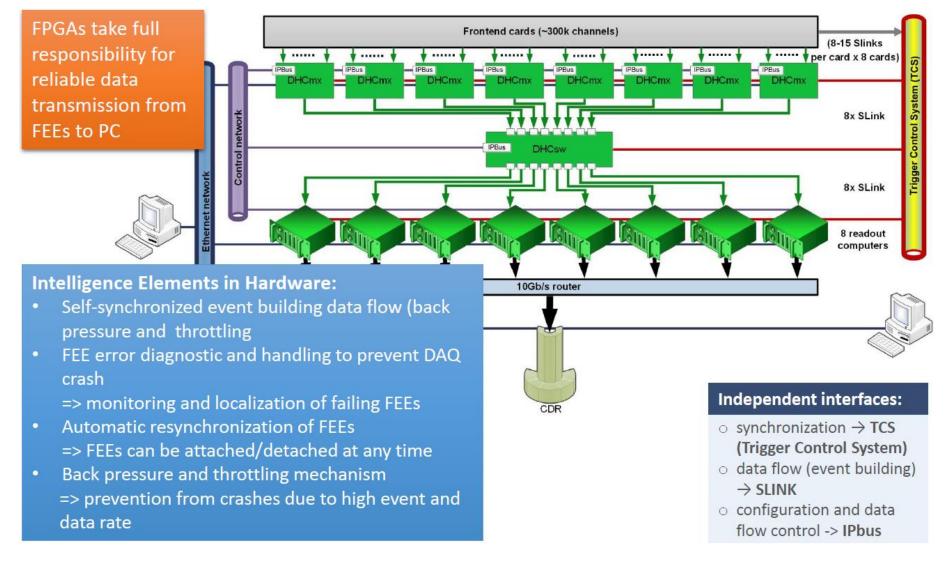

## iFDAQ Architecture

### iFDAQ Architecture

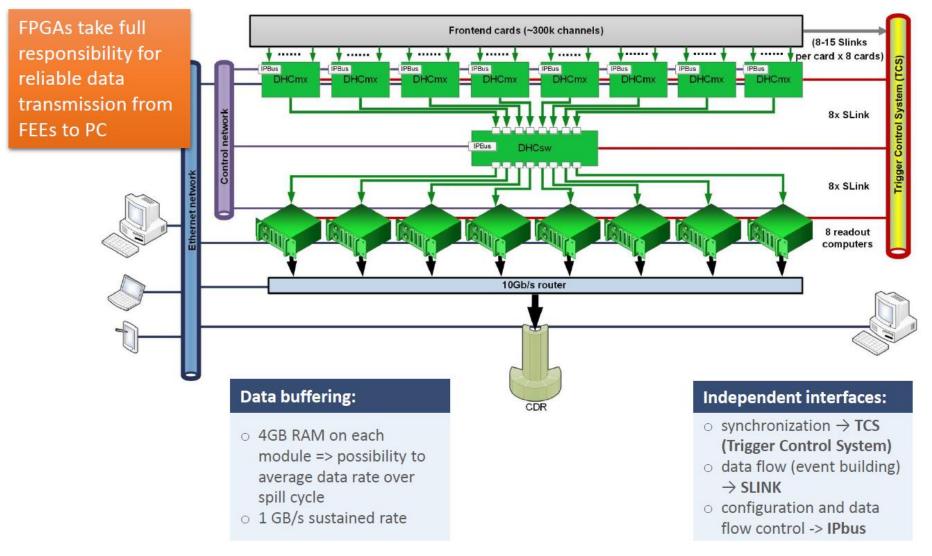

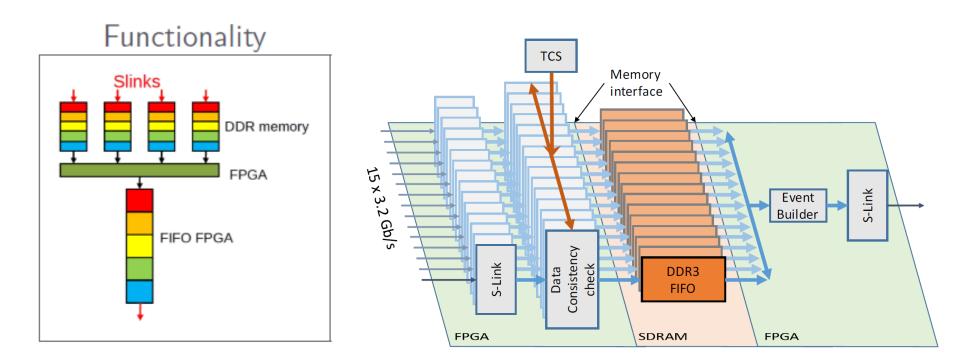

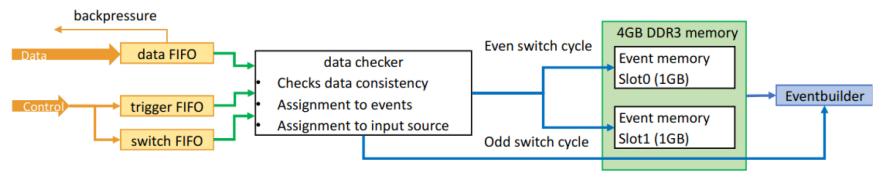

#### FPGA DAQ Module

FPGA

- XC6V130T

- 16 x 6.5 Gbps serial links

- Ethernet UDP

- Time Distribution Input, LVDS

4 Gbyte DDR3 Memory

#### Data Concentrator Firmware

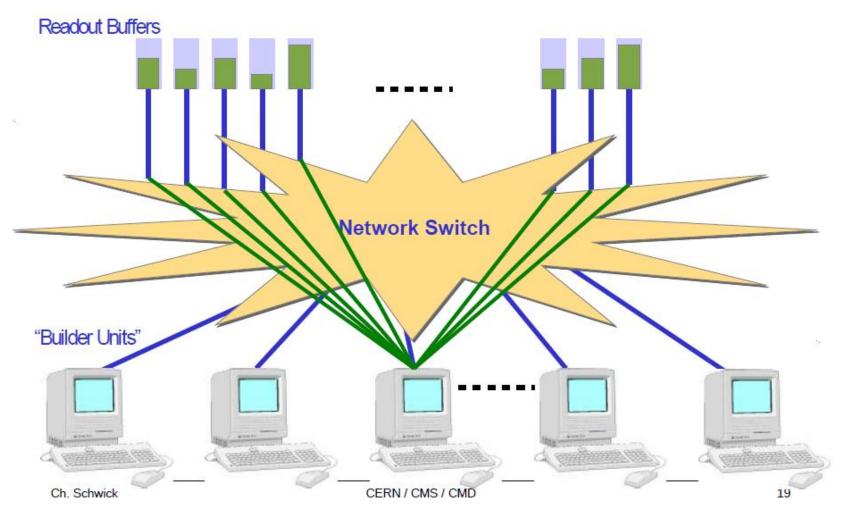

#### **Event Builder**

### ТЛП

#### Event Builder,

#### taken from my KEKB colleague Suzuki-san

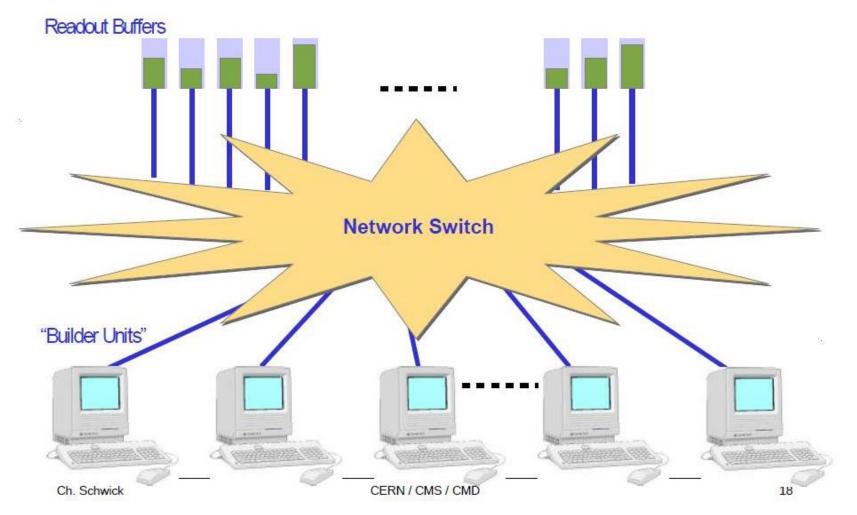

#### **Event Building Challenges I**

From CERN ISODAQ School

### **Event Building Challenges II**

From CERN ISODAQ School

#### Traffic Pattern Causes Congestion Problem

From CERN ISODAQ School

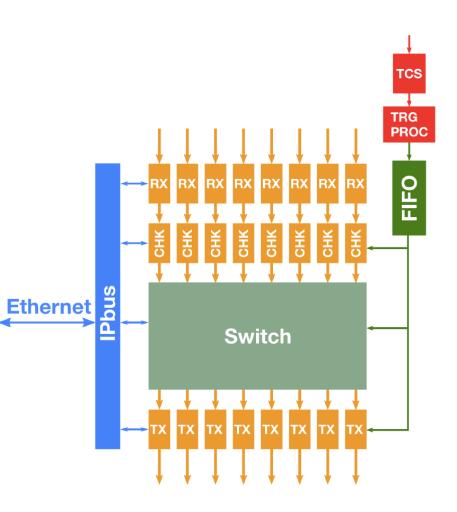

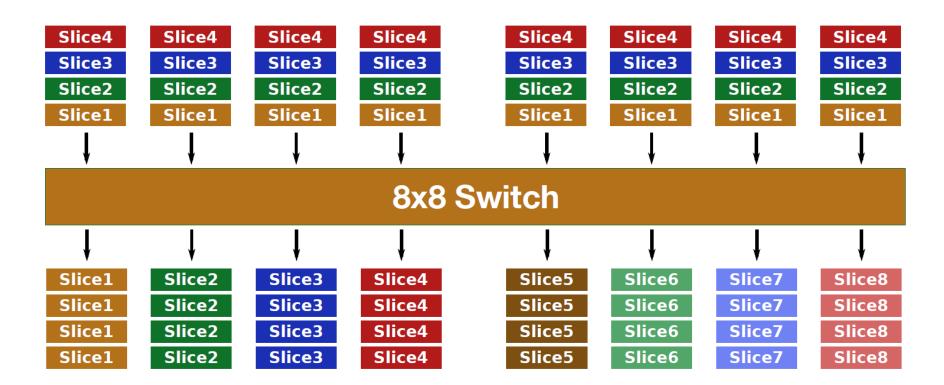

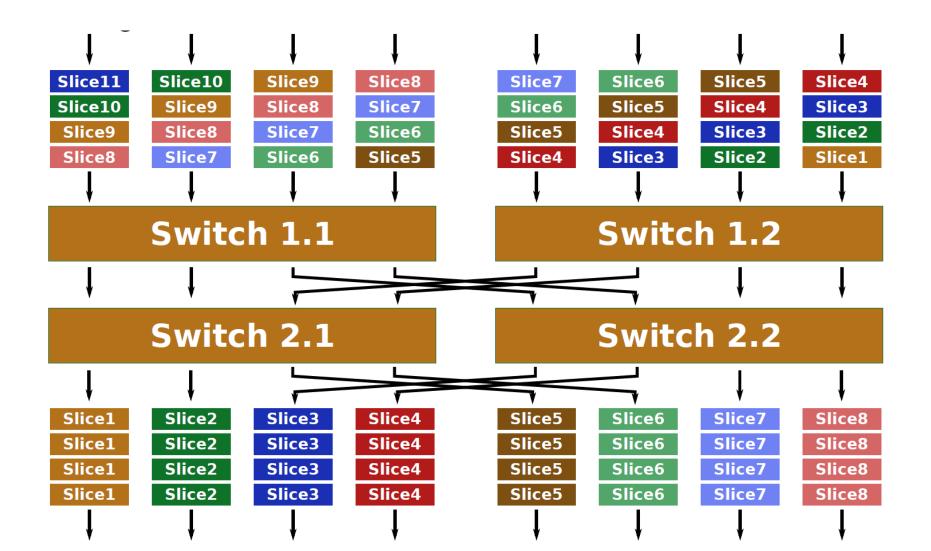

# **Event Builder Firmware**

Control incoming data streams

Verification of data consistency

Control of 8 x 8 switch

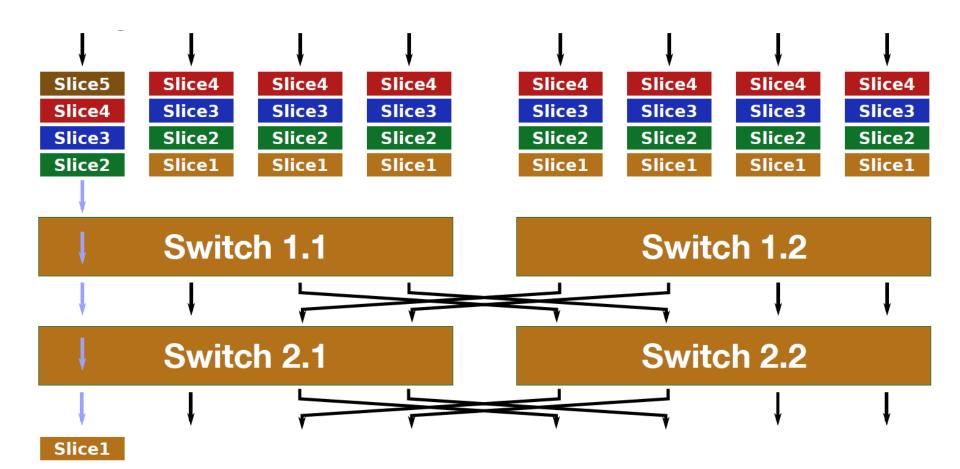

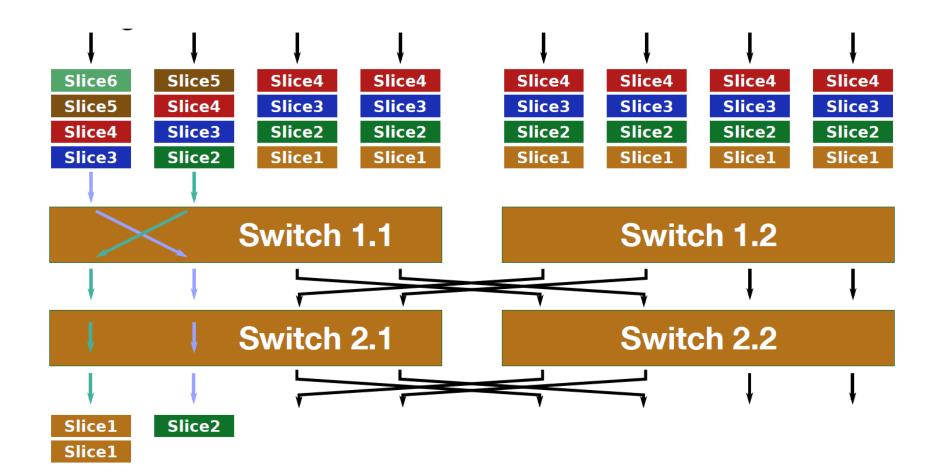

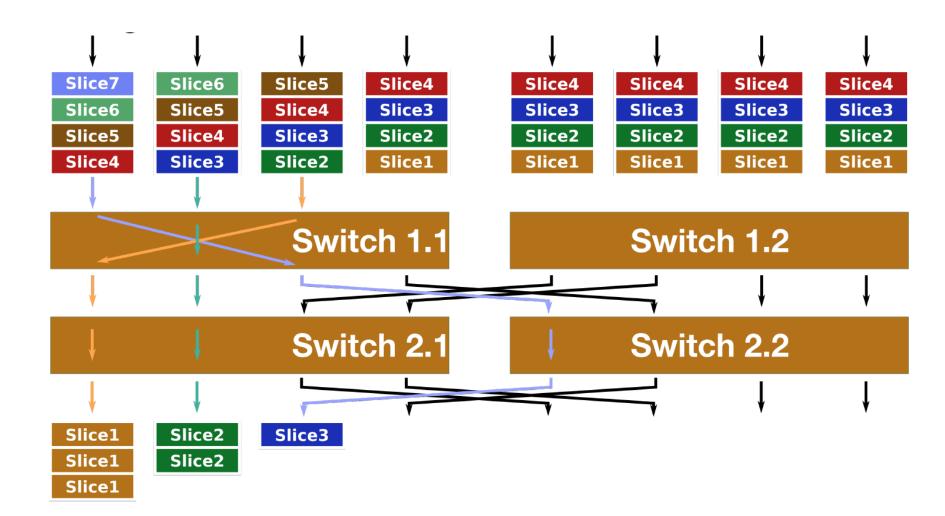

# **Event Builder Firmware**

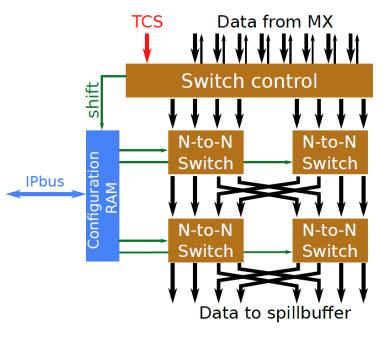

- Switch control

- Defines switch interconnections

- Connects one input to one output

- Combines N consecutive events in one SLICE

- Average size of SLICEs

- After processing one SLICE changes switch interconnections to the next one

- Information about different interconnections stored in RAM

# Switch Operation

# Switch Operation

ЛШ

ЛШ

# Spill Buffer PCIE Card

Commercial hardware

- Nereid Kintex 7 PCI Express

- Kintex 7 XC7K160T FPGA

- 4 x PCIe-Gen2 Interface

- 4 GB DDR3 memory

# ТШП

# Spill Buffer Firmware

- Single 6.25 Gb/s 8b/10b Aurora interface

- Data

- Trigger information

- Switch configuration

- Events stored in DDR3 memory

- · Combination of events according to

- event number

- switch configuration

- Built events pushed to PCIe

- Internal bandwidth 3 GB/s

Event size, pointers, ...

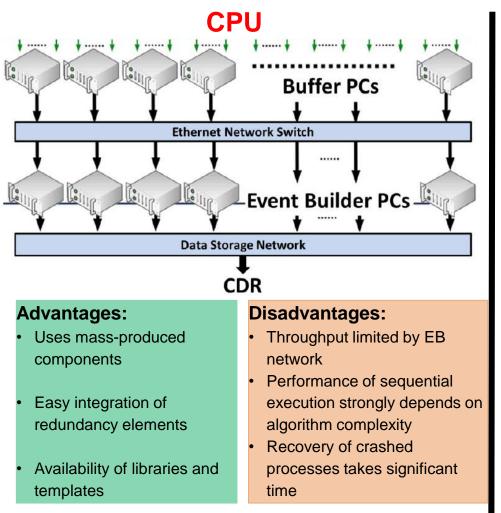

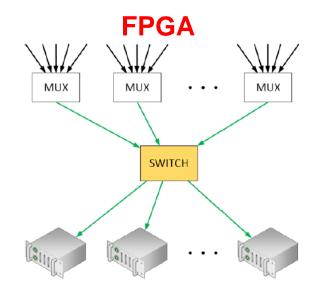

# Event Building CPU vs FPGA

#### Advantages:

- Only FPGA allows to build real real-time system

- High scalability

- High reliability

- Low cost

#### **Disadvantages:**

- Long firmware development progress: high level simulation tools like System Verilog and OSVVM

- $\Rightarrow$  Motivation

- Minimize real time SW processes

- Development of highly autamotized and reliable DAQ

# ЛШ

### iFDAQ

Compact : **Before** : 30 online PCs **Now** : one VME 6U crate + 1 rack (8 computers)

Hardware Event Builder

#### Performance : Up Time in 2017