Rodrigo A. Melo VHDL for FPGA **Synthesis** Virtual | Ene | 2021

Joint ICTP-IAEA School on FPGA-based SoC and its Applications for Nuclear and Related Instrumentation | (smr 3562)

## Introduction

#### **Hardware Description Languages**

#### **VHDL**

- Very High Speed Integrated Circuit (VHSIC) + HDL

- U.S. Department of Defense (1983)

- Standard IEEE 1076 (87, **93**, 00, 02, 08, 19)

#### Verilog

- VERIfication + LOGic

- Gateway Design Automation (1984), Cadence (1990)

- Standard IEEE 1364 (95, **01**, 05)

- Verilog is now part of System Verilog (IEEE 1800)

"Xilinx is now shipping Foundation Series design solutions capable of supporting both VHDL and Verilog."

Xcell Journal, issue 27, 1998

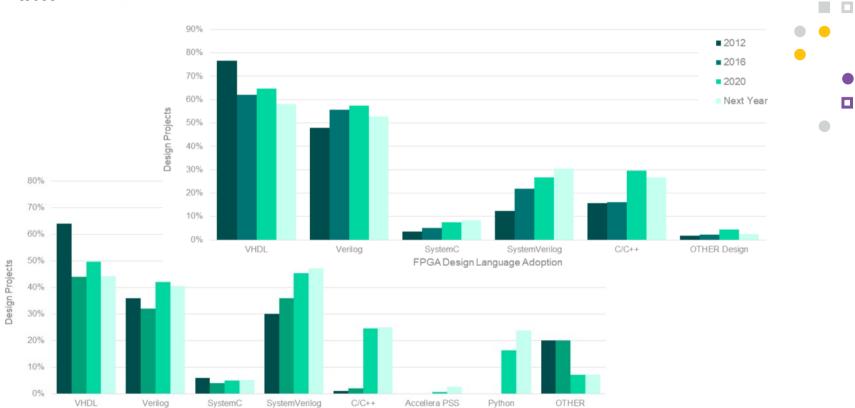

## Languages trends

FPGA Verification Language Adoption Source: The 2020 Wilson Research Group Functional Verification Study

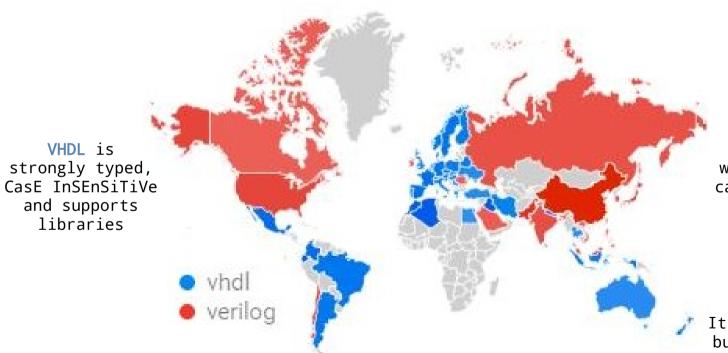

## Nacional de Tecnología VHDL vs Verilog

Verilog is weakly typed, case sensitive and doesn't supports libraries

It is more concise but allows you to write wrong code

#### de Tecnología Industrial HDL for Synthesis

- Only a small subset of the language is synthesizable.

- It is used to describe the **behavior** and/or the **structure** of a digital design.

- You are no writing a software program, you are describing hardware (concurrent code, executed in parallel).

- You can write small combinational circuits parts (asynchronous) but is recommendable to perform synchronous design (based on one or multiple clocks).

Now, we will take a crash course about the VHDL fundamentals for synthesis.

#### Our basic guidelines

- Use UPPERCASE for constants

- Use indentation (4 spaces)

- Use coherent\_and\_descriptive names

- Use meaningful prefixes/suffixes (\_i, \_o, \_r)

# **Basic VHDL**

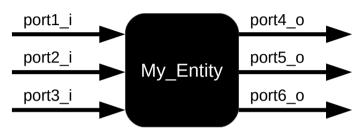

#### de Tecnología Structure of a component

#### **Libraries & Packages Entity** In Out Generics, ports **Architecture** Declarations (signals, types, functions, procedures) Begin Functionality (sentendes, instantiations, asignations)

The file extension is usually vhd or vhdl

- Package provides data types, functions and components, to extend the language support.

- The Entity defines the name and the interface of our component..

- An Architecture implements the functionality of a given Entity.

Commonly, you will have one Entity and one or more related Architectures per file.

### de Tecnología Industrial Libraries and Packages inclusion

```

-- library LIBRARY;

-- use LIBRARY.PACKAGE.all;

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

-- Synopsys non-standard packages

-- use IEEE.std_logic_arith.all;

-- use IEEE.std_logic_signed.all;

-- use IEEE.std_logic_unsigned.all;

```

These packages are commonly found in examples, but they are non-standard. Avoid them!!!

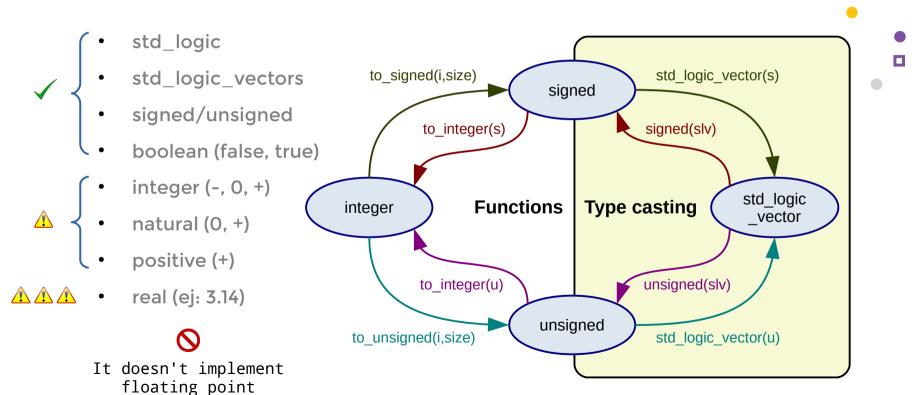

Mandatory for a synthesizable design. It provides the std\_logic (1 bit) and std\_logic\_vector (bus) types (to support 'U', 'X', '0', '1', 'Z', 'W', 'L', 'H' and '-' instead of only '0' and '1')

The numeric\_std package provides arithmetic functions for vectors. It derives from std\_logic\_vector two other types: signed and unsigned.

I recommend to know the content (read the source code) of these two packages

```

use only

in and out

modes

```

```

use only

std_logic and

std_logic_vector

types

```

use **inout** mode only in the Top-level.

don't use the **buffer** mode.

#### Nacional de Tecnología Industrial Architecture

```

architecture My_Arch of My_Entity is

-- declarations

begin

-- instantiations

-- concurrent statements

-- sequential statements

end architecture My_Arch;

Opt

Opt

Opt

Opt

```

- Each Architecture belongs to an Entity (of).

- Generally, you will have more than one Architecture per Entity when looking for alternatives to the same functionality (high-speed vs area, different algorithms, etc).

- The Architecture is where you "design" your component.

## Our first example

```

library IEEE;

use IEEE.std logic 1164.all;

entity nor3 is

port (

a i : in std logic;

b i : in std logic;

c_i : in std_logic;

q_o : out std_logic

end entity nor3;

architecture rtl of nor3 is

begin

q_o <= not(a_i or b_i or c_i);</pre>

end architecture rtl;

```

- Imports std\_logic

- Entity definition

- 3 x 1-bit inputs

- 1-bit output

- The architecture implements a 3-input NOR logic function

It is for illustrative purposes,

it has not much sense as an

individual component.

#### Nacional de Tecnología Instantiation Industrial

```

architecture alternative1 of top is

component nor3 is

port (

a_i : in std_logic;

b i : in std logic;

c i : in std logic;

q o : out std logic

);

end component nor3;

begin

-- label : name

nor3 inst : nor3

port map (

a i \Rightarrow port1 i, b i \Rightarrow port2 i,

c_i => port3_i, q_o => port4_o

end architecture alternative1;

```

**A**

Labels are optional but recommended.

Alternative 2: put your component declaration in a user defined package, in your own library.

```

architecture alternative3 of top is

begin

-- label: entity library.name(arch)

nor3_inst : entity work.nor3

port map (

a_i => port1_i, b_i => port2_i,

c_i => port3_i, q_o => port4_o

);

end architecture alternative3;

```

#### Most used data types

| Operator         | Description    |

|------------------|----------------|

| a ** b 🛕         | exponentiation |

| abs a            | absolute value |

| not a            | complement     |

| a * b            | multiplication |

| a/b <u>^</u>     | division       |

| a mod b <u>∧</u> | modulo         |

| a rem b <u>∧</u> | remainder      |

| +a               | unary plus     |

| -a               | unary minus    |

| a + b            | addition       |

| a - b            | subtraction    |

| a & b            | concatenation  |

| Operator | Description                        |

|----------|------------------------------------|

| a = b    | test for equality                  |

| a /= b   | test for inequality                |

| a < b    | test for less than                 |

| a <= b   | test for less than or equal        |

| a > b    | test for greater than              |

| a >= b   | test for greater than or equal     |

| a and b  | logical and                        |

| a or b   | logical or                         |

| a nand b | logical complement of and          |

| a nor b  | logical complement of or           |

| a xor b  | logical exclusive or               |

| a xnor b | logical complement of exclusive or |

## Shift/rotate functions

| Operator  | Description            | Function           |

|-----------|------------------------|--------------------|

| a ssl N 🚫 | shift left logical     | shift_left(a, N)   |

| a srl N 🚫 | shift right logical    | shift_right(a, N)  |

| a sla N 🚫 | shift left arithmetic  | shift_left(a, N)   |

| a sra N 🚫 | shift right arithmetic | shift_right(a, N)  |

| a rol N 🚫 | rotate left            | rotate_left(a, N)  |

| a ror N 🚫 | rotate right           | rotate_right(a, N) |

Wrong defined, don't use them!!! (unexpected behaviour and/or extra hardware).

Defined into the *numeric\_std* package. Another useful function there is *resize(a, N)*.

```

architecture MyArch of MyEntity is

-- signal name: type [:=default];

signal slv8 : std logic vector(7 downto 0); -- default="UUU"

signal slv3 : std logic vector(2 downto 0):="101";

signal slv5 : std logic vector(4 downto 0):=(others => '0');

signal slv4 : std logic vector(3 downto 0);

signal slva, slvb, slvc : std logic vector(3 downto 0);

signal to1, to2 : std_logic_vector(1 to 4);

signal nat : natural range 0 to 15:=1; -- default=0

begin

-- signal name <= expression;</pre>

slv8 <= slv3 & slv5; -- concatenation ("10100000")

slv4 <= slv5(3 downto 0); -- slice

slva <= slvb xor slvc; -- propagation time involved</pre>

-- hardwired value

to2 <= "0101";

-- connection

to1 <= to2;

end architecture MyArch;

<= is employed to assign the value

of a signal (can be time involved).

```

By convention, we generally use downto.

Default/initial values

are ignored by ASIC

synthesis tools.

For synthesis, always use range with integers and its subtypes (natural, positive).

#### **Concurrent vs Sequential statements**

```

architecture MyArch of MyEntity is

-- declarations

begin

Concurrent statement:

Concurrent statement;

process ()

begin

Sequential statement;

Sequential statement;

Sequential statement;

end process;

Concurrent statement;

begin

Sequential statement;

Sequential statement;

end process;

end architecture MyArch;

```

#### **Concurrent Statements**

- Instantiation

- Signal assignment

- when/else

- with/select

- process

#### **Sequential statements**

- if/else

- case/when

- for/loop

- while/loop

- loop

Advanced

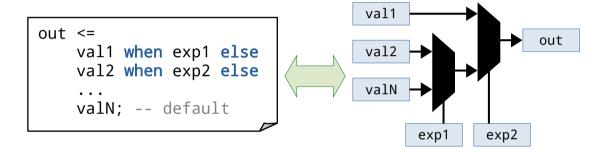

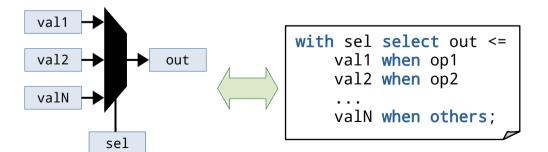

#### **Concurrent statements**

Priorities and differents propagation times involved.

- valX can be a value, signal or expression.

- expX must be a boolean expression.

- **selX** can ve a signal or expression.

- opX are different values of sel.

```

architecture MyArch of MyEntity is

-- declarations

begin

label : process (sensitivity list)

Opt

begin

Sequential statement;

Sequential statement;

Sequential statement;

end process label;

end architecture MyArch;

```

- Is a circuit part which can be active or inactive.

- A process activates when a signal in the sensitivity list changes its value.

- All the process blocks are executed in parallel (concurrent statements).

- Sequential statements allow us to describe the abstract behaviour of a circuit rather than using low-level components (easiest for humans).

Sequential statements are sequentially evaluated (not executed as in a processor).

Inside a process, a signal can be assigned multiple times, but only the last assignment takes effect.

```

label : process (a, b)

-- variable name: type [:=default];

variable tmp0, tmp1, tmp2 : std_logic;

begin

-- variable_name := expression;

tmp0 := '0';

tmp1 := tmp0 or a;

tmp2 := tmp1 or b;

y_o <= tmp2;

end process label;</pre>

```

- Are similar but different than a signal.

- Are declared and visible inside a process.

- Its value changes without delay involved.

- Are assigned with := instead of <=.</li>

The VHDL variables are similar to a programming language variable because you can assign them in a line and read its updated value in the following one. It doesn't happen with a signal.

You can use a variable to produce the same hardware than a signal, but we recommend you to use them only to store intermediate values.

#### Sequential statements

```

label : process (...)

-- declarations;

begin

if exp1 then

-- sentences

opt elsif exp2 then

-- sentences

opt else

-- default

-- sentences

end if;

end process label;

```

```

<u>^</u>

```

Be careful with the incomplete assignment (memory inference).

```

label : process (...)

-- declarations;

begin

case sel is

when op1 =>

-- sentences

when op2 to op5 =>

-- sentences

when op6 | op8 |

op11 =>

-- sentences

when others =>

-- default

-- sentences

end case:

end process label;

```

be nested.

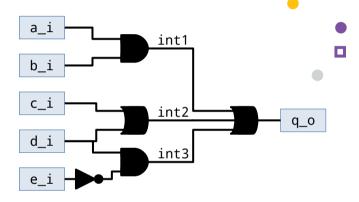

# Concurrent circuits (aka combinational or asynchronous)

```

library IEEE;

use IEEE.std logic 1164.all;

entity comb is

port (

a_i, b_i, c_i, d_i, e_i : in std_logic;

q o : out std logic

end entity comb;

architecture alt1 of comb is

signal int1, int2, int3 : std logic;

begin

int1 <= a i and b i;

int2 <= c i or d i;

int3 <= d i and (not e i);</pre>

q o <= int1 or int2 or int3;

end architecture alt1;

```

- No internal state (no storage, so only LUTs are inferred)

- The outputs only depends on the inputs

# de Tecnología Industrial Concurrent circuits (using a process)

```

architecture alt2 of comb is

signal int1, int2, int3 : std logic;

begin

process (

a_i, b_i, c_i, d_i, e_i,

int1, int2, int3

begin

int1 <= a i and b i;

int2 <= c i or d i;

int3 <= d i and (not e i);</pre>

q o <= int1 or int2 or int3;

end process;

end architecture alt2;

```

```

-- using variables

architecture alt3 of comb is

begin

process (a_i, b_i, c_i, d_i, e_i)

variable int1, int2, int3 :

std logic;

begin

int1 := a i and b i;

int2 := c i or d i;

int3 := d i and (not e i);

q o <= int1 or int2 or int3;</pre>

end process;

end architecture alt3;

```

Synthesizers don't check the Sensitivity list. All the inputs must be included to avoid a simulation mismatch!

# Sequential circuits (aka synchronous)

- They have an internal state (flip-flops, aka registers, are inferred)

- The output depends on the inputs and the internal state

- Depends on a clock (synchronous)

|                  | Asynchronous          | Synchronous                   |  |

|------------------|-----------------------|-------------------------------|--|

| Speed            | Faster (max)          | Depends on clock and the arch |  |

| Power            | Probably lower        | Depends on the arch           |  |

| Area             | Probably higher       | Depends on the arch           |  |

| Development time | Longer                | Shorter                       |  |

| Debug            | Very difficult        | Easiest                       |  |

| Reliability      | Need a lot of testing | Strong                        |  |

```

label : process (clk_i)

begin

if rising_edge(clk_i) then

-- do something

end if;

end process label;

```

OR

```

label : process (clk_i)

begin

if falling_edge(clk_i) then

-- do something

end if;

end process label;

```

Don't do that. The FPGA have only one clock input per FF. You will be using more area, to get lower speed.

OR

- With FPGA, you will normally use synchronous reset.

- Asynchronous reset is common in ASIC designs.

Don't reset more than the needed.

## Counter example (part I)

```

library IEEE;

use IEEE.std logic 1164.all;

use IEEE.numeric std.all;

entity cnt12 is

port (

clk i : in std logic;

rst i : in std logic;

cnt o : out std logic vector(3 downto 0)

end entity cnt12;

architecture RTL of cnt12 is

constant MOD : positive := 12;

signal cnt : unsigned(3 downto 0); -- 16

begin

```

- We will implement a counter module 12 (from 0 to 11).

- A constant is employed to avoid a magic number (good practice).

- There are two reasons to use the signal cnt instead of the port cnt\_o (next slide).

Remember (good practice):

use only **std\_logic** and **std\_logic\_vector** types for ports.

#### de Tecnología Counter example (part II)

```

begin

counter : process (clk_i)

begin

if rising edge(clk i) then

if rst i = '1' then

cnt <= (others => '0');

else

if cnt < MOD then</pre>

cnt <= cnt + 1;

else

cnt <= (others => '0');

end if:

end if:

end if:

end process counter;

cnt_o <= std_logic_vector(cnt);</pre>

end architecture RTL;

```

- Addition (cnt + 1) is not defined for std\_logic\_vector.

- An output can't be read (cnt <= cnt + 1;). You need an intermediate signal connected to the output.

Remember (good practice): use synchronous reset (if needed).

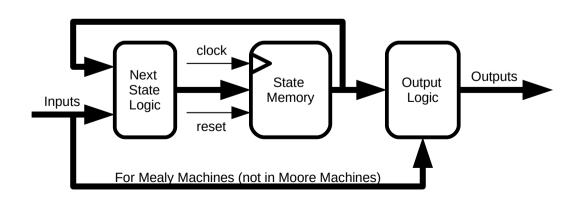

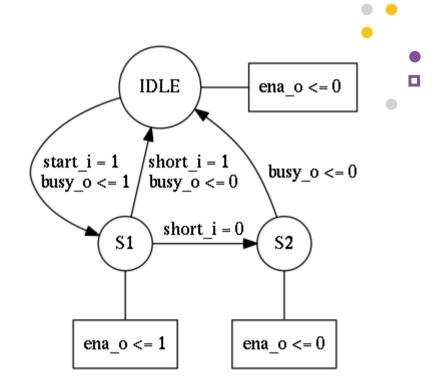

## **Finite State Machines**

| Asynchronous/Combinational                  | Synchronous/Sequential                       |   |

|---------------------------------------------|----------------------------------------------|---|

| No internal state (no memory)               | They have an internal state (FFs, registers) | • |

| Probably Outputs only depends on the inputs | Output depends on inputs/internal state      |   |

| No depends on a clock                       | Depends on a clock                           |   |

- A systematic design technique for sequential circuits, which leads to near/optimal implementations

- Clock-by-clock the machine will be in one of the finite possible states

- The state segmentation helps to detect where there are problems

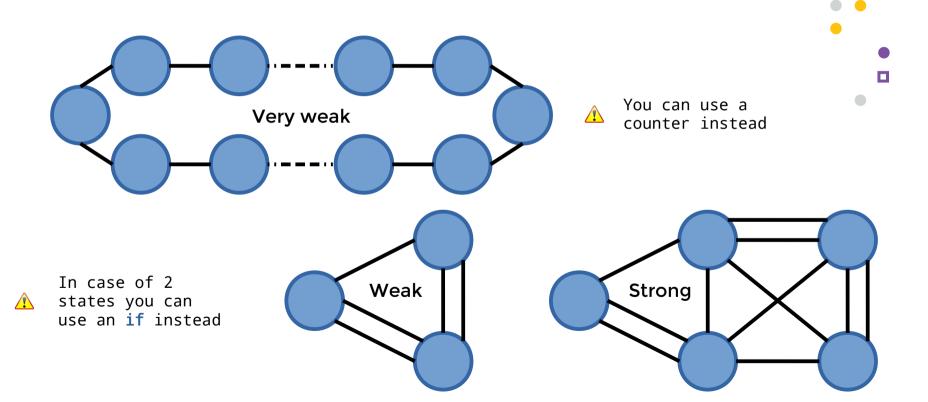

## Macional de Tecnología Undustrial When to use an FSM?

#### States diagram

- Graphical representation of the functional specification

- It must include all possible states.

- All transition conditions that are not unconditional must be specified

- The list of output signals must be the same in all the states

```

architecture FSM of My_Entity is

type state_type is (IDLE_S, S1_S, S2_S);

signal state: state_type;

begin

-- the FSM process here

end architecture FSM;

```

- States in VHDL are defined using enumerations.

- Enumerations in VHDL are defined creating a new type.

- FSM are synchronous and modelated with a case/when statements.

- Each state specify actions and trasanction conditions.

- All the states must be specified (use when others when needed).

```

my fsm : process (clk i) begin

if rising_edge(clk_i) then

if rst i = '1' then

state <= IDLE S;</pre>

else

case sel is

when IDLE S =>

when S1 S =>

when S2_S =>

end case:

end if:

end if;

end process my fsm;

```

#### State encoding

- **Sequential:** conventional binary code (2<sup>N</sup> states)

- One-Hot: one bit per state (N states)

- Johnson: uses a Johnson ring counter (2xN states)

- **Gray:** uses Gray encoding (2<sup>N</sup> states)

- Modified One-Hot: the bit 0 is inverted to start in reset (N states)

- User-defined and auto (default)

It is normally selected by the Synthesis tool, but you can specify another one with tool-specific options.

## Nacional de Tecnología Industrial Transitions

```

when STATE1 S =>

state <= STATE2 S; -- unconditional</pre>

when STATE2 S =>

if cond1 then

state <= STATE3 S;</pre>

end if:

when STATE3 S =>

if cond1 then

state <= STATE1 S;</pre>

elsif cond2 then

state <= STATE2 S;</pre>

else

state <= STATE4 S;</pre>

end if;

```

- The transition to a new state is achieved by assigning the signal that models the state.

- Conditional transitions are modeled with if, elsif, else (be carefull with the priorities).

- condX could be input ports, signals (internal or external to the FSM, such a counter value), etc.

```

-- Output registered in the process

-- which implements the FSM

when STATE1_S =>

port1_o <= '1';

when STATE2_S =>

if cond1 then

port1_o <= '0';

end if;</pre>

```

```

-- Output registered in another

-- process

do_assign : process (clk_i)

begin

if state=STATE2_S then

port2_o <= '0';

if cond2 then

port2_o <= '1';

end if;

end process do_assign;</pre>

```

```

clk state comb

```

```

-- Combinational assign

port3_o <= '1' when state = STATE3_S else '0';</pre>

```

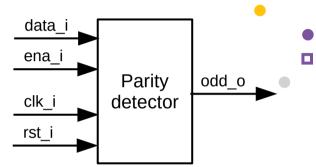

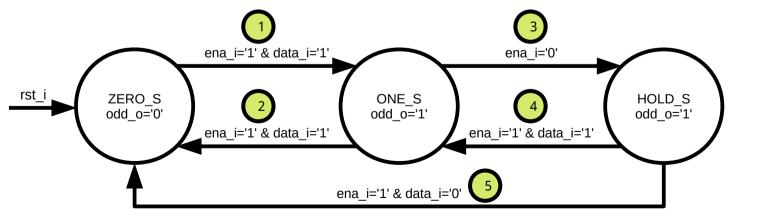

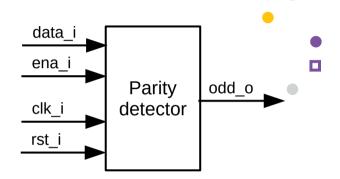

## **Example - Parity Detector - Definition**

- Serial input data.

- While enabling, parity is observed.

- When enable goes down, the output indicates even or odd quantity.

## **Example - Parity Detector - Entity**

```

library IEEE;

use IEEE.std logic 1164.all;

entity ParityDetector is

port (

clk i : in std logic;

rst_i : in std_logic;

ena_i : in std_logic;

data i : in std logic;

odd o : out std logic

);

end entity ParityDetector;

architecture FSM of ParityDetector is

type state_type is (ZERO_S, ONE_S, HOLD_S);

signal state : state_type;

begin

```

### de Tecnología Example - Parity Detector - Architecture

```

do fsm : process (clk i)

begin

if rising_edge(clk_i) then

if rst i = '1' then

state <= ZERO S;

else

-- the case here

end if:

end if:

end process do fsm;

odd o <= '1' when state/=ZERO S;

end architecture FSM;

```

```

case state is

when ZERO S =>

if ena_i='1' and data_i='1' then

state <= ONE S;

end if:

when ONE S =>

if ena i='1' then

if data i='1' then

state <= ZERO S;

end if:

else

state <= HOLD S;

end if:

when HOLD S =>

if ena i='1' then

if data_i='1' then

state <= ONE S;</pre>

else

state <= ZERO S;

end if:

end if:

end case:

```

## **Considerations for Synthesis**

```

architecture my arch of my ent is

signal data : std logic;

begin

proc1 : process (clk_i)

begin

if rising edge(clk i) then

data <= '0':

end if:

end process proc1;

proc2 : process (clk i)

begin

if rising_edge(clk_i) then

data <= '1':

Multiple

end if:

drivers,

end process proc1;

can't be

end architecture my_arch;

synthesized.

```

```

entity bidir is

port (

data io : inout std logic;

data_i : in std_logic;

data o : out std logic;

wr i : in std logic

end entity bidirr;

architecture RTL of bidir is

begin

data io <= data i when wr i='1' else 'Z';

data o <= data io;</pre>

end architecture RTL;

You can use inout

in the IO blocks

of an FPGA, but

normally not

internally.

```

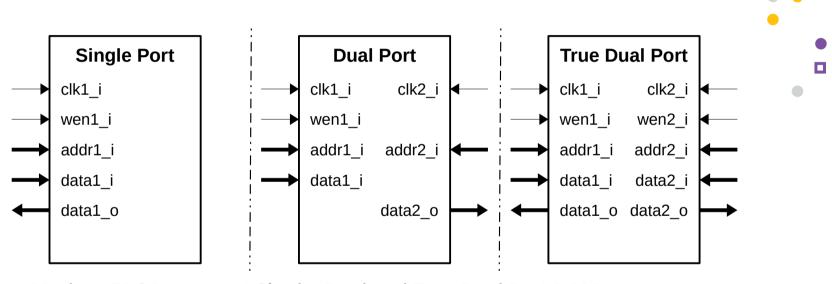

### Memory Inference (I)

- Modern FPGAs support Single, Dual and True Dual Port RAMs.

- Can be instantiated or inferred.

- The description of an unsupported characteristic produces distributed memory.

## de Tecnología Memory Inference (II)

```

architecture Memory of SinglePortRAM is

type ram_type is array (0 to 15) of std_logic_vector(7 downto 0);

signal ram : ram type;

begin

ram_p: process (clk_i)

begin

if rising edge(clk i) then

data o <= ram(to integer(unsigned(addr i)));</pre>

if wen i='1' then

ram(to_integer(unsigned(addr_i))) <= data_i;</pre>

end if:

end if:

addr_i[3:0]

end process ram_p;

data i[7:0]

Single

data_o[7:0]

-- data o <= ram(to integer(unsigned(addr i)));</pre>

Port

wen i

RAM

end architecture Memory;

clk i

```

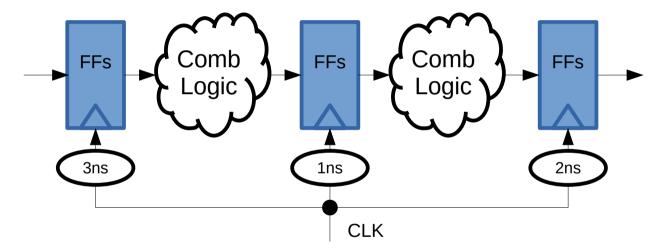

- Clock skew: the same clock signal arrives different components at different times.

- To reduce this effect, you must use global buffers, to employ the clock tree.

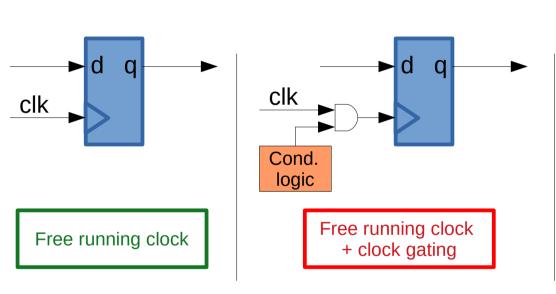

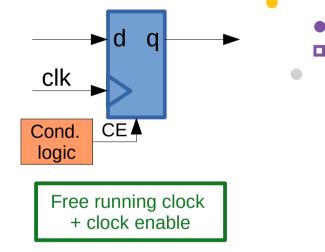

## **Clock strategies**

0

Don't do that in an FPGA.

FPGAs have a predefined clock tree.

The FFs of an FPGA have a chip-enable port.

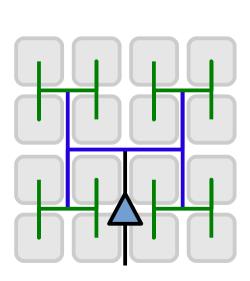

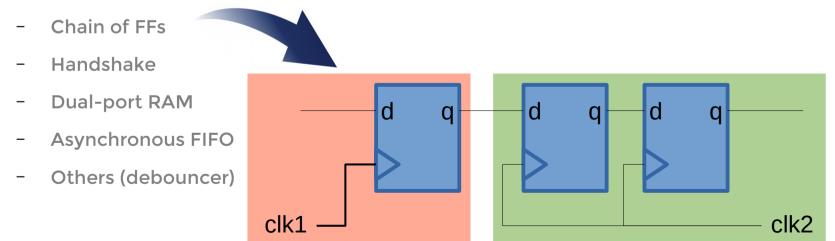

## **Clock Domain Crossing**

- Metastability can cause system failures in digital devices when a signal is transferred between unrelated or asynchronous clock domains.

- CDC techniques:

```

architecture Latches of my ent is

begin

process (ena i, data i)

begin

if ena i = '1' then

latch1 o <= data i;</pre>

end if:

end process ram_p;

latch2 o <=

"0000" when sel i = "00" else

"0011" when sel i = "01" else

"1111" when sel i = "10":

end architecture Latches;

```

- FSs are active by a clock edge, while latches are active by level.

- Latches are created when you have an incomplete assignment using a combinational process or a conditional assignment.

- Latches should never be used in your FPGA design:

- They are usually unintentional.

- They are usually a problem for the FPGA tools (which normally complains about them).

(parametric and reutilizable code)

#### de Tecnología Generics - Declaration

```

entity RAM is

generic (

Generics are constant values

-- NAME: type [:=default];

AWIDTH : positive := 4;

defined at instantiation time. It

DWIDTH : positive := 8;

allows writing of parametric

DEPTH : positive := 16

designs (reusability).

);

port (

clk i : in std logic;

addr i : in std logic vector(AWIDTH-1 downto 0);

data i : in std logic vector(DWIDTH-1 downto 0);

They are commonly natural, positive

data o : out std logic vector(DWIDTH-1 downto 0);

or boolean. Sometimes (Xilinx), you

wr i : in std logic

can found string or real.

end entity RAM;

architecture Memory of RAM is

type ram_type is array (0 to DEPTH-1) of std_logic_vector(DWIDTH-1 downto 0);

signal ram : ram_type;

```

#### Nacional de Tecnología Generics - Instantiation Industrial

```

architecture my arch of my ent is

signal in1, in2, out1, out2 : std logic vector(7 downto 0);

signal addr1, addr2 : std_logic_vector(2 downto 0);

begin

ram1 : ram

generic map (AWIDTH => 2, DWIDTH => 8, DEPTH => 4)

port map (

clk i \Rightarrow clk i, wen i \Rightarrow '1',

addr i => addr1(1 downto 0), data i => in1, data o => out1

ram2 : ram

generic map (AWIDTH => 3, DEPTH => 8) -- DWIDTH = 8 (default)

port map (

clk i \Rightarrow clk i, wen i \Rightarrow '1',

addr i => addr2, data i => in2, data o => out2

end architecture my_arch;

```

```

entity my_ent is

generic (

ENABLE : boolean := true;

QUANTITY : positive := 2

);

port (

...

);

end entity my_ent;

```

By far, if generate is the easiest alternative.

```

architecture my_arch of my_ent is

begin

label_if : if ENABLE generate

-- concurrent statements

-- or instantiation

end generate label_if;

label_not :

if not ENABLE generate

-- there is not an

-- else generate

end generate label_not;

end architecture my_arch;

```

```

entity vector inv is

generic (WIDTH : positive := 4);

port (

data_i : in std_logic_vector(WIDTH-1 downto 0);

data o : out std logic vector(WIDTH-1 downto 0)

);

end entity my_ent;

The range must

architecture my arch of my ent is

be a CONSTANT

begin

value!

my for : process (data i)

begin

for i in 0 to WIDTH-1 loop

data o[WIDTH-1-i] <= data i[i];</pre>

end loop;

You must

end process my_for;

deal with

end architecture my_arch;

indexes!

```

- Useful for iterative HW replication. Be careful! Think on loop unrolling.

- The range attribute can be useful (data\_i'RANGE).

- You can use while and loop but uncommon for synthesis.

## de Tecnología Subprograms - functions Industrial

```

architecture my arch of my ent is

function bin2gray(arg: unsigned) return unsigned is

-- declarations (no signals)

begin

return shift right(arg, 1) xor arg;

end function bin2gray;

function bin2gray(arg: std logic vector) return std logic vector is

begin

return std_logic_vector(bin2gray(unsigned(arg)));

end function bin2gray;

signal aux1 : unsigned(7 downto 0);

signal aux2 : std_logic_vector(7 downto 0);

begin

aux1 <= bin2gray("10101010");

aux2 <= bin2gray("10101010");</pre>

end architecture my_arch;

```

- Only inputs

- Sequentially evaluated

- No time (no signals)

- One output (return)

- Supports overloading

## **Subprograms - procedures**

- Functions and Procedures are like C macros (replaced in place).

- For synthesis, you can found simple functions (types conversion or small computations), being the procedures rarely employed (similar to components).

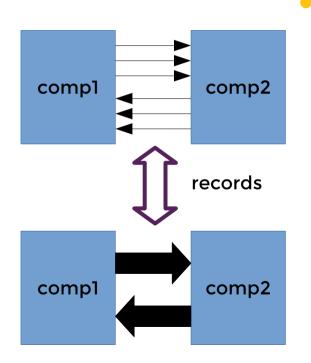

```

architecture my_arch of my_ent is

type instruction t is record

opcode : std logic vector(3 downto 0);

addr : std_logic_vector(11 downto 0);

data : std_logic_vector(15 downto 0);

end record instruction t;

signal ir : instruction t;

begin

ir.opcode <= "1010";

ir.addr <= X"123";

ir.data <= X"CAFE";</pre>

data o <= ir.data;</pre>

ir o <= ir;

end architecture my arch;

```

## de Tecnología User defined Libraries and Packages Industrial

```

library IEEE;

use IEEE.std logic 1164.all;

package My_Package is

-- constants

-- components declarations

-- functions declarations

-- procedures declarations

-- types, subtypes, records

end entity My Package;

package body My_Package is

-- functions implementations

-- procedures implementations

end package body My Package;

```

```

The library name definition is tooldependant.

```

```

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

library My_Library;

use My_Library.My_Package.all;

```

#### Attributes:

- Provides additional information about a signal (S'EVENT)) or a type (T'RIGHT).

- There are predefined attributes in the VHDL specification, predefined attributes per tool and can be also user-defined.

- Allows parametric and more clear code (normally employed in libraries).

#### Types:

- You can define new types (such as std\_logic\_vector) and subtypes (such as signed and unsigned).

- Essential for FSM (enumerations) and memory inference (arrays).

- Configurations: I have never seen FPGA projects using a configuration (ASIC?).

## Conclusions

- There are more things to know when you want to understand any VHDL description.

- There are even more to understand about FPGAs and the EDA tools for a complete system integration.

- Be synchronous and apply good practices! All will be easier and better.

- in rodrigoalejandromelo

- @rodrigomelo9ok

- g rodrigomelo9

- rodrigomelo9

## Thank you

This work is licensed under CC BY 4.0

# If you want to know more about INTI, we wait for you at

- f INTIArg

- @INTlargentina

- in INTI

- @intiargentina

- canalinti

www.inti.gob.ar consulta@inti.gob.ar 0800 444 4004

Joint ICTP-IAEA School on FPGA-based SoC and its Applications for Nuclear and Related Instrumentation | (smr 3562)