#### Rodrigo A. Melo VHDL for FPGA Simulation

Virtual | Feb | 2021

Joint ICTP-IAEA School on FPGA-based SoC and its Applications for Nuclear and Related Instrumentation | (smr 3562)

### Introduction

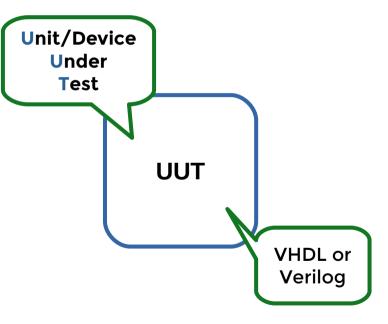

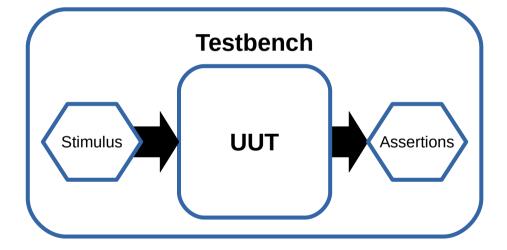

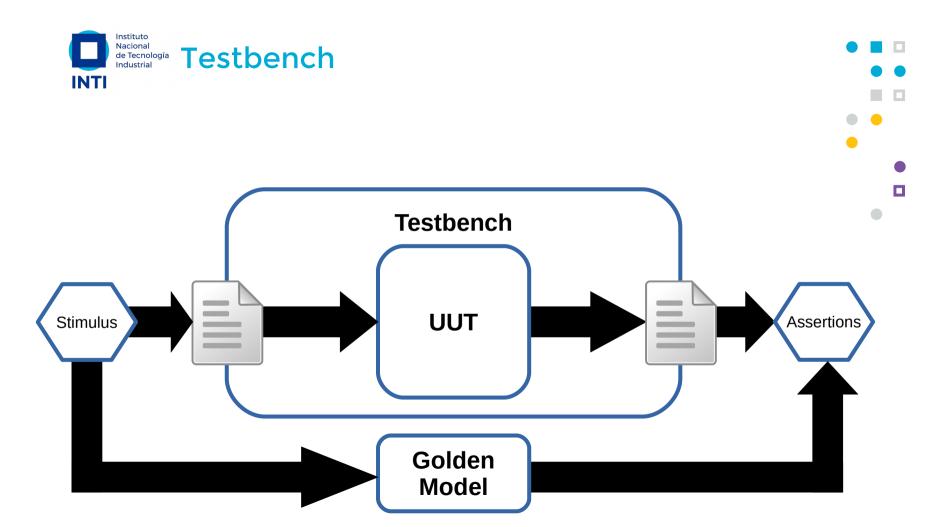

- Verification: to check if a design works as expected.

- In-Circuit Debug:

- Performed in a test bench, with a Scope (simple design with a few signals), Logic

Analyzer (\$\$\$) or Embedded Logic Analyzer (modify your design).

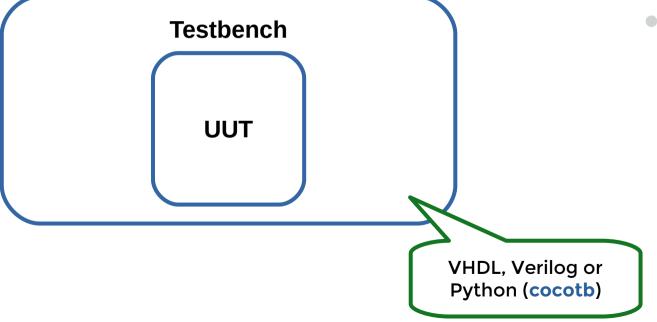

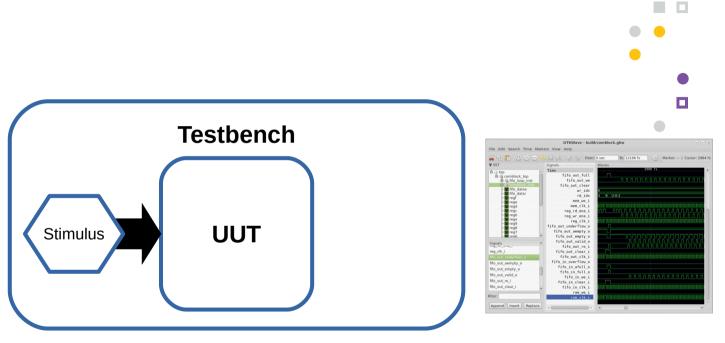

- Functional verification:

- Stimulus are provided and the output compared with expected values, according to a specification.

- It implies a testbench (generally an HDL) and a simulator

- Formal verification:

- Generally speaking, you need to specify formal properties and a tool checks your design against formal methods (mathematical proof). Ex: SymbiYosys (FOSS).

- UVM: Universal Verification Methodology

- Open Verification Methodology

- Functional verification using SystemVerilog

- Supported by a few very expensive simulators (and Vivado?)

- FOSS:

- **OSVVM:** Open Source VHDL Verification Methodology

- UVVM: Universal VHDL Verification Methodology

- VUnit: unit testing framework for VHDL/SystemVerilog

- **SVUnit:** unit testing framework for Verilog/SystemVerilog

- Cocotb: Python based testbenches

But we will learn how to create a basic VHDL testbench from scratch.

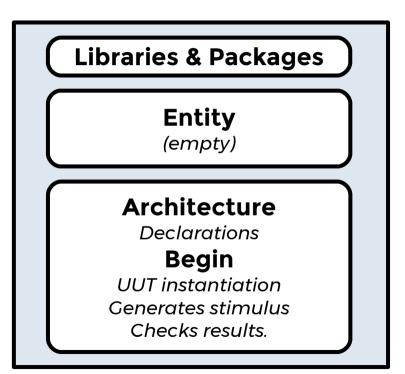

## **VHDL** for simulation

• The **Entity** is employed only to define the name of the testbench.

• Only one Architecture.

```

architecture Simul of counter tb is

constant PERIOD : time := 20 ns; -- 50 MHz

signal clk : std_logic:='1';

signal rst : std_logic;

. . .

signal stop : boolean := FALSE;

begin

do_clock: process

begin

while not stop loop

wait for PERIOD/2;

clk <= not clk;</pre>

end loop;

wait: -- Event Starvation

end process do_clock;

rst <= '1', '0' after 3*PERIOD:</pre>

```

time is a pre-defined physical type. It allows you to specify fs, ps, ns, us, ms, sec, min and hr.

You need to produce Event Starvation (no more events) to finish the simulation. It is achieved by a wait without options.

wait [on signals] [until condition] [for time];

```

-- wait on signals;

wait on s1, s2; -- wait for an event

-- wait until condition;

wait until clk_i = '1'; -- wait for an event

-- wait for time;

wait for 10 ns;

-- wait;

wait; -- wait forever (event starvation)

```

Is a sequential statement.

Used by processes

without a sensitivity list.

report <message\_string> [severity <severity\_level>];

assert <condition> [severity <severity\_level>];

assert <condition> report <message\_string> [severity <severity\_level>];

- Report is a sequential statement (only inside of a process).

- The <severity\_level> can be note (default for report), warning, error (default for assert) or failure.

- Assert can be either, a sequential or a concurrent statement.

- <condition> is a boolean value which must be TRUE to avoid the report.

- You can only report a string. The value of a **signal** or **variable** is not a string. You need to know the data **type** and use the image attribute:

report "unexpected value. i = " & integer'image(i);

```

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

entity counter is

port (

clk_i : in std_logic;

rst_i : in std_logic;

cnt_0 : out std_logic_vector(3 downto 0)

);

end entity counter;

```

```

architecture RTL of counter is

constant MODULE : positive := 12:

signal cnt

: unsigned(3 downto 0);

begin

do counter : process (clk i)

begin

if rising_edge(clk_i) then

if rst i = '1' then

cnt <= (others => '0'):

else

if cnt < MODULE-1 then

cnt <= cnt + 1:

else

cnt <= (others => '0');

end if:

end if;

end if:

end process do_counter;

cnt_o <= std_logic_vector(cnt);</pre>

end architecture RTL;

```

```

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

library std; -- Standard library of VHDL

use std.textio.all; -- we will write to STDOUT

library COUNTER_LIB; -- Our LIBRARY

use COUNTER_LIB.COUNTER_PKG.all; -- Our PACKAGE

```

```

entity counter_tb is

end entity counter_tb;

```

```

architecture Simul of counter_tb is

constant PERIOD : time := 20 ns; -- 50 MHz

signal clk : std_logic:='1';

signal rst : std_logic;

signal cnt : std_logic_vector(3 downto 0);

signal stop : boolean := FALSE;

begin

```

```

do clock: process

begin

while not stop loop

wait for PERIOD/2:

clk <= not clk:</pre>

end loop;

wait: -- Event Starvation

end process do clock;

rst <= '1', '0' after 3*PERIOD;</pre>

-- UUT instantiation

uut : counter

port map(

clk i => clk.

rst i => rst,

cnt o => cnt

);

```

```

testing: process

variable L : LINE; -- buffer

begin

-- Print to STDOUT

write(L,NOW); -- Current simulation time

write(L,STRING'(" --> Start of test"));

writeline(output,L); -- Write to STDOUT

-- Test of the initial value

wait until rising_edge(clk);

wait until rst='0':

assert unsigned(cnt)=0

report "Error! not 0"

severity failure;

-- Test of the intermediate values

for I in 0 to 11 loop

wait until rising_edge(clk);

assert unsigned(cnt)=I

report "Error! cnt = ("&integer'image(to_integer(unsigned(cnt)))&")"

severity failure;

end loop;

wait until rising edge(clk);

```

•

```

-- Test cicle restart

assert unsigned(cnt)=0

report "Error! Mod-12 ("&integer'image(to_integer(unsigned(cnt)))&")"

severity failure;

-- Print to STDOUT

write(L,NOW); -- Current simulation time

write(l,string'("-> End of test"));

writeline(output,L); -- Write to STDOUT

-- Clock stop

stop <= true;

wait;

end process testing;

end architecture Simul;</pre>

```

- Defines read and write procedures to work with FILES.

- The procedures supports the types bit, bit\_vector, boolean, character (ex: 'A'), string (ex: "ICTP", defined from 1 to 4), integer, real and time.

```

procedure READLINE(file F: TEXT; L: out LINE);

procedure READ(L:inout LINE; VALUE: out <type>);

procedure READ(L:inout LINE; VALUE: out <type>; GOOD : out BOOLEAN);

procedure WRITE(

L :inout LINE; VALUE : in <type>;

JUSTIFIED: in SIDE := right;

FIELD: in WIDTH := 0

);

procedure WRITELINE(file F : TEXT; L : inout LINE);

```

```

stimulus: process

file F : TEXT open READ_MODE is "input.dat";

variable L : LINE;

variable tag : string(1 to 3);

variable int : integer;

variable ok : boolean;

begin

while not endfile(F) loop

readline(F, L); -- F can be replaced by input (read from STDIN)

read(L, tag, ok);

assert ok report "Read ERROR!" severity failure;

-- Do something with tag (the read value)

read(L, int, ok);

assert ok report "Read ERROR!" severity failure;

-- Do something with int (the read value)

end loop;

wait; -- event starvation

end process stimulus;

```

•

```

checks: process

file F: TEXT open WRITE_MODE is "output.dat";

variable L: LINE;

begin

...

WRITE(L, NOW);

WRITE(L, STRING'("Your string")); -- This cast is needed for strings

WRITE(L, STRING'("Your string")); -- This cast is needed for strings

WRITE(L, STRING'("Your string")); -- This cast is needed for strings

WRITE(L, STRING'("Your string")); -- This cast is needed for strings

WRITE(L, STRING'("Your string")); -- This cast is needed for strings

WRITE(L, STRING'("Your string")); -- This cast is needed for strings

WRITE(L, STRING'("Your string")); -- This cast is needed for strings

WRITE(L, STRING'("Your string")); -- This cast is needed for strings

WRITE(L, STRING'("Your string")); -- This cast is needed for strings

WRITE(L, STRING'("Your string")); -- This cast is needed for strings

WRITE(L, STRING'("Your string")); -- This cast is needed for strings

WRITE(L, STRING'("Your string")); -- This cast is needed for strings

WRITE(L, STRING'("Your string")); -- This cast is needed for strings

WRITE(L, STRING'("Your string")); -- This cast is needed for strings

WRITE(L, STRING'("Your string")); -- This cast is needed for strings

WRITE(L, STRING'("Your string")); -- This cast is needed for strings

WRITE(L, STRING'("Your string")); -- This cast is needed for strings

WRITE(L, STRING'("Your string")); -- This cast is needed for strings

WRITE(L, STRING'("Your string")); -- This cast is needed for strings

WRITE(L, STRING'("Your string")); -- This cast is needed for strings

WRITE(L, STRING'("Your string")); -- This cast is needed for strings

WRITE(L, STRING'("Your string")); -- This cast is needed for strings

WRITE(L, STRING'("Your string")); -- This cast is needed for strings

WRITE(L, STRING'("Your string")); -- This cast is needed for strings

WRITE(L, STRING'("Your string")); -- This cast is needed for strings

WRITE(L, STRING'("Your string")); -- This cast is needed for strings

WRITE(L, STRING'("Your string")); -- This cast is needed for strings

WRITE(L,

```

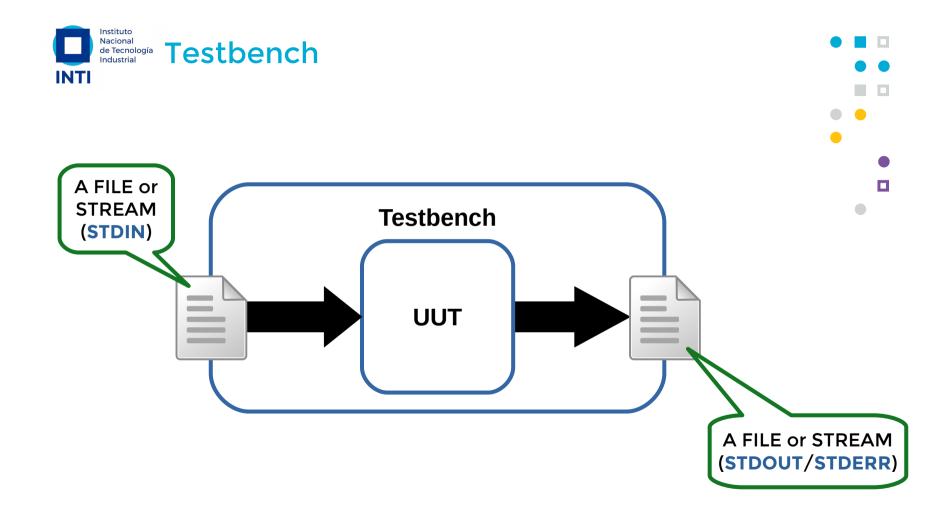

You can read from STDIN with a file called input and to write to STDOUT with a file called output (these files are automatically opened when you include textio).

### Simulators

```

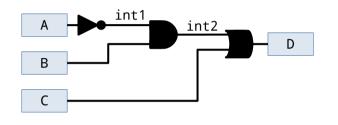

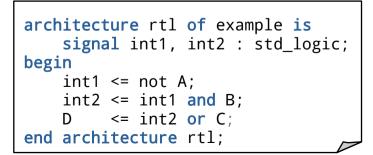

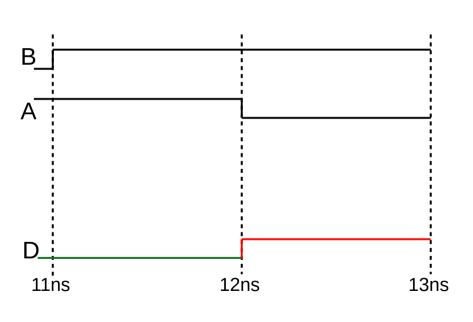

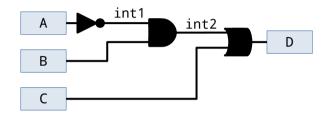

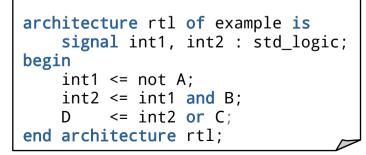

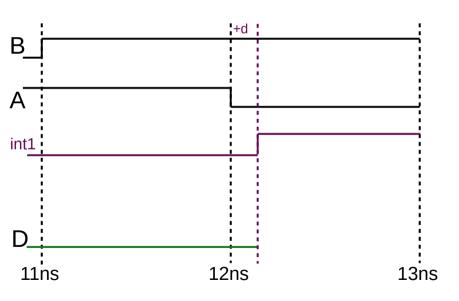

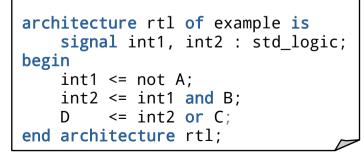

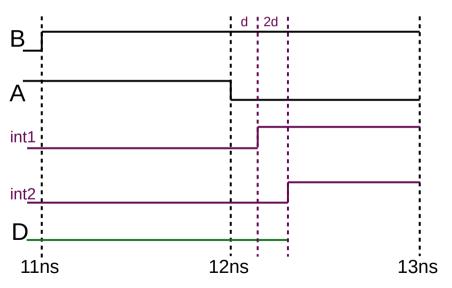

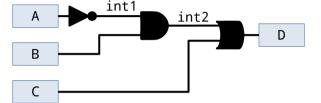

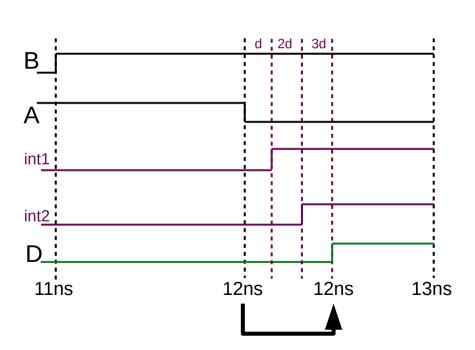

architecture rtl of example is

signal int1, int2 : std_logic;

begin

int1 <= not A;

int2 <= int1 and B;

D <= int2 or C;

end architecture rtl;</pre>

```

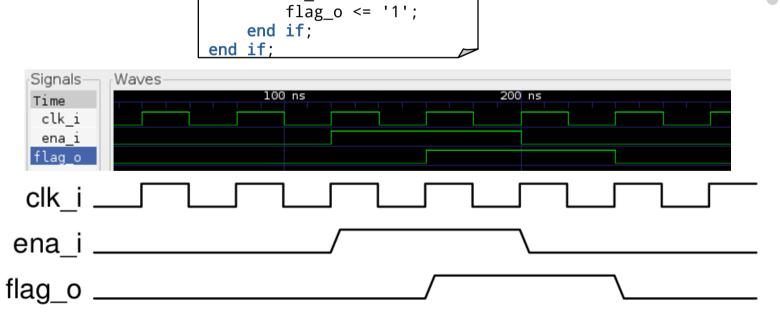

if rising\_edge(clk\_i) then

flag\_o <= '0';

if ena\_i = '1' then</pre>

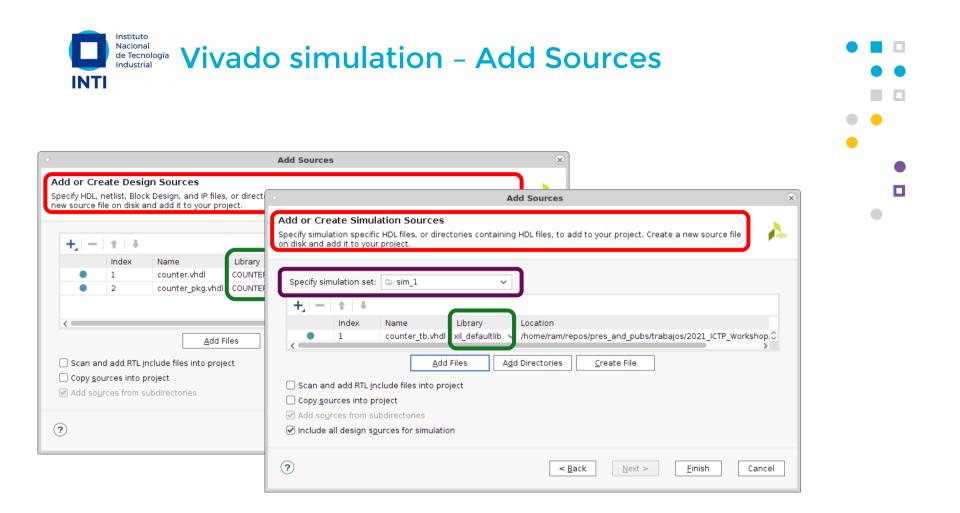

- counter.vhdl: entity/component

- counter\_pkg.vhdl: package which contains the component

- The package name is COUNTER\_PKG (name defined into the VHDL file)

- counter\_tb.vhdl: testbench of the component

- The library name is COUNTER\_LIB (name defined by the tool)

| \$<br>mkdir | ~ - r | o build       |                                                |

|-------------|-------|---------------|------------------------------------------------|

| \$<br>ghdl  | -a    | workdir=build | work=COUNTER_LIB counter.vhdl counter_pkg.vhdl |

| \$<br>ghdl  | -a    | workdir=build | -Pbuild counter_tb.vhdl                        |

| \$<br>ghdl  | -e    | workdir=build | -Pbuild counter_tb                             |

| \$<br>ghdl  | -r    | workdir=build | -Pbuild counter_tbvcd=build/counter.vcd        |

- GHDL analyze (-a), elaborate (-e) and run (-r) our simulation.

- Use --workdir to specify where to put generated files (build directory).

- Use --work to specify the LIBRARY NAME (COUNTER\_LIB).

- Use -P to specify where to find libraries (no space between P and the directory).

• Use --vcd or --wave (.ghw), which are runtime options, to specify where to dump waveforms.

#### \$ gtkwave build/counter.vcd

| •                          |             | GTKWave - build/counter.vcd 📀 📀 🛞                     |

|----------------------------|-------------|-------------------------------------------------------|

| File Edit Search Time Mark | ers View He | lp                                                    |

| 🔏 🗄 📋 🖾 🖨 😑 🚝              | )  & 2)   < | 🔆 🕎 From: 🛛 sec To: 310 ns 🕞 Marker:   Cursor: 600 ps |

| ▼ SST                      | Signals     | Waves                                                 |

| 🖻 📩 counter_tb             | Time        | 0 100 ns 200 ns 300 ns                                |

| L 🚠 uut                    | clk<br>rst  |                                                       |

|                            | cnt[3:0]    | u (0 )1 )2 )3 )4 )5 )6 )7 )8 )9 )A )B )0 )1           |

| Type Signals               | stop        |                                                       |

| reg clk                    |             |                                                       |

| reg cnt[3:0]               |             |                                                       |

| reg rst                    |             |                                                       |

| reg stop                   |             |                                                       |

| Filter:                    |             |                                                       |

| Append Insert Replace      | < >>>       |                                                       |

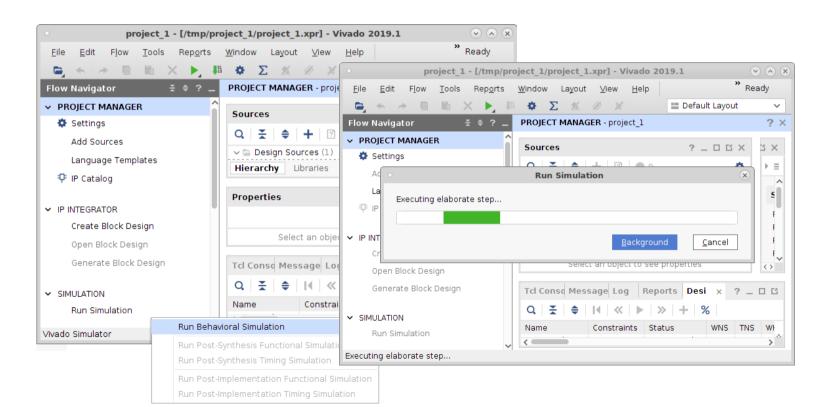

#### Instituto Nacional de Tecnologia Industrial Vivado simulation – Launch simulation

|                                                                                                                                                                                                                                                                                     | project_1 - [/tmp/project_1/project_1.xpr] - Vivado 2019.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | $\odot$ $\otimes$ $\otimes$ |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|

| <u>File Edit Flow T</u> ools Rep <u>o</u> rts                                                                                                                                                                                                                                       | s <u>W</u> indow La <u>v</u> out <u>V</u> iew <u>R</u> un <u>H</u> elp Q- Quick Access                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Ready                       |

|                                                                                                                                                                                                                                                                                     | 👭 🕸 Σ 🖄 🖉 🤘 🖌 🕨 🐜 10 us 🗸 🗄    C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | efault Layout 🛛 🗸 🗸         |

| Flow Navigator 😤 🗘 ?                                                                                                                                                                                                                                                                | SIMULATION - Behavioral Simulation - Functional - sim_1 - counter_tb                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | ? ×                         |

| <ul> <li>PROJECT MANAGER</li> <li>Settings         <ul> <li>Add Sources</li> <li>Language Templates</li> <li>IP IP Catalog</li> </ul> </li> <li>IP INTEGRATOR         <ul> <li>Create Block Design</li> <li>Open Block Design</li> <li>Generate Block Design</li> </ul> </li> </ul> | Sco × Sour       Image: Sc | ? □ Ľ ×<br>*                |

| SIMULATION                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                             |

| Run Simulation                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                             |

| <ul> <li>RTL ANALYSIS</li> </ul>                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | >                           |

| > Open Elaborated Design                                                                                                                                                                                                                                                            | Tcl Console x Messages Log                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ? _ 🗆 🖒                     |

| <ul> <li>SYNTHESIS</li> <li>Run Synthesis</li> </ul>                                                                                                                                                                                                                                | Q     X     ↓     ↓     ↓     ↓       300 ns-> End of test     ↓     ↓     ↓     ↓       INF0:     [USF-XSim-96]     XSim completed.     Design snapshot 'counter_tb_behav' loaded.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | ^                           |

| > Open Synthesized Design                                                                                                                                                                                                                                                           | INF0: [USF-XSim=97] XSim simulation ran for 1000ns<br>launch_simulation: Time (s): cpu = 00:00:06 ; elapsed = 00:00:08 . Memory (MB): peak = 6749.535 ; gain = 0.000 ; free physical                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | = 175 ; free virtu          |

| Open Synthesized Design     IMPLEMENTATION                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | = 175 ; free virtu          |

•

### Conclusions

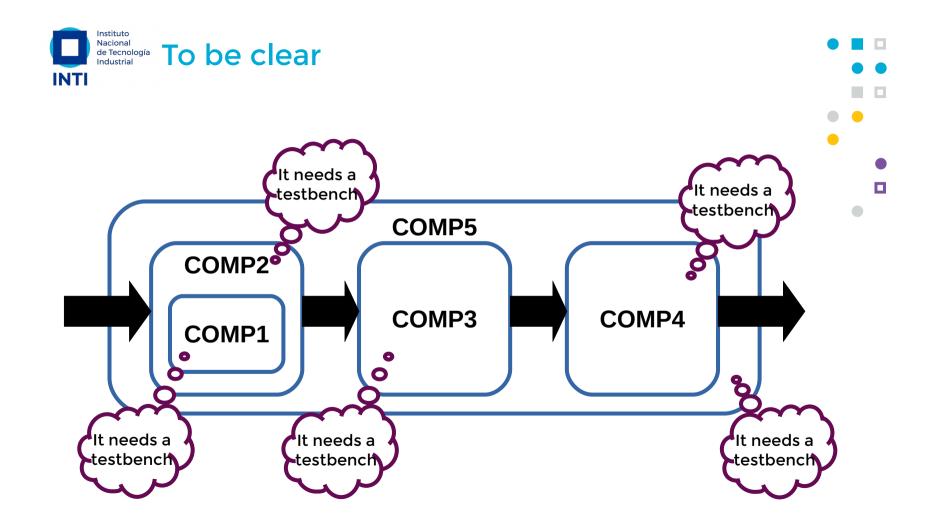

Do not perform a testbench can be only allowed for a very basic (a counter, a ROM) descriptions included in another simulated description. Professional advice.

- What we saw today is enough to develop a small testbench with stimulus and assertions.

- Also, you should be capable of read/write files.

🖾 rmelo@inti.gob.ar

rodrigoalejandromelo

@rodrigomelo9ok

rodrigomelo9

rodrigomelo9

# • H • Thank you

This work is licensed under CC BY 4.0 ⓒ 👔

If you want to know more about INTI, we wait for you at

f INTIArg

@INTIargentina

in INTI

@ @intiargentina

canalinti

www.inti.gob.ar consulta@inti.gob.ar 0800 444 4004

Instituto Nacional de Tecnología Industrial

INT

Joint ICTP-IAEA School on FPGA-based SoC and its Applications for Nuclear and Related Instrumentation | (smr 3562)

Ministerio de Desarrollo Productivo **Argentina**