# JOINT ICTP-IAEA SCHOOL ON FPGA-BASED SOC

------

......

LUCIO J. MARTÍNEZ GARBINO

COMISIÓN NACIONAL DE ENERGÍA ATÓMICA ARGENTINA

• The School Scope

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

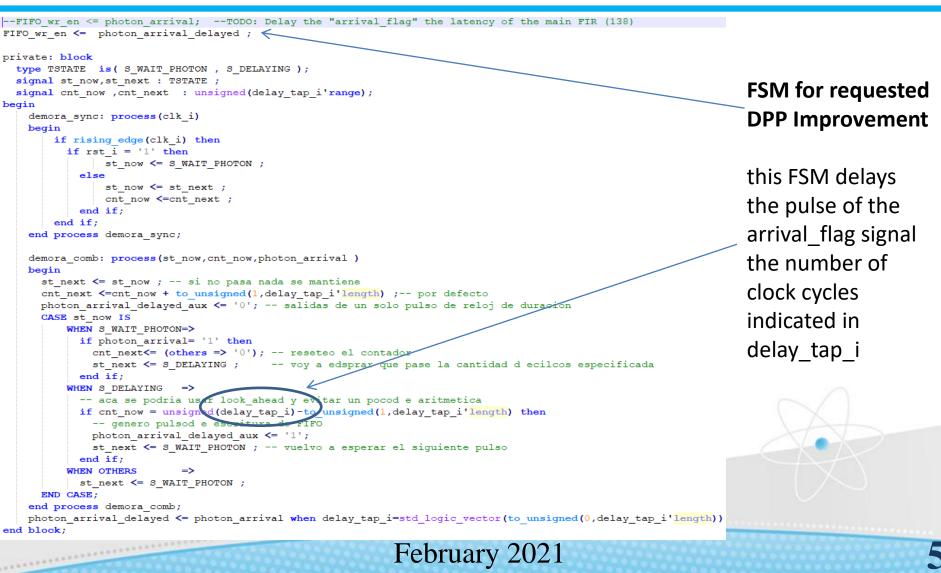

- Final Project

- New Topics

- Useful IP-COREs

......

February 2021

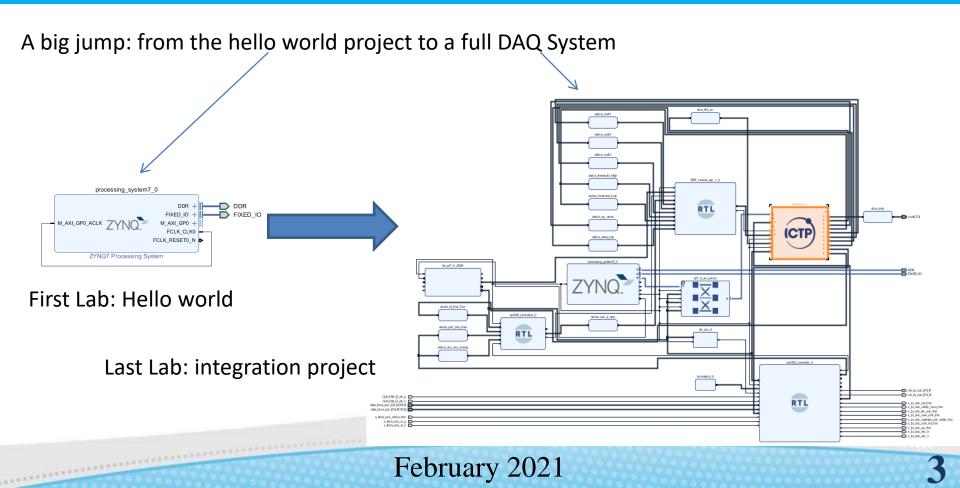

### THE SCHOOL SCOPE

### FINAL PROJECT (MY SOLUTION)

#### **PL-SIDE**

1- started from adc 500 project

\*\*\*\*\*\*

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

- 2- modify the comblock adding 7 registers for the DPP configuration and disable the output FIFO

- 3- add the DPP source files (modified) and put it in the BlockDesign as a component

- 4- finally modify the data stream connections: ADC-> DECIMATOR-> DPP-> FIFO\_in

#### **PS-SIDE**

SDK: I used the same project that I used in the UDMA lab

#### PC-SIDE

I wrote a little UDMA script to automate DPP configuration and data acquisition

February 2021

#### A basic UDMA script to automate DPP configuration and data acquisition

February 2021

A small index to know the mapping of registers to component parameters or function

\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*\*

|   | Register   | function           | bits | Periphera | 1        |

|---|------------|--------------------|------|-----------|----------|

|   | 0          | Leds               | 7:0  |           |          |

|   | 1          | Clear FIFO         | 0    | ComBlock  |          |

| # | 2          | op_mode            | 1:0  | DPP       | [REF 1   |

| # | 3          | threshold[H,L]     | 31:0 | DPP       |          |

|   | 4          | coef_1             | 4:0  | DPP       |          |

|   | 5          | coef_2             | 4:0  | DPP       |          |

|   | 6          | coef_3             | 4:0  | DPP       |          |

|   | 7          | delay_tap          | 15:0 | DPP       |          |

| # | 8          | control_reg        | 31:0 | adc500_co | ntroller |

| # | 9          | N dec_factor       | 22:0 | adc500_de | cimator  |

|   |            |                    |      |           |          |

|   | [REF       | -                  |      |           |          |

| # | 0: Amplitu | ide measurement    |      |           |          |

| # | 1: ADC dek | ougging            |      |           |          |

| # | 2: FIR dek | ougging            |      |           |          |

| # | 3: derivat | tive FIR output    |      |           |          |

|   |            |                    |      |           |          |

|   |            |                    |      |           |          |

|   |            | lab21/.local/bin/  |      |           |          |

|   | ./udma     |                    |      |           |          |

| # | run_script | : ~/script_udma.tx | t    |           |          |

|   |            |                    |      |           |          |

|   |            |                    |      |           |          |

| 28 | #                                   |

|----|-------------------------------------|

| 29 | # conection                         |

| 30 | #                                   |

| 31 | connect -s 192.168.0.5:5900         |

| 32 |                                     |

| 33 | #                                   |

| 34 | # All leds On                       |

| 35 | x_write_reg 0 255                   |

| 36 |                                     |

| 37 | #                                   |

| 38 | # Fifo clean                        |

| 39 | x_write_reg 1 1                     |

| 40 | x_write_reg 1 0                     |

| 41 |                                     |

| 42 | #                                   |

| 43 | <pre># DPP Operation mode</pre>     |

| 44 | x_write_reg 2 0                     |

| 45 |                                     |

| 46 | #                                   |

| 47 | # DPP threshold                     |

| 48 | x_write_reg 3 1023                  |

| 49 |                                     |

| 50 | #                                   |

| 51 | # DPP Coefs                         |

| 52 | x_write_reg 4 1                     |

| 53 | x_write_reg 5 3                     |

| 54 | x_write_reg 6 5                     |

| 55 |                                     |

| 56 | <b>#</b>                            |

| 57 | # DPP Tap Delay (time to peak)      |

| 58 | x_write_reg 7 128                   |

| 59 |                                     |

| 60 | #                                   |

| 61 | # Decimator Factor                  |

| 62 | x_write_reg 9 10                    |

| 63 | ±                                   |

|    | -                                   |

|    | # Read FIFO                         |

| 66 | x_read_fifo -r d -f salida.txt 4096 |

6

......

**NEW TOPICS**

## **GIT** + **TCL** + **VIVADO** A useful things that I learned in this school is the use of tools like GIT and TCL and their interaction with VIVADO

### **Future Work** Free Open Source Software for FPGA design

February 2021

**USEFUL IP-CORES**

Comblock -systems configuration -interface or abstraction layer -perform rapid tests

......

# **Thanks for your attention!**

February 2021

\*\*\*\*\*\*