# VHDL for FPGA Simulation

Rodrigo A. Melo

Oct | 2021

Joint ICTP, SAIFR and UNESP School on Systems-on-Chip, Embedded Microcontrollers and their Applications in Research and Industry | (smr 3557)

# Introduction

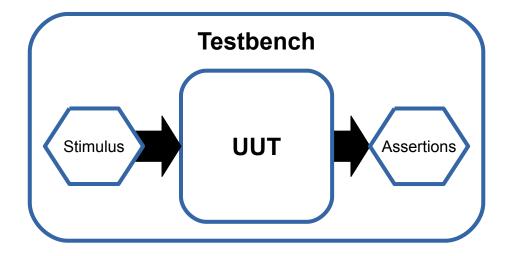

### Verification

- Verification: to check if a design works as expected.

- In-Circuit Debug:

•

Performed in a test bench, with a Scope (simple design with a few signals), Logic

Analyzer (\$\$\$) or Embedded Logic Analyzer (modify your design).

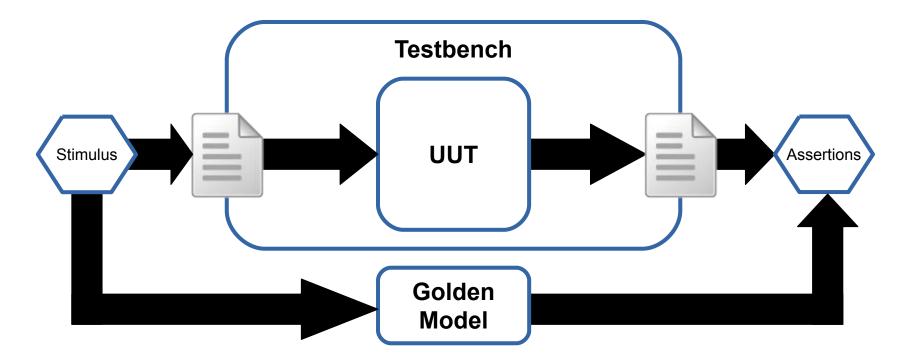

#### Functional verification:

- Stimulus are provided and the output compared with expected values, according to a specification.

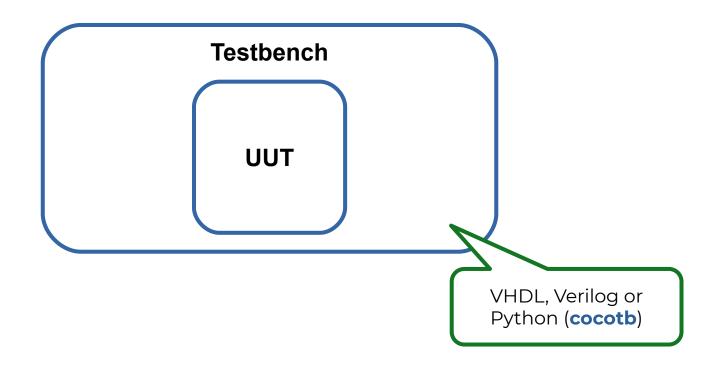

- It implies a testbench (generally an HDL) and a simulator

#### Formal verification:

- Generally speaking, you need to specify formal properties and a tool checks your design against formal methods (mathematical proof). Ex: **SymbiYosys** (FOSS).

#### To be clear

## Frameworks and methodologies

UVM: Universal Verification Methodology

- Open Verification Methodology

- Functional verification using SystemVerilog

- Supported by a few very expensive simulators (and Vivado?)

#### FOSS:

- **OSVVM:** Open Source VHDL Verification Methodology

- **UVVM:** Universal VHDL Verification Methodology

- **VUnit:** unit testing framework for VHDL/SystemVerilog

- **SVUnit:** unit testing framework for Verilog/SystemVerilog

- **Cocotb:** Python based testbenches

But we will learn how to create a basic VHDL testbench from scratch.

# VHDL for simulation

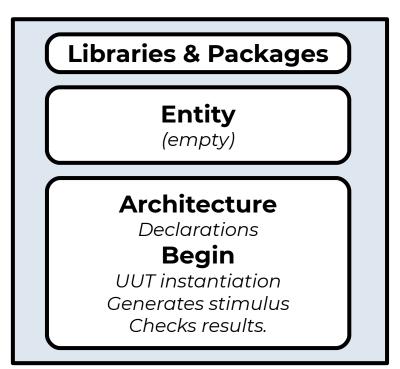

#### Structure of a VHDL testbench

- The **Entity** is employed only to define the name of the testbench.

- Only one **Architecture**.

•

# Clock and reset generation

```

architecture Simul of counter the is

constant PERIOD : time := 20 ns; -- 50 MHz

signal clk : std logic:='1';

: std logic;

signal rst

signal stop : boolean := FALSE;

begin

do clock: process

begin

while not stop loop

wait for PERIOD/2:

clk <= not clk:

end loop:

wait; -- Event Starvation

end process do clock;

```

rst <= '1', '0' **after** 3\*PERIOD;

- time is a pre-defined physical type. It allows you to specify fs, ps, ns, us, ms, sec, min and hr.

- You need to produce **Event Starvation** (no more events) to finish the simulation. It is achieved by a **wait** without options.

#### wait [on signals] [until condition] [for time];

-- wait on signals;

wait on s1, s2; -- wait for an event

-- wait until condition;

wait until clk\_i = '1'; -- wait for an event

-- wait for time;

wait for 10 ns;

-- wait;

wait; -- wait forever (event starvation)

- Is a sequential statement.

- Used by processes without a sensitivity list.

### Assert and report

report <message\_string> [severity <severity\_level>];

assert <condition> [severity <severity\_level>];

assert <condition> report <message\_string> [severity <severity\_level>];

- Report is a sequential statement (only inside of a process).

- The <severity\_level> can be note (default for report), warning, error (default for assert) or failure.

- Assert can be either, a sequential or a concurrent statement.

- **condition>** is a boolean value which must be TRUE to avoid the report.

- You can only report a string. The value of a **signal** or **variable** is not a string. You need to know the data **type** and use the image attribute:

**report** "unexpected value. i = " & integer'image(i);

### Example – Component

```

library IEEE;

use IEEE.std_logic_1164.all;

use IEEE.numeric_std.all;

```

```

entity counter is

port (

clk_i: in std_logic;

rst_i: in std_logic;

cnt_o: out std_logic_vector(3 downto 0)

);

end entity counter;

```

```

architecture RTL of counter is

constant MODULE : positive := 12;

signal cnt : unsigned(3 downto 0);

begin

do counter : process (clk i)

begin

if rising edge(clk i) then

if rst i = '1' then

cnt \leq (others => '0');

else

if cnt < MODULE-1 then

cnt \leq cnt + 1:

else

cnt <= (others => '0'):

end if:

end if:

end if:

end process do counter;

cnt o <= std logic vector(cnt);

end architecture RTL:

```

# Example – Testbench (part 1)

library IEEE; use IEEE.std\_logic\_1164.all; use IEEE.numeric\_std.all; library std; -- Standard library of VHDL use std.textio.all; -- we will write to STDOUT library COUNTER\_LIB; -- Our LIBRARY use COUNTER\_LIB.COUNTER PKG.all; -- Our PACKAGE

entity counter\_tb is

end entity counter\_tb;

architecture Simul of counter\_tb is constant PERIOD : time := 20 ns; -- 50 MHz signal clk : std\_logic:='1'; signal rst : std\_logic; signal cnt : std\_logic\_vector(3 downto 0); signal stop : boolean := FALSE; begin do clock: process begin while not stop loop wait for PERIOD/2:  $clk \leq not clk$ : end loop; wait: -- Event Starvation end process do clock; rst <= '1'. '0' after 3\*PERIOD: -- UUT instantiation uut : counter port map( clk i => clk, rst i => rst. cnt o => cnt

## Example – Testbench (part 2)

testing: process variable L : LINE; -- buffer begin -- Print to STDOUT write(L,NOW); -- Current simulation time write(L,STRING'(" --> Start of test")); writeline(output,L); -- Write to STDOUT -- Test of the initial value wait until rising edge(clk); wait until rst='0': assert unsigned(cnt)=0 report "Error! not 0" severity failure; -- Test of the intermediate values for I in 0 to 11 loop wait until rising edge(clk); assert unsigned(cnt)=I **report** "Error! cnt = ("&integer'image(to integer(unsigned(cnt)))&")" severity failure; end loop; wait until rising\_edge(clk);

# Example – Testbench (part 3)

-- Test cicle restart

assert unsigned(cnt)=0

report "Error! Mod-12 ("&integer'image(to\_integer(unsigned(cnt)))&")"

severity failure;

-- Print to STDOUT

write(L,NOW); -- Current simulation time

write(I,string'("-> End of test"));

writeline(output,L); -- Write to STDOUT

-- Clock stop

stop <= true;

wait;

end process testing;</pre>

end architecture Simul;

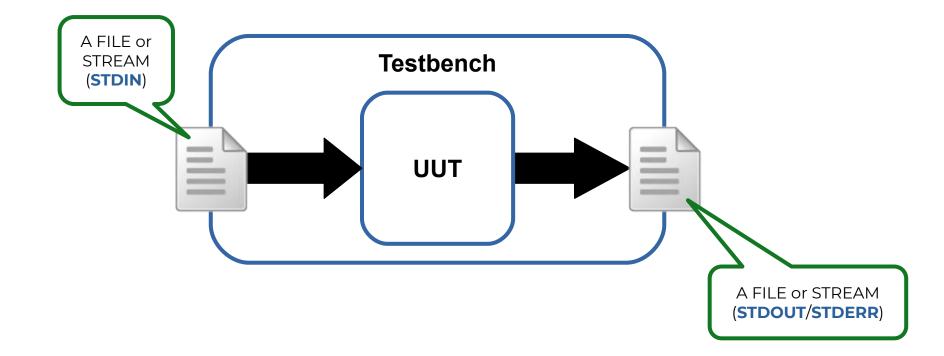

### Files – std.textio

- Defines read and write procedures to work with FILES.

- The procedures supports the types bit, bit\_vector, boolean, character (ex: 'A'), string (ex: "ICTP", defined from 1 to 4), integer, real and time.

```

procedure READLINE(file F: TEXT; L: out LINE);

procedure READ(L:inout LINE; VALUE: out <type>);

procedure READ(L:inout LINE; VALUE: out <type>; GOOD : out BOOLEAN);

procedure WRITE(

L :inout LINE; VALUE : in <type>;

JUSTIFIED: in SIDE := right;

FIELD: in WIDTH := 0

);

procedure WRITELINE(file F : TEXT; L : inout LINE);

```

#### Files – read

stimulus: process file F : TEXT open READ MODE is "input.dat"; variable L : LINE; **variable** tag : string(1 to 3); **variable** int : integer; **variable** ok : boolean; begin while not endfile(F) loop readline(F, L); -- F can be replaced by input (read from STDIN) read(L, tag, ok); assert ok report "Read ERROR!" severity failure; -- Do something with tag (the read value) read(L, int, ok); assert ok report "Read ERROR!" severity failure; -- Do something with int (the read value) end loop; wait; -- event starvation end process stimulus;

#### Files – write

```

checks: process

file F: TEXT open WRITE_MODE is "output.dat";

variable L: LINE;

begin

...

WRITE(L, NOW);

WRITE(L, STRING'("Your string")); -- This cast is needed for strings

WRITELINE(F,L); -- F can be replaced by output (print to STDOUT)

...

wait; -- event starvation

end process checks;

```

You can read from **STDIN** with a file called **input** and to write to **STDOUT** with a file called **output** (these files are automatically opened when you include **textio**).

# Simulators

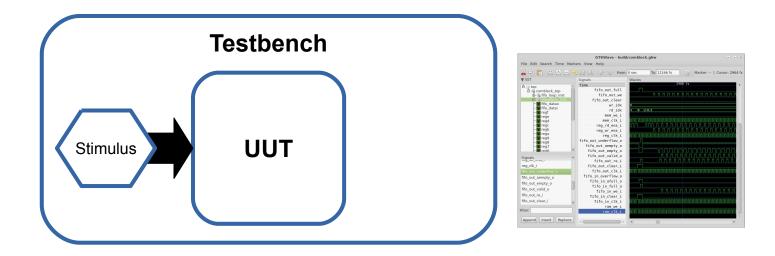

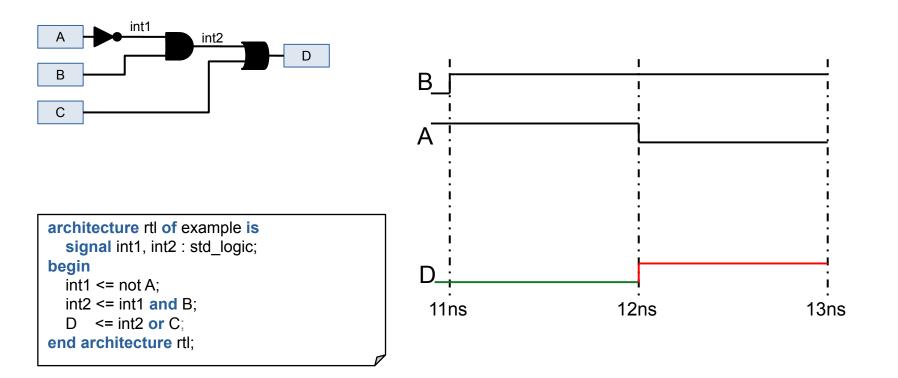

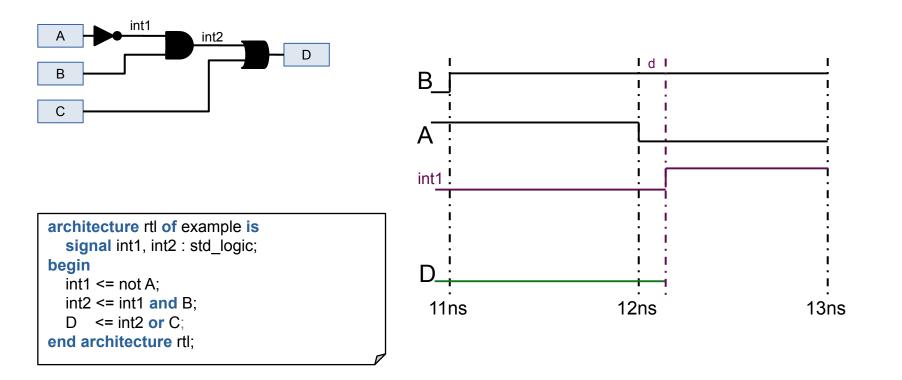

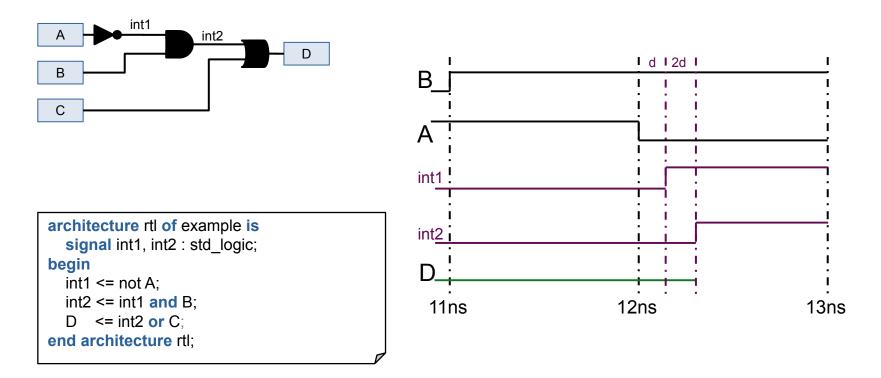

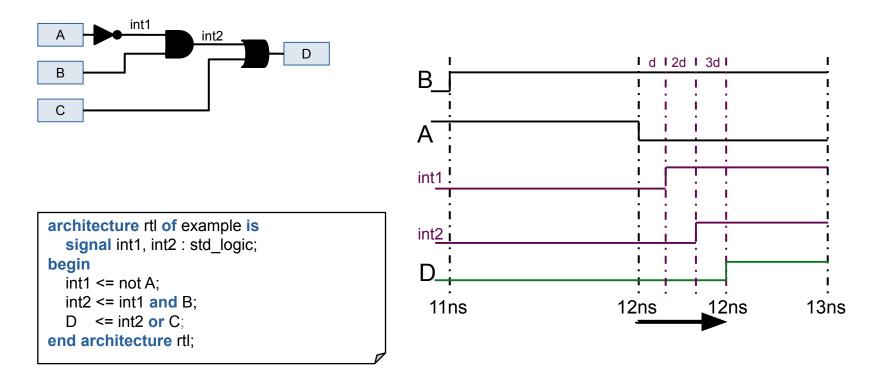

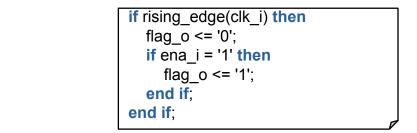

#### Waveforms interpretation

## Example

- counter.vhdl: entity/component

- **counter\_pkg.vhdl**: package which contains the component

- The package name is **COUNTER\_PKG** (name defined into the VHDL file)

- **counter\_tb.vhdl**: testbench of the component

- The library name is COUNTER\_LIB (name defined by the tool)

### **GHDL** simulation

\$ mkdir -p build \$ ghdl -a --workdir=build --work=COUNTER\_LIB counter.vhdl counter\_pkg.vhdl \$ ghdl -a --workdir=build -Pbuild counter\_tb.vhdl \$ ghdl -e --workdir=build -Pbuild counter\_tb \$ ghdl -r --workdir=build -Pbuild counter\_tb --vcd=build/counter.vcd

- GHDL analyze (-a), elaborate (-e) and run (-r) our simulation.

- Use --workdir to specify where to put generated files (build directory).

- Use --work to specify the LIBRARY NAME (COUNTER\_LIB).

- Use -P to specify where to find libraries (no space between P and the directory).

- Use --vcd or --wave (.ghw), which are runtime options, to specify where to dump waveforms.

#### GTKwave waveform viewer

#### \$ gtkwave build/counter.vcd

| •                                                                             | C          | GTKWave - build/counter.vcd 📀 🔿 🛞           |  |

|-------------------------------------------------------------------------------|------------|---------------------------------------------|--|

| File Edit Search Time Markers View Help                                       |            |                                             |  |

| 💑 📮 🚰 🖏 🖶 😑 🥱 🔗 🏈 📎 🤄 🖓 From: 0 sec 🛛 To: 310 ns 🛛 🕑 Marker:   Cursor: 600 ps |            |                                             |  |

| ▼ SST                                                                         | Signals    | Waves                                       |  |

| 🖻 – counter_tb                                                                | Time       | 0 100 ns 200 ns 300 ns                      |  |

| L <sub>and</sub> uut                                                          | clk<br>rst |                                             |  |

|                                                                               | cnt[3:0]   | u 10 )1 )2 )3 )4 )5 )6 )7 )8 )9 )A )B )0 )1 |  |

| Type Signals                                                                  | stop       |                                             |  |

| reg clk                                                                       |            |                                             |  |

| reg cnt[3:0]                                                                  |            |                                             |  |

| reg rst                                                                       |            |                                             |  |

| reg stop                                                                      |            |                                             |  |

| Filter:                                                                       |            |                                             |  |

| Append Insert Replace                                                         | < >>       |                                             |  |

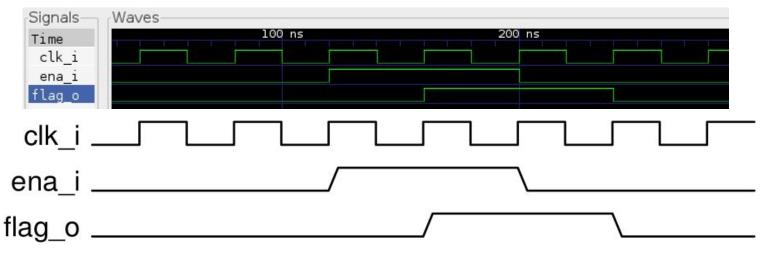

#### Vivado simulation – create project

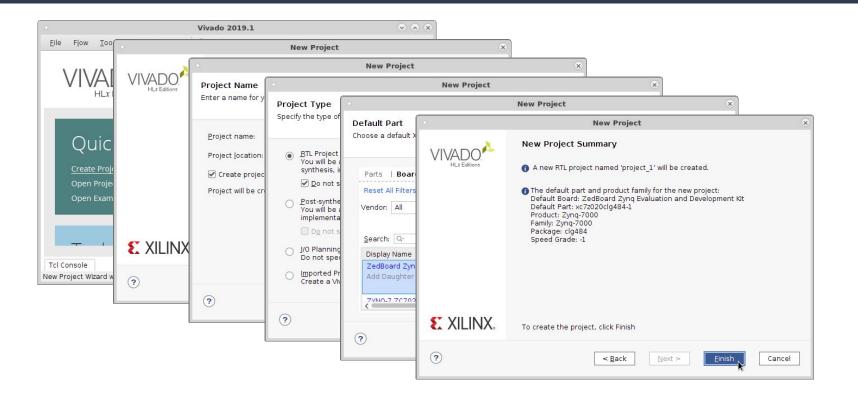

### Vivado simulation – add sources

| -                                                                                                                                             | Add Sources                                                                                                                                                                                                                                                                                                                                                                                                         |

|-----------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Add or Create Design Sources                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Specify HDL, netlist, Block Design, and IP files, or direct<br>new source file on disk and add it to your project.                            | Add Sources                                                                                                                                                                                                                                                                                                                                                                                                         |

| +_  =   +   +                                                                                                                                 | Add or Create Simulation Sources<br>Specify simulation specific HDL files, or directories containing HDL files, to add to your project. Create a new source file<br>on disk and add it to your project.                                                                                                                                                                                                             |

| Index Name Library                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1 counter.vhdl COUNTER                                                                                                                        | Specify simulation set: 🕞 sim 1                                                                                                                                                                                                                                                                                                                                                                                     |

| 2 counter_pkg.vhdl_COUNTER                                                                                                                    | specity simulation set.                                                                                                                                                                                                                                                                                                                                                                                             |

| <u>A</u> dd Files<br>Scan and add RTL include files into project<br>Copy <u>s</u> ources into project<br>Add sources from subdirectories<br>? | <ul> <li>Index Name<br/>Index Name<br/>Counter_tb.vhdl</li> <li>Library<br/>Location<br/>/home/ram/repos/pres_and_pubs/trabajos/2021_ICTP_Workshop.</li> <li>Add Files</li> <li>Add Directories</li> <li>Create File</li> <li>Scan and add RTL include files into project</li> <li>Copy gources into project</li> <li>Add sources from subdirectories</li> <li>Include all design sources for simulation</li> </ul> |

| Г <u> </u>                                                                                                                                    | < Back                                                                                                                                                                                                                                                                                                                                                                                                              |

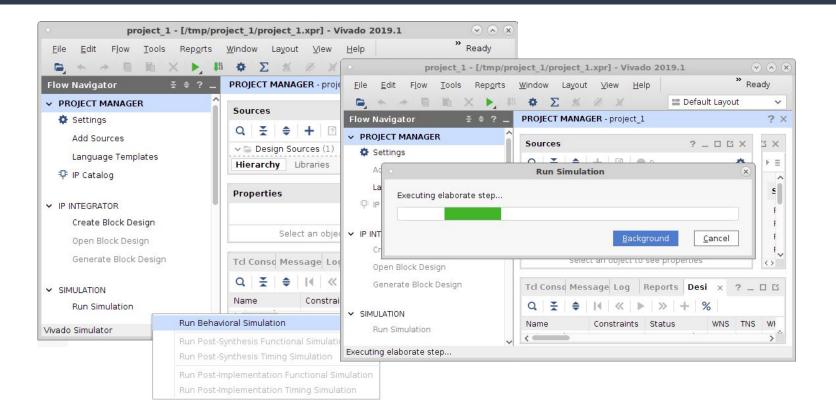

### Vivado simulation – launch simulation

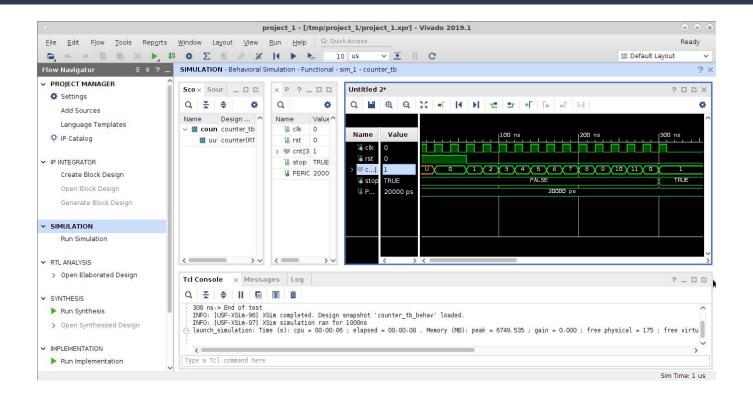

#### Vivado simulation – see waveforms

# Conclusion

## Final remarks

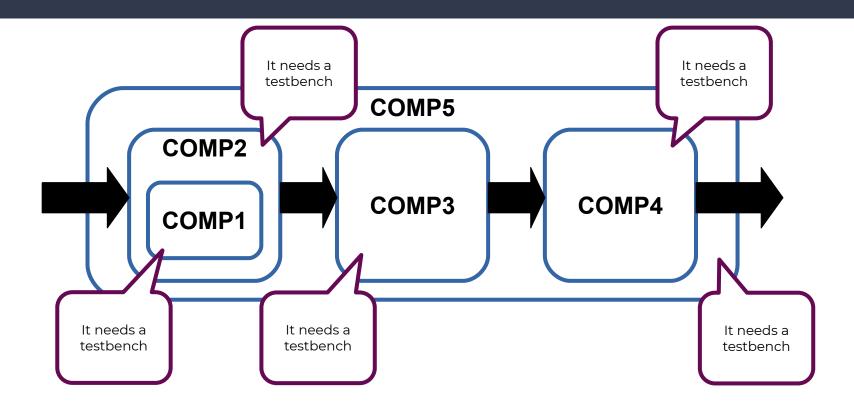

- Do not perform a testbench can be only allowed for very basic descriptions (a counter, a ROM) included in another simulated description. Professional advice.

- What we saw today is enough to develop a small testbench with stimulus and assertions.

- Also, you should be capable of read/write files.

- <u>@rodrigomelo9ok</u>

- g <u>rodrigomelo9</u>

This work is licensed under <u>CC BY 4.0</u>