14 November - 2 December 2022 An ICTP - IAEA Hybrid Meeting Trieste, Italy

Further information: http://indico.ictp.it/event/9933/ smr3765@ictp.it

# Programmable hardware acceleration in Communication Networks

L. Valcarenghi Scuola Superiore Sant'Anna, Pisa, Italy

Joint ICTP-IAEA School on FPGA-based SoC and its Applications to Nuclear and Scientific Instrumentation Nov. 17, 2022, Trieste, Italy

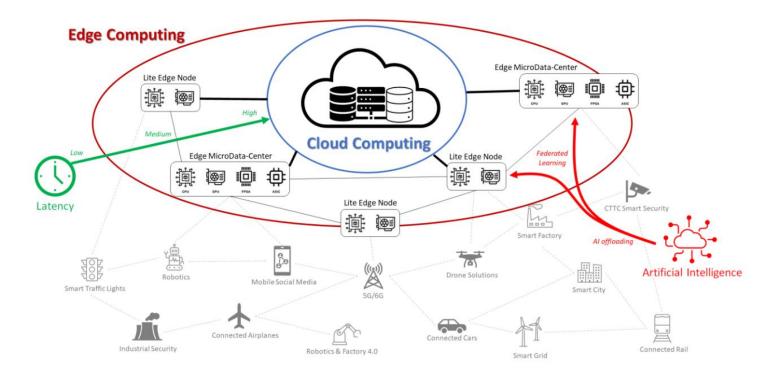

- Edge cloud continuum

- SDN

- NFV

- Chances for in network elaboration

- Network programmability

### Edge Cloud Continuum and In-network computing

- Traditionally, little integration of computing tasks into networks:

- The intelligence remains in end nodes

- Network fabric is optimized for speed and security

- Hardware has evolved

- virtualisation and data processing

- new ways to design in-network services based on local processing of the data

- With the emergence of white boxes and smart Network Interface Cards (smart NICs), network nodes have increased their computation capabilities including also hardware acceleration.

- The availability of new hardware architectures (e.g. Tofino) and programming frameworks (e.g. P4) makes it possible to perform some innetwork computing at line speed

Source: Marie-José Montpetit, Noel Crespi, "The Core-Edge Continuum in 6G Network" Chapter 10 in "Computing in the Network" Book Editor(s):Emmanuel Bertin, Noel Crespi, Thomas Magedanz First published: 05 November 2021 https://doi.org/10.1002/9781119765554.ch10

### Computing Continuum, Digital Continuum, Transcontinuum

- It seamlessly combines resources and services at the center of the network (*e.g.*, in Cloud datacenters), at its Edge, and *in-transit*, along the data path.

- Typically, data is first generated and pre-processed (*e.g.*, filtering, basic inference) on Edge devices, while Fog nodes further process partially aggregated data.

Source: Daniel Rosendo, Alexandru Costan, Patrick Valduriez, Gabriel Antoniu, Distributed intelligence on the Edge-to-Cloud Continuum: A systematic literature review, Journal of Parallel and Distributed Computing, Volume 166, 2022, Pages 71, 04, ISSN 0743, 7315, https://doi.org/10.1016/j.jmdo.2022.04.004

Volume 166, 2022, Pages 71-94, ISSN 0743-7315, https://doi.org/10.1016/j.jpdc.2022.04.004.

AND PHOTOM

Sant'Anna

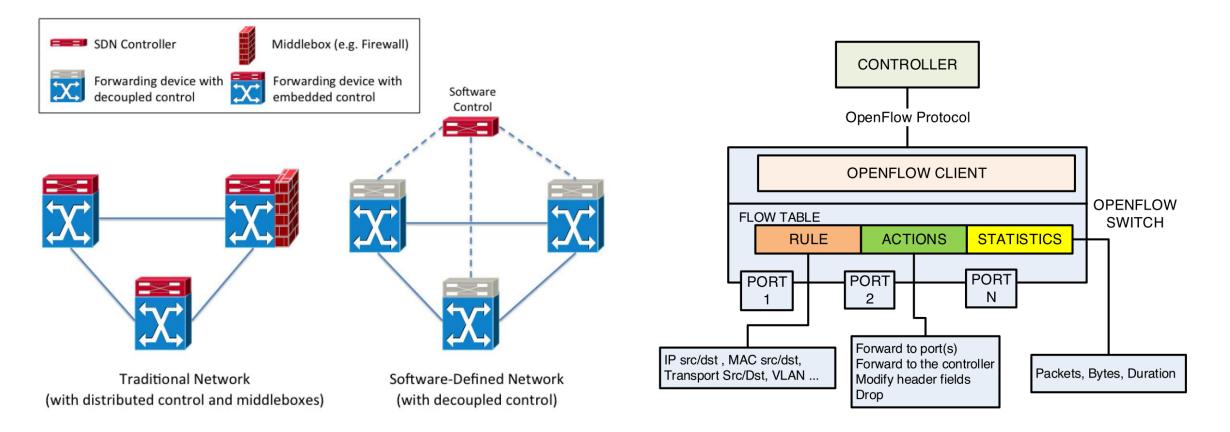

#### Software Defined Networks

Source: B. A. A. Nunes, M. Mendonca, X. -N. Nguyen, K. Obraczka and T. Turletti, "A Survey of Software-Defined Networking: Past, Present, and Future of Programmable Networks," in IEEE Communications Surveys & Tutorials, vol. 16, no. 3, pp. 1617-1634, Third Quarter 2014, doi: 10.1109/SURV.2014.012214.00180.

TELECOMMUNICATIONS, COMPUTER ENGINEERING, AND PHOTONICS INSTITUTE

Sant'Anna

chool of Advanced Studies - Pis

Source: D. Kreutz, F. M. V. Ramos, P. E. Veríssimo, C. E. Rothenberg, S. Azodolmolky and S. Uhlig, "Software-Defined Networking: A Comprehensive Survey," in Proceedings of the IEEE, vol. 103, no. 1, pp. 14-76, Jan. 2015, doi: 10.1109/JPROC.2014.2371999.

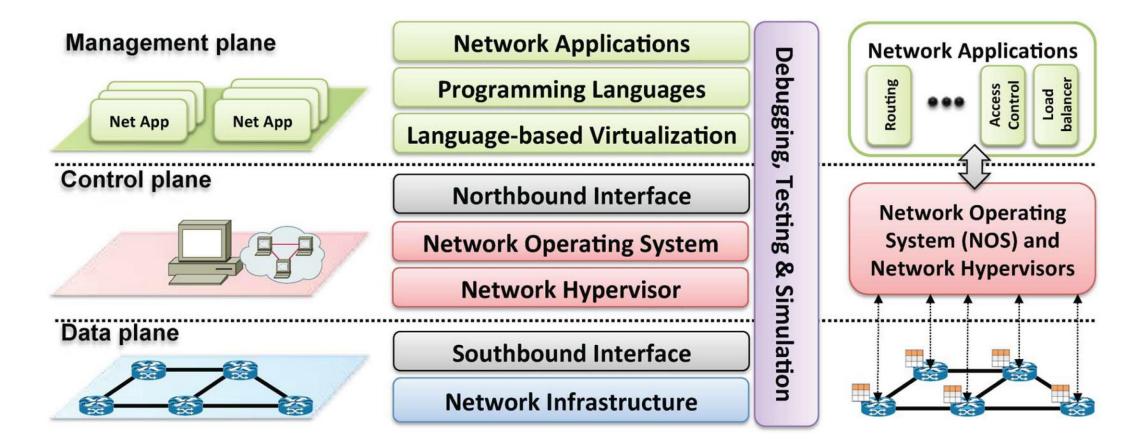

# SDN in different representations: planes, layers, system design architecture

Source: D. Kreutz, F. M. V. Ramos, P. E. Veríssimo, C. E. Rothenberg, S. Azodolmolky and S. Uhlig, "Software-Defined Networking: A Comprehensive Survey," in Proceedings of the IEEE, vol. 103, no. 1, pp. 14-76, Jan. 2015, doi: 10.1109/JPROC.2014.2371999.

Sant'Anna

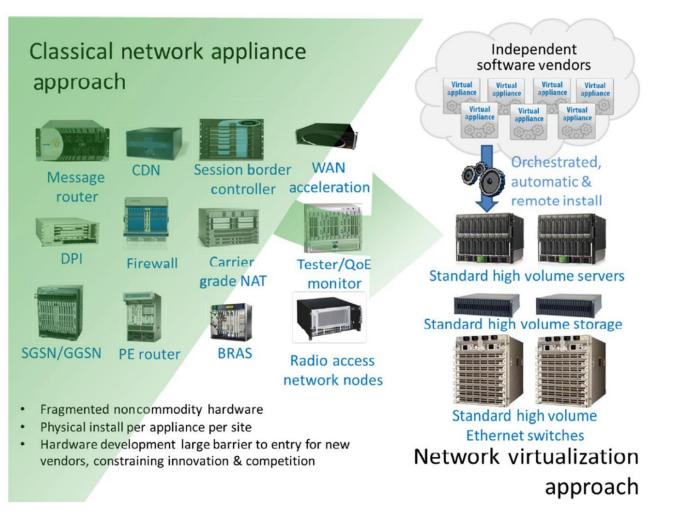

#### Network Function Virtualisation (VNF)

- ETSI has created an approach to migrate a Physical Network Function (PNF) to a Virtual Network Function (VNF)

- The core concept is that those physical functions run on commodity hardware with virtualized resources driven by software

- It is the replacement of network appliance hardware with virtual machines/containers

Paul Göransson, Chuck Black, Timothy Culver, Chapter 10 - Network Functions Virtualization, Editor(s): Paul Göransson, Chuck Black, Timothy Culver, Software Defined Networks (Second Edition), Morgan Kaufmann, 2017, Pages 241-252, ISBN 9780128045558, https://doi.org/10.1016/B978-0-12-804555-8.00010-7

TELECOMMUNICATIONS, COMPUTER ENGINEERING, AND PHOTONICS INSTITUTE

#### What can we virtualize ?

- ETSI NFV use cases includes a wide range of functions

- AR: Enterprise Access Router/Enterprise CPE

- PE: Provider Edge Router

- FW: Enterprise Firewall

- NG-FW: Enterprise NG-FW

- WOC: Enterprise WAN Optimization Controller

- DPI: Deep Packet Inspection (Appliance or a function)

- IPS: Intrusion Prevention System and other Security appliances

- Network Performance Monitoring

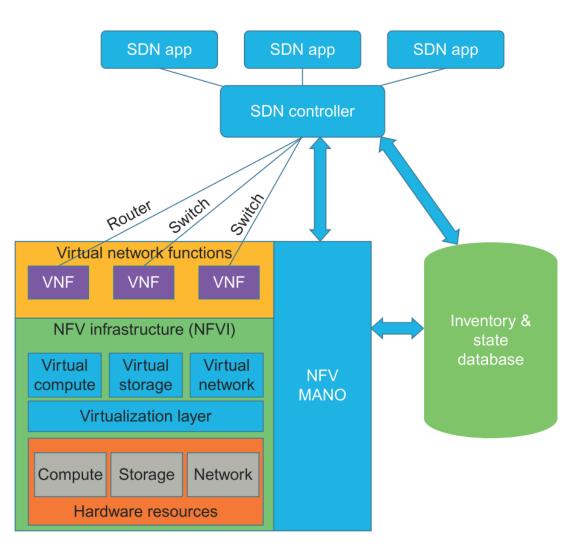

#### SDN and NFV

9

Trade off

## Flexibility

### Performance

© 2022 Scuola Superiore Sant'Anna

#### **ETSI NFV Releases**

#### **ETSI NFV Releases overview**

| Release 1                                                                                                                                                                                                                                                                                                                                                                          | > Release 2                                                                                                                                                                                                                                                                                                                                                                                                       | Release 3                                                                                                                                                                                                                                                                                                                                                                                | > Release 4                                                                                                                                                                                                                                                                                                                                                                                                |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Focus: the feasibility of NFV.</li> <li>Delivered the baseline studies and specifications.</li> <li>Set the NFV Architecture:</li> <li>Infrastructure (NFVI),</li> <li>Virtualized network functions (VNF),</li> <li>Integration of the VNFs into Network Services (NS), and</li> <li>NFV Management and Orchestration (NFV-MANO) aspects at different layers.</li> </ul> | <ul> <li>Focus: interoperability<br/>of NFV solutions.</li> <li>Details requirements<br/>and specification of<br/>interfaces and<br/>descriptors.</li> <li>Realizes the<br/>interoperability of<br/>solutions based on the<br/>NFV Architecture,<br/>detailing</li> <li>VNF Package and VNF<br/>and NS Descriptors,</li> <li>Acceleration,</li> <li>Internal and external<br/>NFV-MANO<br/>interfaces.</li> </ul> | <ul> <li>Focus: feature<br/>enriching the NFV<br/>Architectural<br/>Framework, readying<br/>NFV for deployment<br/>and operation.</li> <li>Interfaces, modeling,<br/>etc. to support new<br/>features such as (not<br/>exhaustive list):</li> <li>Policy framework,</li> <li>VNF snapshot,</li> <li>NFV-MANO<br/>management,</li> <li>Multi-site,</li> <li>Cloud-native, etc.</li> </ul> | <ul> <li>Focus: orchestration,<br/>cloudification and<br/>simplification of<br/>network deployment<br/>and operations.</li> <li>Interfaces, modeling,<br/>etc. to support new<br/>features such as (not<br/>exhaustive list):</li> <li>Container-based<br/>deployments,</li> <li>Further 5G support,</li> <li>Service-based<br/>architecture concepts,</li> <li>Generic OAM<br/>functions, etc.</li> </ul> |

Source:

https://docbox.etsi.org/ISG/NFV/Open/Other/ReleaseDocumentation/NFVTSC(21)000004r1\_Summary\_of\_NFV\_Releases\_by\_Jan\_2021.pdf © 2022 Scuola Superiore Sant'Anna School of Advanced Studies - Pisa

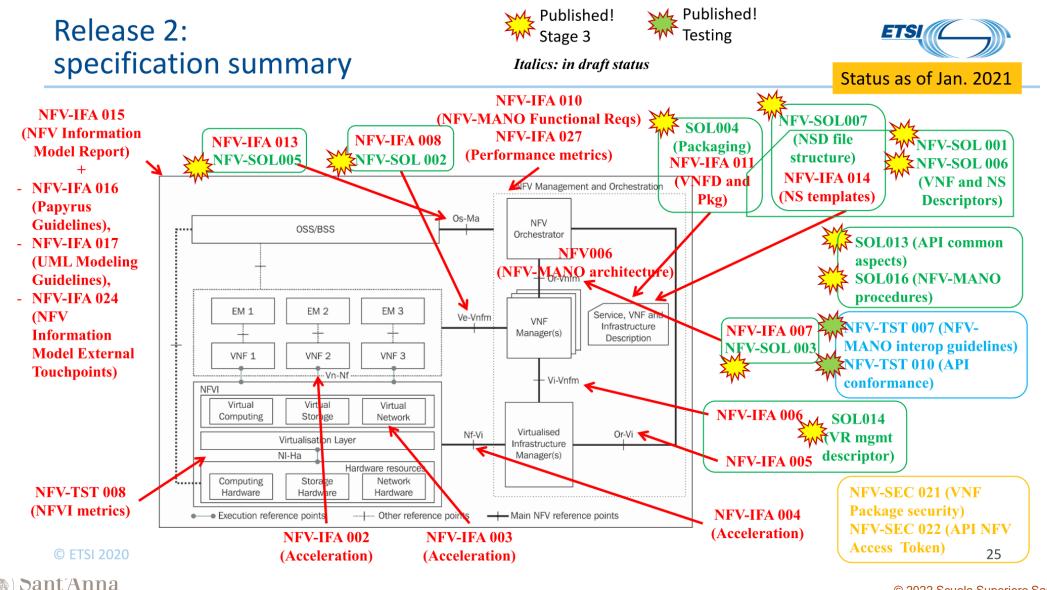

#### **ETSI NFV Release 2**

AND PHOTONICS

School of Advanced Studies - Pisa

12

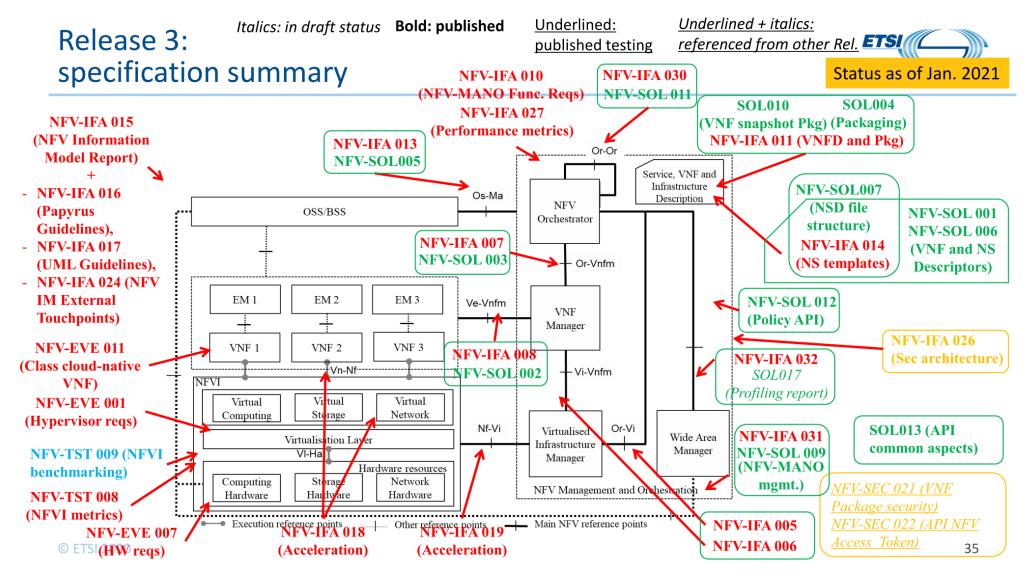

#### **ETSI NFV Release 3**

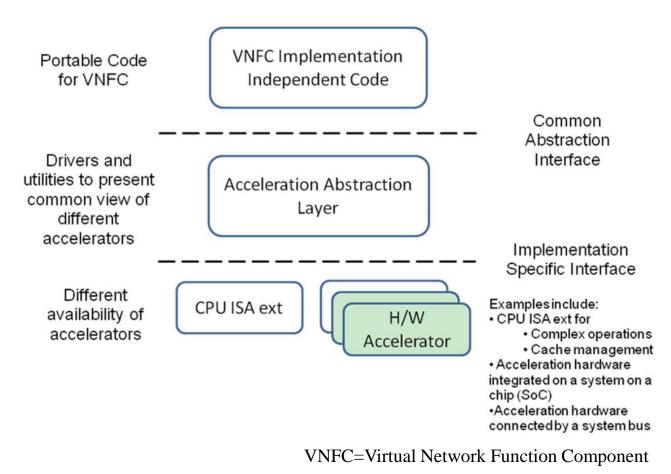

#### **VNF** Acceleration Use Cases

- Acceleration is not just about increasing performance.

- NFVI operators may seek different goals as far as acceleration is concerned:

- Reaching the desirable performance metric at a reasonable price.

- Best performance per processor core/cost/watt/square foot, whatever the absolute performance metric is.

- Reaching the maximum theoretical performance level.

TELECOMMUNICATIONS, COMPUTER ENGINEERING, AND PHOTONICS INSTITUTE

chool of Advanced Studies – Pis

Source: ETSI GS NFV-IFA 001 V1.1.1 (2015-12), Network Functions Virtualisation (NFV); Acceleration Technologies; Report on Acceleration Technologies & Use Cases

**Report on Acceleration Technologies & Use Cases** Sant'Anna

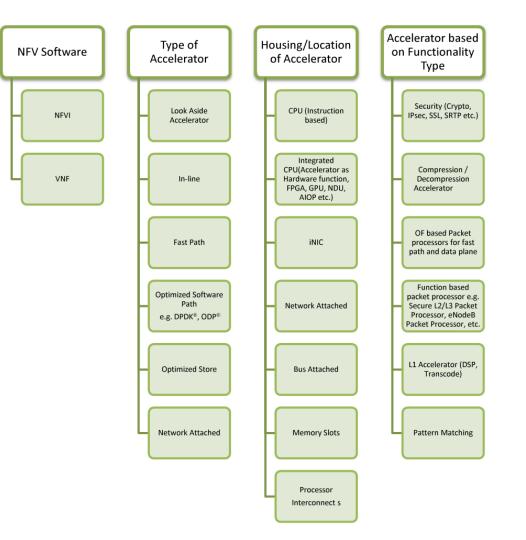

#### **Classification of accelerators**

TELECOMMUNICATIONS, COMPUTER ENGINEERING, AND PHOTONICS INSTITUTE School of Advanced Studies – Plea

Source: ETSI GS NFV-IFA 001 V1.1.1 (2015-12), Network Functions Virtualisation (NFV); Acceleration Technologies;

Sa Report on Acceleration Technologies & Use Cases

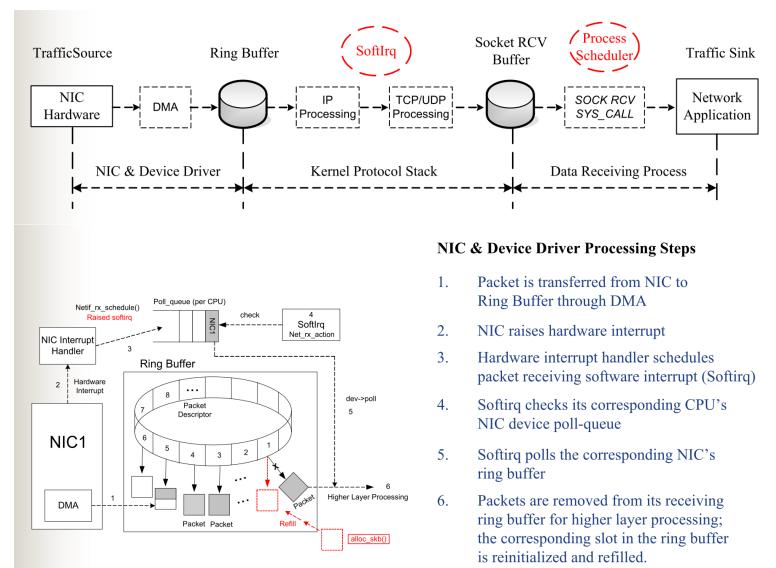

#### Linux Packet Receiving process

AND PHOTONI

Source: Wu, Wenji, Crawford, Matt, Bowden, Mark, and /Fermilab. The performance analysis of linux networking - packet receiving. United Safates: N. p., 2006. Web. © 2022 Scuola Superiore Sant'Anna

#### Network Data Plane Programmability

- Programmability

- the ability of the software or the hardware to execute an externally defined processing algorithm.

- Network programmability

- the ability to define the processing algorithm executed in a network and specifically in individual processing nodes, such as switches, routers, load balancers, etc.

- Data plane models have been proposed as abstractions of the hardware

- Data plane programming languages are tailored to those data plane models and provide ways to express algorithms for them in an abstract way

- The resulting code is then compiled for execution on a specific packet processing node supporting the respective data plane programming model.

Sant'Anna

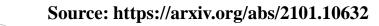

### Protocol-Independent Switching Architecture (PISA)

- Based on the concept of a programmable match-action pipeline

- The programmable parser allows programmers to declare arbitrary headers together with a finite state machine that defines the order of the headers within packets.

- The programmable match-action pipeline consists of multiple match-action units. Each unit includes one or more match-action-tables (MATs) to match packets and perform matchspecific actions with supplied action data.

- Each MAT includes matching logic coupled with the memory (static random-access memory (SRAM) or ternary content-addressable memory (TCAM)) to store lookup keys and the corresponding action data.

- In the programmable deparser, programmers declare how packets are serialized.

Sant'Anna

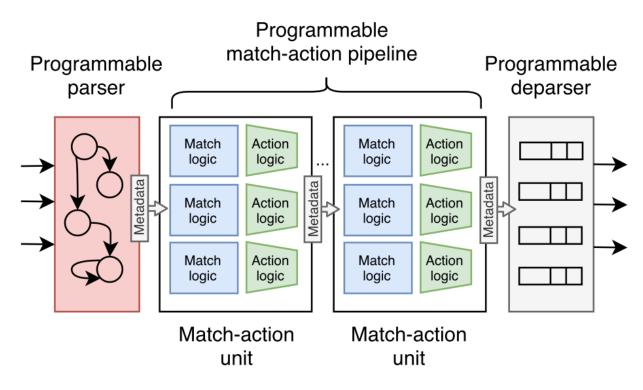

#### Data Plane Programming Languages

- A packet, processed by a PISA pipeline, consists of packet payload and packet metadata. PISA only processes packet metadata that travels from the parser all the way to the deparser but not the packet payload that travels separately.

- P4 (Programming Protocol-Independent Packet Processors) is the most widely used domain-specific programming language for describing data plane algorithms for PISA.

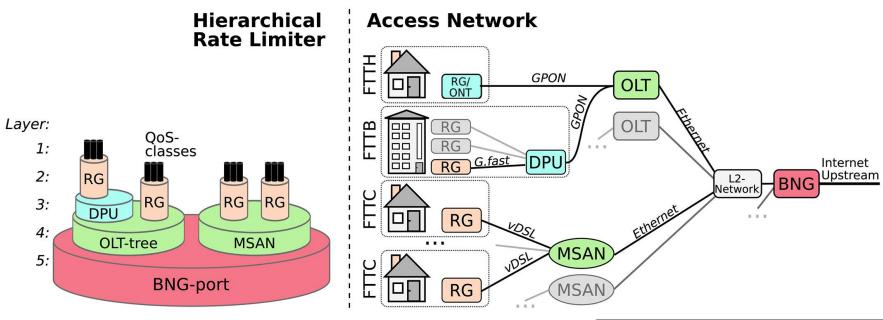

Example: Open Broadband Network Gateway (openBNG)

- Implementing NFV on commodity processors does not match the performance requirements of the highthroughput data plane components in large carrier access networks

- Programmable hardware architectures like field programmable gate arrays (FPGAs), network processors, and switch silicon supporting the flexibility of the P4 language offer a promising way to account for both performance requirements and the demand to quickly introduce innovations into networks

Source: Ralf Kundel, Leonhard Nobach, Jeremias Blendin, Wilfried Maas, Andreas Zimber, Hans-Joerg Kolbe, Georg Schyguda, Vladimir Gurevich, Rhaban Hark, Boris Koldehofe, Ralf Steinmetz, "OpenBNG: Central office network functions on programmable data plane hardware", DOI: 10.1002/nem.2134

#### **OpenBGN** functions

Sant'Anna School of Advanced Studies – Pisa

| Discovery and authentication | Parameters<br>Assignment | Access control and features enforcement | Connection<br>monitoring |

|------------------------------|--------------------------|-----------------------------------------|--------------------------|

| Subscriber<br>tunneling      |                          |                                         |                          |

| Authentication               | Authorization            | Access control                          | Accounting               |

|                              | Resource<br>allocation   | hierarchical<br>QoS                     | Accounting               |

|                              |                          | Traffic rate<br>enforcement             |                          |

| Layer 2                      |                          |                                         |                          |

**OpenBGN Hierachical QoS Implementation**

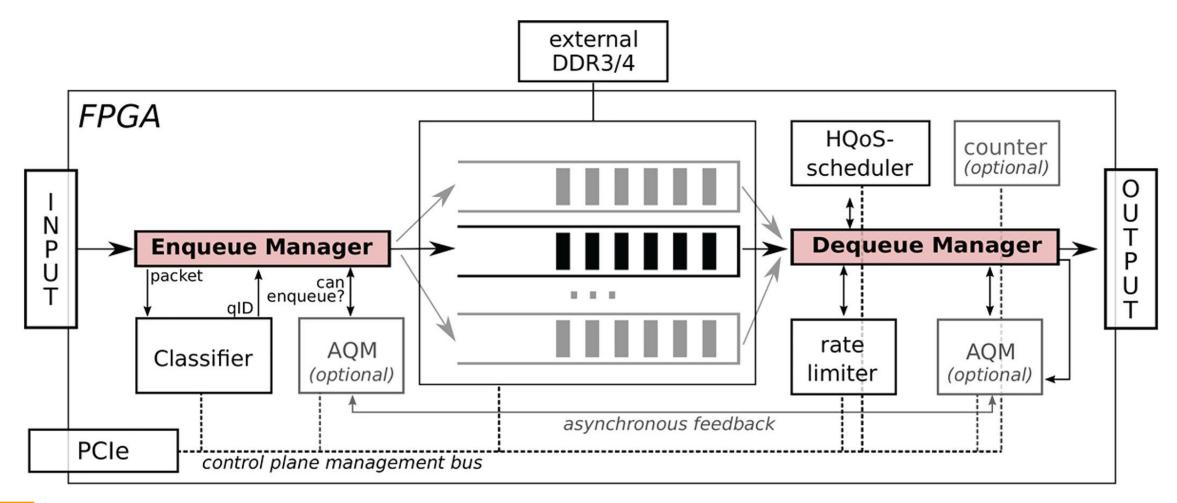

- Design overview of an FPGA-based QoS and shaping processor.

- After being processed by the P4-BNG pipeline, packets will enter the FPGA on the INPUT side.

- The enqueue manager decides, supported by a classifier and an optional Active Queue Management (AQM) module, if and in which queue a packet should be inserted.

- While being queued, packets are stored in external DRAM.

- The dequeue manager decides, which packet should be sent next and if packets should be dropped from a queue by an AQM algorithm.

– Parameter configuration can be done via PCIe

#### Architecture

#### Conclusions

- Edge-cloud continuum

- In network computing

- SDN

- NFVI

- Network data plane programmability

- Flexibility+performance

Seasonal School Artist 2022/2023

https://www.santannapisa.it/it/seasonalschool/artist-5g6g-networks-transforming-digital-society

#### justinecris.borromeo@santannpisa.it, luca.valcarenghi@santannapisa.it

### THANKS !!!