# Computing Just Right: Application-Specific Arithmetic with FloPoCo

#### Florent de Dinechin

S. Banescu, L. Besème, N. Bonfante, N. Brunie, M. Christ, S. Collange, O. Desrentes, J. Detrey, P. Echeverría, F. Ferrandi, L. Forget, M. Grad. K. Illyes, M. Istoan, M. Joldes, J. Kappauf, C. Klein, M. Kleinlein, M. Kumm, D. Mastrandrea, K. Moeller, B. Pasca, B. Popa, X. Pujol, G. Sergent, D. Thomas, R. Tudoran, A. Vasquez, A. Volkova.

### Outline

Intro: arithmetic operators

FloPoCo, the user point of view

Example: fixed-point functions

Example: multiplication and division by constants

Example: FIR filters

Example: IIR filters

Example: Multimodal sound synthesis (WIP)

Example: Low-precision logarithmic neuron

Example: floating-point exponential

Error analysis for dummies (and other proof assistants)

Example: fixed-point sine/cosine

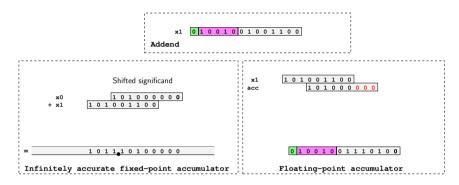

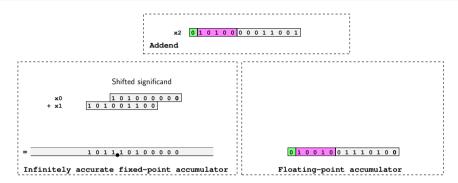

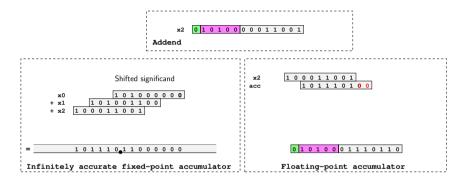

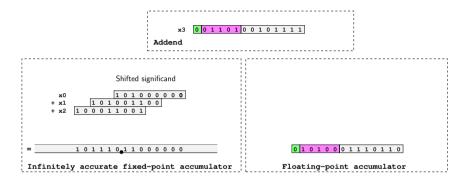

Example: floating-point sums and sums of products

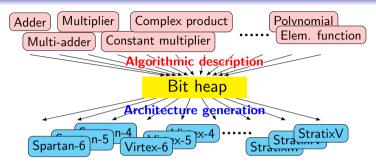

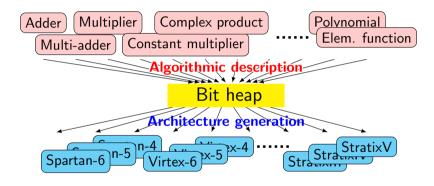

The universal bit heap

Conclusion

# **Bibliography**

You can find articles on all these subjects on the web page of FloPoCo.

And a book to be published soon by Springer:

Application-Specific Arithmetic, by Florent de Dinechin and Martin Kumm.

# Intro: arithmetic operators

Intro: arithmetic operators

FloPoCo, the user point of view

Example: fixed-point functions

Example: multiplication and division by constant

Example: FIR filters

Example: IIR filter

Example: Multimodal sound synthesis (WIP)

Example: Low-precision logarithmic neuron

Example: floating-point exponential

Error analysis for dummies (and other proof assistants)

Example: fixed-point sine/cosine

Example: floating-point sums and sums of products

The universal bit hear

Conclusion

- An arithmetic operation is a function (in the mathematical sense)

- few well-typed inputs and outputs

- no memory or side effect (usually)

- (even *DSP filters* are defined by a transfer function)

- An arithmetic operation is a function (in the mathematical sense)

- few well-typed inputs and outputs

- no memory or side effect (usually)

- (even *DSP filters* are defined by a transfer function)

- An operator is the *implementation* of such a function

- IEEE-754 FP standard: operator(x) = rounding(operation(x))

- Let's use the same approach for fixed-point operators, and non-standard ones

- → Clean mathematic definition, even for floating-point arithmetic

- An arithmetic operation is a function (in the mathematical sense)

- few well-typed inputs and outputs

- no memory or side effect (usually)

- (even *DSP filters* are defined by a transfer function)

- An operator is the *implementation* of such a function

- IEEE-754 FP standard: operator(x) = rounding(operation(x))

- Let's use the same approach for fixed-point operators, and non-standard ones

- → Clean mathematic definition, even for floating-point arithmetic

### An operator, as a circuit...

- ... is a direct acyclic graph (DAG):

- easy to build and pipeline

- easy to test against its mathematical specification

- An arithmetic operation is a function (in the mathematical sense)

- few well-typed inputs and outputs

- no memory or side effect (usually)

- (even *DSP filters* are defined by a transfer function)

- An operator is the *implementation* of such a function

- IEEE-754 FP standard: operator(x) = rounding(operation(x))

- Let's use the same approach for fixed-point operators, and non-standard ones

- → Clean mathematic definition, even for floating-point arithmetic

An operator, as a circuit...

- ... is a direct acyclic graph (DAG):

- easy to build and pipeline

- easy to test against its mathematical specification

And also, operators are small, no FPGA I/O problem, etc...

# FloPoCo, the user point of view

Intro: arithmetic operators

FloPoCo, the user point of view

Example: fixed-point functions

Example: multiplication and division by constants

Example: FIR filters

Example: IIR filters

cample: Multimodal sound synthesis (WIP)

Example: Low-precision logarithmic neuron

Example: floating-point exponential

Error analysis for dummies (and other proof assistants)

Example: fixed-point sine/cosine

Example: floating-point sums and sums of products

The universal bit hear

Conclusion

#### Here should come a demo

#### FloPoCo is freely available from

#### http://flopoco.org/

- Stable version 4.1.2: more operators

- git master version (will be 5.0): cleaner code, fewer operators

- used in these slides (mostly)

- several interface differences

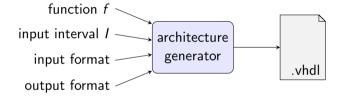

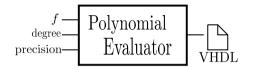

#### Command line syntax

- a sequence of operator specifications

- each with many parameters

- operator parameters (mandatory and optional)

- global optional parameters: target frequency, target hardware, ...

- Output: synthesizable VHDL.

# First something classical

A single precision floating-point adder

(8-bit exponent and 23-bit mantissa)

```

./flopoco FPAdd wE=8 wF=23

```

```

Final report:

```

|---Entity FPAdder\_8\_23\_uid2\_RightShifter

|---Entity IntAdder\_27\_f400\_uid7

|---Entity LZCShifter\_28\_to\_28\_counting\_32\_uid14

|---Entity IntAdder\_34\_f400\_uid17

Entity FPAdder 8\_23\_uid2

Output file: flopoco.vhdl

#### To probe further:

- ./flopoco FPAdd wE=11 wF=51

- double precision

- ./flopoco FPAdd wE=9 wF=36

just right for you

## Actually there are two variants

To get a larger but shorter-latency architectural variant:

./flopoco FPAdd wE=8 wF=23 dualpath=true

Here, dualpath is an optional performance option. (different VHDL, same function)

# Classical floating-point, continued

#### A complete single-precision FPU in a single VHDL file:

```

./flopoco FPAdd wE=8 wF=23 FPMult wE=8 wF=23 FPDiv wE=8 wF=23 FPSqrt wE=8

wF=23

Final report:

|---Entity FPAdder_8_23_uid2_RightShifter

|---Entity IntAdder_27_f400_uid7

|---Entity LZCShifter_28_to_28_counting_32_uid14

```

Entity FPAdder\_8\_23\_uid2

Entity Compressor\_2\_2

Entity Compressor\_3\_2

|---Entity IntAdder\_49\_f400\_uid39

$\verb|---Entity IntMultiplier_UsingDSP_24_48_unsigned_uid26|$

|---Entity IntAdder\_33\_f400\_uid47

|---Entity IntAdder\_34\_f400\_uid17

Entity FPMultiplier\_8\_23\_8\_23\_8\_23\_uid24

Entity FPDiv\_8\_23

Entity FPSqrt\_8\_23

Output file: flopoco.vhdl

F. de Dinechin Computing Just Right: Application-specific arithmetic

#### Damn lies

It was not a classical single-precision FPU

| 1 2                   | $w_E$ | $W_{\mathcal{F}}$ |

|-----------------------|-------|-------------------|

| $\longleftrightarrow$ | -     | $\rightarrow$     |

| s exn                 | Ε     | F                 |

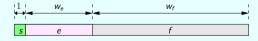

#### FloPoCo floating-point format

Inspired and compatible with IEEE-754, except that

• exponent size  $w_E$  and mantissa size  $w_F$  can take arbitrary values

#### Damn lies

It was not a classical single-precision FPU

| 1 2   | WE | W <sub>F</sub> |

|-------|----|----------------|

| s exn | Ε  | F              |

#### FloPoCo floating-point format

Inspired and compatible with IEEE-754, except that

- exponent size  $w_E$  and mantissa size  $w_E$  can take arbitrary values

- ullet 0,  $\infty$  and NaN flagged in 2 explicit *exception bits*: *exn*

- not as special exponent values

- (as a consequence, two more exponent values available in FloPoCo)

#### Damn lies

It was not a classical single-precision FPU

| 1 2                   | $w_E$ | $W_{F}$ |

|-----------------------|-------|---------|

| $\longleftrightarrow$ |       | ·       |

| s exn                 | E     | F       |

#### FloPoCo floating-point format

Inspired and compatible with IEEE-754, except that

- exponent size  $w_E$  and mantissa size  $w_E$  can take arbitrary values

- 0, ∞ and NaN flagged in 2 explicit exception bits: exn

- not as special exponent values

- (as a consequence, two more exponent values available in FloPoCo)

- subnormal numbers are not supported

- Adding 1 more exponent bit provides them all, and is much more area-efficient

- However we lose a-b==0  $\iff$  a==b

- ► HLS compiler writers, beware!

- Conversions operators from/to IEEE floating point available

#### Number formats in FloPoCo

- Integers and fixed-point numbers

- The previous floating-point format

- A few operators for IEEE floating-point format

- A few operators for posits

- Logarithm Number System (LNS) in older versions

- One Obscure Branch contains decimal arithmetic

- no Residue Number System (RNS) and other modular arithmetic waiting for them

... Plus good old binary fixed-point (integer) for quite a few operators

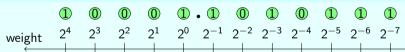

## Fixed-point format

Parameters for an unsigned (positive) fixed-point format

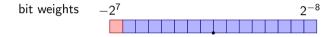

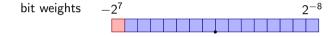

bit weights

$$2^5$$

$2^{-4}$  bit position  $m = 5 \ 4 \ 3 \ 2 \ 1 \ 0 \ -1 \ -2 \ -3 \ -4 = \ell$

$$X = \sum_{i=\ell}^{m} 2^{i} x_{i}$$

- m is the Most Significant Bit position, and determines the range

- ullet is the Least Significant Bit position, and determines the **precision**

Parameters for a fixed-point format in two's complement

bit weights

$$-2^5$$

$2^{-4}$  bit position  $m = 5 \ 4 \ 3 \ 2 \ 1 \ 0 \ -1 -2 -3 -4 = \ell$

$$X = -2^{m} x_{m} + \sum_{i=\ell}^{m-1} 2^{i} x_{i}$$

Integers have  $\ell = 0, m > 0$ .

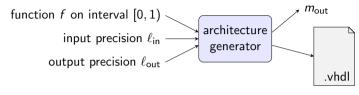

# Typical interface to a fixed-point FloPoCo operator

```

./flopoco FixFunctionByPiecewisePoly f="exp(x*x)" lsbIn=-24 lsbOut=-24 msbOut=3 d=3

```

## Typical interface to a fixed-point FloPoCo operator

./flopoco FixFunctionByPiecewisePoly f="exp(x\*x)" lsbIn=-24 lsbOut=-24

msbOut=3 d=3

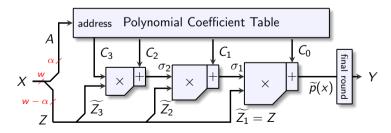

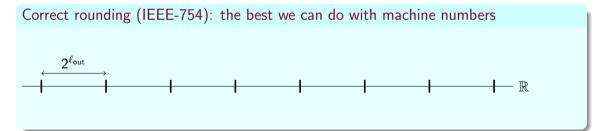

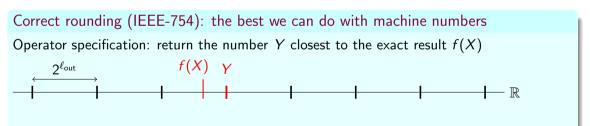

# Computing Just Right makes interfaces simpler

Never output bits that do not hold useful information:

## Output precision ( $\ell_{out}$ ) specifies operator accuracy

- ullet No need to compute more accurately than  $2^{\ell_{out}}$ : we couldn't output it

- No sense in computing less accurately than  $2^{\ell_{\text{out}}}$ :

we don't want to output garbage bits

# Computing Just Right makes interfaces simpler

Never output bits that do not hold useful information:

### Output precision ( $\ell_{out}$ ) specifies operator accuracy

- ullet No need to compute more accurately than  $2^{\ell_{out}}$ : we couldn't output it

- No sense in computing less accurately than  $2^{\ell_{\text{out}}}$ :

we don't want to output garbage bits

## Computing Just Right makes interfaces simpler

Never output bits that do not hold useful information:

## Output precision ( $\ell_{out}$ ) specifies operator accuracy

- No need to compute more accurately than  $2^{\ell_{\text{out}}}$ : we couldn't output it

- No sense in computing less accurately than  $2^{\ell_{\text{out}}}$ :

we don't want to output garbage bits

The difference between the computed value Y and f(X) will be at most  $2^{\ell_{\mathsf{out}-1}}$ .

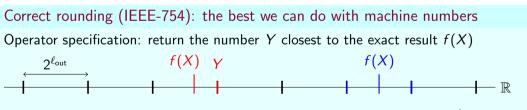

## It would be too simple, people would complain

Sometimes correct rounding is to expensive to implement, or just impossible to guarantee...

Faithful rounding: the next best thing

Two equivalent specifications:

- The output Y of the operator may be one of the two numbers surrounding f(X). When f(X) is a machine number, then Y = f(X).

- The difference between the output value Y and f(x) is strictly smaller than  $2^{\ell_{\text{out}}}$ .

## It would be too simple, people would complain

Sometimes correct rounding is to expensive to implement, or just impossible to guarantee...

Faithful rounding: the next best thing

Two equivalent specifications:

- The output Y of the operator may be one of the two numbers surrounding f(X). When f(X) is a machine number, then Y = f(X).

- The difference between the output value Y and f(x) is strictly smaller than  $2^{\ell_{\text{out}}}$ .

Slightly less accurate than correct rounding, but still:

if you add one bit to the output, you double the accuracy.

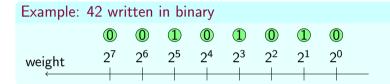

## Binary for theoretical physicists

- $2^{10} \approx 10^3$  (kBytes are actually 1024 bytes).

- Another point of view :  $10 \log_{10}(2) \approx 3$

- In other words, 1 bit  $\approx$  3 dB

I don't count signal/noise ratio in dB, I count accuracy in bits.

The same FPAdder, pipelined for 300MHz:

./flopoco frequency=300 FPAdd wE=8 wF=23

The same FPAdder, pipelined for 300MHz:

./flopoco frequency=300 FPAdd wE=8 wF=23

FloPoCo interface to pipeline construction

"Please pipeline this operator to work at 200MHz"

The same FPAdder, pipelined for 300MHz:

./flopoco frequency=300 FPAdd wE=8 wF=23

FloPoCo interface to pipeline construction

"Please pipeline this operator to work at 200MHz"

Not the choice made by other core generators...

The same FPAdder, pipelined for 300MHz:

./flopoco frequency=300 FPAdd wE=8 wF=23

FloPoCo interface to pipeline construction

"Please pipeline this operator to work at 200MHz"

Not the choice made by other core generators...

... but better because compositional

When you assemble components working at frequency f,

you obtain a component working at frequency f.

The same FPAdder, pipelined for 300MHz:

./flopoco frequency=300 FPAdd wE=8 wF=23

FloPoCo interface to pipeline construction

"Please pipeline this operator to work at 200MHz"

Not the choice made by other core generators...

... but better because compositional

When you assemble components working at frequency f,

you obtain a component working at frequency f.

Remark: automatic pipeline framework improved from version 4 to (future) version 5, but all the operators need to be ported.

# Examples of pipeline

```

./flopoco frequency=400 FPAdd wE=8 wF=23

Final report:

|---Entity FPAdder_8_23_uid2_RightShifter

Pipeline depth = 1

|---Entity IntAdder_27_f400_uid7

Pipeline depth = 1

---Entity LZCShifter_28_to_28_counting_32_uid14

Pipeline depth = 4

|---Entity IntAdder_34_f400_uid17

Pipeline depth = 1

Entity FPAdder_8_23_uid2

Pipeline depth = 9

```

./flopoco frequency=200 FPAdd wE=8 wF=23

```

Final report:

(...)

Pipeline depth = 4

```

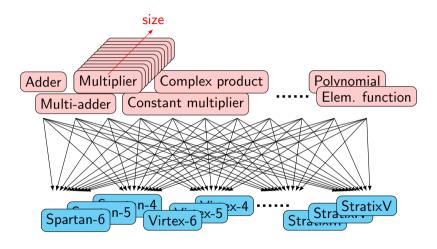

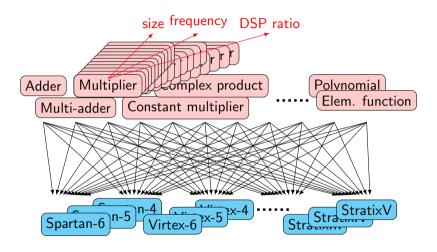

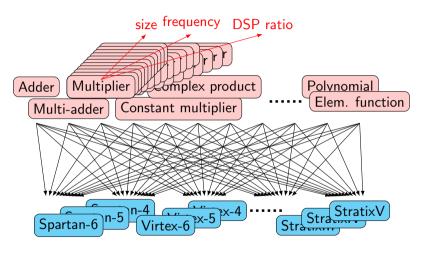

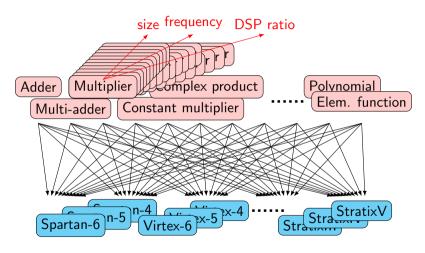

## Of course the frequency depends on the target FPGA

```

./flopoco target=Zynq7000 frequency=200 FPAdd wE=8 wF=23

```

```

Final report:

(...)

Pipeline depth = 5

```

```

./flopoco target=VirtexUltrascalePlus frequency=200 FPAdd wE=8 wF=23

```

```

Final report:

(...)

Pipeline depth = 1

```

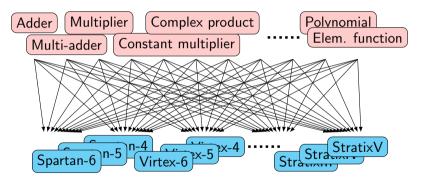

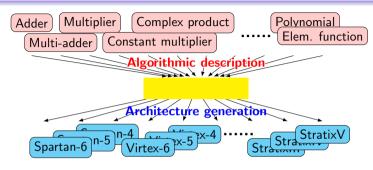

Altera and Xilinx targets supported in the stable branch (at various levels of accuracy, in various versions): Spartan3, Zynq7000, Virtex4, Virtex5, Virtex6, Kintex7, VirtexUltrascalePlus, StratixII, StratixIII, StratixIV, StratixV, CycloneII, CycloneII, CycloneIV, CycloneV.

# Frequency-directed pipelining in practice

## We do our best but we know it's hopeless

The actual frequency obtained will depend on the whole application (placement, routing pressure etc)...

- best-effort philosophy,

- aiming to be accurate to 10% for an operator synthesized alone

- asking a higher frequency provides a deeper pipeline

# Frequency-directed pipelining in practice

### We do our best but we know it's hopeless

The actual frequency obtained will depend on the whole application (placement, routing pressure etc)...

- best-effort philosophy,

- aiming to be accurate to 10% for an operator synthesized alone

- asking a higher frequency provides a deeper pipeline

And a big TODO: VLSI targets.

## Also match the architecture to the target FPGA

Compare the VHDL produced with FloPoCo 4.1.2 for

flopoco target=Virtex4 IntConstDiv wIn=16 d=3

flopoco target=Virtex6 IntConstDiv wIn=16 d=3

## Also match the architecture to the target FPGA

Compare the VHDL produced with FloPoCo 4.1.2 for

flopoco target=Virtex4 IntConstDiv wIn=16 d=3

flopoco target=Virtex6 IntConstDiv wIn=16 d=3

## Also match the architecture to the target FPGA

Compare the VHDL produced with FloPoCo 4.1.2 for

flopoco target=Virtex4 IntConstDiv wIn=16 d=3

flopoco target=Virtex6 IntConstDiv wIn=16 d=3

#### Architecture specificities

- LUTs

- DSP blocks

- memory blocks

#### Non-standard operators

• Correctly rounded divider by 3:

```

flopoco FPConstDiv wE=8 wF=23 d=3

```

• Floating-point exponential:

```

flopoco FPExp wE=8 wF=23

```

Multiplication of a 32-bit signed integer by the constant 1234567 (two algorithms, your mileage may vary):

```

flopoco IntIntKCM

```

flopoco IntConstMult

Full list in the documentation, or by typing just

flopoco

Sorry for the sometimes incomplete or inconsistent interface.

#### Don't trust us

TestBench generates a test bench for the operator preceding it on the command line

- flopoco FPExp wE=8 wF=23 TestBench n=10000 generates 10000 random tests

- flopoco IntConstDiv wIn=16 d=3 TestBench generates an exhaustive test

#### Don't trust us

TestBench generates a test bench for the operator preceding it on the command line

- flopoco FPExp wE=8 wF=23 TestBench n=10000 generates 10000 random tests

- flopoco IntConstDiv wIn=16 d=3 TestBench generates an exhaustive test

Specification-based test bench generation

Not by simulation of the generated architecture!

#### Don't trust us

TestBench generates a test bench for the operator preceding it on the command line

- flopoco FPExp wE=8 wF=23 TestBench n=10000 generates 10000 random tests

- flopoco IntConstDiv wIn=16 d=3 TestBench generates an exhaustive test

## Specification-based test bench generation

Not by simulation of the generated architecture!

Helper functions for encoding/decoding FP format, if you want to check the testbench...

- fp2bin 9 36 3.1415926

# **Example: fixed-point functions**

Intro: arithmetic operators

FloPoCo, the user point of view

Example: fixed-point functions

Example: multiplication and division by constant

Example: FIR filters

Example: IIR filter

Example: Multimodal sound synthesis (WIP)

Example: Low-precision logarithmic neuron

Example: floating-point exponential

Error analysis for dummies (and other proof assistants)

Example: fixed-point sine/cosine

Example: floating-point sums and sums of products

The universal bit heap

Conclusion

## Generic generator of fixed-point functions

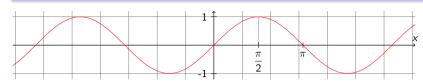

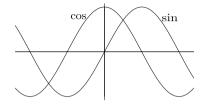

## The sine function

## The sine function

## Input format is in fixed point

Arbitrary choice in FloPoCo: the input domain will be [0,1) or [-1,1).

$$sin(x)$$

on  $[-1,1)$

$$\sin(\pi x)$$

on  $[-1,1]$

$$\sin(x)$$

on  $[-1,1)$   $\sin(\pi x)$  on  $[-1,1)$   $\sin(\frac{\pi}{2}x)$  on  $[0,1)$

#### Discretization issues

Inputs and outputs in [0,1) (4-bit fixed-point) :

## Possible fixes for corner-case discretization issues

## FixFunction By Table

flopoco FixFunctionByTable f="sin(pi/2\*x)" signedIn=0 lsbIn=-6 lsbOut=-6

Go check in the VHDL which solution is used... (Hint: remember that msbOut is computed.)

## FixFunctionByTable, fixed

flopoco FixFunctionByTable f="63/64\*sin(pi/2\*x)" signedIn=0 lsbIn=-6 lsbOut=-6

Go check the VHDL...

## Tables can hold functions that are arbitrarily ugly

$\sin(\frac{\pi}{2x})$  on [0,1)

flopoco FixFunctionByTable f="sin(pi/2/x)" signedIn=0 lsbIn=-16 lsbOut=-16

## Tables scaling

The previous example was a 16-bit in, 16-bit out.

## Tables scaling

The previous example was a 16-bit in, 16-bit out. (you just added 64 KLOC to your project)

## Tables scaling

The previous example was a 16-bit in, 16-bit out. (you just added 64 KLOC to your project)

#### Practical sizes

- The generated VHDL: 2<sup>-lsbIn</sup> lines of lsbOut bits each

- LUT cost:  $2^{-1sbIn-6} \times 1sbOut$

- A table of  $2^6 \times 6$  bits costs exactly 6 LUTs.

$\bullet$  A 20 Kb dual-port BlockRAM can hold two tables of  $2^{10} \times 10$  bits.

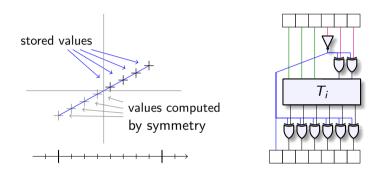

## FixFunctionByMultipartiteTable for 12 to 24 bits

- rule of thumb: cost grows as  $2^{p/2} \times p$  instead of  $2^p \times p$

- but requires the function to be continuous, derivable, and even monotonic

## One more trick: symmetry

We exploit symmetry to trade one table input bit for two rows of XOR gates...

#### And above 16 bits...

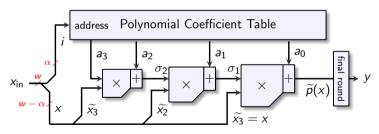

A generic piecewise polynomial approximation method: FixFunctionByPiecewisePoly

- requires higher-order derivability, but scales to 64 bits.

- One more parameter: the *degree* of the polynomials, trades-off **memory** and multipliers

All these function evaluation methods have the same interface, you can swap one for another.

# **Example: multiplication and division by constants**

FloPoCo, the user point of view Example: fixed-point functions

Example: multiplication and division by constants

Example: FIR filters

Example: Multimodal sound synthesis (WIP) Example: Low-precision logarithmic neuron

Example: floating-point exponentia

Error analysis for dummies (and other proof assistants)

Example: fixed-point sine/cosine

Example: floating-point sums and sums of products

The universal bit heap

Conclusion

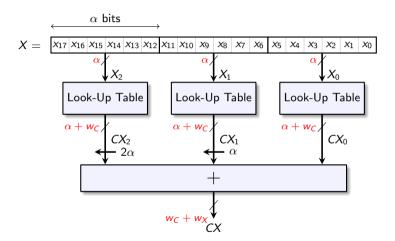

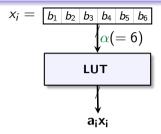

## Multiplication by a constant, first method

#### FPGA-specific LUT-based methods

• Write x in radix  $2^{\alpha}$ :  $x = \sum_{i=0}^{n} 2^{\alpha i} x_i$  with  $0 \le x_i < 2^{\alpha}$

$$\leftarrow \alpha$$

bits

Ex: good old hexadecimal is  $\alpha = 4$ :  $X = \begin{bmatrix} x_{11} | x_{10} | x_9 | x_8 & x_7 | x_6 | x_5 | x_4 & x_3 | x_2 | x_1 | x_0 \end{bmatrix}$

- then  $Cx = \sum_{i=0}^{n} 2^{\alpha i} (Cx_i)$

- ullet and tabulate the products  $Cx_i$  in lpha-input LUTs

- (also works if C is a real number like, say,  $1/\log(2)$ )

Extremely efficient for small n (input size) on LUT-based FPGAs.

## An architecture for 6-input LUTs

## Multiplication by a constant, second method

#### Shift-and-add methods for integer constants

•

$$17x = 16x + x = (x \ll 4) + x$$

•

$$15x = 16x - x$$

(Booth recoding)

•

$$7697x = 15x \ll 9 + 17x$$

(open problem here)

- very good recent ILP-based heuristics

- In FPGAs, take into account the size of each addition

## (demo?)

Extremely efficient for some constants such as 17.

## Multiplication by a constant, second method

#### Shift-and-add methods for integer constants

•

$$17x = 16x + x = (x \ll 4) + x$$

•

$$15x = 16x - x$$

(Booth recoding)

(open problem here)

- $7697x = 15x \ll 9 + 17x$

- very good recent ILP-based heuristics

- In FPGAs, take into account the size of each addition

(demo?)

Extremely efficient for some constants such as 17.

FloPoCo offers both methods (and the exponential uses both).

## Floating-point multiplication by a rational constant

# Motivation

divisions by 3 and by 9 in stencil applications  $\,$

# Floating-point multiplication by a rational constant

#### Motivation

divisions by 3 and by 9 in stencil applications

```

1/3 = 0.01010101010101010101010101010101\cdots

```

$$1/9 = 0.000111000111000111000111 \cdots$$

#### Two specificities

- The binary representation of the constant is periodic

- → specific optimisation of the shift-and-add approach

- Precision required for correct rounding

## Computing periodicity

A lemma adapted from 19th century number theory

Let a/b be an irreductible rational such that

- a < b

</p>

- 2 divides neither a nor b (powers of two are a matter of exponent)

#### Then

- $\bullet$  a/b has a purely periodic binary representation

- The period size s is the multiplicative order of 2 modulo b

- (the smallest integer such that  $2^s \mod b = 1$ )

- The periodic pattern is the integer  $p = \lfloor 2^s a/b \rfloor$

## Computing periodicity

#### A lemma adapted from 19th century number theory

Let a/b be an irreductible rational such that

- a < b

</p>

- 2 divides neither a nor b (powers of two are a matter of exponent)

#### Then

- $\bullet$  a/b has a purely periodic binary representation

- The period size s is the multiplicative order of 2 modulo b

- (the smallest integer such that  $2^s \mod b = 1$ )

- The periodic pattern is the integer  $p = \lfloor 2^s a/b \rfloor$

#### Example: 1/9

- b = 9; period size is s = 6 because  $2^6 \mod 9 = 1$ .

- The periodic pattern is  $\lfloor 1 \times 2^6/9 \rfloor = 7$ , which we write on 6 bits 000111, and we obtain that  $1/9 = 0.(000111_2)^{\infty}$ .

# Optimal architecture for precision $p_c$

## Correct rounding of a floating-point x by a rational a/b

A lemma adapted from the exclusion lemma of FP division

• Correct rounding on *n* bits needs  $n + 1 + \lceil \log_2 b \rceil$  bits of the constant

In practice, it is for free if b is small.

## This work was motivated by divisions by 3 and by 9

| constant       | р   | This work |     | previous SotA |      |       |

|----------------|-----|-----------|-----|---------------|------|-------|

|                |     | $p_c$     | #FA | $p_c$         | #FA  | depth |

| 1/3            | 24  | 32        | 118 | 27            | 190  | 4     |

|                | 53  | 64        | 317 | 56            | 368  | 5     |

| $p = 01_2$     | 113 | 128       | 792 | 116           | 1026 | 6     |

| 1/9            | 24  | 30        | 132 | 29            | 131  | 5     |

|                | 53  | 60        | 356 | 58            | 408  | 6     |

| $p = 000111_2$ | 113 | 120       | 885 | 118           | 1116 | 7     |

(The precisions chosen here are those of the IEEE754-2008 formats)

... But the FloPoCo code manages arbitrary a/b (including a>b).

## And now for something completely different

Instead of specializing multiplication, let us try and specialize division.

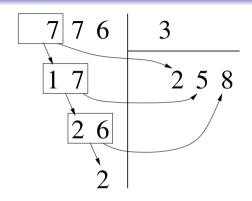

## Anybody here remembers how we compute divisions?

## Anybody here remembers how we compute divisions?

- iteration body: Euclidean division of a 2-digit decimal number by 3

- The first digit is a remainder from previous iteration: its value is 0, 1 or 2

- Possible implementation as a look-up table that, for each value from 00 to 29, gives the quotient and the remainder of its division by 3.

#### Writing an integer x in radix $2^{\alpha}$

$$x = \sum_{i=0}^{n} 2^{\alpha i} x_i$$

(split of the bits of x into chunks of  $\alpha$  bits)

Writing an integer x in radix  $2^{\alpha}$

$$x = \sum_{i=0}^{n} 2^{\alpha i} x_i$$

(split of the bits of x into chunks of  $\alpha$  bits)

Writing an integer x in radix  $2^{\alpha}$

$$x = \sum_{i=0}^{n} 2^{\alpha i} x$$

(split of the bits of x into chunks of  $\alpha$  bits)

Writing an integer x in radix  $2^{\alpha}$

$$x = \sum_{i=0}^{n} 2^{\alpha i} x$$

(split of the bits of x into chunks of  $\alpha$  bits)

Writing an integer x in radix  $2^{\alpha}$

$$x = \sum_{i=0}^{n} 2^{\alpha i} x$$

(split of the bits of x into chunks of  $\alpha$  bits)

Writing an integer x in radix  $2^{\alpha}$

$$x = \sum_{i=0}^{n} 2^{\alpha i} x$$

(split of the bits of x into chunks of  $\alpha$  bits)

Writing an integer x in radix  $2^{\alpha}$

$$x = \sum_{i=0}^{n} 2^{\alpha i} x$$

(split of the bits of x into chunks of  $\alpha$  bits)

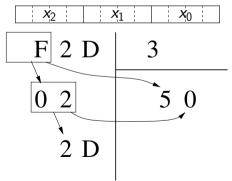

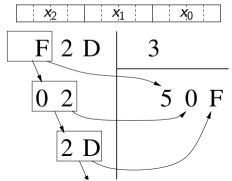

#### And now for some mathematical obfuscation

```

procedure ConstantDiv(x, d)

r_k \leftarrow 0

for i = k - 1 down to 0 do

y_i \leftarrow x_i + 2^{\alpha} r_{i+1}

(q_i, r_i) \leftarrow (\lfloor y_i/d \rfloor, \ y_i \mod d)

end for

\text{return } q = \sum_{i=0}^k q_i.2^{-\alpha i}, \ r_0

end procedure

```

(this + is a concatenation) (read from a table)

#### And now for some mathematical obfuscation

```

procedure ConstantDiv(x, d)

r_k \leftarrow 0

for i = k - 1 down to 0 do

y_i \leftarrow x_i + 2^{\alpha} r_{i+1} \qquad \qquad \text{(this + is a concatenation)}

(q_i, r_i) \leftarrow (\lfloor y_i/d \rfloor, \ y_i \mod d) \qquad \qquad \text{(read from a table)}

end for

return \ q = \sum_{i=0}^k q_i.2^{-\alpha i}, \ r_0

end procedure

```

#### Each iteration

- consumes  $\alpha$  bits of x, and a remainder of size  $\gamma = \lceil \log_2 d \rceil$

- ullet produces lpha bits of  $oldsymbol{q}$ , and a remainder of size  $\gamma$

- implemented as a table with  $\alpha + \gamma$  bits in,  $\alpha + \gamma$  bits out

# At this point nobody wants to see the proof

(if you're convinced the decimal version works...)

- prove that we indeed compute the Euclidean division

- $\bullet$  prove that the result is indeed a radix- $2^{\alpha}$  number

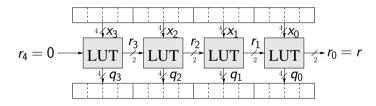

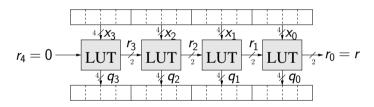

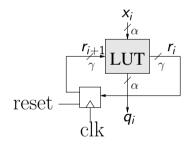

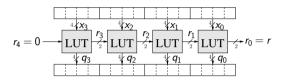

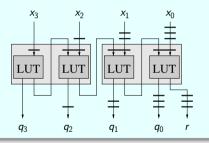

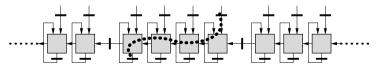

## Sequential implementation

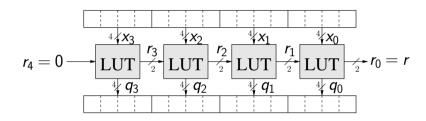

## Unrolled implementation

#### Logic-based version

For instance, assuming a 6-input LUTs (e.g. LUT6)

- A 6-bit in, 6-bit out consumes 6 LUT6

- Size of remainder is  $\gamma = \log_2 d$

- If  $d < 2^5$ , very efficient architecture:  $\alpha = 6 \gamma$

- The smaller *d*, the better

- Easy to pipeline (one register behind each LUT)

## Dual-port RAM-based version?

For larger d?

(not really studied, waiting for the demand)

# Synthesis results on Virtex-5 for combinatorial Euclidean division

|                        |      | n = 32 bits |         |

|------------------------|------|-------------|---------|

|                        |      |             |         |

| constant               | LUT6 | (predicted) | latency |

| $d = 3 \ (\alpha = 4)$ | 47   | (6*8=48)    | 7.14ns  |

| $d = 5 \ (\alpha = 3)$ | 60   | (6*11=66)   | 6.79ns  |

| $d = 7 \ (\alpha = 3)$ | 60   | (6*11=66)   | 7.30ns  |

|                        |      | n = 64 bits |         |

| constant               | LUT6 | (predicted) | latency |

| $d = 3 \ (\alpha = 4)$ | 95   | (6*16=96)   | 14.8ns  |

| $d = 5 \ (\alpha = 3)$ | 125  | (6*22=132)  | 13.8ns  |

| $d=7$ $(\alpha=3)$     | 125  | (6*22=132)  | 15.0ns  |

# Synthesis results on Virtex-5 for combinatorial Euclidean division

|                        |      | n=32 bits   |         |

|------------------------|------|-------------|---------|

| constant               | LUT6 | (predicted) | latency |

| $d = 3 \ (\alpha = 4)$ | 47   | (6*8=48)    | 7.14ns  |

| $d = 5 \ (\alpha = 3)$ | 60   | (6*11=66)   | 6.79ns  |

| $d = 7 \ (\alpha = 3)$ | 60   | (6*11=66)   | 7.30ns  |

|                        |      | n = 64 bits |         |

| constant               | LUT6 | (predicted) | latency |

| $d = 3 \ (\alpha = 4)$ | 95   | (6*16=96)   | 14.8ns  |

| $d = 5 \ (\alpha = 3)$ | 125  | (6*22=132)  | 13.8ns  |

| $d=7$ $(\alpha=3)$     | 125  | (6*22=132)  | 15.0ns  |

Logic optimizer even finds something to chew: don't care lines in the tables.

# Synthesis results on Virtex-5 for pipelined Euclidean division by 3

| n=32 bits       |                    |  |

|-----------------|--------------------|--|

| FF + LUT6       | performance        |  |

| 33 Reg + 47 LUT | 1 cycle @ 230 MHz  |  |

| 58 Reg + 62 LUT | 2 cycles @ 410 MHz |  |

| 68 Reg + 72 LUT | 3 cycles @ 527 MHz |  |

| n = 64 bits       |                    |  |

|-------------------|--------------------|--|

| FF + LUT6         | performance        |  |

| 122 Reg + 112 LUT | 2 cycles @217 MHz  |  |

| 168 Reg + 198 LUT | 5 cycles @ 410 MHz |  |

| 172 Reg + 188 LUT | 7 cycles @ 527 MHz |  |

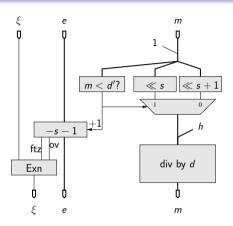

## Floating-point version is cheap, too

• pre-normalisation and pre-rounding:

$$\left|\frac{2^{s+\epsilon}m}{d}\right| = \left|\frac{2^{s+\epsilon}m}{d} + \frac{1}{2}\right| = \left|\frac{2^{s+\epsilon}m + d/2}{d}\right|$$

# Synthesis results on Virtex-5 for pipelined floating-point division by 3

## single precision

| FF + LUT6                          | performance         |  |

|------------------------------------|---------------------|--|

| 35 Reg + 69 LUT                    | 1 cycle @ 217 MHz   |  |

| 105 Reg + 83 LUT                   | 3 cycles @ 411 MHz  |  |

| standard correctly rounded divider |                     |  |

| 1122 Reg + 945 LUT                 | 17 cycles @ 290 MHz |  |

#### double precision

F. de Dinechin

| FF + LUT6           | performance        |  |

|---------------------|--------------------|--|

| 122 Reg + 166 LUT   | 2 cycles @ 217 MHz |  |

| 245 Reg + 250 LUT   | 6 cycles @ 410 MHz |  |

| using shift-and-add |                    |  |

| 282 Reg + 470 LUT   | 5 cycles @ 307 MHz |  |

Was it worth to spend so much time on division by 3?

## Was it worth to spend so much time on division by 3?

(this slide intentionally left blank)

### Was it worth to spend so much time on division by 3?

(this slide intentionally left blank)

(three years later, Ugurdag et al spent more time on a parallel version)

## My personal record

Two weeks from the first intuition of the algorithm to complete pipelined FloPoCo implementation + paper submission.

#### Implementation time

- 10 minutes to obtain a testbench generator

- 1/2 day for the integer Euclidean division

- 20 mn for its flexible pipeline

- 1/2 day for the FP divider by 3

- and again 20 mn

This was advertising for the FloPoCo framework.

# **Example: FIR filters**

Intro: arithmetic operators

FloPoCo, the user point of view

Example: fixed-point functions

Example: multiplication and division by constants

Example: FIR filters

Example: IIR filter

Example: Multimodal sound synthesis (WIP)

Example: Low-precision logarithmic neuron

Example: floating-point exponential

Error analysis for dummies (and other proof assistants)

Example: fixed-point sine/cosine

Example: floating-point sums and sums of products

The universal bit heap

Conclusion

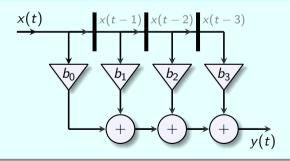

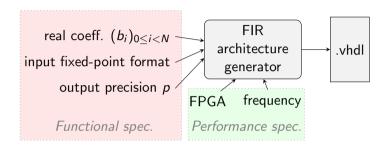

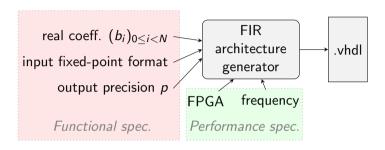

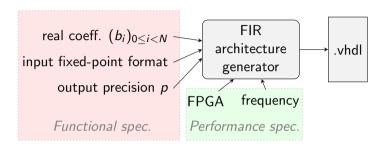

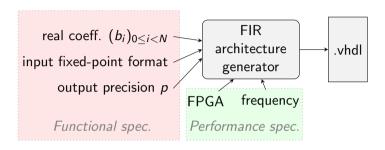

#### Finite Impulse Response filters

$$y(t) = \sum_{i=0}^{N-1} b_i x(t-i)$$

- the  $b_i$  are potentially real numbers (or almost: Matlab numbers)

- the x(t) and y(t) are discrete, fixed-point, low-precision signals

(the lower, the cheaper)

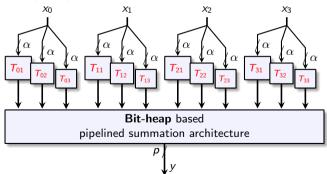

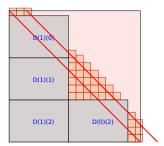

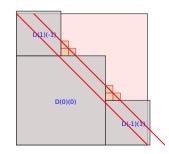

## FIR filters, architectural view (abstract)

$$y(t) = \sum_{i=0}^{N-1} b_i x(t-i)$$

#### Abtract architecture

$$y(t) = \sum_{i=0}^{N-1} b_i x(t-i)$$

The  $b_i$  are reals, therefore the exact result y may be an irrational.

$$y(t) = \sum_{i=0}^{N-1} b_i x(t-i)$$

Naive approach: round the  $b_i$  and the products to the target precision.

$$y(t) = \sum_{i=0}^{N-1} b_i x(t-i)$$

... but the accumulation of rounding errors makes the result inaccurate

$$y(t) = \sum_{i=0}^{N-1} b_i x(t-i)$$

Proposed approach: last-bit-accurate architecture with respect to the exact result

• Output precision defines accuracy of the architecture

- Output precision defines accuracy of the architecture

- Accuracy defines the optimal precisions to be used internally

- Output precision defines accuracy of the architecture

- Accuracy defines the optimal precisions to be used internally

No point in computing more, no point in computing less

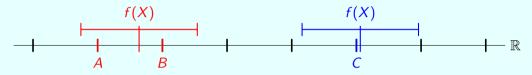

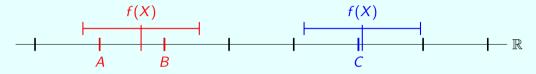

#### Example of the accuracy/cost tradeoff

#### 8-tap, 12 bit Root-Raised Cosine FIR filters

Naive,

$$p = 12$$

5.9 ns, 444 LUT  $\bar{\epsilon} > 2^{-9}$

Proposed,

$$p=12-4.4$$

ns, 564 LUT  $\bar{\epsilon} < 2^{-12}$

Proposed,

$$p=9$$

4.12 ns, 380 LUT  $\bar{\epsilon} < 2^{-9}$

#### Demo

- Coefficients entered as math. formulae

- FPGA-specific optimizations

- Frequency-directed pipeline

- Test-driven design

... and all the other operators

## Compute Just Right: Determining msbo

The MSB of  $a_i x_i$

- x<sub>i</sub> bounded (fixed-point number)

- a; known

$$msb_{a_ix_i} = \lceil \log_2(|a_i|val_{max}(x_i)) \rceil$$

The MSB of the sum

a<sub>i</sub>x<sub>i</sub> bounded

$$msb_o = msb_y = \lceil \log_2(\sum_{i=0}^{N-1} |a_i| val_{max}(x_i)) \rceil$$

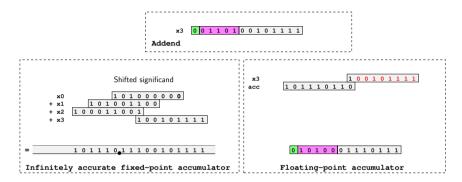

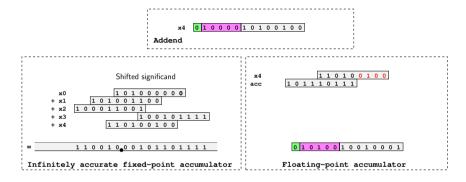

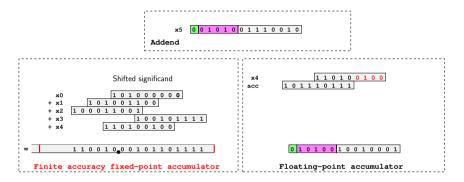

# Compute Just Right: Determining the LSB

Supose we use perfect multipliers:  $\varepsilon_{mult} < 2^{-p-1}$

# Compute Just Right: Determining the LSB

```

.0000100111111110100010101011101...

a_1 = .00101110110001000101001110000...

a_2 = .11000001011011010001001100101...

.00110101000001001110111001111...

a_0 x_0

+a_1x_1

+a_2x_2

+a_3x_3

```

Supose we use perfect multipliers:

$$arepsilon_{mult} < 2^{-p-1}$$

Supose we use perfect multipliers:

$$\varepsilon_{mult} < 2^{-p-1}$$

• sum error:  $\varepsilon_{y} = \sum\limits_{i=0}^{N} \varepsilon_{mult} < N \cdot 2^{-p-1}$

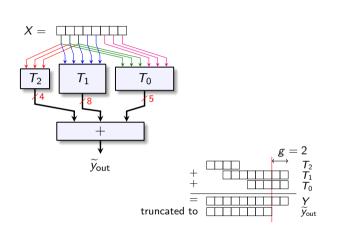

# Compute Just Right: Determining the LSB

Supose we use perfect multipliers:  $\varepsilon_{mult} < 2^{-p-1}$

• sum error:

$$\varepsilon_{y_{total}} = \sum_{i=0}^{N} \varepsilon_{mult} + \varepsilon_{final\_rounding} < N \cdot 2^{-p-g-1} + 2^{-p-1}$$

Need for larger intermediary precision

- g guard bits

- such that errors accumulate in the guard bits

$$\Longrightarrow \mathbf{g} = \lceil \log_2(N) \rceil$$

## Perfect constant multipliers in an FPGA

• basic FPGA computing element: look-up table (LUT)

### Perfect constant multipliers in an FPGA

- basic FPGA computing element: look-up table (LUT)

- tabulate all the  $2^{\alpha}$  values of  $\mathbf{a_i x_i}$

- ... correctly rounded to the output precision

#### Perfect constant multipliers in an FPGA

- basic FPGA computing element: look-up table (LUT)

- tabulate all the  $2^{\alpha}$  values of  $\mathbf{a_i x_i}$

- ... correctly rounded to the output precision

- perfect fit for small sizes:  $\alpha$ -input LUT +  $\alpha$ -bit input  $\Longrightarrow$  1 LUT/output bit

- but doesn't scale:

- 2 LUT/output bit for  $(\alpha + 1)$ -bit inputs,...

- $2^k$  LUT/output bit for  $(\alpha + k)$ -bit inputs

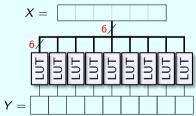

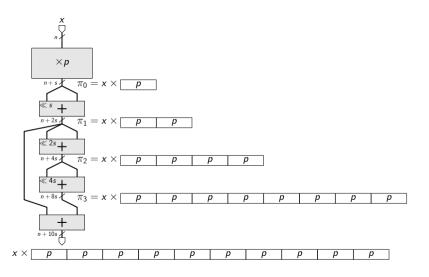

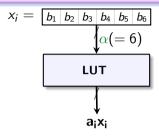

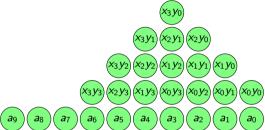

$$x_i = \sum_{k=1}^{n} 2^{-k\alpha} d_{ik}$$

where  $d_{ik} \in \{0, ..., 2^{\alpha} - 1\}$

$$x_i = \sum_{k=1}^n 2^{-k\alpha} d_{ik}$$

where  $d_{ik} \in \{0, ..., 2^{\alpha} - 1\}$

$$\Longrightarrow \mathbf{a_i} \mathbf{x_i} = \sum_{k=1}^n 2^{-k\alpha} a_i d_{ik}$$

$$x_i = \sum_{k=1}^{n} 2^{-k\alpha} d_{ik}$$

where  $d_{ik} \in \{0, ..., 2^{\alpha} - 1\}$

$$\implies a_i x_i = \sum_{k=1}^n 2^{-k\alpha} a_i d_{ik}$$

Each  $a_i d_{ik}$  tabulated, 1 LUT/output bit

$$x_i = \sum_{k=1}^{n} 2^{-k\alpha} d_{ik}$$

where  $d_{ik} \in \{0, ..., 2^{\alpha} - 1\}$

$$\implies a_i x_i = \sum_{k=1}^n 2^{-k\alpha} a_i d_{ik}$$

Each  $a_i d_{ik}$  tabulated, 1 LUT/output bit How many output bits?

$$x_i = \sum_{k=1}^{n} 2^{-k\alpha} d_{ik}$$

where  $d_{ik} \in \{0, ..., 2^{\alpha} - 1\}$

$$\implies a_i x_i = \sum_{k=1}^n 2^{-k\alpha} a_i d_{ik}$$

Each  $a_i d_{ik}$  tabulated, 1 LUT/output bit How many output bits?

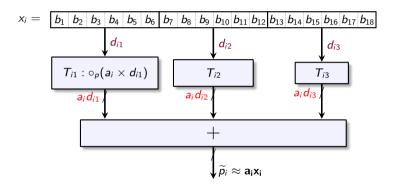

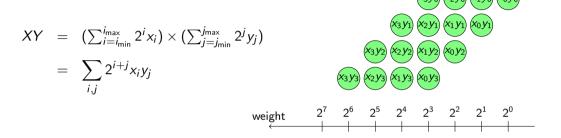

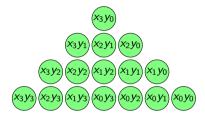

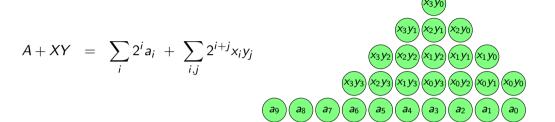

$$y = \sum_{i=0}^{N-1} \mathbf{a_i x_i}$$

$$y = \sum_{i=0}^{N-1} a_i x_i = \sum_{i=0}^{N-1} \sum_{k=1}^n 2^{-k\alpha} a_i d_{ik}$$

$$y = \sum_{i=0}^{N-1} a_i x_i = \sum_{i=0}^{N-1} \sum_{k=1}^{n} 2^{-k\alpha} a_i d_{ik}$$

- each  $a_i d_{ik}$  is a perfect multiplier

- therefore  $g = \lceil \log_2(N \cdot n) \rceil$

$$y = \sum_{i=0}^{N-1} a_i x_i = \sum_{i=0}^{N-1} \sum_{k=1}^{n} 2^{-k\alpha} a_i d_{ik}$$

- each  $a_i d_{ik}$  is a perfect multiplier

- therefore  $g = \lceil \log_2(N \cdot n) \rceil$

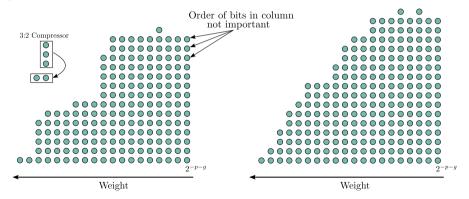

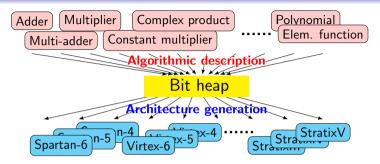

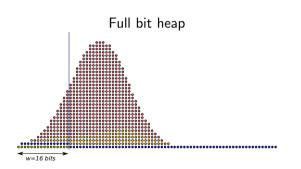

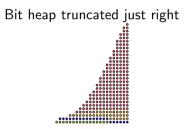

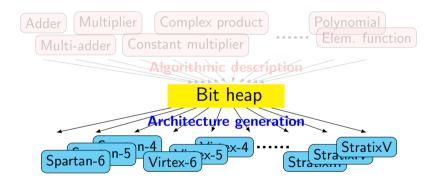

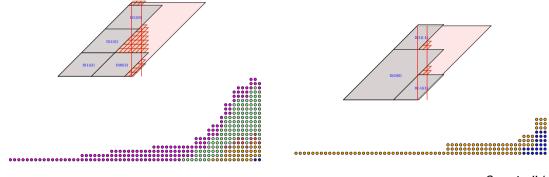

**Bit-heaps** (generalization of **bit arrays**) in FloPoCo (see FPL 2013 article)

• 8-tap, 12-bit FIR filters

Half-Sine

Root-Raised Cosine

## Work in progress

Extension to IIRs done last year

- (with Paris VI and ENS-Lyon)

- infinite accumulation of rounding errors: how many guard bits?

- link with a trusted library computing the worst-case peak gain of a filter

• Address the combinatorics of filter realizations

(with Paris VI)

• Filter approximation from frequency response

(with ENS-Lyon)

Remez with an arithmetic focus

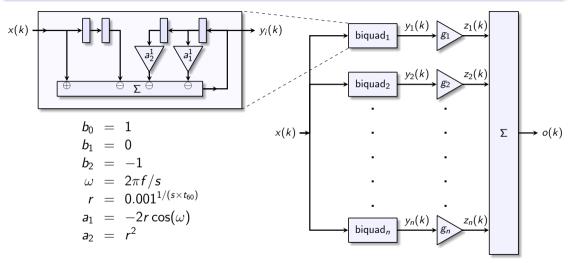

# **Example: IIR filters**

Intro: arithmetic operators

FloPoCo, the user point of view

Example: fixed-point functions

Example: multiplication and division by constants

Example: FIR filter

Example: IIR filters

Example: Multimodal sound synthesis (WIP)

Example: Low-precision logarithmic neuron

Example: floating-point exponential

Error analysis for dummies (and other proof assistants)

Example: fixed-point sine/cosine

Example: floating-point sums and sums of products

The universal bit hear

Conclusion

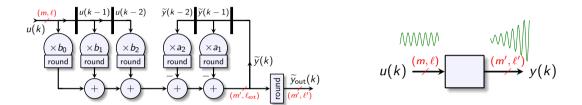

# Once upon a time in the green pastures of pure mathematics

... there lived a handsome filter named  ${\cal H}$

$$u(k) \longrightarrow \mathcal{H} \longrightarrow y(k)$$

<sup>&</sup>lt;sup>1</sup>This is a fairy tale, everybody knows Matlab does not compute with real numbers.

## Once upon a time in the green pastures of pure mathematics

... there lived a handsome filter named  ${\cal H}$

$$u(k) \longrightarrow \mathcal{H} \longrightarrow y(k)$$

$\mathcal{H}$  was linear and time-invariant.

He was born in the distant Frequency Domain from a frequency specification, which the Matlab fairies had transformed into a transfer function:

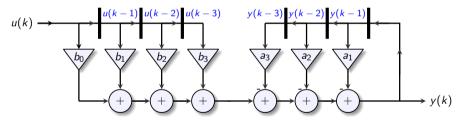

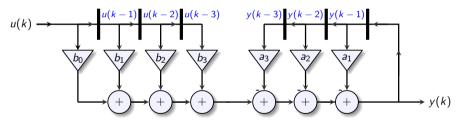

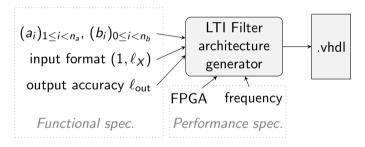

$$\mathcal{H}(z) = rac{\displaystyle\sum_{i=0}^{n_b} b_i z^{-i}}{1 + \displaystyle\sum_{i=1}^{n_a} a_i z^{-i}}, \quad orall z \in \mathbb{C}.$$

whose coefficients  $(a_i)$  and  $(b_i)$  were real numbers<sup>1</sup>.

<sup>&</sup>lt;sup>1</sup>This is a fairy tale, everybody knows Matlab does not compute with real numbers.

## And so $\mathcal{H}$ converged beautifully

using its evaluation formula in the time domain

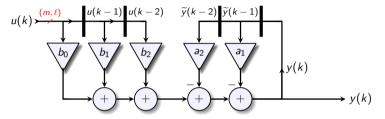

$$y(k) = \sum_{i=0}^{n_b} b_i u(k-i) - \sum_{i=1}^{n_a} a_i y(k-i)$$

as long as  ${\cal H}$  remained safely linear and its poles safely within the unit circle.

## And so $\mathcal{H}$ converged beautifully

using its evaluation formula in the time domain

$$y(k) = \sum_{i=0}^{n_b} b_i u(k-i) - \sum_{i=1}^{n_a} a_i y(k-i)$$

as long as  ${\cal H}$  remained safely linear and its poles safely within the unit circle.

But the fairies had warned  $\mathcal{H}$ :

Don't let your poles come close to the unit circle! And above all, remain linear!

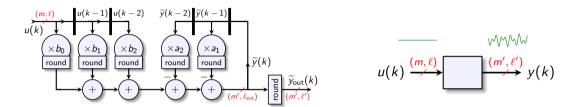

### But one day, ${\cal H}$ decided to travel far from home

Our hero decided to visit the land of Digital Circuits, a rough and arid country where ony binary fixed-point numbers could live.

### But one day, ${\cal H}$ decided to travel far from home

Our hero decided to visit the land of Digital Circuits, a rough and arid country where ony binary fixed-point numbers could live.

${\cal H}$  thought he could feed on them, for a fixed-point number is also a real number.

### But one day, ${\cal H}$ decided to travel far from home

Our hero decided to visit the land of Digital Circuits, a rough and arid country where ony binary fixed-point numbers could live.

${\cal H}$  thought he could feed on them, for a fixed-point number is also a real number.

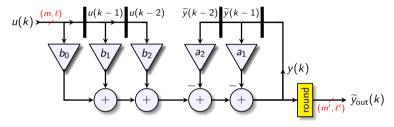

But  $\mathcal{H}$  also had to round his outputs, and this transformed him into a vile monster with a tilde.

To become a Digital Circuit, an LTI filter had to be cursed with time-domain rounding

To become a Digital Circuit, an LTI filter had to be cursed with time-domain rounding

To become a Digital Circuit, an LTI filter had to be cursed with time-domain rounding

on its output

To become a Digital Circuit, an LTI filter had to be cursed with time-domain rounding

- on its output

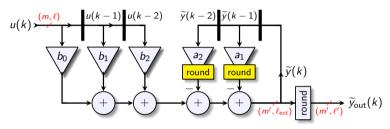

- and on its feedback loops if it was recursive

for without rounding, a product has more bits than each of its arguments.

To become a Digital Circuit, an LTI filter had to be cursed with time-domain rounding

- on its output

- and on its feedback loops if it was recursive

for without rounding, a product has more bits than each of its arguments.

For performance, it was not uncommon to see time-domain rouding warts all over the innards of a circuit...

Time-domain rounding is not linear, and for this reason

${\cal H}$  was cut from his transfer function heritage!

Time-domain rounding is not linear, and for this reason

${\cal H}$  was cut from his transfer function heritage!

Sometimes he would become an unstable digital circuit, in a way difficult to predict.

Time-domain rounding is not linear, and for this reason

${\cal H}$  was cut from his transfer function heritage!

Sometimes he would become an unstable digital circuit, in a way difficult to predict.

Sometimes he would even become a zombie with limit cycle oscillations,

howling in the night even when fed with a null signal.

Time-domain rounding is not linear, and for this reason

${\cal H}$  was cut from his transfer function heritage!

Sometimes he would become an unstable digital circuit, in a way difficult to predict.

Sometimes he would even become a zombie with limit cycle oscillations,

howling in the night even when fed with a null signal.

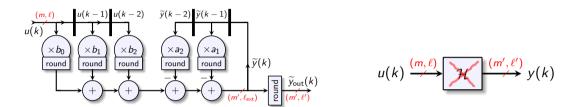

## So $\mathcal{H}$ was crying, alone and forgotten

### So $\mathcal{H}$ was crying, alone and forgotten

... when the good old witch FloPoCo heard his complaint.

Looking at him, she said:

you're not that evil, you are just poorly specified.

### So ${\cal H}$ was crying, alone and forgotten

... when the good old witch FloPoCo heard his complaint.

Looking at him, she said:

you're not that evil, you are just poorly specified.

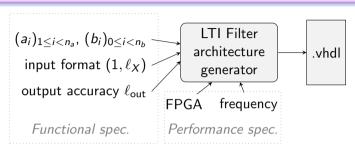

And in a whip of her magical TikZ cursor, she designed him a new interface:

### So ${\cal H}$ was crying, alone and forgotten

... when the good old witch FloPoCo heard his complaint.

Looking at him, she said:

you're not that evil, you are just poorly specified.

And in a whip of her magical TikZ cursor, she designed him a new interface:

These  $a_i$  and  $b_i$  were reals! The very real coefficients!

${\cal H}$  suddenly felt much lighter.

### So ${\cal H}$ was crying, alone and forgotten

... when the good old witch FloPoCo heard his complaint.

Looking at him, she said:

you're not that evil, you are just poorly specified.

And in a whip of her magical TikZ cursor, she designed him a new interface:

These  $a_i$  and  $b_i$  were reals! The very real coefficients!

${\cal H}$  suddenly felt much lighter.

But but

No, said FloPoCo, for I have, somewhere in my library, a spell that can compute it out of your coefficients.

No, said FloPoCo, for I have, somewhere in my library, a spell that can compute it out of your coefficients. (wait a moment, where is it? It was written by poor princess Anastasia Volkova during her captivity in the caves of the mighty sorcerers Lauter and Hilaire...)

No, said FloPoCo, for I have, somewhere in my library, a spell that can compute it out of your coefficients. (wait a moment, where is it? It was written by poor princess Anastasia Volkova during her captivity in the caves of the mighty sorcerers Lauter and Hilaire...) (I hope it still compiles...)

No, said FloPoCo, for I have, somewhere in my library, a spell that can compute it out of your coefficients. (wait a moment, where is it? It was written by poor princess Anastasia Volkova during her captivity in the caves of the mighty sorcerers Lauter and Hilaire...) (I hope it still compiles...) Ha, here you go:

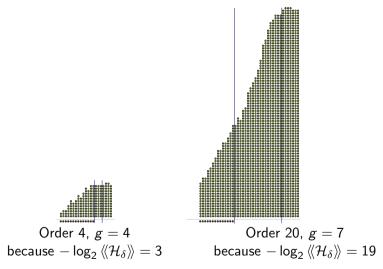

Definition: Worst-Case Peak Gain  $\langle\!\langle \mathcal{H} \rangle\!\rangle$  of a filter  $\mathcal{H}$

$$\langle\!\langle \mathcal{H} \rangle\!\rangle = \max_{||u||_{\infty} = 1} ||y||_{\infty}$$

where  $||u||_{\infty}$  is defined as  $||u||_{\infty} = \max_{k} |u(k)|$ .

Then of course,

$$m_R = \lceil \log_2 \langle\!\langle \mathcal{H} \rangle\!\rangle \rceil$$

.

#### But how will this save me from diverging? cried ${\cal H}$

ullet Remember: you are  ${\cal H}$ , answered the good witch and  ${\cal H}$  doesn't diverge in the pure mathematical world

### But how will this save me from diverging? cried ${\cal H}$

- ullet Remember: you are  ${\cal H}$ , answered the good witch and  ${\cal H}$  doesn't diverge in the pure mathematical world

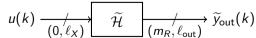

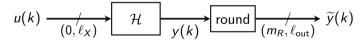

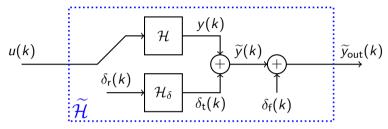

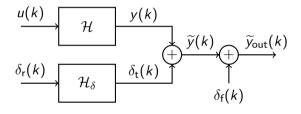

- Let me cast this spell on your architecture:  $\widetilde{\mathcal{H}}$  shall return a result that is that of  $\mathcal{H}$ , rounded only once.

- ullet Then, your alter ego  $\widetilde{\mathcal{H}}$  won't diverge.

#### But how will this save me from diverging? cried ${\cal H}$

- ullet Remember: you are  ${\cal H}$ , answered the good witch and  ${\cal H}$  doesn't diverge in the pure mathematical world

- Let me cast this spell on your architecture:  $\widetilde{\mathcal{H}}$  shall return a result that is that of  $\mathcal{H}$ , rounded only once.

- ullet Then, your alter ego  $\widetilde{\mathcal{H}}$  won't diverge.

$$u(k) \xrightarrow{(0,\ell_X)} \mathcal{H} \xrightarrow{y(k)} \text{round} \xrightarrow{(m_R,\ell_{\text{out}})} \widetilde{y}(k)$$

And FloPoCo invoked his two most crafted gremlins, Istoan and de Dinechin, to code this spell, with the help of Princess Anastasia who had managed to escape her tormentors.

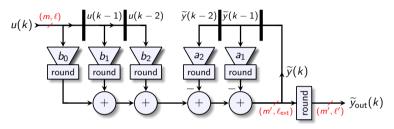

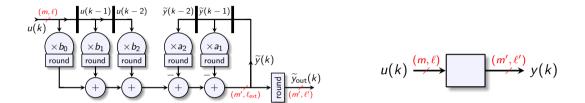

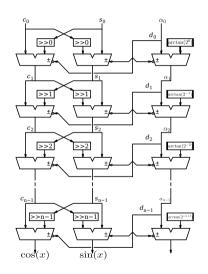

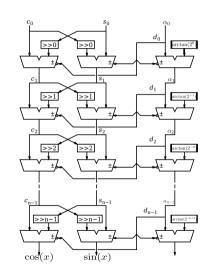

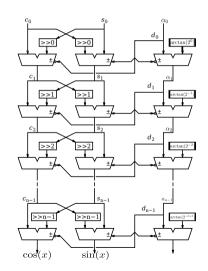

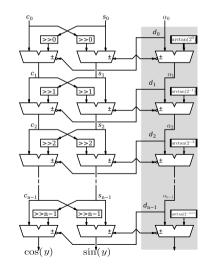

#### Actual architecture

#### Actual architecture

Another point of view:

When  $\ell_{\text{ext}} \to -\infty$  (which means: as the internal accuracy increase), at some point the computation shall become accurate enough for  $\widetilde{\mathcal{H}}$  to converge.

### Amplification of errors on the feedback loop

Here should come 3 pages of runes which end in the following figure:

•  $\delta_r$  is the sum of all rounding errors

$$\delta_{\mathsf{r}}(k) = \widetilde{y}(k) - \left(\sum_{i=0}^{n_b} b_i u(k-i) - \sum_{i=1}^{n_a} a_i \widetilde{y}(k-i)\right)$$

•  $\mathcal{H}_{\delta}$  is the virtual filter that captures the error amplification on the feedback loop:

$$\overline{\delta}_t = \langle\!\langle \mathcal{H}_\delta \rangle\!\rangle \, \overline{\delta}_r \ .$$

#### Errors are captured, let us chain them in the basement

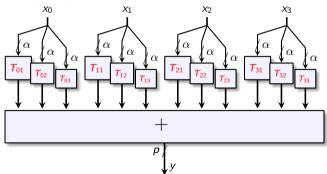

### Rounding errors depend on the architecture

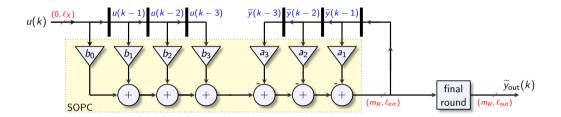

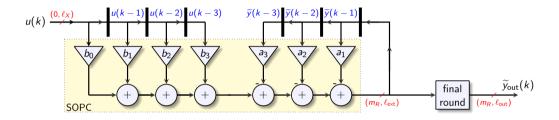

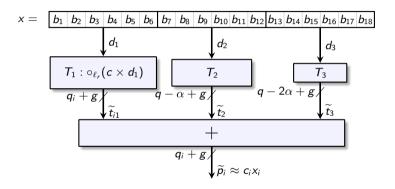

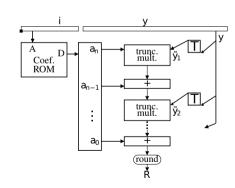

Example: An architecture optimized for LUT-based FPGAs:

• Split an input x into D chunks of  $\alpha$  bits (e.g.  $\alpha = 4$ : hexadecimal).

$$x = \sum_{k=1}^{D} 2^{-k\alpha} d_k$$

where  $d_k \in \{0,...,2^{\alpha}-1\}$

• Then cx becomes

$$cx = \sum_{k=1}^{D} 2^{-k\alpha} c d_k$$

• Tabulate each  $cd_k$  sub-product in an  $\alpha$ -input table indexed by  $d_k$

• Remark: c is a real number here, no need to quantize it!

#### A LUT-based architecture

The error is proportional to  $2^{-g}$ , so can made as small as needed by increasing g.

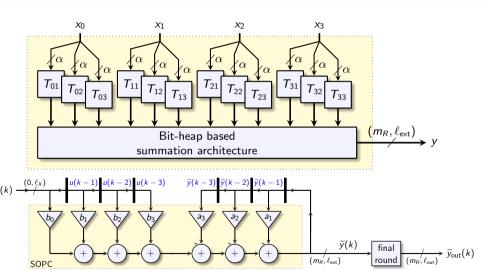

#### Overall architecture

## You're not evil, you're just poorly specified

- $\bullet$   $a_i$  and  $b_i$ : real numbers

- high-precision numbers from Matlab

- mathematical formulae such as sin(3\*pi/8)

- $\ell_X$  and  $\ell_{\text{out}}$ : integers denoting the weight of the least significant bits of the input and of the result.

#### Computing just right (TM)

$\ell_{\text{out}}$  specifies output precision, but also output accuracy.

#### A demo?

#### A small Butterworth filter

```

./flopoco generateFigures=1 FixIIR

coeffb="0x1.7bdf4656ab602p-9:0x1.1ce774c100882p-7:0x1.1ce774c100882p-7:0x1.7bdf4656ab602p-9"

coeffa="-0x1.2fe25628eb285p+1:0x1.edea40cd1955ep+0:-0x1.106c2ec3d0af8p-1"

lsbIn=-12 lsbOut=-12

TestBench n=10000

```

a radar filter submitted to Thibault a few years ago, with poles really close to 1

```

./flopoco generateFigures=1 FixIIR

coeffb="0x1.89ff611d6f472p-13:-0x1.2778afe6e1ac0p-11:0x1.89f1af73859fap-12:

0x1.89f1af73859fap-12:-0x1.2778afe6e1ac0p-11:0x1.89ff611d6f472p-13"

coeffa="-0x1.3f4f52485fe49p+2:0x1.3e9f8e35c8ca8p+3:-0x1.3df0b27610157p+3:

0x1.3d42bdb9d2329p+2:-0x1.fa89178710a2bp-1"

lsbIn=-12 lsbOut=-12

TestBench n=10000

```

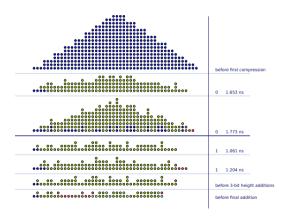

### Bit heaps for some 12-bit Butterworth filters

Sometimes I wonder if this is the right arithmetic for this problem.

## Everybody lived happily ever after...

- A point of view on filter design that is universal

- don't compute useless bits: output format specifies output accuracy

- complete error analysis (coefficient quantization + architectural rounding errors)

- error amplification captured by a safe implementation of the WCPG

#### Everybody lived happily ever after...

- A point of view on filter design that is universal

- don't compute useless bits: output format specifies output accuracy

- complete error analysis (coefficient quantization + architectural rounding errors)

- error amplification captured by a safe implementation of the WCPG

- Also a magical cure for a few other filter diseases

- If you input a 0 signal, the output converges to 0

$(\pm \ 1$  unit in the last place)

## Everybody lived happily ever after...

- A point of view on filter design that is universal

- don't compute useless bits: output format specifies output accuracy

- complete error analysis (coefficient quantization + architectural rounding errors)

- error amplification captured by a safe implementation of the WCPG

- Also a magical cure for a few other filter diseases

- If you input a 0 signal, the output converges to 0

$(\pm \ 1$  unit in the last place)

A finely tuned implementation that uses FPGA-specific arithmetic

#### ... And they had a lot of children

This is just a basic block on the way to more interesting filter structures.

- implementation space: state space, SIF

- clean rule of the game: enables comparison of functionally equivalent architectures

(to be continued)

- Try me in FloPoCo v. 4.1.3 or later

- Read more on HAL or in IEEETC

Towards Hardware IIR Filters Computing Just Right: Direct Form I Case Study

## Later, they visited the Frequency Domain Fairies

... with two presents to help them design circuits that obey a frequency specification:

#### Definitive Curse 1

A digital circuit  $\mathcal C$  is said to be faithful to a stable LTI filter  $\mathcal H$  iff the numerical difference between the fixed-point output  $\widetilde{y}_{\mathrm{out}}(k)$  of  $\mathcal C$  and the exact result y(k) of  $\mathcal H$  does not exceed one unit in the last place of  $\widetilde{y}_{\mathrm{out}}(k)$ .

#### **Definitive Curse 2**

A Digital Circuit  $\mathcal C$  is said to be faithful to a frequency specification iff there exists a stable LTI filter  $\mathcal H$  such that  $1/\mathcal H$  respects the frequency specification, and  $2/\mathcal C$  is faithful to  $\mathcal H$ .

# Example: Multimodal sound synthesis (WIP)

Intro: arithmetic operators

FloPoCo, the user point of view

Example: multiplication and division by constants

Example: FIR filters Example: IIR filters

Example: Multimodal sound synthesis (WIP)

Example: floating-point exponentia

Error analysis for dummies (and other proof assistants)

Example: fixed-point sine/cosine

Example: floating-point sums and sums of products

The universal bit heap

Conclusion

## Big picture

#### The part that I don't understand:

- finite element decomposition of a noisy object (e.g. a bell)

- physics simulation to get its resonnant frequencies with their attenuations

#### The part that I more or less understand:

- build a biquad filter for each frequency

- sum them all together to simulate the sound of the noisy object

#### The big picture in picture

https://ccrma.stanford.edu/~jos/filters/Decay\_Time\_Q\_Periods.html

## Resonating filters with slow decay time have high WCPGs

From the bell model in the FAUST distribution:

| i  | $a_1$        | $a_2$        | $\langle\!\langle \mathcal{H}  angle\! angle_i$ | $\langle\!\langle \mathcal{H}_\delta \rangle\!\rangle_i$ |

|----|--------------|--------------|-------------------------------------------------|----------------------------------------------------------|

| 0  | -1.99510896  | 0.999985754  | 1.79e5                                          | 1.29e6                                                   |

| 1  | -1.99504113  | 0.999985695  | 1.79e5                                          | 1.27e6                                                   |

| 2  | -1.98264325  | 0.999980509  | 1.31e5                                          | 4.98e5                                                   |

|    |              |              |                                                 |                                                          |

| 25 | -1.85236752  | 0.999858916  | 1.81e4                                          | 2.40e4                                                   |

|    |              |              |                                                 |                                                          |

| 47 | -1.42887342  | 0.7367661    | 9.78                                            | 8.59                                                     |

| 48 | -0.351596594 | 0.0449641831 | 2.71                                            | 1.45                                                     |

- For a bell actioned with a hammer, do we need to consider WCPG?

- ... and for a violin string?

- Audible zombies when using low precisions.

## And the work in progress is

• To build a FloPoCo operator that builds the hardware for all this.

## **Example: Low-precision logarithmic neuron**

Intro: arithmetic operators

FloPoCo, the user point of view

Example: fixed-point functions

Example: multiplication and division by constant

Example: FIR filters

Example: Multimodal sound synthesis (WIP)

Example: Low-precision logarithmic neuron

Example: floating-point exponentia

Error analysis for dummies (and other proof assistants

Example: fixed-point sine/cosine

Example: floating-point sums and sums of products

The universal bit heap

Conclusion

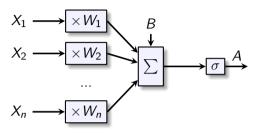

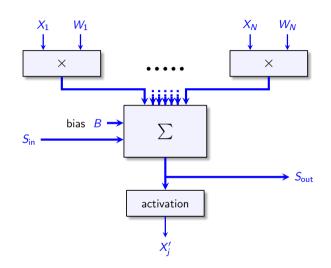

#### Perceptron artificial neuron model

**X**: input vector, **W**: weight vector, *B*: bias,  $\sigma$ : activation function Output *A* of the neuron defined by:

$$A = \sigma(\mathbf{W} \cdot \mathbf{X} + B)$$

#### What precision should a neuron use?

#### Current consensus

- 8-bit integers are good enough for weights and activations

- (if higher precision is used for internal computations)

- 1-bit representations (binary and ternary networks)

- require more layer and specific training

- entail loss of application-level accuracy

Is there some space in between?

- data on 3 to 6 bits ?

- (incidentally, this would be a very good match to LUT-based FPGAs)

Proposed approach: use ad-hoc logarithmic formats

Bones 2009

## Logarithmic Number System

#### Instead of encoding a real value X, encode its logarithm.

Unfortunately log(X) is only defined for X > 0. To represent  $X \in \mathbb{R}$ , we will need

- a sign bit  $s_x$  for the sign of X,

- L<sub>X</sub> ≈ log(|X|) encoded in some signed fixed point format

itself signed: L<sub>X</sub> > 0 ⇐⇒ X > 1

"A kind of floating-point where you only have the exponent, and it is fractional"

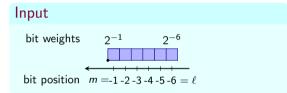

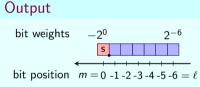

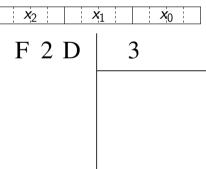

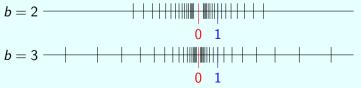

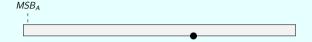

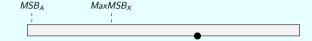

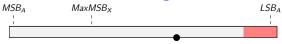

# The MSB and LSB of a LNS representation

$$(m,\ell)=(2,-2)$$

$L_X=$   $x_2$   $x_1$   $x_0$   $x_{-1}$   $x_{-2}$

Adding one bit to the LSB doubles the number of representable values, with the same range.

$$(m,\ell) = (2,-3) \qquad L_X = \begin{bmatrix} x_2 & x_1 & x_0 & x_{-1} & x_{-2} & x_{-3} \\ & & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & & \\ & & \\ & & & \\ & & & \\ & & & \\ & & \\ & & & \\ & & \\ & & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & & \\ & \\ & & \\ & & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ & \\ &$$

Adding one bit to the MSB increases the range, and also reduces the gap around zero.

$$(m,\ell) = (3,-2)$$

$L_X = \begin{bmatrix} x_3 & x_2 & x_1 & x_0 & x_{-1} & x_{-2} \\ x_3 & x_2 & x_1 & x_0 & x_{-1} & x_{-2} \end{bmatrix}$

0 1

### LNS arithmetic

Multiplication turns into addition

$$\log(X\times W) = \log(X) + \log(W)$$

And it is exact! (fixed-point addition may overflow, but no rounding)

### LNS arithmetic

Multiplication turns into addition

$$\log(X\times W) = \log(X) + \log(W)$$

- And it is exact! (fixed-point addition may overflow, but no rounding)

- Division and square root similarly cheap (no use here)

#### LNS arithmetic

Multiplication turns into addition

$$\log(X\times W)=\log(X)+\log(W)$$

- And it is exact! (fixed-point addition may overflow, but no rounding)

- Division and square root similarly cheap (no use here)

- Addition turns into a nightmare

$$\log(X+Y) = \log\left(X\times\left(1+\frac{Y}{X}\right)\right) = \log(X) + \log\left(1+b^{\log(Y)-\log(X)}\right)$$

- one subtraction to compute  $Z = \log(Y) \log(X)$

- evaluation of the ugly function  $\log (1 + b^Z)$

- another addition

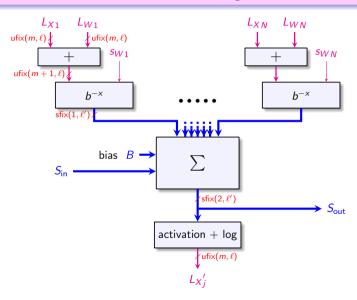

### Reference ad-hoc linear domain implementation

We unroll a neuron:

$$B + \sum_{i} (W_i \times X_i)$$

(it unlocks some optimizations in the  $\boxed{\sum}$  box)

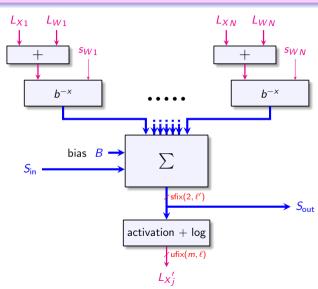

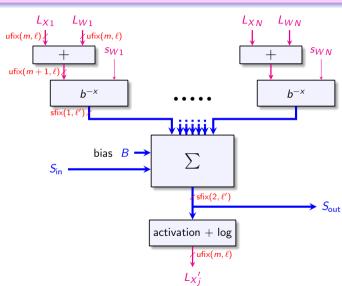

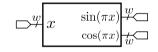

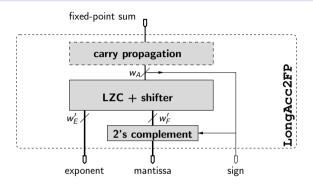

# Proposed design

logarithmic data linear data

# Proposed design

F. de Dinechin

logarithmic data

linear data

# Key ideas

- ullet Leverage LNS to replace imes by +

- Dodge the complexity of accumulating in LNS

- Parametric design to experiment with application-level accuracy

- Merge linear to log conversion with activation function table

- Leverage FPGA LUT architecture to tabulate ugly functions

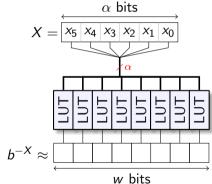

# Cost of tabulating $b^{-x}$ (or any function) in an FPGA

The FPGA basic logic element: an  $\alpha$ -input Look-Up Table

$$\xrightarrow{\alpha}$$

LUT

- universal logic gate (any truth table of  $\alpha$  bits)

- $\alpha \in \{4, 5, 6\}$  these days, depending on vendor and generation

# Cost of tabulating $b^{-x}$ (or any function) in an FPGA

The FPGA basic logic element: an  $\alpha$ -input Look-Up Table

$$\xrightarrow{\alpha}$$

LUT  $\xrightarrow{1}$

- ullet universal logic gate (any truth table of lpha bits)

- $\alpha \in \{4, 5, 6\}$  these days, depending on vendor and generation

Therefore, a table of  $\alpha$  in bits and w out bits costs w FPGA LUTs:

Input size  $\alpha$  is FPGA soft spot! For input sizes larger than  $\alpha$ , cost grows exponentially.

# Other advantages of plain tabulation

- As accurate as your output format allows

- no approximation error

- one single rounding error

- Output size can be larger than input size

- cost grows only linearly with output size

- this is what enables accurate summation

- It works for any function

- No reason why 2 should be the best b

- Activation: Gaussian ReLU or sigmoid for the same cost

- Oh, and it is simple to program and use.

#### Only condition: keep our data format really, really small!

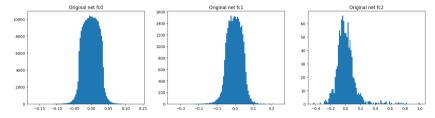

# Weight distribution observations

- Looks like a normal distribution

- $|W| \le 1$

- $|X| \le 1$  ?

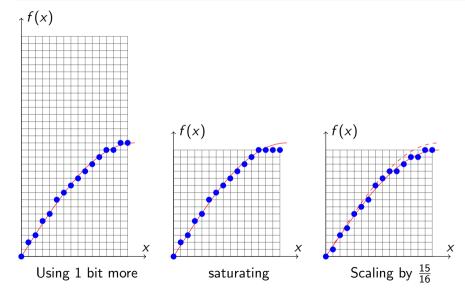

## Every bit matters, in particular sign bits

- If  $|X| \le 1 \implies \log(|X|) \le 0$

- •

- We can decide that  $L_X = \lfloor -\log(|X|) \rceil$  instead of  $L_X = \lfloor \log(|X|) \rceil$

- encoding  $L_X$  as an unsigned fixed-point number effectively saves 1 bit!

- How to ensure  $X \le 1$  and  $W \le 1$ ?

- For the weights: it is OK without retraining (saturate the few large values to 1)

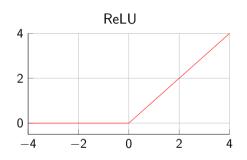

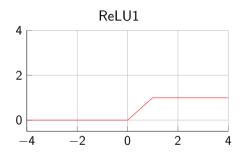

- For the activations: just use ReLU1 (or any function that maxes at 1)

### Every bit matters, and activation functions may help

Now  $X \leq 1!$ Also  $X \geq 0$ , we can drop  $s_X$  as well Now  $^{\lg}X = (z_X, L_X)$  and  $^{\lg}W = (s_W, z_W, L_W)$

## Every bit matters, in particular zero bits

Now

$$^{\lg}X=(z_X,L_X)$$

and  $^{\lg}W=(s_W,z_W,L_W)$

What happens if we drop those bits  $z_X$  and  $z_W$ ?

• 0 is no longer representable

It should be very very bad, as zero is the most common value

both for weights and activations.

#### Yet another trick

Let us call Z the largest possible value of  $L_X$

(which corresponds to the smallest representable value of  $X = 2^{-L_X}$ ).

If Z is rounded to 0 by the  $b^{-X}$  block, then the same holds for  $Z + L_W$ ,  $\forall L_W$

Then Z effectively represents a zero activation.

(the same holds for weights)

So we do not care that we cannot represent zero, and we can drop both zero bits.

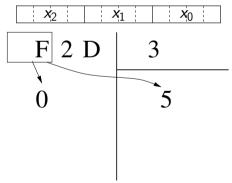

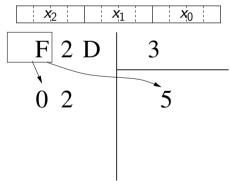

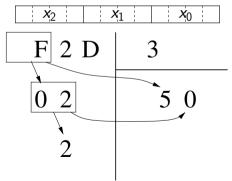

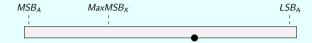

# Summary of "every bit matters": ${}^{\lg}X$ and ${}^{\lg}W$

Logarithmic representation for inputs and product (here for MSB m=2 and LSB  $\ell=-1$ )

binary weight

$$2^3$$

$2^2$   $2^1$   $2^0$   $2^{-1}$

$$|gW = -\lfloor \log_b |W| \rceil = \boxed{w_2 \quad w_1 \quad w_0 \quad w_{-1}} \quad s_W$$

$$|gX = -\lfloor \log_b X \rceil = \boxed{x_2 \quad x_1 \quad x_0 \quad x_{-1}}$$

$$|gP = -\lfloor \log_b |P| \rceil = \boxed{p_3 \quad p_2 \quad p_1 \quad p_0 \quad p_{-1}} \quad s_W$$

## Back to the design

### Simulation setup

- pytorch to evaluate the classification accuracy

- FloPoCo to describe the architecture

- Vivado to synthesize our design and evaluate the area

Exhaustive exploration of the design space for MNIST,

then targetted experiments on a larger CIFAR10.

### Accuracy experiments on MNIST

- Training standard (784, 300, 100, 10) MLP in full precision with pytorch: 98.03% accuracy on test set

- Conversion to LNS and evaluate accuracy on the test set again

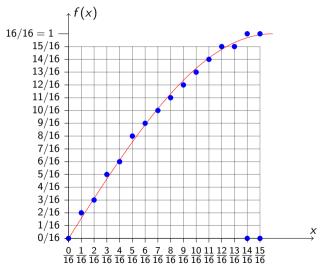

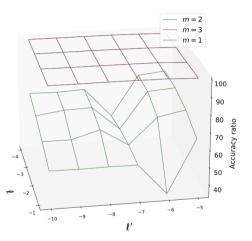

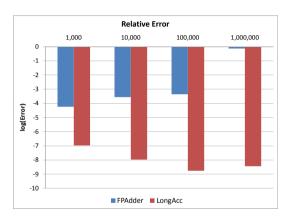

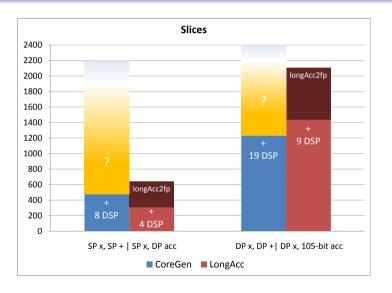

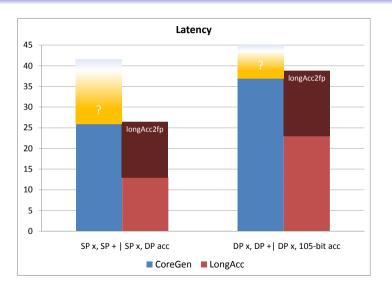

# Accuracy experiments on MNIST

# Accuracy experiments on MNIST

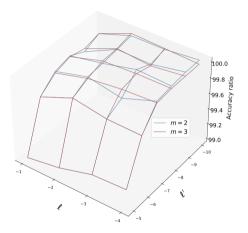

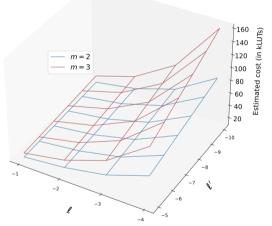

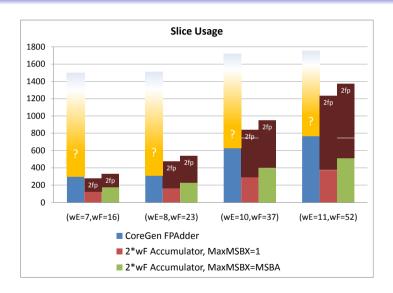

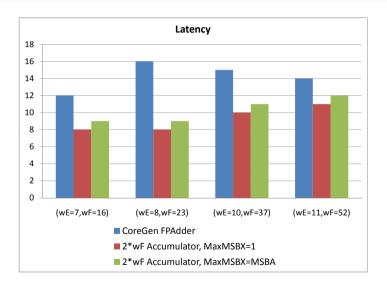

### Cost of the MNIST architecture

As expected, exponential in  $\ell$ , linear in  $\ell'$

### CIFAR10

Take a pre-trained network, and convert it to LNS VGG-like network layer architecture:

| layer index | layer type                   |

|-------------|------------------------------|

| (1)         | LNSConv(3, 128) + ReLU1()    |

| (2)         | LNSConv(128, 128) + ReLU1()  |

| (3)         | MaxPool2d(2,2)               |

| (4)         | LNSConv(128, 256) + ReLU1()  |

| (5)         | LNSConv(256, 256) + ReLU1()  |

| (6)         | MaxPool2d(2,2)               |

| (7)         | LNSConv(256, 512) + ReLU1()  |

| (8)         | LNSConv(512, 512) + ReLU1()  |

| (9)         | MaxPool2d(2,2)               |

| (10)        | LNSConv(512, 1024) + ReLU1() |

| (11)        | MaxPool2d(2, 2)              |

#### Results are similar for CIFAR 10

Accuracy and synthesis results for parallel neurons

| benchmark | parameters $(m,\ \ell),\ (1,\ \ell')$ | accuracy ratio | LUT cost     | latency       |

|-----------|---------------------------------------|----------------|--------------|---------------|

| MNIST     | (2, -1), (1, -6)                      | 99.6           | 12491        | 10.3ns        |

| MNIST     | (2, -1), (1, -7)                      | 99.8           | 13790        | 10.9ns        |

| MNIST     | 6-bit linear                          | 99.9           | 36658        | 10.2ns        |

| CIFAR10   | 6-bit linear                          | 96.9           | 51910        | 13.0ns        |

| CIFAR10   | (3, -1), (1, -10)                     | 97.5           | 30632        | 12.8ns        |

| CIFAR10   | (2, -2), (1, -10)*                    | 98.5           | <b>28652</b> | <b>12.4ns</b> |

| CIFAR10   | 8-bit linear                          | <b>99.8</b>    | 83522        | 13.4ns        |

<sup>\*</sup>  $L_X$  on 5 bits,  $L_W$  on 6 bits,  $L_P$  on 7 bits, summation of 12-bit terms.

### Conclusion

Very small logarithmic encoding works for the weights and activations :

- more accurate than standard linear quantization with identical bit-width

- smaller on FPGA than standard linear implementation of similar accuracy

All this was without any form of retraining.

Retraining can only improve accuracy and/or save a few more bits.

#### All this was in base 2

There is absolutely no reason to think that it is the best base.

Another base, another range/accuracy trade-off for the same format.

# **Example: floating-point exponential**

Intro: arithmetic operators

FloPoCo, the user point of view

Example: fixed-point functions

Example: multiplication and division by constants

Example: FIR filters

Example: IIR filters

Example: Multimodal sound synthesis (WIP)

Example: Low-precision logarithmic neuron

Example: floating-point exponential

Error analysis for dummies (and other proof assistants)

Example: fixed-point sine/cosine

Example: floating-point sums and sums of products

The universal bit hear

Conclusion

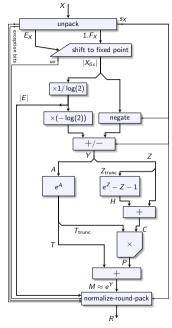

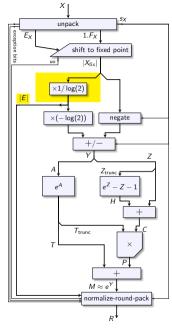

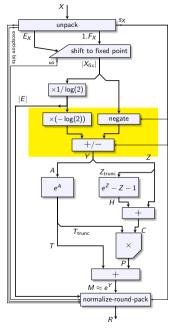

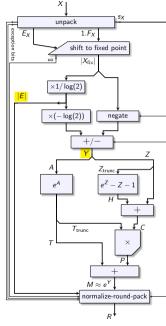

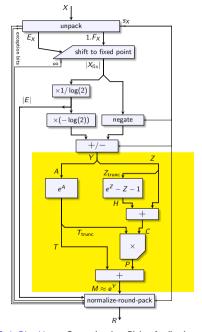

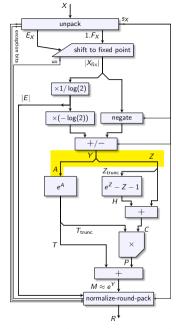

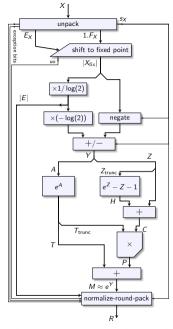

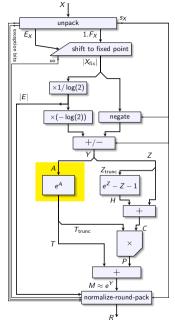

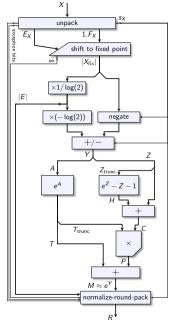

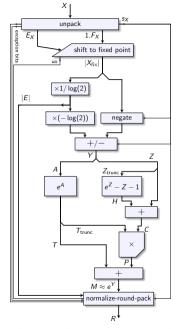

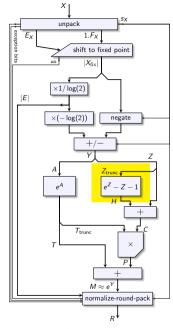

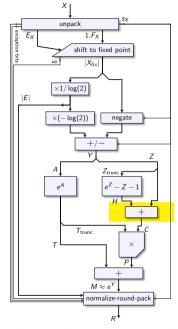

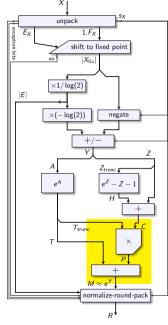

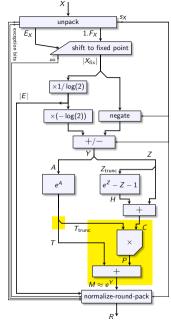

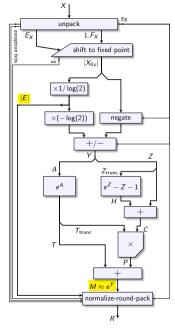

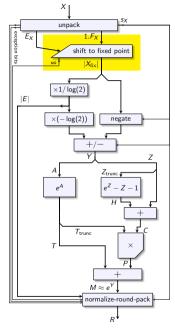

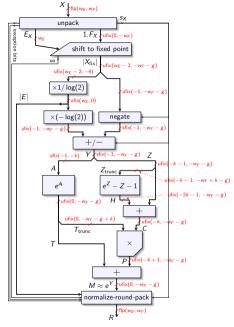

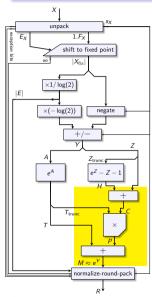

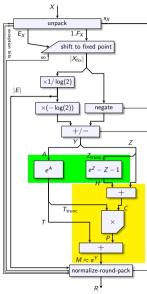

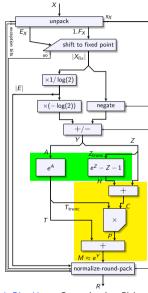

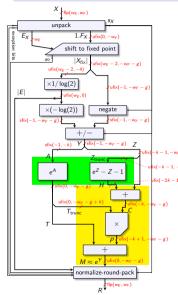

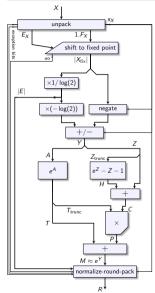

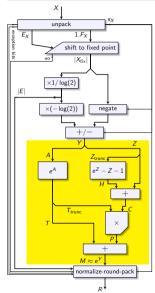

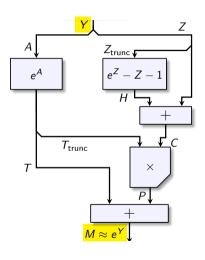

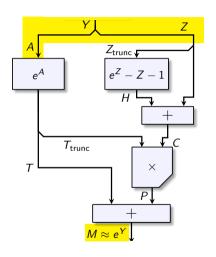

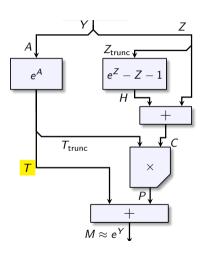

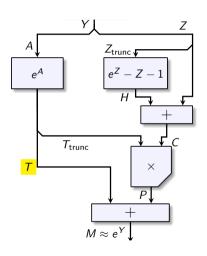

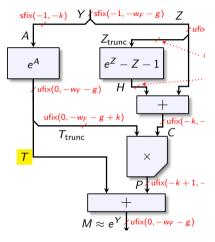

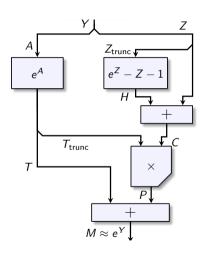

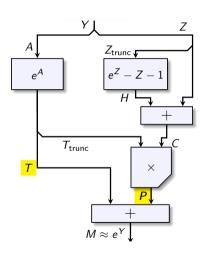

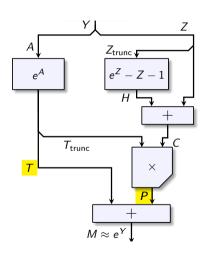

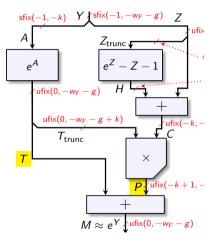

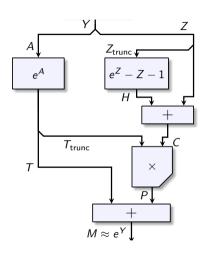

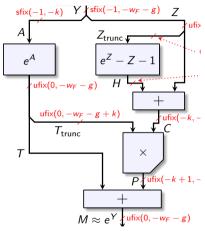

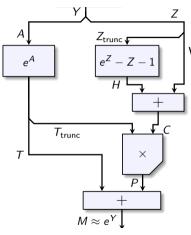

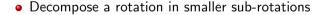

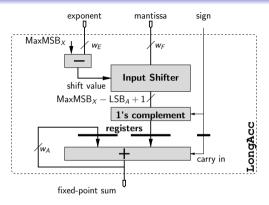

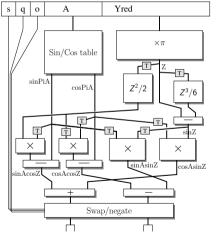

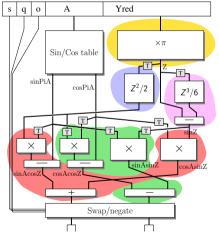

### First, a math proficiency test

### Three identities to remember from our happy school days

$$2^X = e^{X\log(2)} \tag{1}$$

$$e^{A+B} = e^A \times e^B \tag{2}$$

$$e^Z \approx 1 + Z + \frac{Z^2}{2}$$

if Z is small (3)

$$e^X = 2^E \cdot 1.F$$

$$e^X = 2^E \cdot 1.F$$

Compute

$$E \approx \left\lfloor \frac{X}{\log 2} \right

ceil$$

$$e^X = 2^E \cdot 1.F$$

Compute

$$E \approx \left\lfloor \frac{X}{\log 2} \right

ceil$$

then

$$Y \approx X - E \times \log 2$$

.

$$e^X = 2^E \cdot 1.F$$

Compute

$$E \approx \left\lfloor \frac{X}{\log 2} \right

ceil$$

then

$$Y \approx X - E \times \log 2$$

.

Now

$$e^{X} = e^{E \log 2 + Y}$$

$= e^{E \log 2} \cdot e^{Y}$

$= 2^{E} \cdot e^{Y}$

$$e^X = 2^E \cdot e^Y$$

Now we have to compute  $e^Y$  with  $Y \in (-1/2, 1/2)$ .

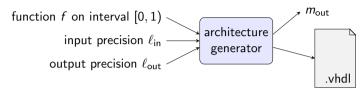

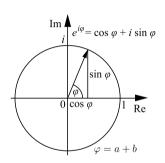

$$e^X = 2^E \cdot e^Y$$

Now we have to compute  $e^Y$  with  $Y \in (-1/2, 1/2)$ .

Split Y:

$$Y = A Z -w_F - g$$

i.e. write

$$Y = A + Z$$

with  $Z < 2^{-k}$

$$e^X = 2^E \cdot e^Y$$

Now we have to compute  $e^Y$  with  $Y \in (-1/2, 1/2)$ .

#### Split Y:

$$Y = \begin{array}{c|cccc} -1 & -k & -w_F - g \\ \hline A & Z & \end{array}$$

i.e. write

$$Y = A + Z$$

with  $Z < 2^{-k}$

so

$$e^Y = e^A \times e^Z$$

$$e^X = 2^E \cdot e^Y$$

$$e^Y = e^A \times e^Z$$

Tabulate  $e^A$  in a ROM

$$e^X = 2^E \cdot e^Y$$

$$e^Y = e^A \times e^Z$$

Evaluation of  $e^Z$ :  $Z < 2^{-k}$ , so

$$e^Z \approx 1 + Z + Z^2/2$$

$$e^X = 2^E \cdot e^Y$$

$$e^Y = e^A \times e^Z$$

Evaluation of  $e^Z$ :  $Z < 2^{-k}$ , so

$$e^Z \approx 1 + Z + Z^2/2$$

Notice that  $e^Z - 1 - Z \approx Z^2/2 < 2^{-2k}$

$$e^X = 2^E \cdot e^Y$$

$$e^Y = e^A \times e^Z$$

Evaluation of  $e^Z$ :  $Z < 2^{-k}$ , so

$$e^Z \approx 1 + Z + Z^2/2$$

Notice that  $e^Z - 1 - Z \approx Z^2/2 < 2^{-2k}$

Evaluate  $e^Z - Z - 1$  somewhow (out of Z truncated to its higher bits only)

$$e^X = 2^E \cdot e^Y$$

$$e^Y = e^A \times e^Z$$

Evaluation of  $e^Z$ :  $Z < 2^{-k}$ , so

$$e^Z \approx 1 + Z + Z^2/2$$

Notice that  $e^Z - 1 - Z \approx Z^2/2 < 2^{-2k}$

Evaluate  $e^Z - Z - 1$  somewhow (out of Z truncated to its higher bits only) then add Z to obtain  $e^Z - 1$

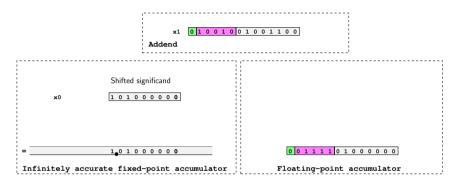

$$e^X = 2^E \cdot e^Y$$

$e^Y = e^A \times e^Z$

Also notice that

$$e^Z = 1.$$

$\overbrace{000...000}^{k-1 \text{ zeroes}} zzzz$

Evaluate  $e^A \times e^Z$  as

$$e^A + e^A \times (e^Z - 1)$$

$$e^X = 2^E \cdot e^Y$$

$e^Y = e^A \times e^Z$

Also notice that

$$e^Z = 1. \overbrace{000...000}^{k-1 \text{ zeroes}} zzzz$$

Evaluate  $e^A \times e^Z$  as

$$e^A + e^A \times (e^Z - 1)$$

(before the product, truncate  $e^A$  to precision of  $e^Z - 1$ )

$$e^X = 2^E \cdot e^Y$$

$e^Y = e^A \times e^Z$

And that's it, we have E and  $e^Y$

$$e^X = 2^E \cdot e^Y$$

$e^Y = e^A \times e^Z$

And that's it, we have E and  $e^Y$  (using only fixed-point computations)

$$e^X = 2^E \cdot e^Y$$

$e^Y = e^A \times e^Z$

And that's it, we have E and  $e^Y$  (using only *fixed-point* computations)

Modern FPGAs also have

#### Modern FPGAs also have

small multipliers with pre-adders and post-adders

#### Modern FPGAs also have

- small multipliers with pre-adders and post-adders

- ... and dual-ported small memories

Modern FPGAs also have

- small multipliers with pre-adders and post-adders

- ... and dual-ported small memories

Single-precision accurate exponential on Xilinx

- one block RAM (0.1% of the chip)

- one DSP block (0.1%)

- ullet < 400 LUTs (0.1%, pprox one FP adder)

to compute one exponential per cycle at 500MHz ( $\sim$  one AVX512 core trashing on its 16 FP32 lanes)

Modern FPGAs also have

- small multipliers with pre-adders and post-adders

- ... and dual-ported small memories

Single-precision accurate exponential on Xilinx

- one block RAM (0.1% of the chip)

- one DSP block (0.1%)

- ullet < 400 LUTs (0.1%, pprox one FP adder)

to compute one exponential per cycle at 500MHz ( $\sim$  one AVX512 core trashing on its 16 FP32 lanes)

$(\sim \text{ one AVX512 core trasning on its 10 FP32 lanes})$

For one specific value only of the architectural parameter k! (over-parameterization is cool)

# Error analysis for dummies (and other proof assistants)

Intro: arithmetic operators

FloPoCo, the user point of view

Example: multiplication and division by constants

Example: FIR filters Example: IIR filters

Example: Multimodal sound synthesis (WIP) Example: Low-precision logarithmic neuron

Example: floating-point exponential

Error analysis for dummies (and other proof assistants)

Example: fixed-point sine/cosine

Example: floating-point sums and sums of products

The universal bit heap

Conclusion

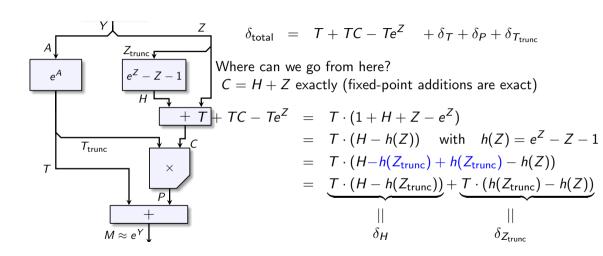

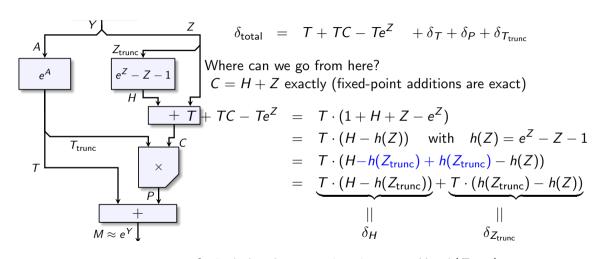

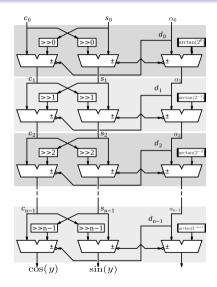

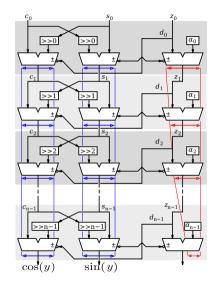

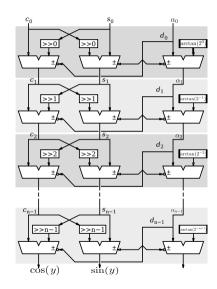

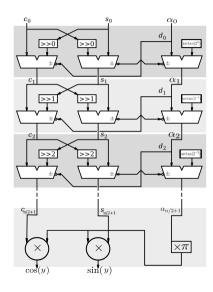

## Computing just right

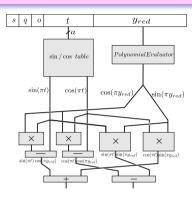

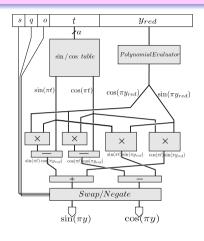

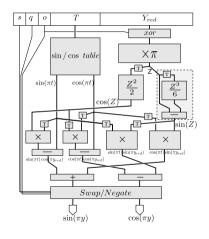

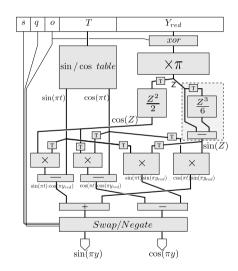

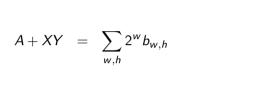

"Error analysis" used to be the kind of things you do to ensure the operator works.

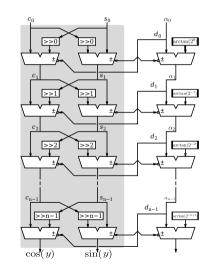

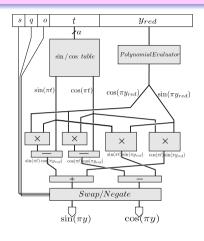

## Computing just right