international atomic energy agency the **abdus salam** international centre for theoretical physics

301/1352-4

#### MICROPROCESSOR LABORATORY SEVENTH COURSE ON BASIC VLSI DESIGN TECHNIQUES

29 October - 23 November 2001

VHDL, ALLIANCE

Nizar ABDALLAH Actel Corporation 955 East Arues Avenue Sunnyvale, CA 94-86-4533 U.S.A.

These are preliminary lecture notes intended only for distribution to participants.

strada costiera, 11 - 34014 trieste italy - tel. +39 040 2240111 fax +39 040 224163 - sci\_info@ictp.trieste.it - www.ictp.trieste.it

#### NIZAR ABDALLAH

#### LABORATOIRE MASI - EQUIPE CAO-VLSI

#### UNIVERSITE PIERRE ET MARIE CURIE (PARIS VI)

4, PLACE JUSSIEU, 75252 PARIS CEDEX 05 FRANCE

Nizar.Abdallah@masi.ibp.fr

33 - 1 44 27 53 99

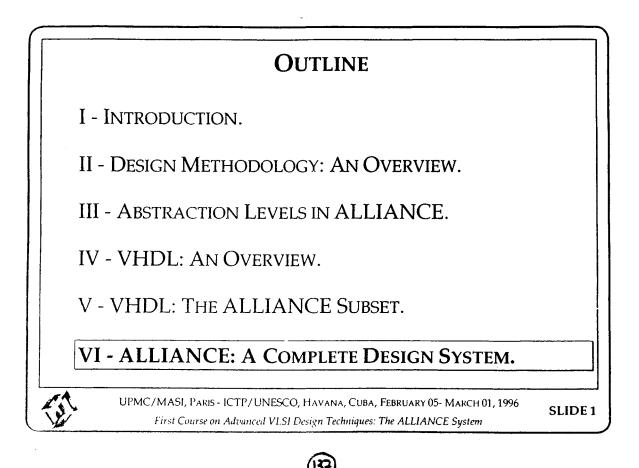

### OUTLINE

- **1** INTRODUCTION

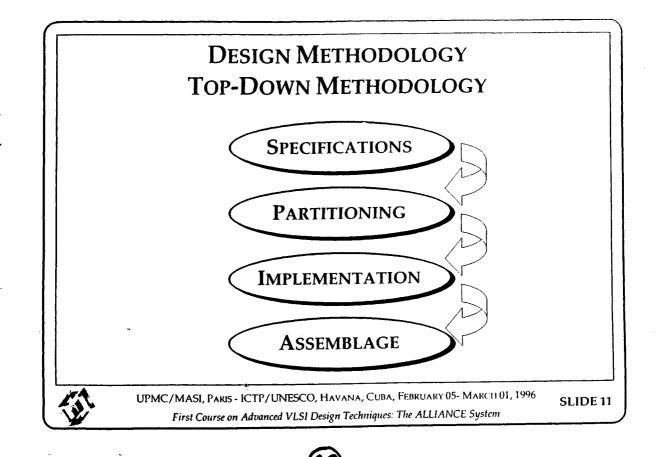

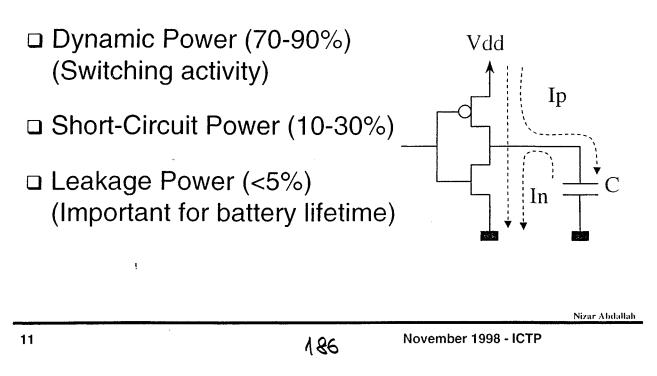

- **II Design methodology:** An Overview

- **III ABSTRACTION LEVELS IN ALLIANCE**

- TV VHDL: A HARDWARE DESCRIPTION LANCUAGE

- Y VHDL: THE ALLIANCE SUBSET

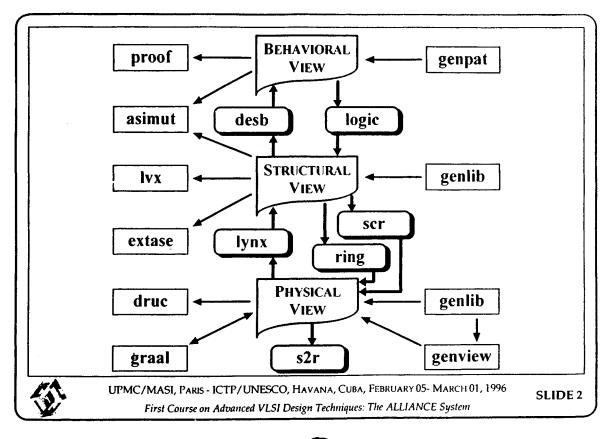

- VI ALLIANCE: A COMPLETE DESIGN SYSTEM

- VII- TODAY'S CHALLENGES IN CAD TOOLS

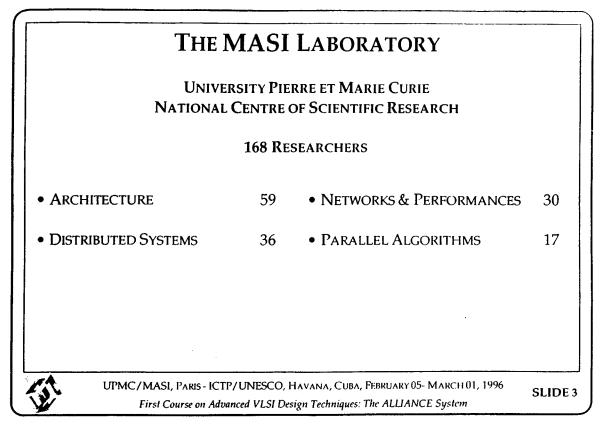

## THE MASI LABORATORY

#### UNIVERSITY PIERRE ET MARIE CURIE NATIONAL CENTRE OF SCIENTIFIC RESEARCH

**168 RESEARCHERS**

ARCHITECTURE59NETWORKS & PERFORMANCES30DISTRIBUTED SYSTEMS36PARALLEL ALGORITHMS17

(8)

(13)

(15

(18)

### (22)

| STEP 2: HOW TO ? (6) |                                                                                                                                                   |         |

|----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------|

|                      | The cutting is guided by:                                                                                                                         |         |

|                      | 5. CAD TOOLS.                                                                                                                                     |         |

| • 1                  | What tools do I have to make my circuit ?                                                                                                         |         |

| EX                   | NO SYNTHESIS TOOLS SO I TRY TO REDUCE THE RAND<br>LOGIC PART.                                                                                     | DOM     |

|                      | UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996<br>First Course on Advanced VLSI Design Techniques: The ALLIANCE System | SLIDE 1 |

### CONCLUSION (2)

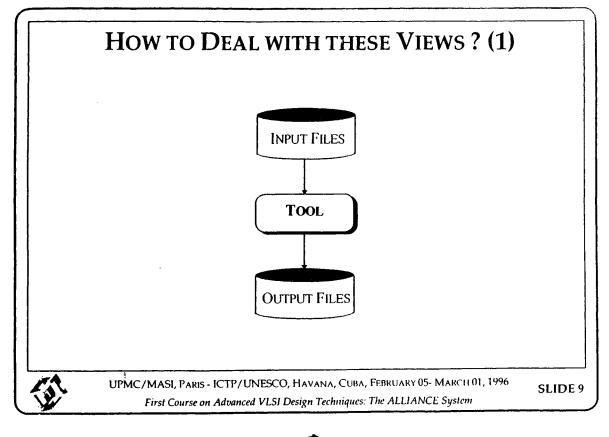

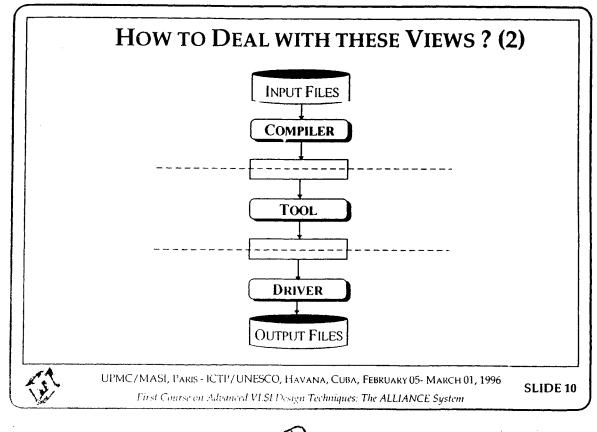

ALL ALONG THE METHODOLOGY, WE HANDLED DIFFERENT VIEWS:

- 1. EQUATIONS.

- 2. NETLISTS.

- 3. LAYOUT.

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996 First Course on Advanced VLSI Design Techniques: The ALLIANCE System

(حت)

**(41)**

### $\Theta$

લ્ડ

(45)

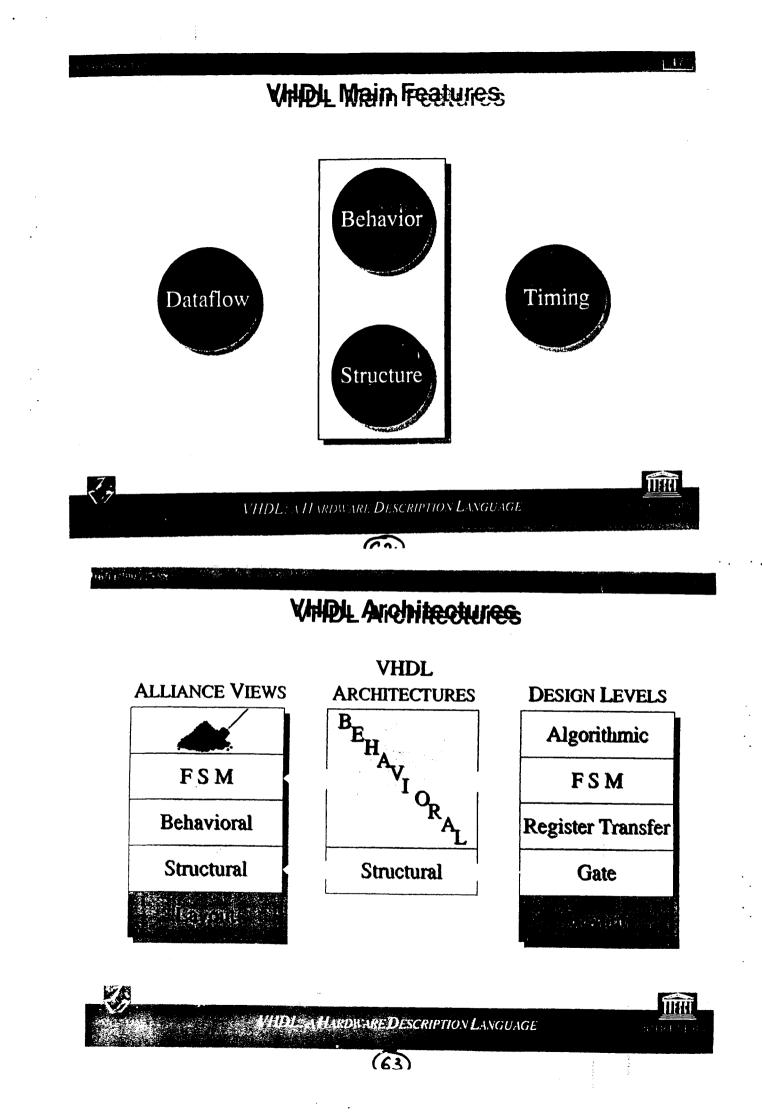

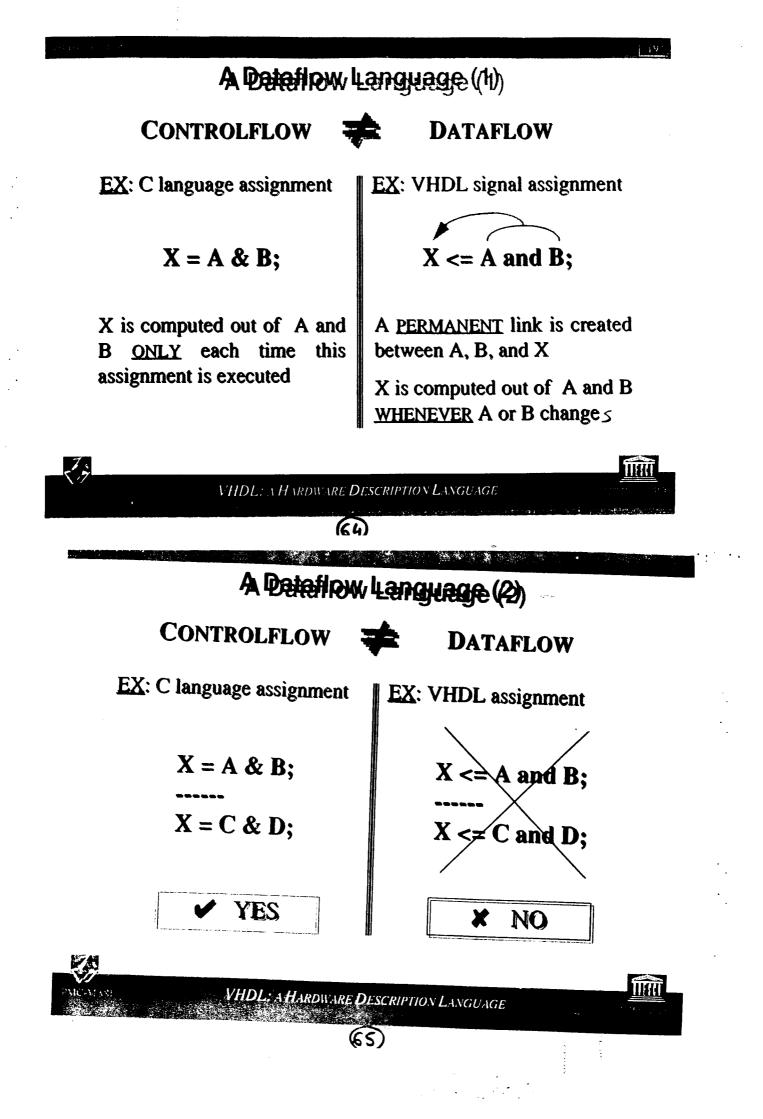

## ONITIFINE

- I INTRODUCTION

- **II DESIGN METHODOLOGY: AN OVERVIEW**

- **III ABSTRACTION LEVELS IN ALLIANCE**

- **IV VHDL: A HARDWARE DESCRIPTION LANGUAGE**

X Different vendors incompatible HDLs

✗ Impossible to verify a whole mixed-system

## History,

- 1981: an Extensive Public Review (DOD)

- 1983: a Request for Proposal

(Intermetrics, IBM, and Texas Instruments)

- 1986: VHDL in the Public Domain

- 1987: a Standard Language <u>VHDL'87</u> (IEEE-1076)

- 1992: a New Standard VHDL'92

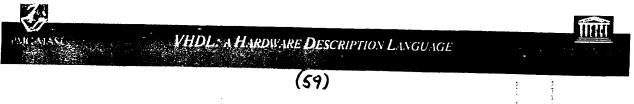

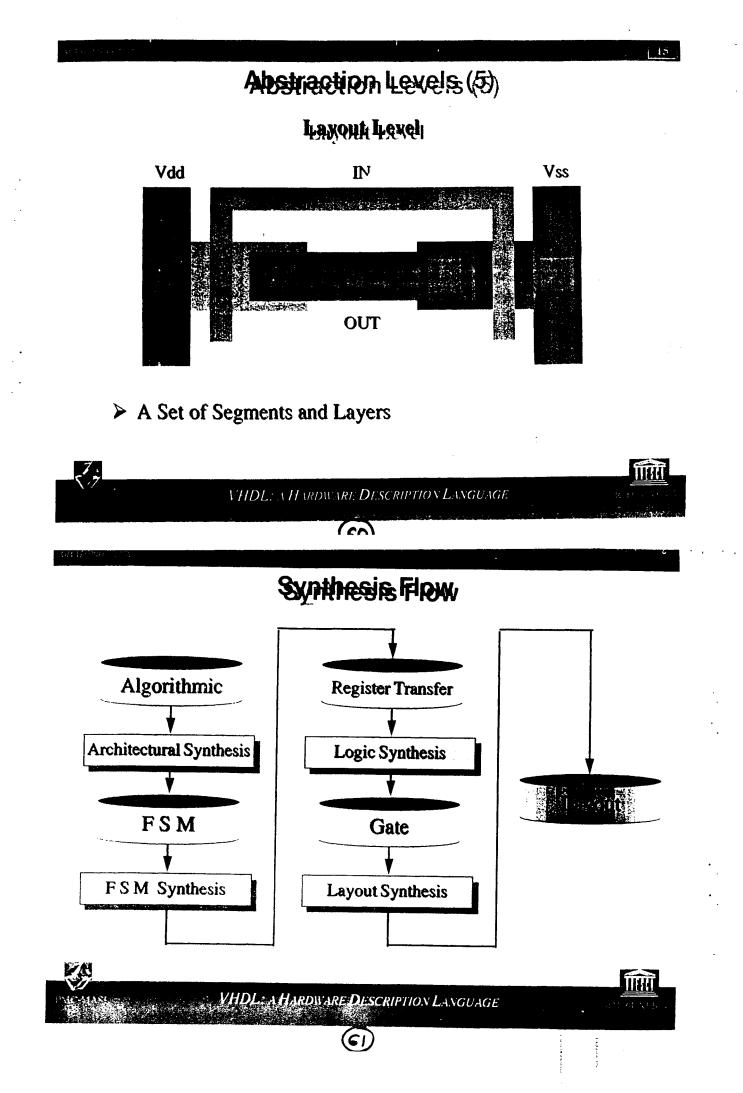

# Abstraction Levels (11)

### Algorithmic Level

- > Very High Abstraction Level

- Functional Interpretation of a Discrete System

- > No Implementation Details

- Sequential Program-Like Description

- > Programmer's Point of View

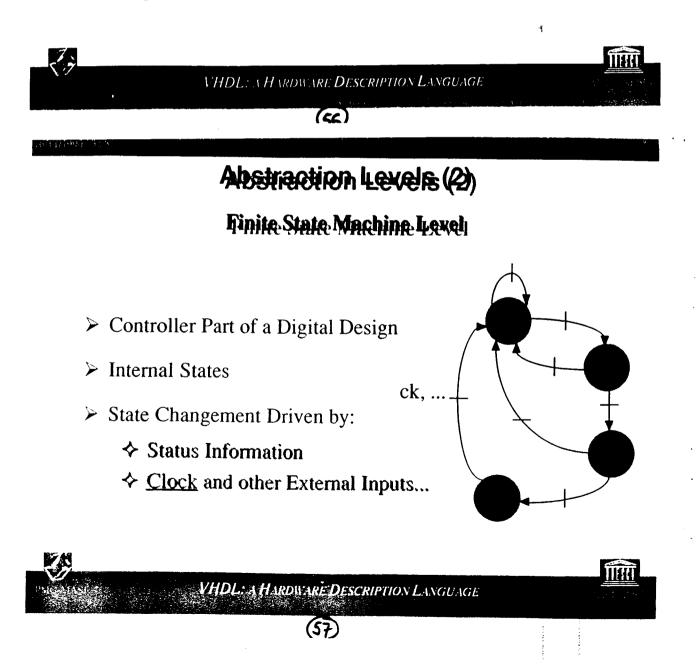

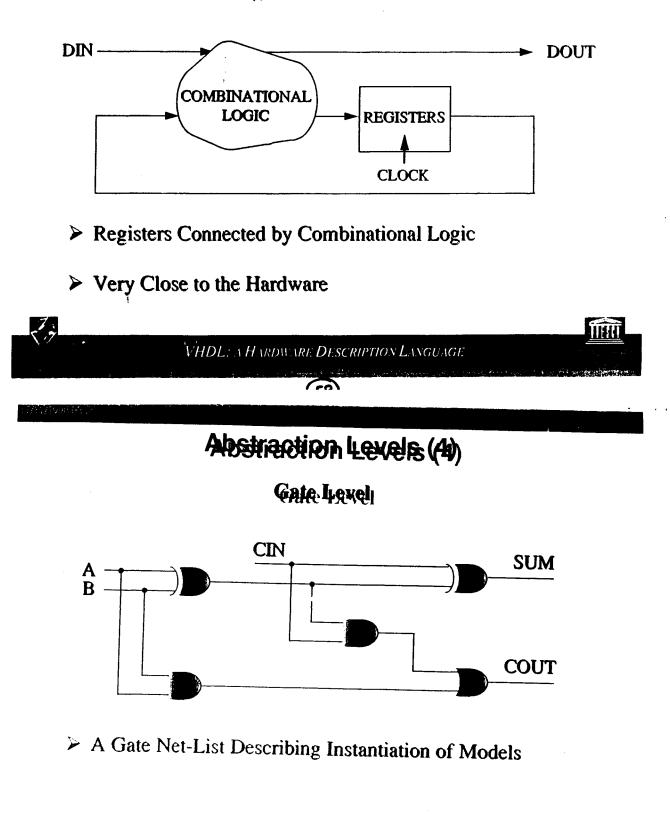

# Abstraction Levels (3)

## Register Transfer Level

(67)

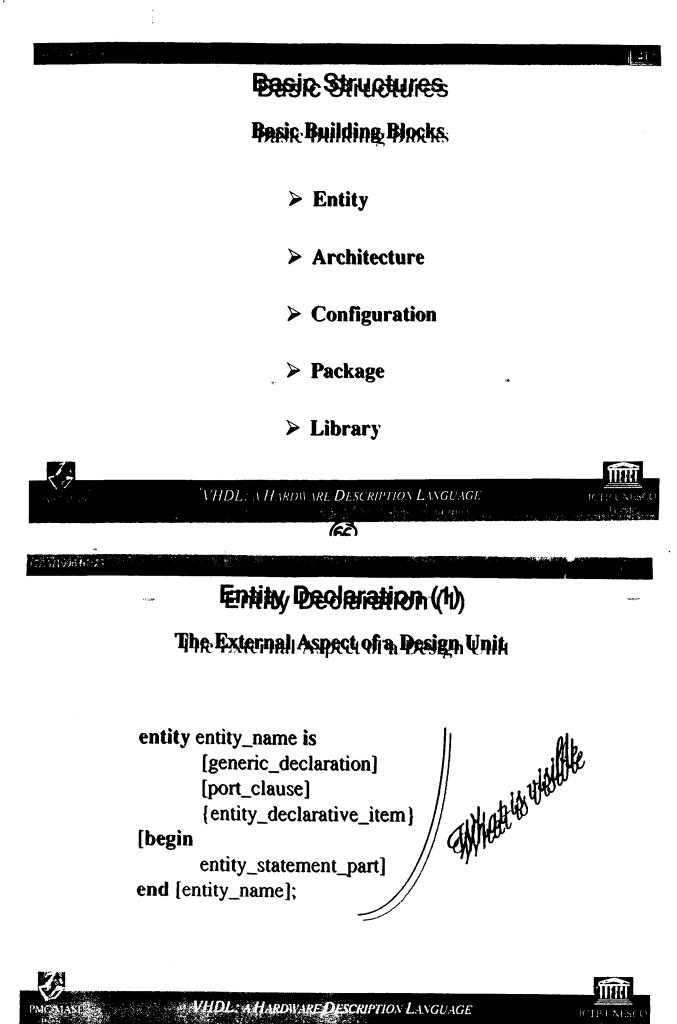

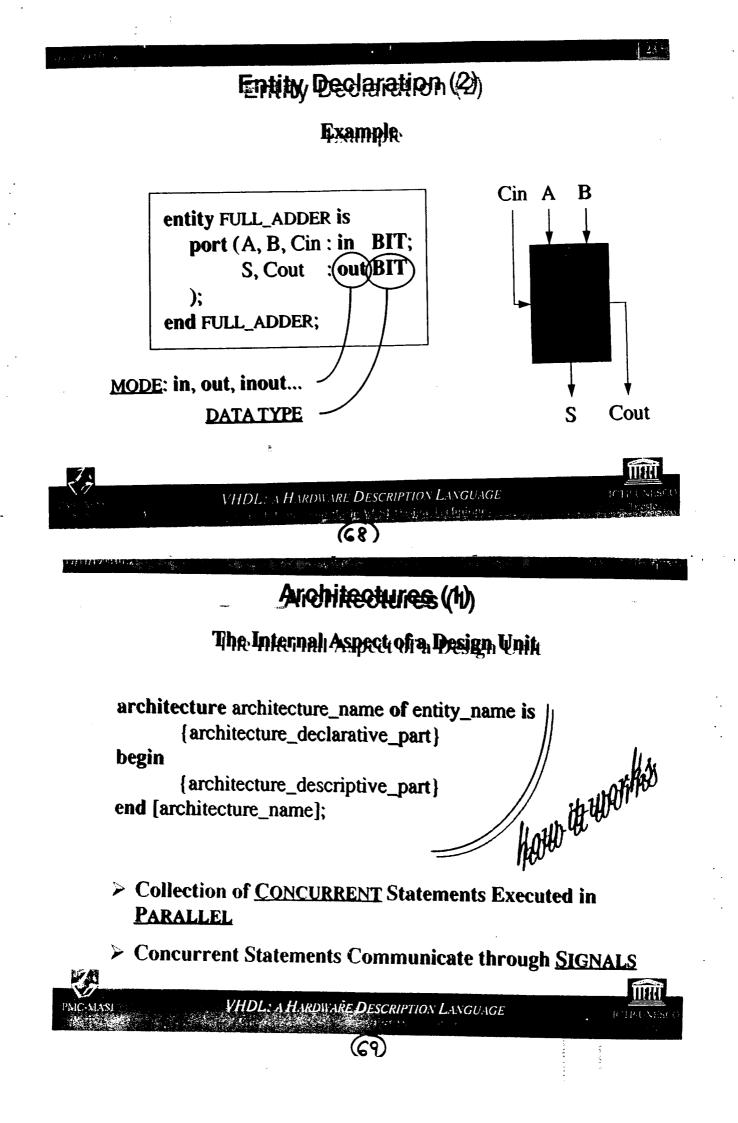

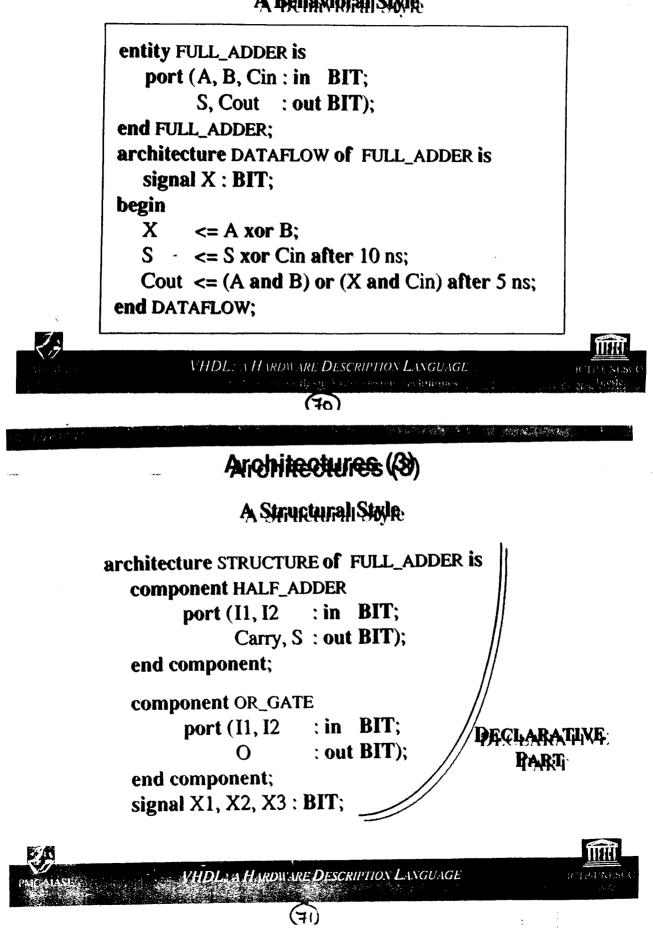

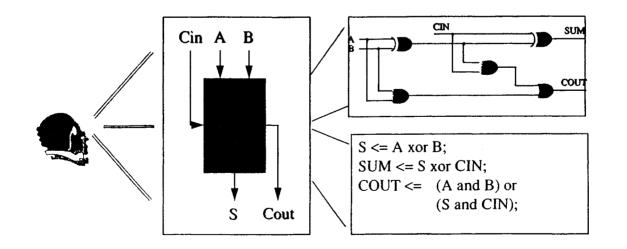

# Arichitectures (2)

A Behavioral Style

#### 21

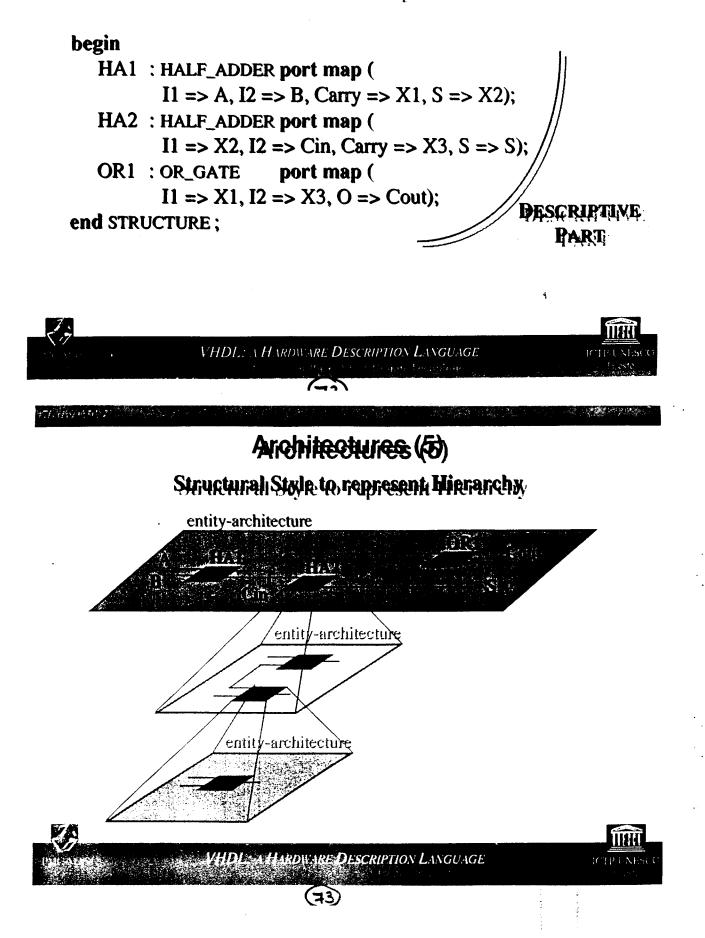

### Arichitectures (A)

#### A Structural Stale

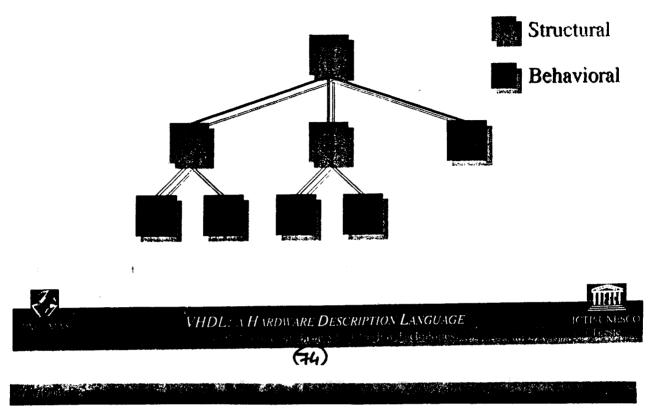

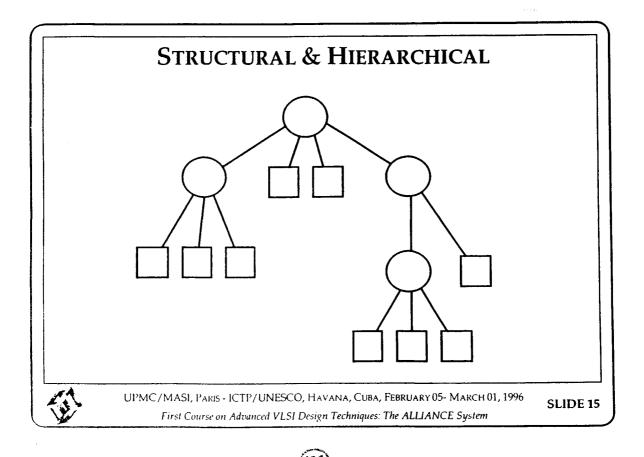

Striuctural & Behavioralina Design Tree.

Anchitectures (7)

entity/architecture: a One to Many Relationship

Specification Inside the Architecture Body

for instantiation\_list: component\_name use binding\_indication;

**use** library\_name.entity\_name [(architecture\_name)];

### > Binding a couple "entity/architecture" to each instance

# Configurations (2)

Peclaration as a Separate Design Unit

configuration configuration\_name of entity\_name is

for { architecture | component } binding\_indication;

end [configuration\_name];

> Can be compiled separately and stored in a library

> It defines a configuration for a particular entity

31

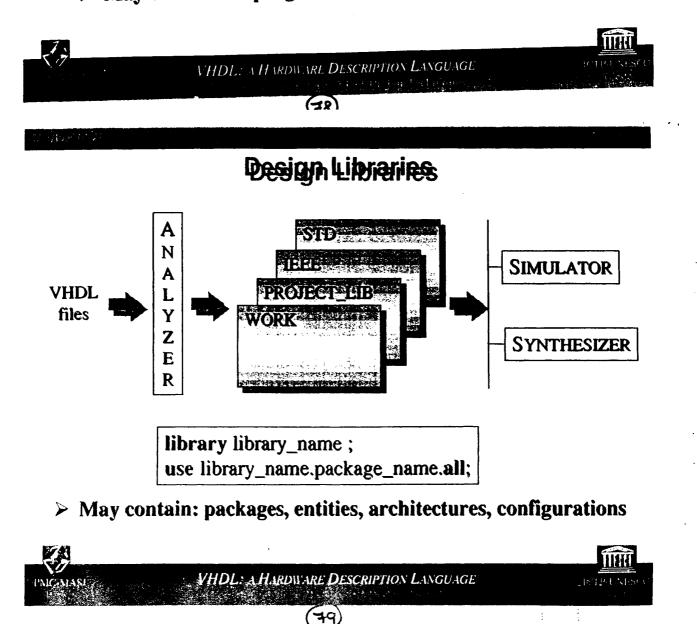

### Peckages

### Global Design Unit

package package\_name is

{package\_declarative\_item}

end [package\_name];

package body package\_name is

{package\_body\_declarative\_item}

end [package\_name];

# Same declarations visible by a number of design entities

# May contain subprograms, components, signals, ...

ALASL

. . . . · . · .

# (P-UKESC)

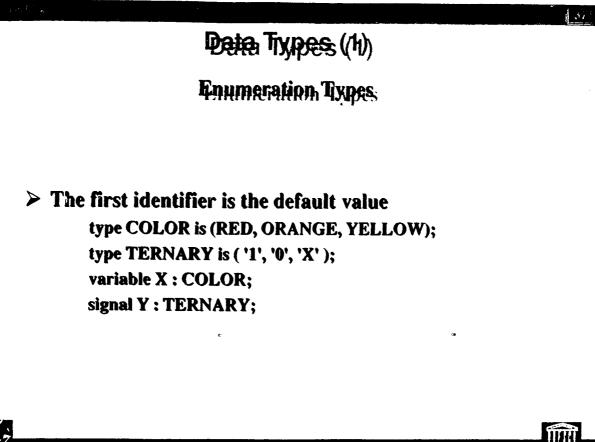

# Data Objects ((h))

Three Classes

#### $\succ$ Constants

Initialized to a specific value and <u>never</u> modified constant MSB : INTEGER := 5;

> Variables

Used to hold temporary data

♦ <u>Only</u> used within processes & subprograms

variable DELAY : INTEGER range 0 to 15 := 0;

|           | VHDL: A HARDWARE DESCRIPTION LANGUAGE                |

|-----------|------------------------------------------------------|

| 5 MS64129 |                                                      |

|           | Data Objects (2)                                     |

|           | Three Classes                                        |

| > Signa   | als                                                  |

| •         | Used to communicate between processes                |

|           | ♦ When declared in a package : <u>Global Signals</u> |

|           | Also declared within entities, blocks, architectures |

|           | Can be used but not defined in processes and         |

|           | subprograms                                          |

|           | signal CLK : BIT;                                    |

|           |                                                      |

|           |                                                      |

VHDL: A HARDWARE DESCRIPTION LANGUAGE

(8)

| 5.7         |                                                                       |                                     |

|-------------|-----------------------------------------------------------------------|-------------------------------------|

|             | VHDL: A HARDWARE DESCRIPTION LANGUAGE                                 | ICTP-UNESCO<br>Foloster<br>Foloster |

|             | <b>6</b> .                                                            |                                     |

|             | Dete Trypes (2)                                                       | -6.23*                              |

|             | Integer Types                                                         |                                     |

|             |                                                                       |                                     |

| <u>ь</u> ть | a range must be creatified                                            |                                     |

|             | e range must be specified                                             |                                     |

| > No        | logical operations on integer<br>type MEMORY_SIZE is range 1 to 2048; |                                     |

|             |                                                                       |                                     |

|             |                                                                       |                                     |

|             |                                                                       |                                     |

|             |                                                                       | Î                                   |

| PHIC-MASSI  | VHDL: A HARDWARE DESCRIPTION LANGUAGE                                 | ICTP4 XESC                          |

(83)

\*P \* 1

### **Dete Types** (3) Predefined: VHD4, Data Types IFFF 1076-1987 Standard: Package

- > **BOOLEAN** : (false, true)

- > BIT : ('0', '1')

- > CHARACTER

- INTEGER : range -2 147 483 647 to +2 147 483 647

- > NATURAL : Subtype of INTEGER (Non Negative)

- > **POSITIVE : Subtype of INTEGER (positive)**

- > BIT\_VECTOR : array of BIT values

- **> STRING : array of CHARACTERS**

- > REAL : range -1.0E+38 to +1.0E+38

- > TIME : Physical type used for simulation

Array Types

> Constrained Array

type VEC\_64 is array (0 to 63) of INTEGER; variable S : VEC\_64; variable S1 : INTEGER; S1 := S (1);

#### > Unconstrained Array type BIT\_VECTOR is array (POSITIVE range <>) of BIT; signal S : BIT\_VECTOR (4 downto 0);

#### > Multiple Dimentional Arrays type TWO\_D is array (0 to 7, 0 to 3) of INTEGER;

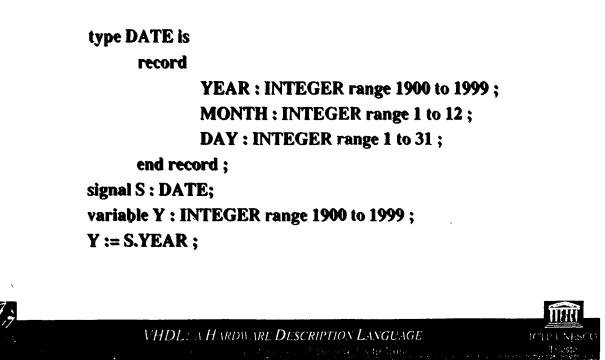

## Pate Types (5)

Record Tixpes.

#### (86)

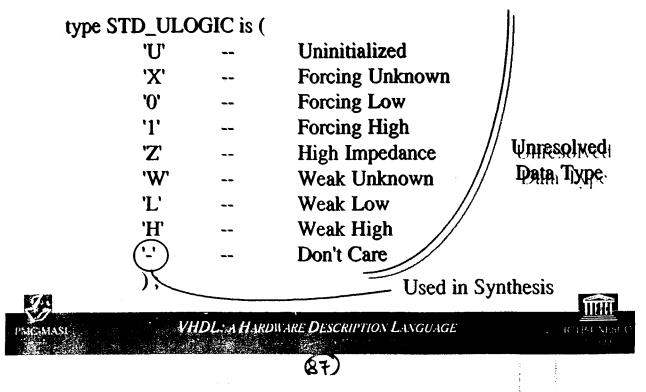

**Dette Trypes (G)** STID\_4.0GHC Date Trypes; IEEE 1164-1993 Standard 4.0gic Package

41

### **Dete:** Types (77) STD\_40GKC Date: Types IEEE 4464-1993: Standard: 498ic Backage

### > STD\_LOGIC : Resolved (Resolution Function provided)

#### > STD\_LOGIC\_VECTOR

#### > STD\_ULOGIC\_VECTOR

Also,

- > FILE : Useful for RAM Values or Stimuli Files

- > ACCESS : Like "pointers" in High Level Languages

- > TEXT : FILE of STRING (TEXTIO package)

- LINE : access STRING (TEXTIO package)

# Subbypes

Subsets of Other Tixpes

- > To Insure Valid Assignments

- Inherit All Operators and Subprograms from the Parent Type

subtype DIGIT is INTEGER range 0 to 9;

4.

### **Operands (3)** Attributes Names A Pate Attached to VHPL Objects:

- > S'LEFT : Index of the leftmost element of the data type

- > S'RIGHT : Index of the rightmost element of the data type

- > S'HIGH : Index of the highest element of the data type

- > S'LOW : Index of the lowest element of the data type

- > S'RANGE : Index range of the data type

- > S'REVERSE\_RANGE : Reverse index range

- > S'LENGTH : Number of elements of an array

|               | VHDL: A HARDWARE DESCRIPTION LANGUAGE ACTIVATION LANGUAGE |

|---------------|-----------------------------------------------------------|

| i 🌮 ny too ka |                                                           |

|               | Operands (4)                                              |

|               | Attributes Names                                          |

|               | A Data Attached to VHD4 Signals                           |

| ¥             | S'EVENT : A change value at the current simulation time   |

| ¥             | S'STABLE : No change value at the current simulation time |

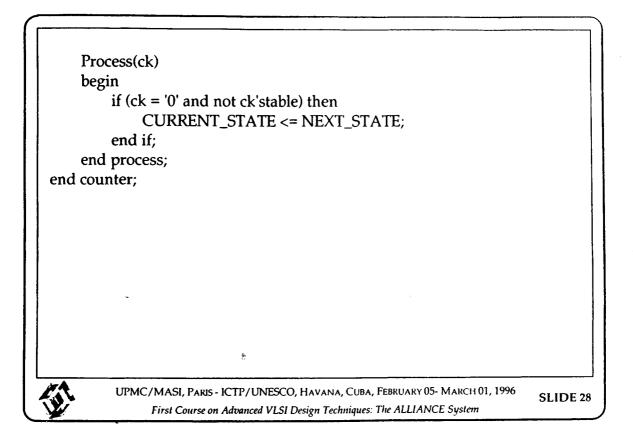

|               | if (CK = 0 and not CK'STABLE)                             |

| June 1        | •••••                                                     |

| 807°°- 880    |                                                           |

| 1             |                                                           |

VHDL; A HARDWARE DESCRIPTION LANGUAGE

(95)

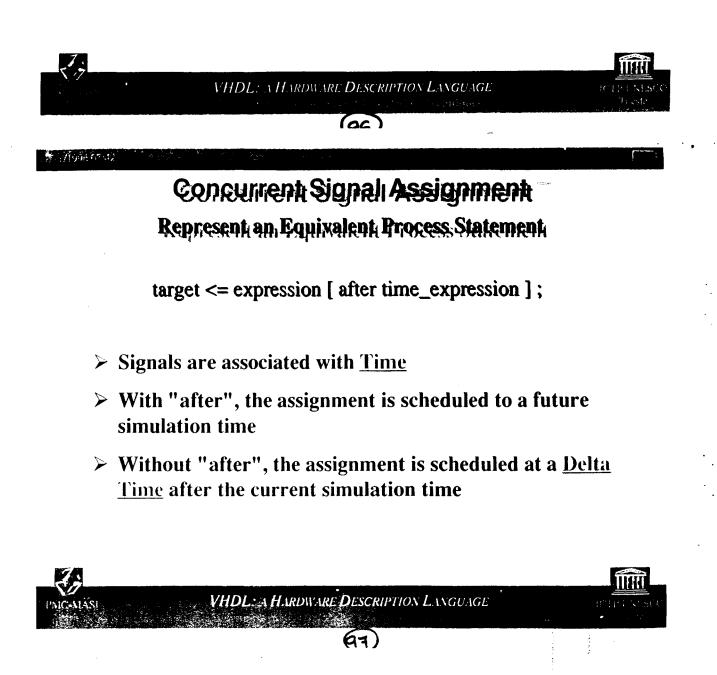

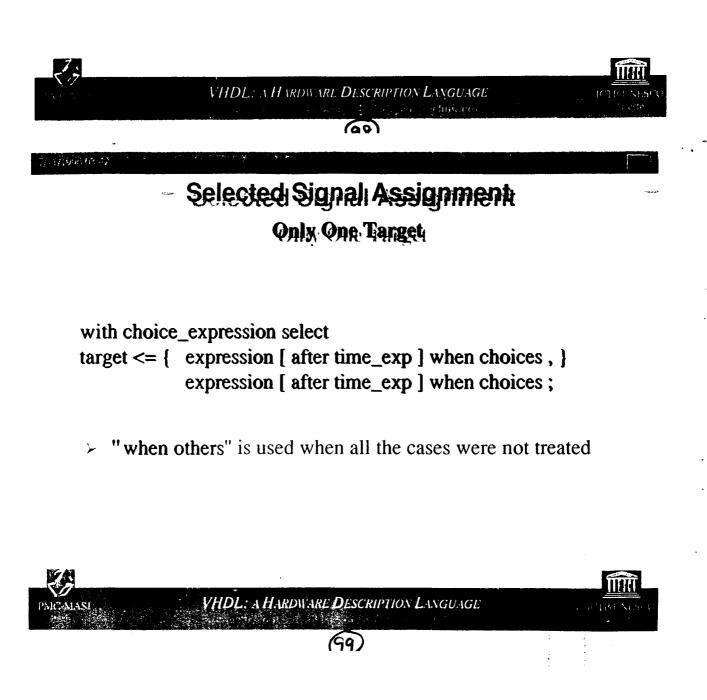

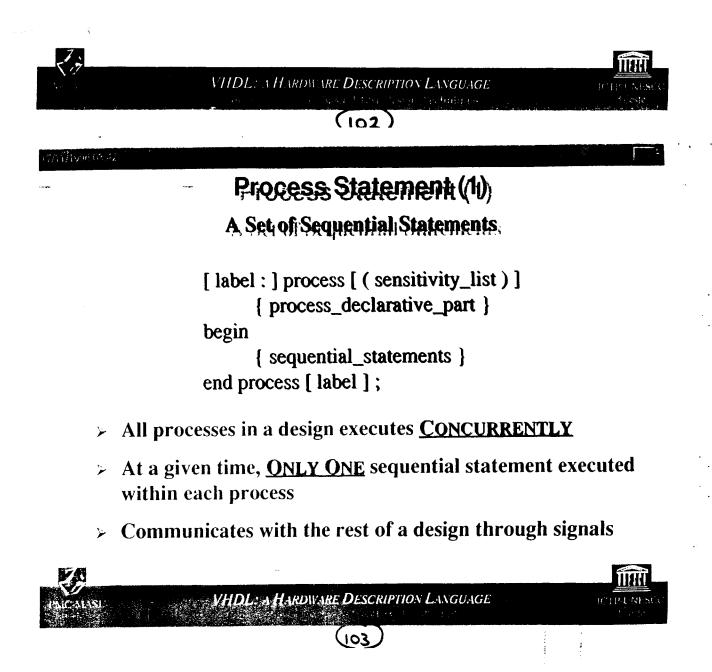

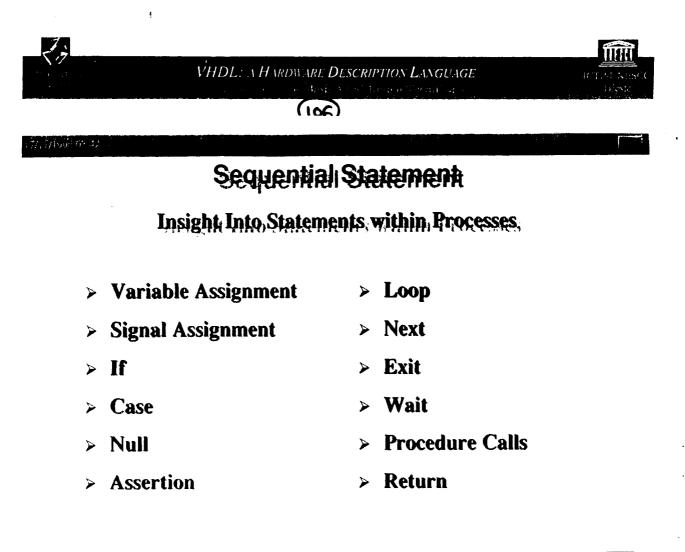

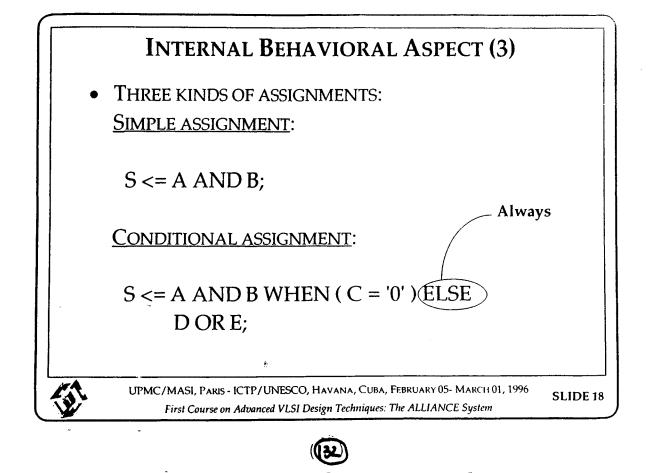

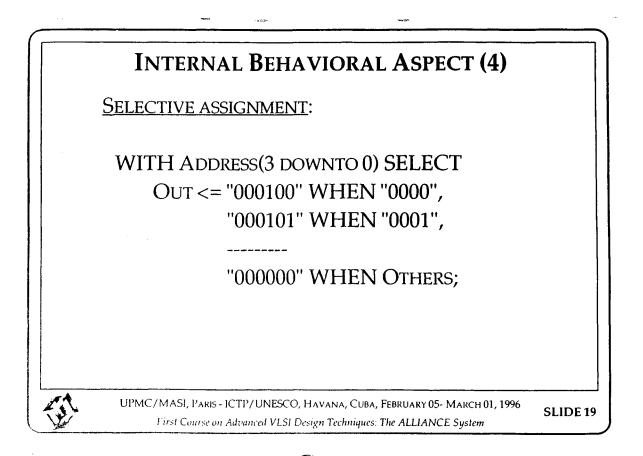

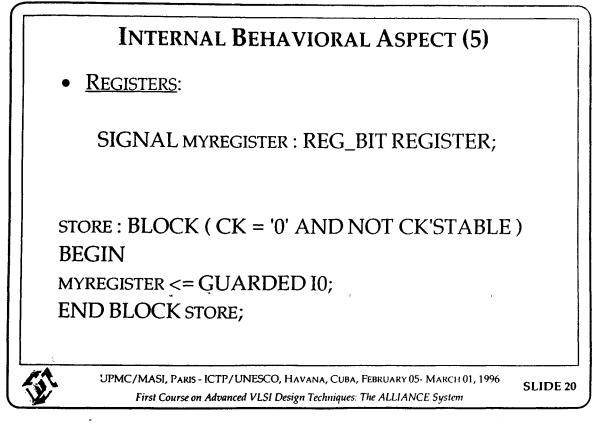

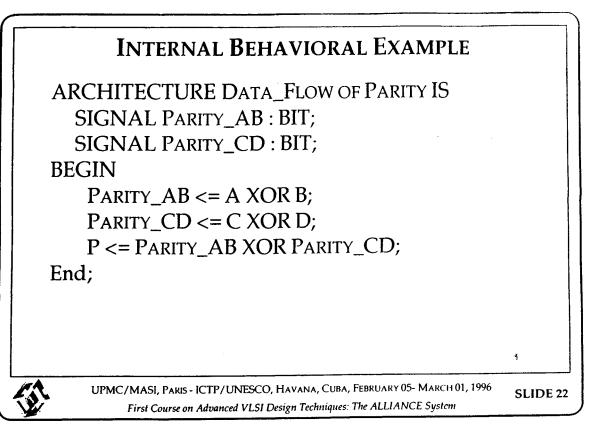

#### **Concurrent** Statement

Natural Concept for Describing Hardware

- Concurrent Signal Assignment

- Conditional Signal Assignment

- Selected Signal Assignment

- Block Statement

- Concurrent Assertion Statement

- Process Statement

# Conditional Signal Assignment More than One Expression,

- > Condition / expression except for the last expression

- > One and only one of the expressions is used at a time

3

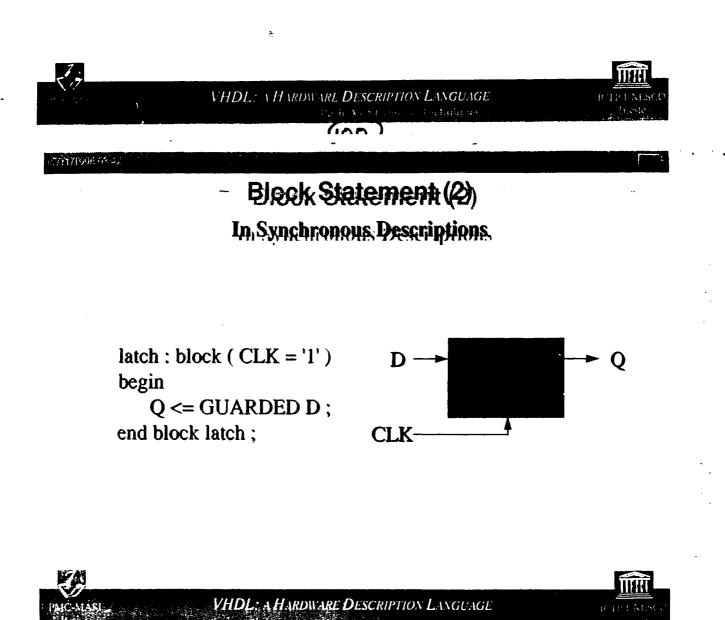

### Block Statement (1)

A Set of Concurrent Statements

label : block

{ block\_declarative\_part }

begin

{ concurrent\_statements }

end block [ label ];

> Used to organize a set of concurrent statements hierarchically

(101)

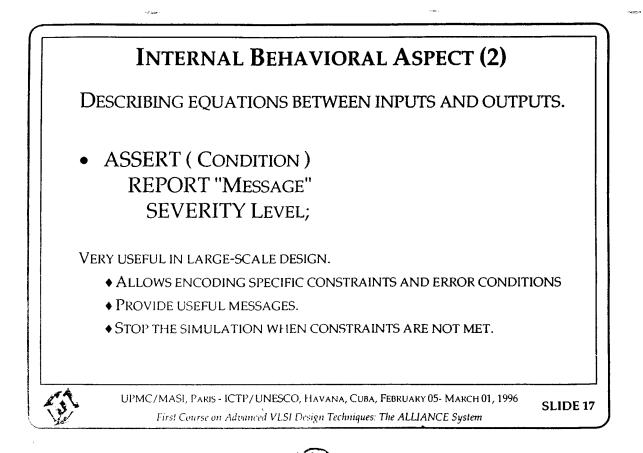

# Assertion Statement

Only One Target,

assert condition

[ report error\_message ]

[ severity severity\_level ];

- > If the condition is false, it reports a diagnostic message

- > Useful for detecting condition violation during simulation

- > Not used in synthesis

end process;

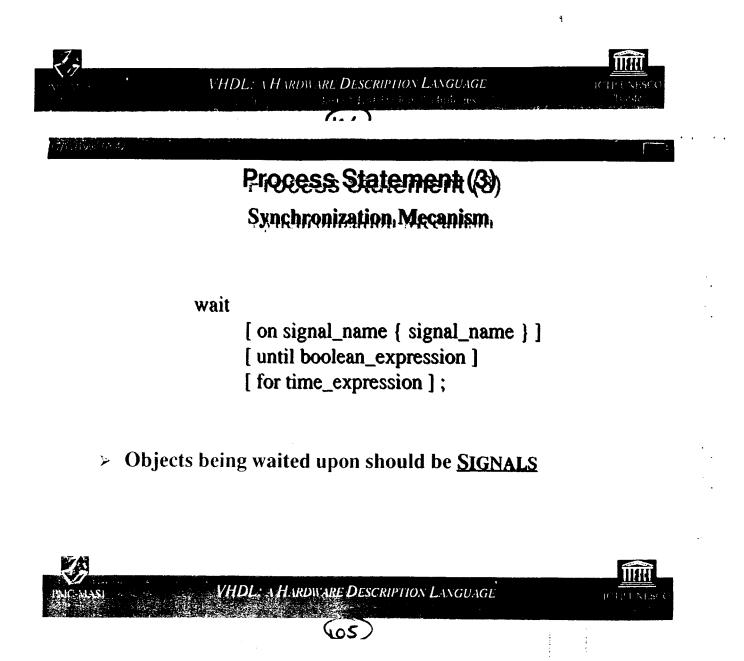

#### > A Synchronization Mecanism is Needed

# Process Statement (4) The Sensitivity List

process [ ( sensitivity\_list ) ]

begin

{ sequential\_statements }

end process ;

Equivalent to a "wait" statement as the last statement wait on sensitivity\_list;

114

1.5 -1

# Variable Assignment Statement **Immediate** Assignment

target\_variable := expression ;

- > Always executed in **ZERO SIMULATION TIME**

- > Used as temporary storages

- > Can not be seen by other concurrent statements

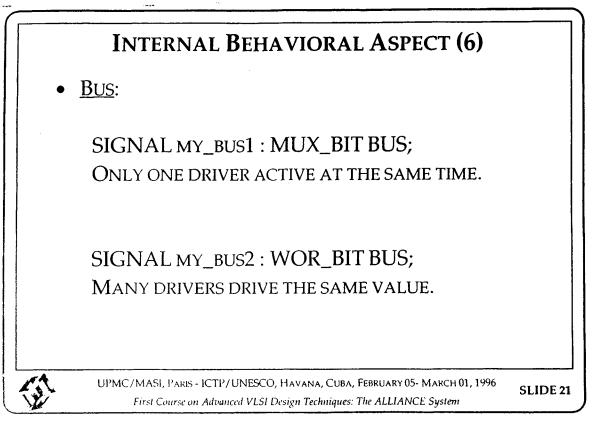

Defines a DRIVER of the Signal

target\_signal <= [ transport ] expression [ after time\_expression ];</pre>

- Within a process, **ONLY ONE** driver for each signal ۶

- > When assigned in multiple processes, it has <u>MULTIPLE</u> **DRIVERS.** A RESOLUTION FUNCTION should be defined

### (14)

(17

(22)

(126)

(23)

(142)

OPTIMIZATION

✓ IMPROVE DESCRIPTION AT EQUIVALENT LEVEL.

$$\begin{cases} X = A + \overline{A}. C. D \\ Y = C. D \end{cases} \Rightarrow \begin{cases} X = A + Y \\ Y = C. D \end{cases}$$

$Y = C. D$

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

ઉપ્લે

(150)

152)

162)

AG4

165

#### ALL

--

(AU

(15)

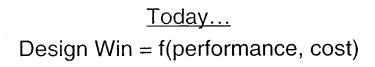

# Low P wer Design & P wer Estimation

|              |     |                      | Nizar Abdallah |

|--------------|-----|----------------------|----------------|

| 1            | 176 | November 1998 - ICTP |                |

| <u>Actel</u> |     | Outline              |                |

- □ Motivation for Power Tools

- Low-Power Design Methodology

- □ Principles for Power Reduction

- □ Principles for Power Estimation

- □ Conclusion

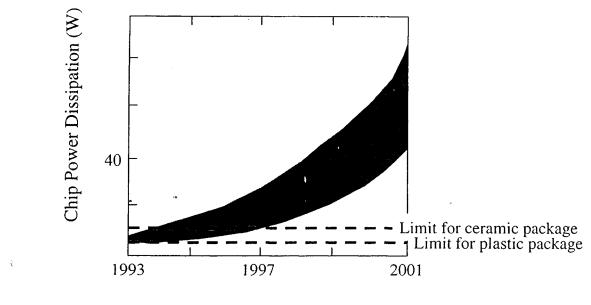

**Deep-Submicron Technologies**

Higher Density and Performance Capabilities (FPGAs: 100 000 Gates; 100 MHz Clock rates)

Power Dissipation Problem

|          |     |                      | Nizar Abdallah |

|----------|-----|----------------------|----------------|

| <u>^</u> |     |                      |                |

| 3        |     | November 1998 - ICTP |                |

|          | 178 |                      |                |

**Actel** Motivation for Power Tools

4 times / 3 Years Increase for the last 20 Years

| PowerPC / Motorola    | 8.5 | 5 Watts |

|-----------------------|-----|---------|

| Dentium / Intel       | 16  | Watts   |

| 🗆 Alpha / Dec         | 30  | Watts   |

| 🗆 Alpha 300 Mhz / Dec | 50  | Watts   |

179

# Motivation for Power Tools

Power = Cost For Major Applications Today

□ Battery Lifetime (Cellular, Medical, ...)

Packaging Cost

□ Reliability (Time to Failure)

□ Green PC program (< 30 Watts)

|                                  |                        | Nizar Abdallah |  |  |

|----------------------------------|------------------------|----------------|--|--|

| 5                                | 180 Novembe            | er 1998 - ICTP |  |  |

| •                                |                        |                |  |  |

| Actel Motivation for Power Tools |                        |                |  |  |

| P                                | ower – Less Performanc | <br>בי         |  |  |

- □ Clock Frequency

- □ Temperature Increase

- □ Electromigration

Nizar Abdallah

November 1998 - ICTP

# **Actel** Motivation for Power Tools

<u>Tomorrow...</u> Performance = f(Power, ...) cost = f(Power, ...)

Design Win will also be low-power dependent

Nizar Abdallah

Motivation for Power Tools

4

We Need...

✓ Low Power Design Methodology

✓ Power Estimation Tools

✓ Power Optimization Tools

| 9            | 184      | Nizar Abdallah<br>November 1998 - ICTP |

|--------------|----------|----------------------------------------|

| <u>Actel</u> | M        | lethodology                            |

| Analogous to | Timing N | /lethodologies                         |

✓ All Levels of Abstraction

✓ Back-Annotation from physical Design

### Sources of Power Consumption

**Power Reduction**

Expression for CMOS Power

□ Gate Generating a Simple Clock Signal with Frequency f

$P_{average} = C V_{dd}^2 f$

□ In general, a signal with a transition density D

$P_{average} = 1/2 C V_{dd}^2 D$

# $P_{average} = 1/2 C V_{dd}^2 D$

- Reducing Switching Activity

Prevent glitches (Architecture, Synthesis, ...)

20% of power increase due to glitches

- Reducing Load Capacitance

Gate sizing, Low-Power cell library

Circuit techniques (Pass-Transistor, ...)

- Reducing Supply Voltage

Drawback: Circuit delay increases

Nizar Abdallah

**Power Estimation**

November 1998 - ICTP

### Two Problems

188

- Design Dependent

Tools Should be Available to the Customer

- Input Pattern Dependent (more Central Problem)

Difficult when the application is not known

A good vector set may be very long

## **High-Level Power Estimation**

- FPGA: Block Macromodels Available Problem to estimate net consumption

- Models for Logical Level, RTL Level, Behavioral Level Need for a power cost function

|                             |             | Nizar Abdallah       |

|-----------------------------|-------------|----------------------|

| 15                          | 190         | November 1998 - ICTP |

| Actel                       | Pow         | er Estimation        |

| What About Accur            | racy and    | Improvements?        |

| Assuming we Have a repre    | esetative V | Vector Set,          |

| Low-Level Timing Simul      | ation       | 10% from Spice       |

| Low-Level Static Technique  |             | 20-60% from Spice    |

| Low-Level Dynamic Technique |             | 10-20% from Spice    |

| Improvement                 |             |                      |

| At the Logical Level is A   | bout        | 5%                   |

| At the RTL Level May R      | each        | 90%                  |

|                             |             |                      |

Nizar Abdallah

- Power Consumption Issues Can no Longer be Ignored for High Density FPGA Design

- **D** Timing / Power : The same challenge

- Input pattern dependency

- All abstraction levels

- Power and timing constraints

- Net consumption is becoming very significant

- □ DPCS IEEE 1481 is also for Power

- □ A Balance between Power, Area, and Delay

- □ Absolute Accuracy is not a Critical Issue

|      |                                                                                                                 |                                          | Anam |

|------|-----------------------------------------------------------------------------------------------------------------|------------------------------------------|------|

| 17   | 192                                                                                                             | November 1998 - ICTP                     |      |

|      |                                                                                                                 |                                          |      |

|      | and a state of the second s | an a |      |

| Acte | <b>)/</b>                                                                                                       |                                          |      |

|      | 70                                                                                                              |                                          |      |

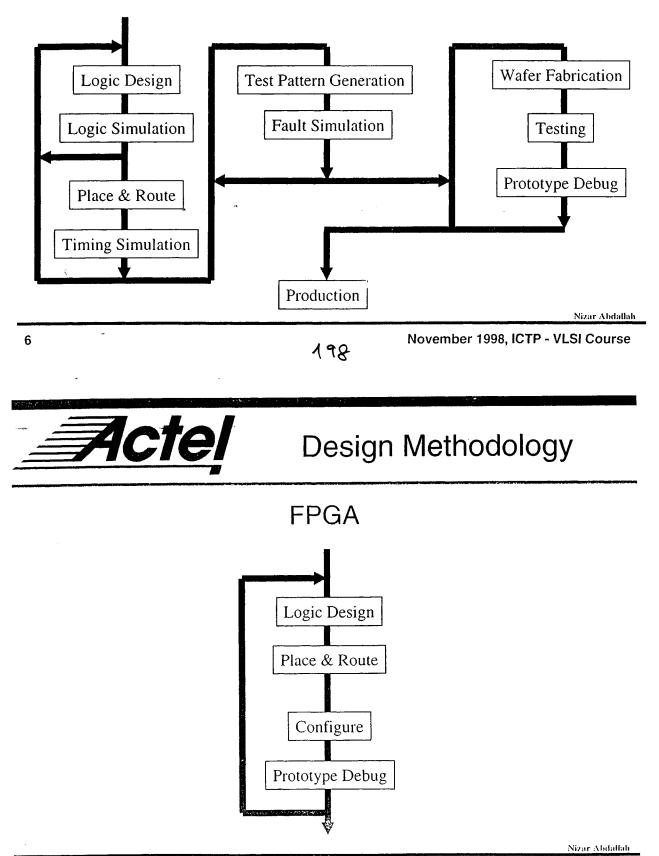

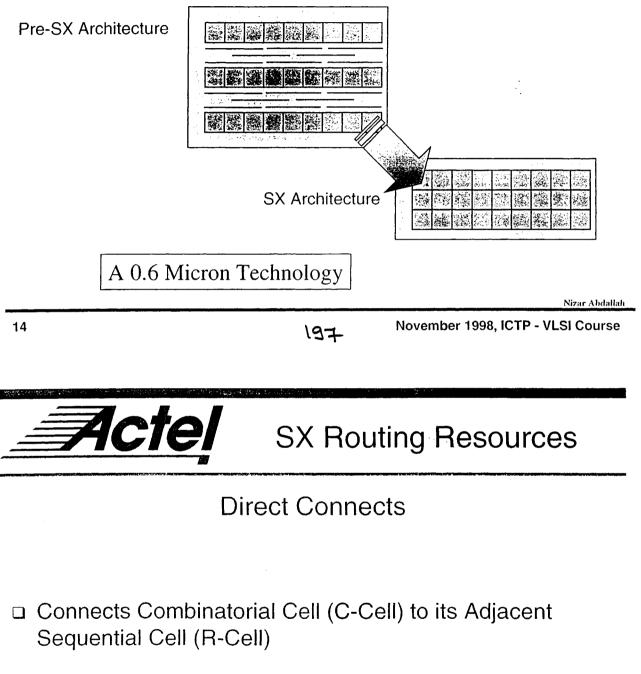

# **FPGA Solutions**

الطليطية س

- □ Cost (Small Series, New Designs, ...)

- □ Rapid Prototyping

- Emulators

- Development Time

- □ Test Time

|              |                                  | Nizar Abdallah                    |

|--------------|----------------------------------|-----------------------------------|

| 2            | 194                              | November 1998, ICTP - VLSI Course |

| <u>Actel</u> | ST MALE AND THE REPORT OF THE ST | Motivation                        |

□ Relatively High Density (100 000 Gates)

Relatively High Performance Capabilities (100MHz)

□ Market in 1993 : \$539M

□ Market in 1998 : \$2124M

### □ Annual Growth Rate of 32%

|        | Nizar Abdallah                    |

|--------|-----------------------------------|

| 4 -    | November 1998, ICTP - VLSI Course |

| Actel  | Sales                             |

|        |                                   |

| Actel  | \$151.3M                          |

| Altera | \$639.0M                          |

| Xilinx | \$610.6M                          |

# **Typical ASIC**

November 1998, ICTP - VLSI Course

□ Relatively High Density (100 000 Gates)

Relatively High Performance Capabilities (100MHz)

|              |                                       | Nizar Abdallah                    |  |

|--------------|---------------------------------------|-----------------------------------|--|

| 8            | 191                                   | November 1998, ICTP - VLSI Course |  |

| <u>Actel</u> | · · · · · · · · · · · · · · · · · · · | Based Architecture                |  |

| Can be       |                                       |                                   |  |

□ Changed During the Development

□ Updated after Delivery to the Customer

Purchased in Larger Quantities

□ Reused (No Inventory if not Sold)

□ Fully Tested Prior to Delivery

Have ...

- Higher Speed (Less RC Delays on the Interconnections)

- □ High Reliability

- No Time-Delay to Reload the Interconnection Information (Available Immediately on Power-Up)

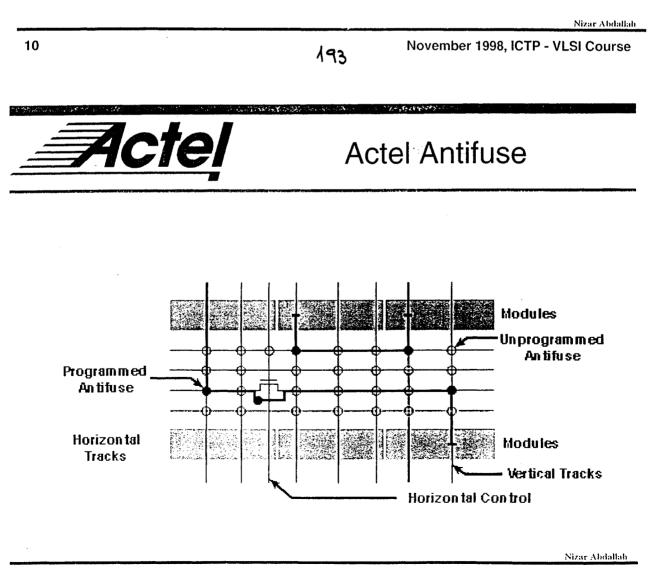

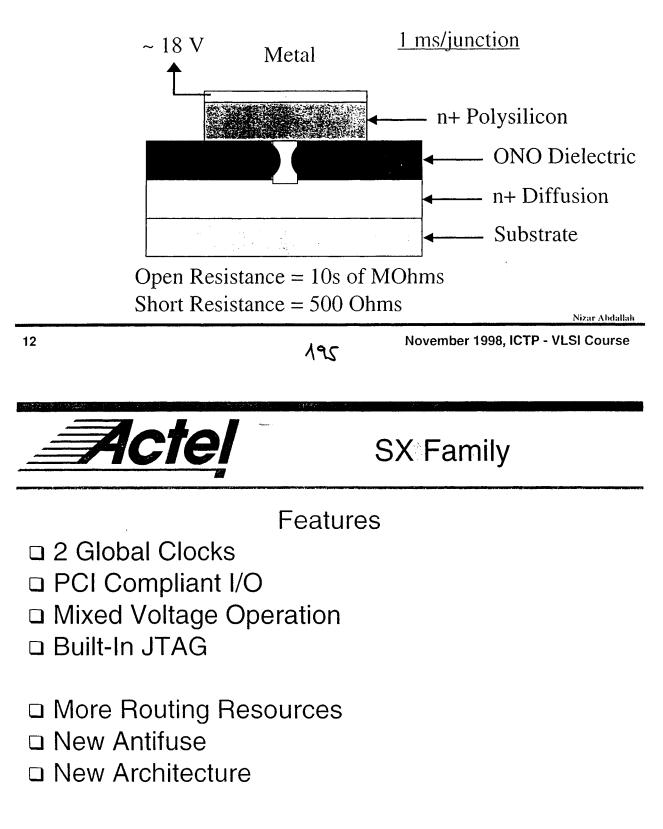

## Programmable Low Impedance Circuit Element

### Routing Interconnects are Above Logic Modules

- No Antifuses

- □ 0.1 ns Routing Delay

## Fast Connects

- Every Cell Output Connects to One

- Accessible by Cells in the Same Cluster or the One Below by One Antifuse

- □ 0.4 ns Routing Delay

|                |             |             |              |             | Nizar Abdallah                    |

|----------------|-------------|-------------|--------------|-------------|-----------------------------------|

| 16             |             |             |              | <b>1</b> 9q | November 1998, ICTP - VLSI Course |

| Actel SX Parts |             |             |              |             |                                   |

|                |             |             |              |             |                                   |

| Part#          | <u>SX08</u> | <u>SX16</u> | <u>SX16P</u> | <u>SX32</u> | <u>SX64</u>                       |

| Gates          | 8,000       | 16,000      | 16000        | 32,000      | 64,000                            |

| MaxIO          | 129         | 177         | 177          | 246         | 340                               |

| Rcells         | 256         | 528         | 528          | 1080        | 2160                              |

| CCells         | 512         | 924         | 924          | 1800        | 3600                              |

| Availb.        | 98          | 98          | 98           | 98          | 99                                |

# ALLIANCE Web Site

# http://www-asim.lip6.fr

|     |                   | Nizar Abdallah      |

|-----|-------------------|---------------------|

| 201 | November 1998, IC | TP - VLSI Course    |

|     |                   |                     |

|     |                   | •• <b>825</b> 8<br> |

|     | 201               |                     |

# Good Luck...