# **Embedded Systems**

# Workshop on Distributed Laboratory Instrumentation Systems

Abdus Salam ICTP, Trieste, November 26 - December 21, 2001

Chu Suan Ang Kuala Lumpur Malaysia

Email: csang@pc.jaring.my

#### Abstract

An overview of embedded systems is first given. This is followed by analysis, design and implementation. Development techniques relevant to embedded system are introduced. Embedded systems networking in distributed environment is discussed. An introduction of web-based embedded systems then follows. Examples of web-based systems are dealt with.

## 1 Overview of Embedded Systems

## 1.1 Introduction

Embedded systems have been around since 1950s. Early examples were a closed-loop control system at a Texaco refinery in Texas and a similar system at a Monsanto Chemical Company ammonia plant in Louisiana. When chemical plants used a mainframe computer for process control in 1950s and 1960s, the mainframe was really an embedded processor, albeit a big and expensive one. When a physicist used a PDP11 minicomputer in 1970s to control and monitor his cryogenics experiments, he had built an embedded system. However, in those days, the number of such systems was not very large, basically because of the cost of hardware. How many PDP11 can a cryogenics laboratory possess? From 1980 onwards PC and microcontroller based embedded systems have been widely used. There is an enormous proliferation of such systems in workplaces. Now we see the post-PC period where embedded systems are generally cheaper, smaller and more powerful. A recent high growth area is the wireless communications area where embedded systems again play a vital role.

The importance of embedded systems can be easily deduced from its huge market. Statistics from the Semiconductor Industry Association (SIA) show for the year 2000 the following market values: (1) Microcontrollers: \$19 billion, (2) Microprocessors: \$30 billion, (3) Entire Semiconductor Industry: \$200 billion. The distribution is as follows: (1) America: 31%, (2) Asia Pacific: 25%, (3) Japan: 23% and (4) Europe: 21%. For comparison, the world population is now at 6 billion and the GDP at \$39,128 billion. Three countries whose GDP is near the world semiconductor market are the Netherlands (\$355 billion), Malaysia (\$233 billion) and Switzerland (\$191 billion).

The reasons behind the rapid growth of embedded systems are due to their rapid and continuous reduction in price and the increase in power and complexity. The cost change for embedded controller is phenomenal in the last three decades - from \$100,000 in 1970s, \$10,000 in 1980s, \$1,000 in 1990s. It is below a thousand dollars now. There has been an order of magnitude change in price for systems carrying the same function in a decade.

Advances in telecommunications are another reason for the growth. Data communications equipment, cellular phones are two huge markets. The explosive growth of the Internet and the progresses in software technology bring in a wide variety of hitherto unknown devices and products. Web-based embedded systems are likely to be deployed in a wide range of applications, including the laboratories and the homes.

Workshop on Distributed Laboratory Instrumentation Systems Abdus Salam ICTP, Trieste, Italy. November 26 – December 21, 2001

## 1.2 What are Embedded Systems?

An embedded system is one with a built-in or embedded processor or computer, typically for carrying out some kind of real-time applications. The computer in such a system is not used as a general purposed computing machine. An embedded processor may or may not have a standard keyboard and video monitor, but it will always have some kind of connection to the outside world, be it a synchrotron, an air-conditioner or a handphone. While it is possible to cite many examples for which the time of response is not critical, there are far more applications of embedded systems which are time critical. Thus the study of real-time aspects of embedded systems becomes an important issue and this workshop dedicates a significant amount of time on it.

It is the application rather than the hardware itself that defines an embedded system. A PC used as a general purposed computer is generally not considered an embedded system. The same type of PC used in the laboratory to log data or control and thus forming an integrated equipment is an embedded processor. In such a case, peripheral interface will be used. However, it may involve only the standard I/O (input/output) ports such as the COM Port, Printer Port, SCSI or USB interface.

There are numerous examples of embedded systems around us. Embedded processors can be found in a large number of applications and situations:

**Laboratory** - test equipment, data acquisition systems, control systems, dedicated equipment. The use of embedded systems in laboratories has been going on for a long time. In 1960s and 1970s researchers in laboratories used minicomputers as embedded processors. Now standard PC and microcontrollers are typically used. From 2000 onwards, the ubiquitous Ethernet and Internet make the use of distributed embedded systems in laboratory environment a reality. Test and laboratory equipment manufacturers are among the first major users of microprocessors in embedded systems. For example, Tektroniks and HP (now Agilent) used microprocessors in their equipment as early as 1970s. The predecessor of this Workshop was a college on the use of microprocessors and PC under real-time environment for laboratories.

**Process industry** - process control systems. This is the granddaddy of real-time embedded systems. Early examples were the closed-loop control system at a Texaco refinery in Texas in 1959 and a similar system at a Monsanto Chemical Company ammonia plant in Louisiana. As the industry was able to pay, they were the ones that use mainframe computers as embedded processors. It is interesting to note that the use of computers in the process industry more or less charts out the history of computer engineering and computer science. Practically all the hardware and software techniques have been used by this industry in one way or the other.

**Manufacturing industry** - production line assembly equipment, automatic test equipment, robots. Manufacturing industry benefits tremendously from embedded processors especially in the area of automation or robotics. Without the use of embedded systems, you would not be paying the current price of about \$1000 for your PC which is really more powerful than a minicomputers in 1970s, let alone the ENIAC (Pennsylvania, 1945, 19,000 vacuum tubes, 200kW, 10 decimal digits, 0.2 ms addition, 2.8 ms multiplication.) or the EDSAC (Cambridge, 1949, 3,800 vacuum tubes, 500kHz mercury delay lines, 256 words, 35 bits, 1.5 ms addition, 6 ms multiplication.) Assembly plants in Malaysia, Mexico, Philippines, Thailand, China and other countries are producing more than 4 billions microcontroller ICs this year. This is only possible when large amount of embedded systems with clever software are used in the assembly and production lines.

**Automotive** - engine controls, anti-lock braking, lamp, indicator and other controls. It turns out that the automotive industry is one of the most important customers of the embedded processors. The average amount spent by a car manufacturer on a car in microelectronics is more than one thousand dollars. New models and especially up-market cars engage more. The Mercedes S-series and the BMW 7-series both have more than 60 embedded processors in each vehicle. This industry stipulates high requirements; electronics used must be highly reliable while able to withstand severe conditions of temperature, vibration and electromagnetic interference. Some processors were initially specially designed for the automotive industry and latter only modified for general purposed use. A robust network CAN (Controller Area Network) was also first introduced in this market and is now adopted by many other industries.

**Consumer Electronics** - audio-visual equipment, household electronics (microwave ovens, washing machines, dishwashers, air-conditioners, etc.), Personal electronics (electronic toys, gadgets, etc.) The list of products in this category is very large and is expanding continuously as the costs of embedded controllers drop. It is inconceivable now to operate a new television set without an IR remote controller. This is of course easily made possible when the price of 4-bit microcontrollers drops below a dollar each.

**Offices** – office and other commercial equipments. Nowadays, fax machines, photocopiers, calculators, computers, scanners, printers, time attendance systems, access control systems, surveillances systems, amongst others, are used in most offices and commercial environment. In banks, more specialised equip-

Workshop on Distributed Laboratory Instrumentation Systems Abdus Salam ICTP, Trieste, Italy. November 26 – December 21, 2001

ments including autoteller machines, counting machines are used. All these are embedded systems of varying complexities.

**Telecommunications** - pagers, telephones, wireless phones, cellular phones, switches, base stations and associated equipment. This is yet another major area of embedded processor application. With the rapid growth in the telecommunications especially in the area of cellular phones, telecommunications manufacturers have been pushing the advancement of embedded processors in terms of size, cost and complexity. With the requirement of integrating analogue and digital circuitries, they are encouraging the chip designer and manufacturer to push towards the limits of this technology.

**Internet** – PC and accessories. Within a PC system, there are many embedded system submodules: keyboards, visual display units, I/O units, and modems. Peripherals are embedded systems: disk drives, printers, scanners, cameras, etc. As mentioned earlier, the growth in the Internet provides a significant impetus for the development of embedded systems.

#### 1.3 Embedded System Structure

Despite the many different types of applications, the principles of operation, system components and design methodologies of embedded systems are essentially the same. A typical system consists of a **Computer** and an **Interface** to the physical environment, which may be a chemical plant, a car engine or a keyboard, for example. In some applications, standard I/O (Input/Output) devices such as the VDU, keyboard and printer are present, as in the case of process controller in a chemical plant. In others there are no standard I/O devices, as in the case of car fuel injection control. In the former case, it is likely that a general purposed computer such as a PC or a more powerful workstation PC will be adapted as the embedded processor. In the latter, microcontrollers designed together with dedicated electronics will be used.

The computers generally fall into three categories: (1) Small, (2) Medium and (3) Large. Small computers are used in small applications such as TV remote controls. In such applications, 4-bit microcontrollers are sufficient. Medium sized computers are 8- or 16-bit microcontrollers or PCs. They are used in jobs like data acquisition systems in laboratories or factories. Large computers are typically high-end computers. A plant monitoring and control system calls for such a computer.

The interfaces in embedded systems may be grouped into the following types: (1) Common serial and parallel interface, (2) Industrial interface, (3) Networking interface, and (4) ADC & DAC. By far the most common interface to the out-

side world is the first group consisting of standard serial buses including RS-232, RS-423, RS-422 and RS-485. The parallel interface (Centronics or IEEE 1284), commonly referred to as the printer port, is also an important interface. More specific to embedded systems are a number of bus arrangements introduced by various semiconductor manufacturers. The common ones are I2C, SPI, Microwire and 1-Wire bus.

A second group of interfaces are used in industrial or other more special applications. They are the IEEE 488 (GPIB, HPIB), SCSI (small computer system interface), CAMAC (Computer Automatic Measurement And Control) and CAN (Controller Area Network). A number of newer interfaces may be grouped here as well. They are the IrDA (Infrared Data Association), USB (Universal Serial Bus) and IEEE 1394 (FireWire or iLink).

Embedded systems in a distributed environment such as the laboratory often have to be networked together. While some of the above are used to network embedded systems, the more common ones for this purpose are the Ethernet, modems, ISDN (Integrated Services Digital Network), DSL (Digital Subscriber Line), ADSL (Asymmetric Digital Subscriber Line), and ATM (Asynchronous Transfer Mode). The Ethernet is used for intra-building networking. The others are used for networking embedded systems over longer distances, over the Internet in most cases.

## 1.4 Real-time Embedded Systems

It was mentioned earlier that embedded systems are typical used to carry out real-time applications. What are real-time systems? One definition is as follows: "Any system in which the time at which the output is produced is significant. This is usually because the input corresponds to some movement in the physical world, and the output has to relate to that same movement. The lag from input time to output time must be sufficiently small for acceptable timeliness."

The above definition covers a wide range of systems - from UNIX workstations to aircraft engine control systems. When a command is entered in a UNIX workstation, we typically get a response on the screen 'with a sufficiently small time lag'. In an aircraft engine control system, the response to commands and other input parameters has to be within certain time limits. There is however a subtle difference between the UNIX workstation and the aircraft engine control system in terms of timeliness.

An alternative definition of a real-time system is as follows: "A real-time system receives inputs and sends outputs to the target system at times determined by the

target system operational considerations - not at times limited by the capabilities of the computer system." This further defines the meaning of response time and it distinguishes between the UNIX workstation and the engine controller. In a UNIX workstation, occasionally when we issue a command, we may not get the response in a time to our liking because the CPU is running some other higher priority tasks or simply overloaded. In this case, the UNIX workstation no longer qualifies as a real-time system according to the more stringent definition mentioned above.

Thus we have (1) Hard real-time system – one that must satisfy deadlines on each and every occasion, e.g. temperature controller of a critical process, and (2) Soft real-time system – one where occasional failure to meet deadlines acceptable, e.g. autoteller machines.

While real-time embedded systems have received a lot of attention in recent years, the earliest proposal of using a computer in real-time applications for controlling a plant actually dates back to 1950 when Brown and Campbell published his paper:

Brown, G.S., Campbell, D.P., "Instrument engineering: its growth and promise in process-control problems', *Mechanical Engineering*, 72(2): 124 (1950).

A couple of early industrial installations of embedded systems are listed below:

A plant monitoring system was installed in September 1958 by Louisiana Power and Light Company at a power station in Sterling, Louisiana, USA.

An industrial computer control installation was implemented by Texaco Company for a refinery at Port Arthur in Texas, USA in March 1959.

The above systems, as well as many other early systems were *supervisory control* systems that used steady-state optimisation calculations to determine the set points for standard analogue controllers. In other words, the digital computer was used to compute and to send simple command to many standard analogue controllers that had been in use for a longer time in the industry. These analogue controllers were generally expensive, complicated and required periodic calibrations. Later, *direct digital control* that allowed the direct control of plant actuators was added and analogue controllers were not required.

The early real-time programs were written in *machine code*, which was manageable when the tasks were well defined and the system small. However, in combining supervisory control with direct digital control the complexity of programming increased significantly. The two tasks have very different time scales and interrupting of the supervisory control is necessary. This led to the development of general purposed real-time operation systems and high-level languages for such systems.

Workshop on Distributed Laboratory Instrumentation Systems Abdus Salam ICTP, Trieste, Italy. November 26 – December 21, 2001

## 2 Analysis, Design & Implementation

Bringing up an embedded system is no different from bringing up any other computer based system and it is important that one applies good design and engineering methodology. Many different approaches have been advocated and there are many books written on the subject but basically the objective is to apply a systematic approach so that the target system may be built to specifications functionally and it is easy to maintain.

As in most other cases, the tasks are *analysis*, *design* and *implementation*.

#### 2.1 Analysis

During the first phase, the functions, requirements and possible constraints of the target system are analysed. The *problem* must be well defined. Otherwise there is no *solution*. Difficulties in the later stage of a project often arise when the scope of the work is not rigidly known or when the designer is uncertain of the capabilities and constraints of the various hardware and software resources. Except for very small jobs, this analysis phase must be carried out with care.

In specifying the requirements of a system, the following list of questions form a basis to *freeze the specifications*:

What is the type of user interface required?

What are the data processing and storage requirements?

Communication requirements – does it connect to the Ethernet or the Internet?

What are the I/O requirements - serial, parallel, ADC/DAC?

What are the real-time requirements or constraints?

## 2.2 Choice of Hardware

As mentioned earlier, an embedded system typically consists of two modules – the processor module and the interface module. Before the actual design phase is entered, there is a decision to make. That is whether the hardware should be purchased or built? This normally hinges on economy consideration amongst others. Delivery time may be another consideration, for example.

Five or ten years ago, ready-made hardware modules for embedded system use were expensive and for many laboratory applications they are out of reach.

Workshop on Distributed Laboratory Instrumentation Systems Abdus Salam ICTP, Trieste, Italy. November 26 – December 21, 2001

However, the past couple of years see the appearance of a range of affordable hardware modules specially targeted at the embedded system market. Many semiconductor manufacturers produce processor and interface modules besides IC components. A number of new manufacturers appear in the market offering very cost effective hardware that can no longer be ignored even for small applications in small laboratories.

One such manufacturer is Rabbit Semiconductor, Davis, California. In their recent catalogue, there is a module RabbitCore RCM2200 selling at \$49 which has the following features:

8-bit powerful CPU based on the Z8010Base-T Ethernet connection128K SRAM256K Flash26 general purpose I/O lines

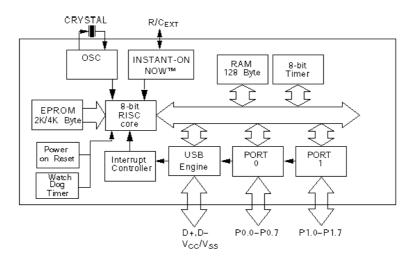

If the decision is to build your own hardware, it is likely that for laboratory applications, 8-bit microcontrollers (MCU) are the choice. Of course, for very large systems or for those requiring special data handling or processing, larger processors including the 32-bit CPU and DSP may be used. However, it is noted that the PCs or high-end PCs would generally be a more cost effective solution in this case, if they can handle the task in hand.

Indeed, for very small jobs, there are available off the shelf a range of small 4-bit MCUs. The costs of the bare MCUs are in the following range:

4-bit at \$1

8-bit between \$5 and \$10

16- 32-bit between \$50 and \$100

Information on the various products in the market can be obtained from the manufacturers' websites. The major suppliers are: Motorola, Mitsubishi, NEC, Hitachi, Philips, Intel, SGS-Thomson, Microchip, Matshushita, Toshiba, NS, Zilog, TI, Siemens, Sharp.

Since the mid 1970s when microprocessors were first introduced, there have been a large number of processors produced. Many of them fall into families of devices which have the same core CPU and general characteristics. A few famous such families are:

Motorola: 6805, 6809, 6811, 683xx Intel: 8051, 80186, 80386 Zilog: Z8, Z80180 Microchip: PIC family

If the decision is to buy ready made hardware, it is still necessary to choose the right host of products offered by many suppliers. If a PC can be used, it is probably still the simplest to implement. However, other than the desk top or notebook PCs, there are the SBCs (Single Board Computers) that are effectively an entire PC shrunk into a single board. These SBCs usually have all the standard I/O ports clustered around various connectors. RAM disks are often available. These are IC memories devices plugged into sockets on the SBC to replace floppy disks. Advantech is a major supplier for SBC but there are many others in the market offering similar products.

While SBCs are neat substitutes for PC, they are generally more expensive than the PC with the same capabilities. This is due to the smaller volume of production. Thus SBC are typically chosen when size constraint dictates its use. Or the environment necessitates the use of industrial grade SBC. (Industrial grade PCs are more expensive.)

Many semiconductor manufacturers formerly producing only component ICs are now marketing board level modules which incorporate processors and I/O devices. These are sometimes referred to as core modules and are typically a fair bit less complex than the SBC. However, they are suitable candidates for a wide variety of embedded system applications. The attractions of these modules are cost and size. The RabbitCore series of Rabbit Semiconductor, from which one example was mentioned earlier, is an example. Dallas Semiconductor's TBM 390 (TINI Board Module) is yet another.

These modules typically have a modern MCU with serial and parallel I/O sufficient for most small to medium sized embedded system applications. Memories are in the range of about 1 Mbytes, half of which are RAM. Flash memories are getting common too. For larger storage, serial memories can usually be added. In the last year or so, Ethernet connection is incorporated making the module ready web enabled. This particular feature may prove to be an extremely important enhancement in core modules.

Software support for these core modules are generally good. Most manufacturers will provide development package consisting of both the hardware and the software environment. An IDE (integrated development environment) is usually provided. C compilers on top of assemblers are commonly available from either the manufacturer or a third party. The TBM is rather unique in that it is designed to run Java in the Internet environment.

## 2.3 Hardware Design

After the decision of whether to build or purchase the hardware is made, one can embark on the design proper. If the choice is on a standard PC or ready built hardware as the embedded processor, then the hardware design step is simplified to that of designing the interface board or circuitry to the target system. Although there can be an infinite variety of target systems, the interface requirements however can be grouped into just a few standard categories - digital I/O, analogue I/O, serial data communications and parallel data communications. Many of the interface requirements are normally provided for by the embedded processor hardware. Perhaps signal conditioning circuits (instrumentation amplifiers, precision attenuators, current drivers, etc.) are needed in the case of analogue I/O or special actuators or sensors.

What are steps taken if you have to design your own processor boards? Ten or fifteen years ago, one would build a microprocessor based system using a hand-

ful of chips including microprocessor, memory, peripheral devices and other glue chips to build an embedded processor. And to do that effectively, certain basic skills have to be acquired. In fact, the earlier Microprocessor College at ICTP spent four weeks trying to achieve just that.

A good example of building a processor board in this way is the 6809 system used in the workshop and earlier Colleges. There are many good reasons for doing so. First of all, it generally has more memory resources than a single chip microcontroller. This facilitates the use of more sophisticated resident firmware including a full-featured monitor or a real-time kernel, for example. Often, there is readily available software for a popular microprocessor such as the 6809. The designer may already be familiar with a well-known microprocessor and need not learn to use a new one.

The trend however, is to use single chip microcontrollers whenever possible. The beauty of designing embedded systems using microcontrollers is the relative ease and simplicity. In general, the overall cost of the system is also lower because of the lower component count.

Whether we use microprocessors or microcontrollers, there is a set of good design rules or practice that one should adhere to. Amongst them, one that has often been overlooked is that the design must incorporate facilities for debugging and testing. Small tests or diagnostics, switches or indicators, added during the designing stage cost very little, but help tremendously in the later stage.

## 2.4 Outline of Hardware Test Procedure

It would be nice if sophisticated tools such as development system, in-circuit emulator and logic analyzer are available. However, it is possible to test and debug with the basic electronics laboratory equipment such as multimeter, oscilloscope and function generator alone, if a systematic approach is adopted.

- Printed circuit board (PCB) inspection for track continuity and possible bridging. This is a step that is often overlooked. However, it is a vital step because easily locatable faults if left undetected, usually cause much more debugging efforts at a later stage.

- Power up the bare PCB and check voltages.

- If it is a microprocessor-based system, such as the 6809, or a microcontroller-based system operating in *expanded multiplexed* mode, test the address bus and (partially) the data and control bus on the *hardware kernel* which is the processor itself. This step is skipped if the system is single-chip, micocontroller-based.

In the case of 6809, this is done by forcing a NOP (\$12) on the data bus by pulling up D1 and D4 to 5V via resistors and grounding all other data lines. It causes the continuous execution of NOP for all memory locations. This in turn results in A0 toggling at half the system clock rate, A1 toggling at half the rate of A0 and so forth. The address bus can thus be checked easily with an oscilloscope. In this test, data bus and control bus are partially verified.

The above test procedure is actually making use of the 1-byte instruction of the microprocessor in an unintended manner. For Z80, 8085 and 8088 similar techniques can be used. In Z80 and 8085, RST 7 (\$FF) instruction is used whereas in 8088 either the 1-byte INT 3 or PUSH instructions may be similarly used.

- If a logic analyzer is not available, implement a tight loop program in the EPROM or EEPROM such as a branch-to-itself loop (LOOP BRA LOOP). For 6809, this consists of two bytes (\$20 \$FE) and takes three machine cycles to execute. A two-byte reset vector is also needed in the ROM. The execution of this very short program can be followed cycle by cycle on an oscilloscope and thereby confirming the proper operation, at least partially, of the data and control bus.

- It is a good idea to include DIP switches and LED indicators in the hardware even if they are not required in the final target system. Test routines for I/O ports which have these input switches and output indicators can be written and tested. Commonly used routines include incrementing the binary value of the output port at a slow rate for visual inspection, reading status of switches and sending it to the output port. This stage of testing serves to verify the operation of I/O ports and to provide users with function selection. Normally on power up the system is programmed to check the status of the input switches and jump to appropriate test routines or the main program.

- Small test routines for other components in the system are then implemented. This includes testing the serial link, the timers, ADC and the memories.

- In some embedded systems where the memory is not very small, a monitor program or kernel is then implemented.

- At this stage most of the hardware testing are done and the task moves on to application software testing and debugging. However, there is one type of hardware bug which is not detected by the testing mentioned above. These are problems caused by intermittent faults, glitches or external interference.

Workshop on Distributed Laboratory Instrumentation Systems Abdus Salam ICTP, Trieste, Italy. November 26 – December 21, 2001

These are detected by means of logic analyzer or in-circuit emulator running in surveillance mode.

## 2.5 Some Hardware Development Tools

While one can get by with the basic tools for small embedded system development, nevertheless it will help if a number of other hardware development tools are available, especially when one is dealing with more sizeable projects or when problems such as intermittent faults, external electromagnetic interference, and glitches arise as mentioned above. It is impossible to give a thorough treatment of various hardware tools in detail here. However, a number of more important ones are introduced below.

**Oscilloscope** - The oscilloscope really needs no introduction other than listed here for completeness sake. It is noted that while the conventional dual-trace 20MHz cathode ray oscilloscope (CRO) is still the faithful workhorse in the lab, there exists in the market now digital oscilloscopes with liquid crystal display (LCD) at a reasonable price. Often it combines the function of a digital (me mory) oscilloscope with a logic analyzer. The importance of the oscilloscope cannot be over-emphasized - after all the HP and Tektronix logic analyzer designers used their oscilloscopes to debug their embedded systems in the '70s!

**Logic Analyzer** - The two traces of an oscilloscope is really rather inadequate or impossible when it comes to *simultaneously* monitoring the 40 or so lines of a typical microprocessor or microcontroller circuit. Logic analyzers capture 48 or more signals and display them in multiple traces or in coded form. Being a powerful embedded system itself, the logic analyzer can perform a number of other things that expedite the debugging of embedded systems.

It allows a trigger condition (data, address and control bus pattern) to be set up and captures the cycle by cycle information in memory (typically few thousand cycles deep) when the trigger condition is met. The captured data can be viewed as traces, in binary/hex form or in mnemonics of the target processor after being disassembled. This provides a very powerful tool for monitoring what's going on at a very low level non-intrusively - at least while the embedded system is running at its normal speed.

Most logic analyzers also provide *timing analysis* whereby the traces are sampled at rates higher than the system clock and hence glitches or other irregular waveforms may be detected.

**Emulator** - First introduced by Intel, now in-circuit emulators are used in large number of embedded system development. This tool brings the debugging of

hardware one step higher than using the logic analyzer alone. Basically it not only allows the target system to be monitored, but also has the ability to stop execution in a controlled manner, change memory and register contents and resume execution. This is achieved by replacing the target system CPU with a more elaborate system typically containing the same type of CPU but having other resources which can carry out the actions mentioned above. In theory the system *emulates* all the CPU's functions in real time.

The major features of the in-circuit emulators are breakpoint, real-time trace, RAM overlay, and performance analysis. Breakpoint setting, as mentioned above, allows us to stop execution, for example, at the end of a function and monitor the return value. When the code does not behave as expected, real-time trace can be used to *look* at what the code is doing. Embedded systems often have their code stored in ROM or EPROM. To change the code during debugging is tedious. RAM overlay is a technique to circumvent this difficulty. Instead of running the code in the target system ROM or EPROM, RAM in the emulator which can be easily modified is used. Performance analysis deals with the problem of code not able to deliver the performance required, such as keeping up with external events. The analysis allows the programmer to scrutinize the execution of his code carefully and find remedies if possible.

In the case of microprocessor-based systems, the target microprocessor is replaced by an emulating processor which has overall control over the data, address and control bus and thus the operation of the entire system. In the case of microcontroller-based systems, it is more complicated. Typically, the emulator operates the microcontroller in the expanded mode so as to gain access to the internal bus. It must also have:

- extra RAM to hold the application software during development,

- a monitor program, and

- rebuilt ports to replace those lost in the expanded mode.

Other features available in an emulator are:

- communication facility between the monitor program and a host computer,

- ability to download object code from the host computer to the target system,

- ability to display and change RAM contents and processor status of the target system,

- single stepping and breakpoint features, and

• execution of the application program in full speed.

The emulator is almost an indispensable tool in the development of embedded systems but the downside is that it is generally not cheap. Good emulator can run to tens of thousands of dollars. Fortunately there are a number of low-cost emulators typically produced by chip manufacturers themselves to promote the sales of their microcontrollers. These are often sold under the name of evaluation board of system. They lack the sophistication of full featured emulators but nevertheless are very useful for small projects.

**ROM Emulator** - ROM emulators are like RAM overlays mentioned above, used to temporarily replace the target system firmware. A ROM emulator consists of RAM and associated circuit, a connection to the ROM socket in the target system and a link to a host computer. The host computer downloads the data into RAM which is then used by the target system as its ROM memory. This relatively simple tool is very effective in embedded system development because it reduces the iteration time significantly.

### 2.6 Software Design and Development

Since the late 1960s, the notion of software development as an engineering process has been universally accepted. For embedded systems, software development is basically a software engineering work. In essence, the aim is to produce well-engineered software, not just software that provides the required functionality. Software should be:

- Simple, clear and easily maintainable

- Reliable

- Efficient

- User friendly, i.e. having an appropriate user interface

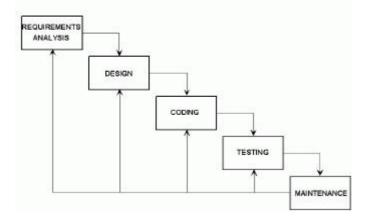

Of the several models developed for software processes, we do not have to stick to a particular one religiously. For practical reasons, it is likely that we shall pick whichever model that appears to be more appropriate for the job in hand:

- The waterfall model or classic life-cycle approach

- The prototyping approach

- The spiral model

Workshop on Distributed Laboratory Instrumentation Systems Abdus Salam ICTP, Trieste, Italy. November 26 – December 21, 2001

The waterfall model is the earliest and most widely used. In a way it is the most natural approach, being derived from other engineering disciplines and is considered a good model which offers a clear picture of the development process. Prototyping and the spiral models are also practised in other engineering disciplines and their use often encompasses the waterfall model within themselves.

### 2.7 The Waterfall Model of Software Development

The Waterfall Model depicted above is easy to understand and it emphasises the importance of the various phases of software development. In other words, software development is not just coding - thus you don't rush to the keyboard and start *programming* the moment you are given a job. A civil engineer does not build a bridge by sending some steel beams and concrete to the site, he designs it first. An electronic engineer does not go to the component rack and pick up a few resistors, capacitors and transistors and start soldering his amplifier, he designs it first. Similarly a software programmer should not write the software without first designing it.

Statistics on business software projects show the following cost breakdowns for the various phases:

| Phase               | Cost |

|---------------------|------|

| Requirements/Design | 44%  |

| Coding              | 28%  |

| Testing             | 28%  |

You do not consider mission completed when you have just finished writing your last line of code or pasting your last control on a form. You test your code, thoroughly! You are responsible for your own code just as a circuit designer is responsible for the functionality of his circuits. A circuit designer does not send

out an untested circuit and let the user come back with failure reports. The first principle in testing is of course *test as you write your code* as it is easier to find problems in small modules and the earlier the problem is found, the easier it is to fix. For a thorough account of various testing techniques, read chapter 6 of "The Practice of Programming" by Kernighan and Pike.

It is common for project groups to work long hours towards the deadline, sometimes round the clock. However, it is obvious that debugging convoluted code at 3 o'clock in the morning is unlikely to produce satisfactory results and thus no credit can be given even though you work seemingly long hours. The real solution is to avoid having to get yourself into such a situation - having to test and debug your code in the small hours because otherwise you are holding up the progress of the whole project. The difficulty or stress in many such situations can be avoided by having a well designed program and by having effective and thorough testing of code in the first place. That is, *design* and *test* your program for greater efficiency.

Design also allows you to eliminate ambiguities, in specifications and interface. Discuss your design with your fellow workers or supervisor. Assumptions you make in your design will be known in the early stage by them and can be modified with less effort if necessary. Difficulties you may have can also be addressed and solved much earlier. Modules that are new and difficult to you can be identified and tested first. Likewise critical modules are easily identified and can thus be dealt with accordingly.

Possible improvements of old designs are to be encouraged. However some improvements may have adverse effects on other part of the system or result in inconsistency. Without a proper design document, it will be too late when others realise your unacceptable improvements. And you will be reluctant to modify your code or design at that stage.

There are earlier work or code that may be reused or modified for reuse. You should find out as much as possible if you are new to the group. Often, your supervisor can suggest or tell you the existence of such prior art or point you to someone who has it, provided that you show him or her the design so that the necessary components can be identified.

## 2.8 Documentation

Documentation can never be overemphasized. Without good documentation, the requirements of the project itself are not known after a short while, even by you yourself. Needless to say, the effort of maintaining the software subsequently will be costly if at all possible.

Documentation should not be postponed till the end of the project, except for collation of documents and writing of manuals. Many of the documentation tasks should be carried out as the project progresses. In fact each and every phase of the waterfall model calls for documentation to be done, there and then. You should never wait till you finish the whole project to document because you almost never ever will, and even if you do, you will have difficulties in reconstructing past events.

## 2.9 Programming Languages

What programming language to use for embedded systems development? Most people agree that one should use a high level language (HLL) to develop embedded systems. Amongst the HLLs, C is known to be a good choice for embedded systems because of its versatility and widespread use. Java has become a strong candidate for its inherent object oriented programming features.

Besides knowing C, an embedded system programmer usually has to learn the assembly language as well. For very small projects, assembly language is still a good choice for speed and code efficiency. Even when one writes in C, a small amount of code such as the interrupt routines and sometimes the device drivers are still implemented in assembly language. Source code debugging is nice, but occasionally, one may have to debug at a lower level, especially when hardware debugger such as logic analyzer is used. In which case, a good knowledge of the assembly language is needed.

One important point in designing software for embedded system is to design with debugging in mind. More often than not, your code won't work the first time. Unlike hardware development, the time taken in testing and debugging during software development can be surprisingly long if you are not careful. Well organised code is a must if you want to minimize debugging time. Well commented code mentioned above is another cardinal virtue in programming.

Ideally a software development environment for embedded systems work should have the following three components:

**Host computer** - This is typically a PC which runs the editor, linker and compiler. PC has become the de facto standard as development platform for embedded systems because of its availability and the amount of commercial and public domain software tools obtainable. Traditional embedded system vendors have designed their development tools with the PC in mind. This also encourages a large number of third party software vendors to use the PC platform for their software tools.

Workshop on Distributed Laboratory Instrumentation Systems Abdus Salam ICTP, Trieste, Italy. November 26 – December 21, 2001

**Debugging engine** - This refers to the component that allows you to *look* into your target system in terms of code execution. It may be in the form of an incircuit emulator or in smaller projects a monitor program resident in the target system itself. This debugging engine allows you to open a window in the host computer and monitor the execution of your code or status of your processor in the target system. For any serious work, it is no longer acceptable to compile your code, program the EPROM, plug it in and hope that it will work!

**Source-level debugger (SLD)** - This is a piece of software running in the host PC which allows you to debug your code at source level, in conjunction with the debugging engine. Not only does it communicate with the debugging engine or target system, it also provides intelligent assistance in the debugging stage. For example it displays the source code (actual C statement instead of assembly code) at which the target is at, resolves symbolic references, examines in the high level format, allows breakpoint to be set at source level, single step through the code again at source code level, etc. Generally a good SLD will provide all these features in very neat multiple window environment, thus making debugging a much easier task than if it is done at assembly code or machine code level.

#### 2.10 Cross Development

As mentioned above, mainly because of the ubiquitous position, the PC is almost universally used as the platform for embedded system development. In which one would be doing cross development running a host of cross software - cross assemblers and linkers, cross interpreters, cross compilers. Unless of course one is developing an embedded system with the same CPU as the PC used (e.g. 80186, 80188, 80386EX or the PC itself used an embedded processor.).

Cross development is necessary for a number of other reasons:

Many microcontrollers used in embedded systems are just too small to be used as processors in development systems. Native or resident assemblers and compilers may not be available for such systems.

Existing computer facilities are readily available and with the appropriate crossdevelopment software tools, are suitable for carrying out the task of software development. This is considered an important advantage because no extra hardware is needed and software tools such as editors are already available.

Nowadays, one can find cross-development software tool for almost any processor in the market. Some manufacturers are supporting their products with a dialup facility or through Internet which allows users to download cross-assemblers and cross-compilers to the PC. Thus, cross assemblers are programs that run on a computer with a different processor from that of the target system, and *assemble* programs written for the target system into *re-locatable object code*. The linkers then relocate, usually with other object modules such as library modules, to the desired execution addresses for the target machine. Common features of cross assemblers are: (1) provision for using macros in program, thus *macro-assembler*, (2) conditional assembly, (3) assembly time calculations and (4) listing control.

Similarly, cross compilers are programs that run on a computer with a different processor from that of the target system, and *compile* high level language programs written for the target system typically into assembly language programs. The use of cross compiler can reduce program development time significantly for large project. It also makes programs more portable, since they are written in high level languages such as C. A typical cross compiler consists of: (1) macro pre-processor, (2) parser, (3) optimiser and (4) code generator.

### 2.11 Simulation

Simulation is a way of using software to model the target system including the target processor itself. A programmer can *see* his system running in the stable environment of his host computer which runs the simulation program. This is used when the target system is not available, when the target prototype is still unreliable, or when the programmer has to access the low level status of the system not normally accessible in embedded systems.

While it sounds like a great idea, unfortunately good simulators for embedded systems are not readily available. This is due to the fact that the simulator has to deal with real-time events and sometimes rather complex I/O. How can you get a general purposed simulator to understand your obtuse or ingenious interface to the solar tracking system? How do you simulate real-time, asynchronous events? To duplicate the data stream coming from the outside world is not easy either.

Nevertheless, there are simulators available for many processors. One successful category of simulators seems to be the microcontrollers such as the 8051. When many of the I/O are integrated on a single chip, they are well defined and thus can be simulated more readily.

## 2.12 Other Techniques for Embedded Systems

There are several other techniques that are found to be useful in developing or debugging software for embedded systems. A monitor program will help in the debugging process tremendously. In structuring your program, the following are found to be very useful: (1) state machine technique and (2) task scheduler and (3) real-time kernel.

A monitor program in the case of MCU embedded systems is usually a small program of 1 to 2 Kbytes of memory for monitoring (and modifying) hardware related information. These may be memory contents, I/O status or even processor status. At low level debugging, a monitor program is an indispensable tool that allows a programmer to *look* into the hardware of the system.

Workshop on Distributed Laboratory Instrumentation Systems Abdus Salam ICTP, Trieste, Italy. November 26 – December 21, 2001

# 3 Development Techniques

## 3.1 State Machine Method

For small systems, *sequential organization* of the program is often used. The entire function of an embedded system is represented by a flowchart and implemented accordingly using a single main loop. When external inputs or events arrive, the program branches off to some modules to carry out the required actions.

There are however a number of shortcomings using the above method:

- Testing of a monolithic program is often difficult.

- When the loop becomes large as more functions are added, life becomes complicated. When a single large loop is used, there is a tendency to produce *spaghetti* code.

- Subsequent modifications of system function, like adding another control switch, are tedious because the entire flowchart has to be revised and often re-implemented entirely.

For many embedded systems, the complexities often justify a more systematic approach of designing the software. Representing the function of a system by a **state machine** is such an approach. The power of state machine representation comes from the fact that it can subsequently be represented by a **state table** which is well suited for microcontroller and microprocessor implementation, even at assembly language level.

Using the state table method of implementing the functions of a system, it is natural that the job be broken down into small, more manageable and often independent modules, called the *action routines*. Such routines are more easily tested and often reusable.

However, the single most important advantage of state table implementation really lies in the ease of function modification. In most cases, only the state table is modified together with the necessary new routines, while most of the old code would be intact.

Workshop on Distributed Laboratory Instrumentation Systems Abdus Salam ICTP, Trieste, Italy. November 26 – December 21, 2001

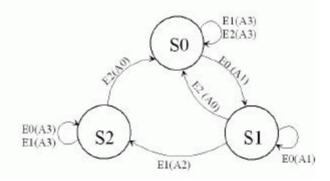

## 3.1 Example of State Machine Representation

A simple example of a system with key switches and display is given here to illustrate the method of state machine representation.

- Suppose we have a keypad with ten numeric keys 0 to 9 and two function keys ENTER and DELETE and a 4-digit numeric LED display.

- On power up, the display shall show 0.

- Numeric values can be entered on the keypad and as each digit is entered, it is scrolled into the display from the rightmost digit. During this mode, the display blinks to indicate *digit entering mode*.

- The *digit entering mode* is terminated with either the ENTER key or the DELETE key.

- If ENTER is pressed, the display stops blinking.

- If DELETE is pressed, the display stops blinking and shows 0.

There are 3 possible states in this example:

| State | Name       | Description                                                     |

|-------|------------|-----------------------------------------------------------------|

| SO    | Initial    | Power-on state or after DELETE, display shows 0 in steady mode. |

|       |            | 5                                                               |

| S1    | Data Entry | Digit entry mode, display shows digits in blinking mode.        |

| S2    | Display    | Final display mode, display shows final value in                |

|       |            | steady mode                                                     |

There are 3 types of event:

| Event | Name   | Description               |

|-------|--------|---------------------------|

| E0    | Number | Entry of any numeric key. |

| E1    | Enter  | ENTER key is pressed.     |

| E2    | Delete | DELETE key is pressed.    |

There are four action routines needed:

| Action | Name           | Description                                      |

|--------|----------------|--------------------------------------------------|

| A0     | Reset          | Display 0.                                       |

| A1     | Build digits   | Build up display buffer from right while numbers |

|        |                | are entered and blink display.                   |

| A2     | Steady display | Show steady display.                             |

| A3     | Null           | No action.                                       |

The specification mentioned earlier is represented by a state diagram.

The above state diagram can be easily transformed into a state table representation as follows:

| Present State | Event | Action | Next State |

|---------------|-------|--------|------------|

| SO            | E0    | A1     | S1         |

|               | E1    | A3     | SO         |

|               | E2    | A3     | SO         |

| S1            | E0    | A1     | S1         |

|               | E1    | A2     | S2         |

|               | E2    | A0     | SO         |

| S2            | E0    | A3     | S2         |

|               | E1    | A3     | S2         |

|               | E2    | A0     | SO         |

The complexity of the system has thus been broken down into:

- A number of action routines.

- A service routine to scan the keypad and update display.

- A state stable.

- A very small main program.

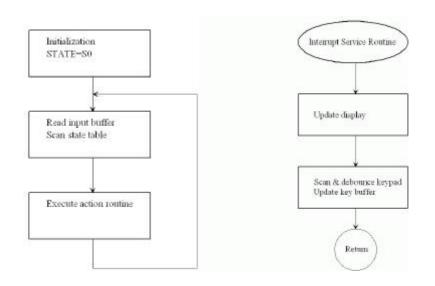

The main program has reduced to a trivial program consisting of initialization and an infinite loop of reading the input buffer to get a new event, scanning the state table to decide what is the next state and the action to be taken. The action is carried out simply by calling the action routine.

The advantage of this seemingly tedious process is as follows. First the state diagram technique allows a complete and systematic approach to the problem. All events can be analyzed at all possible states. This technique is often used to implement communications protocols which can be rather complex because of the large number of possible states.

The next important advantage of the state machine method is that subsequent modification of the functions of the system is relatively painless. Often, a rearrangement of the state diagram and state table is all that is necessary. In other case, the modification may involve the introduction of several new action routines. In either case, the modification is straightforward.

The keypad and display service routine may be implemented as an **interrupt service routine** based on 10-ms clock ticks from a programmable timer module, for example.

The main program:

The interrupt service routine:

## 3.2 Task Scheduler in Embedded System

An application in real-time embedded system can always be broken down into a number of distinctly different tasks. For example,

- Keyboard scanning

- Display control

- Input data collection and processing

- Responding to and processing external events

- Communicating with host or others

Each of the tasks can be represented by a state machine. However, implementing a single sequential loop for the entire application can prove to be a formidable task. This is because of the various time constraints in the tasks – keyboard has to be scanned, display controlled, input channel monitored, etc.

One method of solving the above problem is to use a simple **task scheduler**. The various tasks are handled by the scheduler in an orderly manner. This produces the effect of simple multitasking with a single processor. A bonus of using a scheduler is the ease of implementing the *sleep* mode in microcontrollers which will reduce the power consumption dramatically (from mA to  $\mu$ A). This is important in battery operated embedded systems.

There are several ways of implementing the scheduler – preemptive or cooperative, round robin or with priority. In a cooperative or non-preemptive system, tasks cooperate with one another and relinquish control of the CPU themselves. In a preemptive system, a task may be preempted or suspended by different task, either because the latter has a higher priority or the time slice of the former one is used up. Round robin scheduler switches in one task after another in a round robin manner whereas a system with priority will switch in the highest priority task.

For many small microcontroller based embedded systems, a cooperative (or nonpreemptive), round robin scheduler is adequate. This is the simplest to implement and it does not take up much memory. Ravindra Karnad has implemented such a scheduler for 8051 and other microcontrollers. In his implementation, all tasks must behave cooperatively. A task waiting for an input event thus cannot have infinite waiting loop such as the following:

Workshop on Distributed Laboratory Instrumentation Systems Abdus Salam ICTP, Trieste, Italy. November 26 – December 21, 2001

```

While (TRUE) {

{

Check input

....

}

```

This will hog processor time and reprieve others of running. Instead, it may be written as:

```

If (input TRUE)

{

...

}

Else (timer[i]=100ms)

```

In this case, *task i* will check the input condition every 100 ms, set in the associated timer[i]. When the condition of input is false, other tasks will have a chance to run.

The job of the scheduler is thus rather simple. When there is clock interrupt, all task timers are decremented. The task whose timer reaches 0 will be run. The greatest *virtue* of the simple task scheduler ready lies in the smallness of the code, which is of course very important in the case of microcontrollers. The code size ranges from 200 to 400 byes.

Workshop on Distributed Laboratory Instrumentation Systems Abdus Salam ICTP, Trieste, Italy. November 26 – December 21, 2001

### 3.3 Real-time Kernel in Embedded Systems

It would be ideal if we can incorporate a real-time operation system (RTOS) in the embedded system we build. Unfortunately, more often than not, the memory and other resources of most embedded systems do not permit this. There is however an alternative - that of using a subset of the RTOS to solve the problem of real-time requirements. If the I/O and file handling is removed from the fully fledged RTOS, we are left with a kernel which deals with tasks handling. This turns out to be a powerful tool in dealing with real life embedded system applications, such as the state machine technique.

In embedded systems, interrupts are used to respond to external events and in doing so avoid the waste of CPU time by constant polling for such events. However, interrupts handling can be rather complex if there are many processes to be handled simultaneously. In many situations, embedded systems run more or less independent programs that share some common resources. A very large intertwined program will result if we use simple interrupt handling technique. Realtime kernel (RTK) will help the programmer to deal with such circumstances by thinking in terms of concurrent tasks instead of individual routines that execute when certain events occur.

Real-time kernels come in a great variety of types. Many of the small RTKs are implemented in assembly language; others are implemented in HLL such as C. There are many RTK manufacturers producing kernels for 8-, 16- and 32-bit processors including proprietary and open market ones. The price tag of these commercial RTKs ranges from USD100 to USD10,000.

There are also a small number of real-time kernels appearing in journals, magazines and books, which are normally available in source code. One such example is an RTK designed by Jean J. Labrosse called  $\mu$ C/OS, which is implemented in C with full source code available to the user.

Jean J. Labrosse published an early version of  $\mu$ C/OS in *Embedded Systems Programming* magazine in June 1992. It was written in C with the initial goal for creating a small but powerful kernel for the 68HC11 microcontroller. It has since been extended to a portable system suitable for use with any microcontroller/microprocessor provided that it has a stack pointer and the processor status can be stacked and unstacked.

Labrosse has subsequently written a book describing  $\mu C/OS$ . The latest edition is:

Workshop on Distributed Laboratory Instrumentation Systems Abdus Salam ICTP, Trieste, Italy. November 26 – December 21, 2001

Jean J. Labrosse, *MicroC/OS-II The Real-Time Kernel*, R & D Books, Lawrence, Kansas, 1999, ISBN 0-87930-543-6

The complete source listing of  $\mu$ C/OS is available in the book. It is also available in a companion disk.

The code is protected by copyright. However, you do not need a license to use the code in your application if it is distributed in object format. You should indicate in you document that you are using  $\mu C/OS$ .

#### 3.4 Main Features of $\mu$ C/OS

The main features of  $\mu C/OS$  are:

**Portable** - It is written in C, with a small processor specific code in assembly to create task, start multitasking and perform context switching. For 80186/80188 the assemble language code is less than 4 pages.

**ROMable** - The size and design of the kernel is such that it is suitable for storing in ROM or EPROM.

Priority driven - It always runs the highest priority task that is ready.

**Pre-emptive** - When a task makes a higher priority task ready to run, the current task is pre-empted or suspended and the higher priority task is immediately given control of the processor. Execution of the highest priority task is deterministic.

Multitasking - Up to 63 tasks may be set up.

**Interrupt feature** - Interrupts can suspend the execution of a task. If a higher priority task is awakened as a result of the interrupt, the higher priority task will run as soon as the interrupt completes. Interrupts can be nested up to 255 levels deep.

Workshop on Distributed Laboratory Instrumentation Systems Abdus Salam ICTP, Trieste, Italy. November 26 – December 21, 2001

## 3.5 µC/OS Tasks

```

A task is an infinite loop function or one that deletes itself when it is finished. The infinite loop can be pre-empted by an interrupt that can cause a higher priority task to run as mentioned above. A task can also call the following \muC/OS services: OSTaskDel(), OSTimeDly(), OSSemPend(), OSMbox-Pend(), OSQPend(). Each task has a unique priority, ranging form 0 to 62. The lower the value the higher the task priority.

```

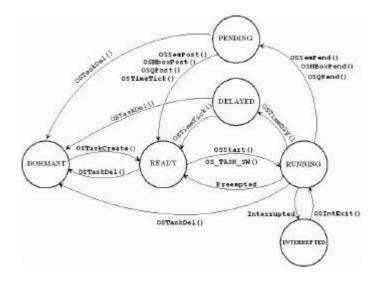

There are altogether six possible states for a task as listed below:

- DORMANT -The state when a task has not been made available to  $\mu$ C/OS.

- READY When a task is created by calling **OSTaskCreate()**, it is in the READY state. Tasks may be created before multitasking starts or dynamically by a running task. If the created task has a higher priority than its creator, the created task is immediately given the control of the processor. A task can return itself or another task to the DORMANT state by calling **OSTaskDel()**.

- RUNNING The highest priority task created is in the RUNNING state when multitasking is started by calling **OSStart()**.

- DELAYED -The running task may call OSTimeDly() and enters the DE-LAYED state. The next highest priority task then runs. The delayed task is made ready to run by **OSTimeTick()** when the desired delayed time expires.

- PENDING The running may have to wait for an event by calling **OSSem-Pend()**, **OSMboxPend()** or **OSQPend()**. It then enters the PENDING state. The next highest priority task then runs. The task is made ready when the event occurs. The occurrence of an event may be signalled by another task or by an interrupt service routine (ISR).

- INTERRUPTED A task may be interrupted and enters the INTER-RUPTED state. The ISR then runs. The ISR may make one or more tasks ready to run. When all tasks are either waiting for events or delayed, an idle task OSTaskIdle() is executed.

#### µC/OS Task State Transition Diagram:

### 3.6 Task Scheduling

Task scheduling is done by **OSSched()** which determines which task has the highest priority and thus will be the next to run. Each task has a unique priority number between 0 and 63. Priority 63, the lowest, is assigned to the idle task when  $\mu$ C/OS is initialised.

Each task that is ready to run is placed in a ready list. The task scheduling time is constant irrespective of the number of tasks created. **OSSched()** looks for the highest priority task and verifies that it is not the current task to prevent unnecessary context switch. A context switch is then carried out by **OS\_TASK\_SW()**.

**OSSched()** runs in a critical section to prevent ISR from changing the ready status of a task.

### 3.7 Interrupt Processing

$\mu$ C/OS requires an *interrupt service routine* (ISR) written in assembly language. Interrupts are enabled early in the ISR to allow other higher priority interrupts to enter. **OSIntEnter()** is called on entering and **OSIn-tExit()** on leaving the ISR to keep track of the interrupt nesting level. There may be 255 levels.

Workshop on Distributed Laboratory Instrumentation Systems Abdus Salam ICTP, Trieste, Italy. November 26 – December 21, 2001

$\mu$ C/OS's worst case interrupt latency is 550 MPU clock cycles (80186/80188).  $\mu$ C/OS's worst case interrupt response time is 685 MPU clock cycles (80186/80188).

### 3.8 Clock Tick

Time measurement in suspending execution and in waiting for an event is provided by **OSTIMETICK()**, which supplies the *clock ticks* or the heartbeats. **OSTIMETICK()** also decrements the **OSTCBDLy** field for each **OS\_TCB** that is not zero. The time between tick interrupts is application specific and is typically between 10 ms and 200 ms. **OSTIMETICK()** increments a 32-bit variable OSTime since power up. This provides a system time.

### 3.9 Communication and Synchronisation

$\mu$ C/OS supports message *mailboxes* and *queues* for communication. A task can deposit, through a kernel service, a message (the pointer) into the mailbox. Similarly, one or more tasks can receive messages through a service provided by the kernel. Both the sending and receiving task have to agree as to what the pointer is pointing to. A message queue is an array of mailboxes.  $\mu$ C/OS supports *semaphore* (0-32767) for synchronisation and coordination.

The above services are *events*. Thus, a task can signal the occurrence of an event (**POST**) or wait for an event to occur (**PEND**). However, the ISR can **POST** an event but cannot **PEND** on an event. When an event occurs, the highest priority task waiting for the event is made ready to run.

## 3.10 Memory Requirements

The memory required for the program is less than 3150 for the 80186/80188 microcontroller. This can be reduced if some of the services are not required. The RAM or data memory is as follows:

200

- + ((1 + OSMAX\_TASK) \* 16)

- $+ (OS_MAX_EVENTS * 13)$

- $+ (OS_MAX_QS * 13)$

- + SUM(Storage requirements for each message queue)

- + SUM(Storage requirements for each task stack)

- + (OS\_IDLE\_TASK\_STK\_SIZE)

Workshop on Distributed Laboratory Instrumentation Systems Abdus Salam ICTP, Trieste, Italy. November 26 – December 21, 2001

## 3.11 Kernel Services

For reference the kernel services are given in the following table:

| #  | Service            | Description                     |

|----|--------------------|---------------------------------|

| 1  | OSInit()           | Initialize µC/OS                |

| 2  | OSIntEnter()       | Signal ISR entry                |

| 3  | OSIntExit()        | Signal ISR exit                 |

| 4  | OSMboxCreate()     | Create a mailbox                |

| 5  | OSMboxPend()       | Pend for message from mailbox   |

| 6  | OSMbox Post()      | Post a message to mailbox       |

| 7  | OSQCreate()        | Create a queue                  |

| 8  | OSQPend()          | Pend for message from queue     |

| 9  | OSQPost()          | Post a message to queue         |

| 10 | OSSchedLock()      | Prevent rescheduling            |

| 11 | OSSchedUnlock()    | Allow rescheduling              |

| 12 | OSSemCreate()      | Create a semaphore              |

| 13 | OSSemPend()        | Wait for a semaphore            |

| 14 | OSSemPost()        | Signal a semaphore              |

| 15 | OSStart()          | Start multitasking              |

| 16 | OSTaskChangePrio() | Change a task's priority        |

| 17 | OSTaskCreate()     | Create a task                   |

| 18 | OSTaskDel()        | Delete a task                   |

| 19 | OSTimeDly()        | Delay a task for n system ticks |

| 20 | OSTimeGet()        | Get current system time         |

| 21 | OSTimeSet()        | Set system time                 |

| 22 | OSTimeTick()       | Process a system tick           |

Workshop on Distributed Laboratory Instrumentation Systems Abdus Salam ICTP, Trieste, Italy. November 26 – December 21, 2001

# 4 Embedded Systems Networking in Distributed Environment

## 4.1 Introduction

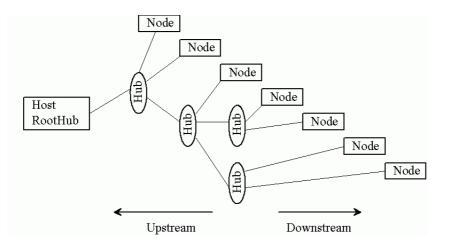

There are two broad methods of connecting embedded systems in a distributed environment:

- (1) Non-Internet connection

- (2) Internet connection

Before the proliferation of the Ethernet and Internet, connecting embedded systems in a distributed environment such as a laboratory or a factory was usually achieved by conventional parallel or serial connections. Parallel connections were suitable for short-range use, typically within a few meters, limited by difficulties in driving synchronous multiple signals and cost of cabling. The advantage of parallel connection was obviously higher data rates on a parallel bus. Parallel bus standards at Mbps rates were implemented when the standard serial link was still at Kbps.

While there are dedicated parallel bus standards designed for specific industries or environments such as the General Purpose Interface Bus (GPIB), the Computer Automated Measurement And Control (CAMAC) and the Small Computer System Interface (SCSI), the most common method is the parallel port, used typically for printer connection. This is simple to use and is readily available, being a standard I/O port in all PCs. The newer version (IEEE 1284) available in most new PCs is being used for many purposes other than connecting to a printer.

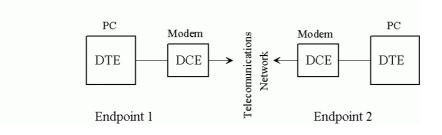

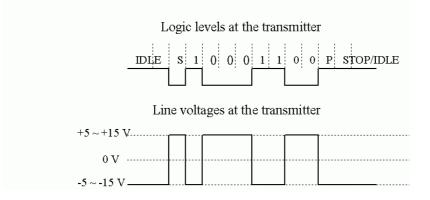

However, by far the most important networking technique in a distributed environment beyond the size of a test bench is, of course, the serial bus, exemplified by the RS-232-C (Recommended Standard number 232, revision C from the Electronic Industry Association) and its related standards. Like the parallel port, the use of this serial technique is extremely handy. There are two serial ports available in most standard desktop PCs – COM1 and COM2. Users and manufacturers alike are taking advantage of these two serial ports for almost every type of equipment.

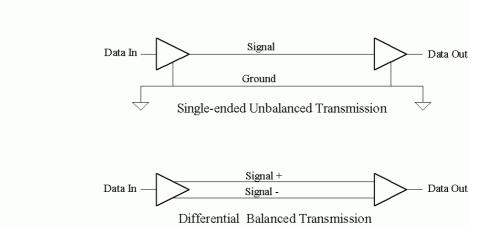

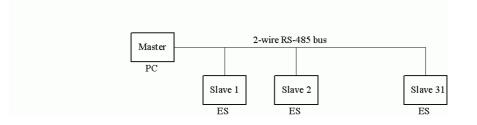

The limitations of the standard PC serial ports are data rate and distance, being 20 Kbps and <50 feet. Related standards such as RS-485 eliminate such limitations to a great extent while still maintaining the simplicity of the standard. For

example, RS-485 is capable of 4000 feet and 10 Mbps performance. It has an added advantage of a bus configuration which allows it to connect to 32 transmitters and 32 receivers. (For comparison, the RS-232 is a point-to-point connection which can only connect two machines together.) Although existing OS in PCs would not be able to handle continuous 10 Mbps data rate, the 4000-foot transmission distance is a welcome feature in distributed laboratory environment.

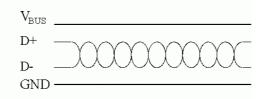

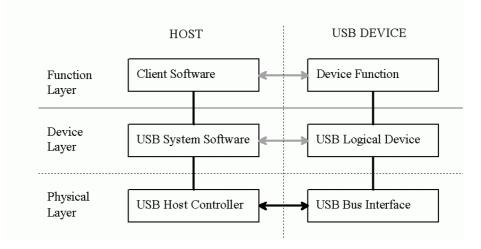

As newer equipment and gadgets (especially video devices) demand higher and higher data rates, there are a couple of high-speed serial communication standards that have been introduced to the PC world in recent years. Universal Serial Bus (USB) provides for peripheral speeds of up to 1.5 Mbps for low-speed devices and up to 12 Mbps for full-speed devices. The latest USB 2 specification increases the data rate to 480 Mbps. The cable length is limited to 5 metres, extendable to 25 metres using 4 hubs or with active cables. A total of 127 devices may be connected.

A competing standard to USB is the IEEE 1394 (FireWire or iLink) which has a maximum data rate of 400 Mbps and is cable of connecting up to 63 devices. At this dazzling speed, full frame rate video can be transmitted from cameras to PCs directly through a thin cable. The cable length is 4.5 metres, again extendable with hubs and repeaters.

Some applications call for wireless connection. This is provided by IrDA, a standard defined by the Infrared Data Association. It specifies wireless transfer via infrared radiation at 875 nm. IrDA 1.1 has a maximum data rate of 1.152 Mbps. At this rate, the range is small, typically less than 20 cm.

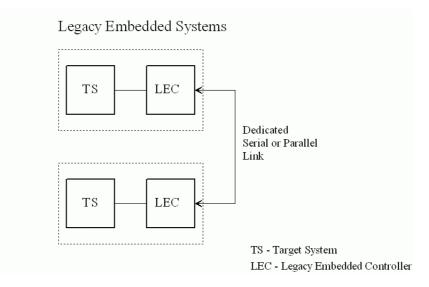

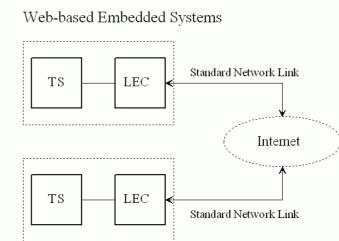

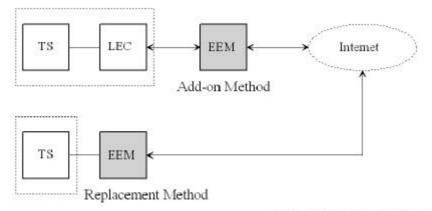

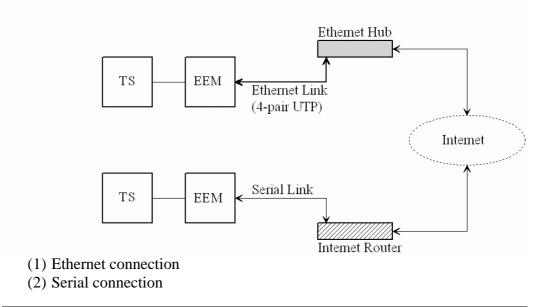

The recent ubiquitous deployment of the Ethernet and Internet and the availability of low cost embedded systems, capable of functioning as web server, have changed everything in networking equipments in a distributed environment. It is now the age of the Internet! In this respect there are two approaches. One is to forget your old equipment and design new web-based ones and network them. The other is to add a web-enabled front-end or intermediary to your existing equipment and thus make it accessible via the Internet. Prudence and reality tell us that there are many situations where existing equipment cannot be abandoned or redesigned. Thus the second approach is an important one. Indeed, many companies dedicated to providing such hardware and software have appeared in the last couple of years. Their solutions are typically very attractive and cost effective, and we shall look at a couple of them.

If you embark on an entirely new project then you have two options in hardware for your embedded systems. If you are lucky enough to have a large budget, then use a PC or one of its derivatives (SBC and embedded PC) as your embedded processor. The interface hardware can also be purchased as standard plug-in boards on the PCI (Peripheral Component Interconnect) bus. This eliminates hardware design completely. There are numerous suppliers producing a plethora of I/O boards. You can almost always find what you want provided that you can afford it. We shall not look into this area in these lectures.

Sometimes a PC is an overkill for your applications or your budget simply cannot afford using PCs. Until recently, building web-based applications under such a situation has been difficult. One often settled for the non-Internet option. Rather affordable hardware is currently available in the market either as components or ready built modules that are web-enabled. We shall look into this area.

#### 4.2 Non-Internet Connection

The hardware or physical layer specifications of a few common methods of connecting embedded systems are described in this section. They are

- (1) The parallel port

- (2) The serial port

- (3) Selected high-speed ports

#### 4.3 The Parallel Port

Originally intended for printer connection, this port has undergone several revisions and it now provides bi-directional connection to a host of equipment. The initial printer port in the IBM PC in 1981 was really designed for unidirectional connection to the relatively slow dot-matrix printers at the time. It transferred data at 150 kilobytes/second and was software intensive. Lack of design standards forced a cable limitation to 6 feet. In 1987, IBM PS/2 was introduced and this PC enhanced the parallel port by adding bi-directional data flow.

Printer and computer manufacturers started to enhance the parallel port standard in 1991 and this resulted in two improved standards: EPP (Enhanced Parallel Port) and ECP (Extended Capability Port). EPP was introduced by Intel, Xircom and Zenith Data Systems and was used primarily by non-printer peripherals such as CD ROM, tape drives, hard disks etc. ECP was introduced by Hewlett Packard and Microsoft and was used primarily by new printers and scanners.

In 1994 the current IEEE 1284 standard, "Standard Signalling Method for a Bidirectional Parallel Peripheral Interface for Personal Computers", was released. This standard encompasses all the other modes of parallel port, viz.

Workshop on Distributed Laboratory Instrumentation Systems Abdus Salam ICTP, Trieste, Italy. November 26 – December 21, 2001

- (1) Compatibility mode Centronics or standard mode

- (2) Nibble mode -4 bits at a time using status line for data

- (3) Byte mode 8 bits at a time using data line

- (4) EPP bi-directional, up to 2 Mbytes/second

- (5) ECP bi-directional, DMA transfer, up to 2 Mbytes/second

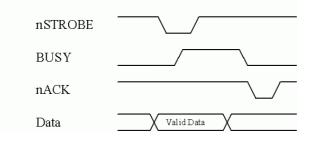

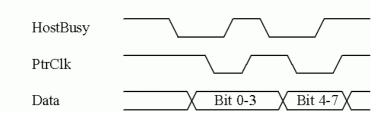

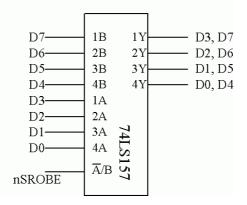

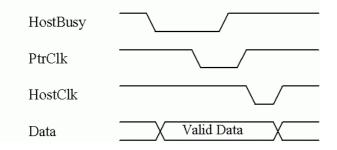

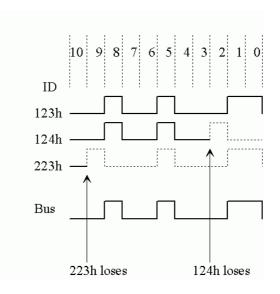

The standard specifies a cable length of 10 metres.