### OUTLINE

- I INTRODUCTION

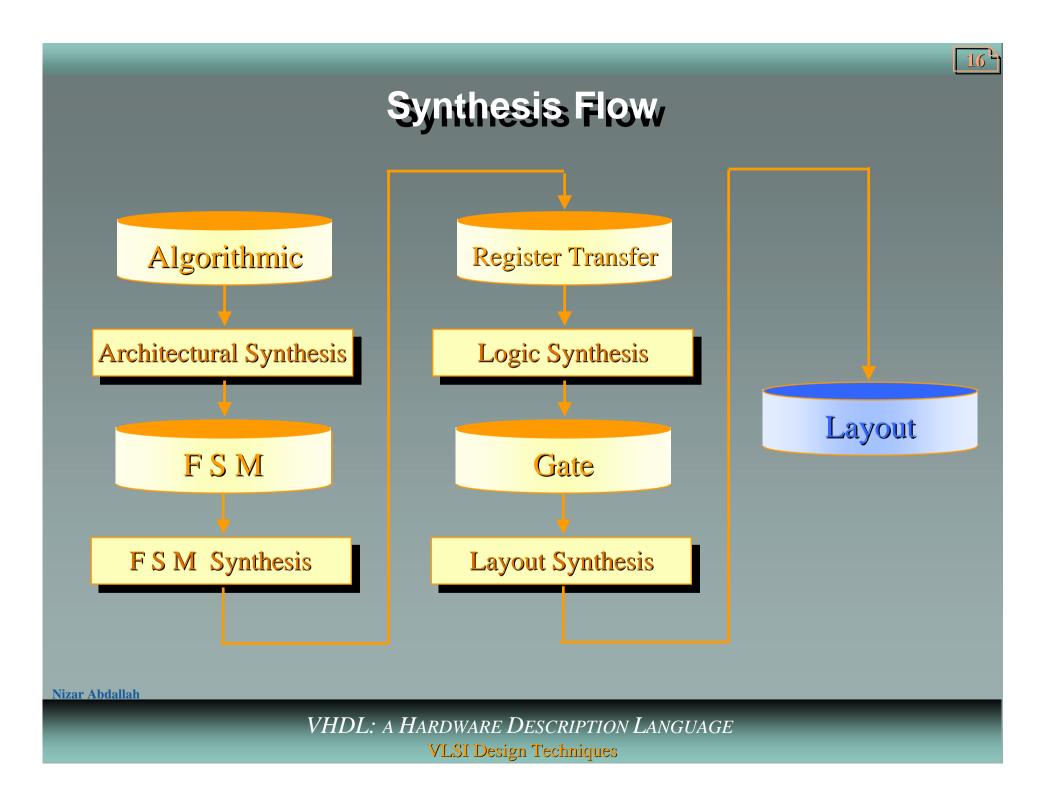

- II DESIGN METHODOLOGY: AN OVERVIEW

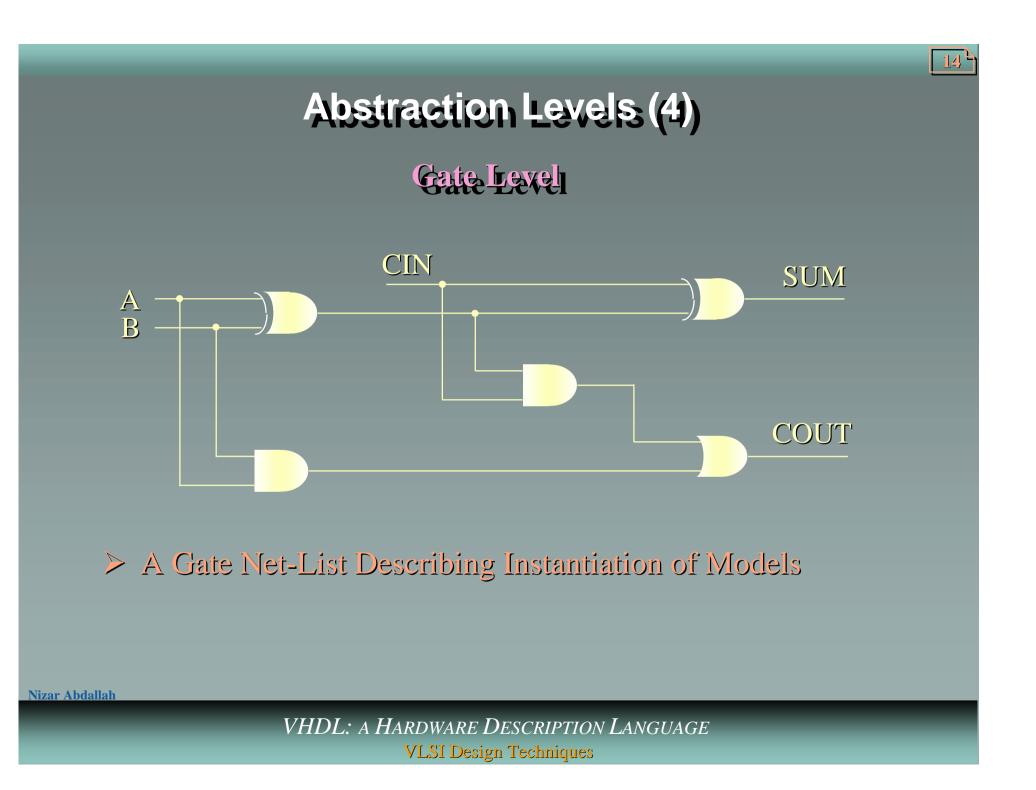

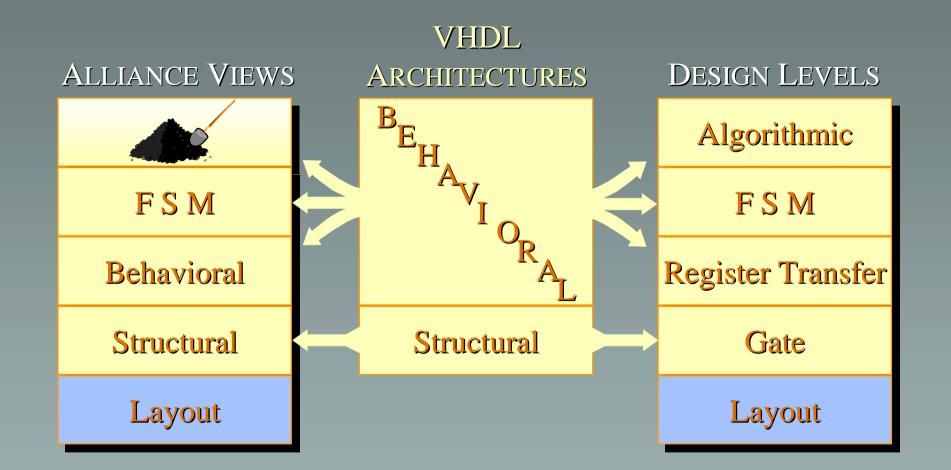

- **III ABSTRACTION LEVELS IN ALLIANCE**

- IV VHDL: A HARDWARE DESCRIPTION LANGUAGE

# Why an HDL ? (2)

3

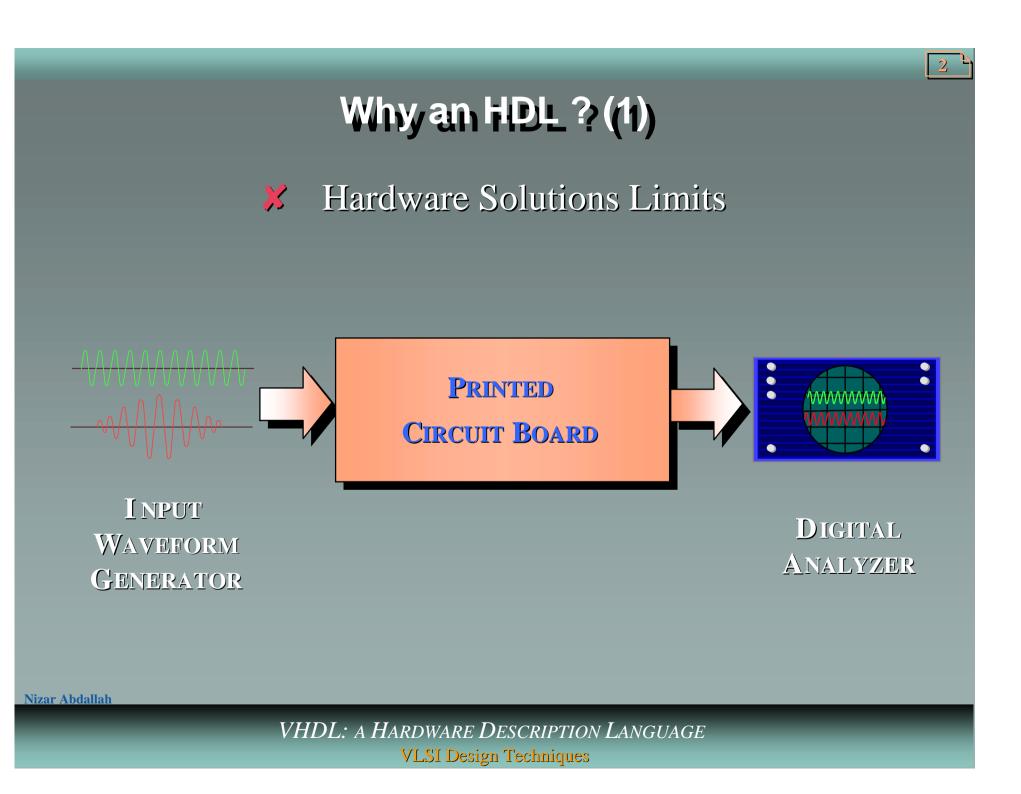

Increasing Complexity

Increasing Cost in Time & Investment

Increasing Knowledge Requirement

A Software Solution is Needed

# Why an HDL ?(3)

#### Programming Language not Suited

#### A Special Purpose Language : **HDL**

Nizar Abdallah

VHDL: A HARDWARE DESCRIPTION LANGUAGE

VLSI Design Techniques

# Why VHDL ? (1)

Circuit Manufacturers Fully Satisfied with their Proprietary HDLs...

Nizar Abdallah

VHDL: A HARDWARE DESCRIPTION LANGUAGE VLSI Design Techniques

# Why VHDL ? (2)

6

Problems for system manufacturers

✗ Different vendors ➡> different incompatible HDLs

X Impossible to verify a whole mixed-system

#

7

✗ Vendor dependency

####

#### A Standard HDL from the System Manufacturer's Point of View: V H D L

Nizar Abdallah

### VHDL

**Very High Speed Integrated Circuits (VHSIC)**

Hardware

Description

Language

Nizar Abdallah

VHDL: A HARDWARE DESCRIPTION LANGUAGE VLSI Design Techniques

# History

9

- 1981: an Extensive Public Review (DOD)

- 1983: a Request for Proposal

(Intermetrics, IBM, and Texas Instruments)

- 1986: VHDL in the Public Domain

- 1987: a Standard Language <u>VHDL'87</u> (IEEE-1076)

- 1992: a New Standard VHDL'92

### Advantages & Drawbacks

Standard

Open language

$10^{-10}$

Vendor independent

User definable

Wide capabilities

**X** Complex tools

X Slow tools

Nizar Abdallah

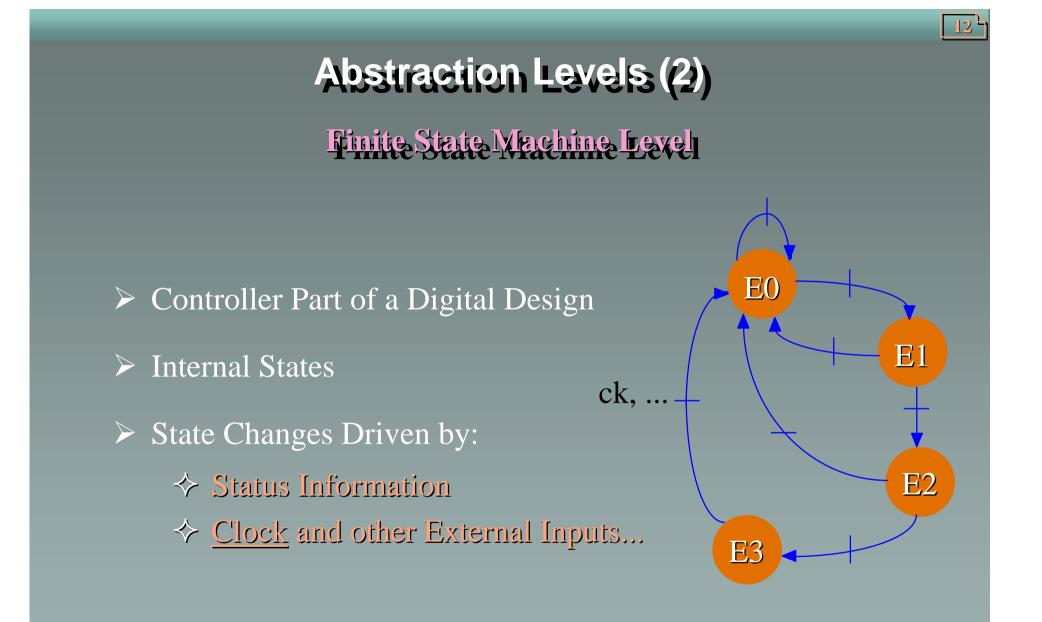

### Abstraction Levels (1)

11

Algorithmic Level

- Very High Abstraction Level

- > Functional Interpretation of a Discrete System

- > No Implementation Details

- > Sequential Program-Like Description

- > Programmer's Point of View

Nizar Abdallah

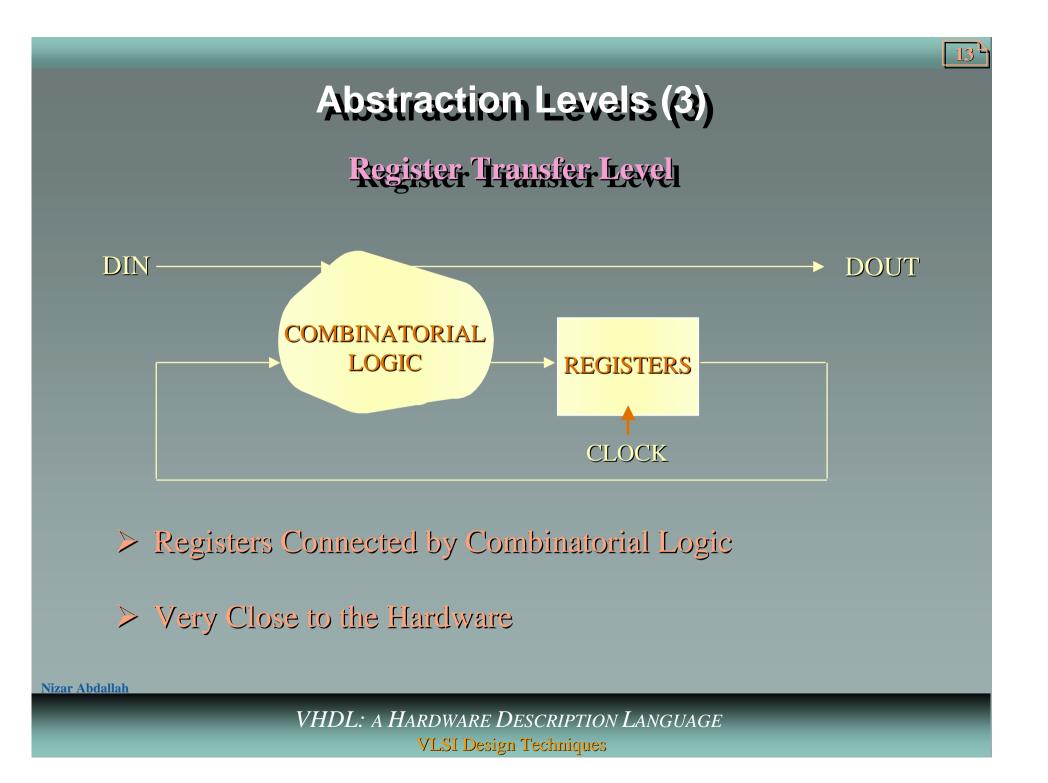

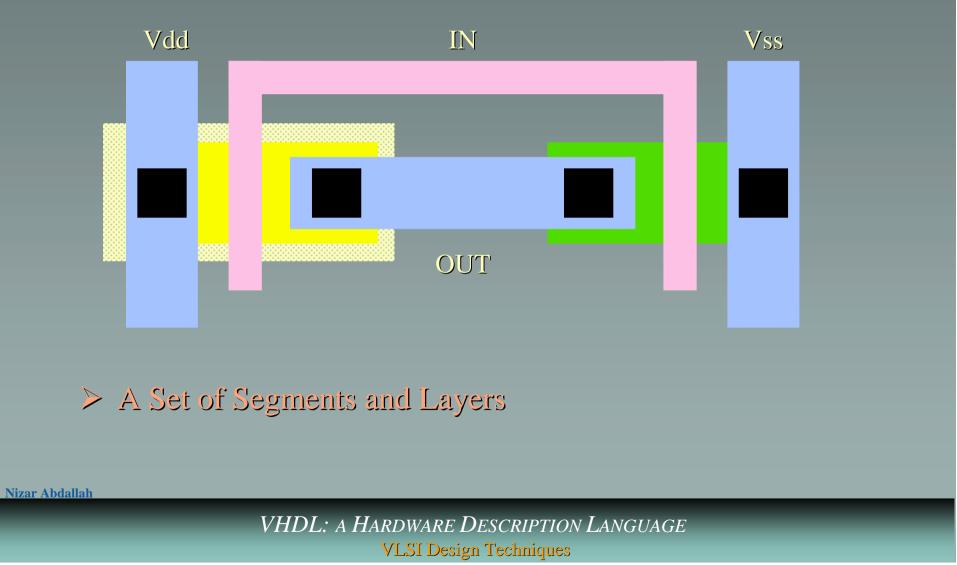

# Abstraction Levels (5)

15<sup>°</sup>

### Layout Level

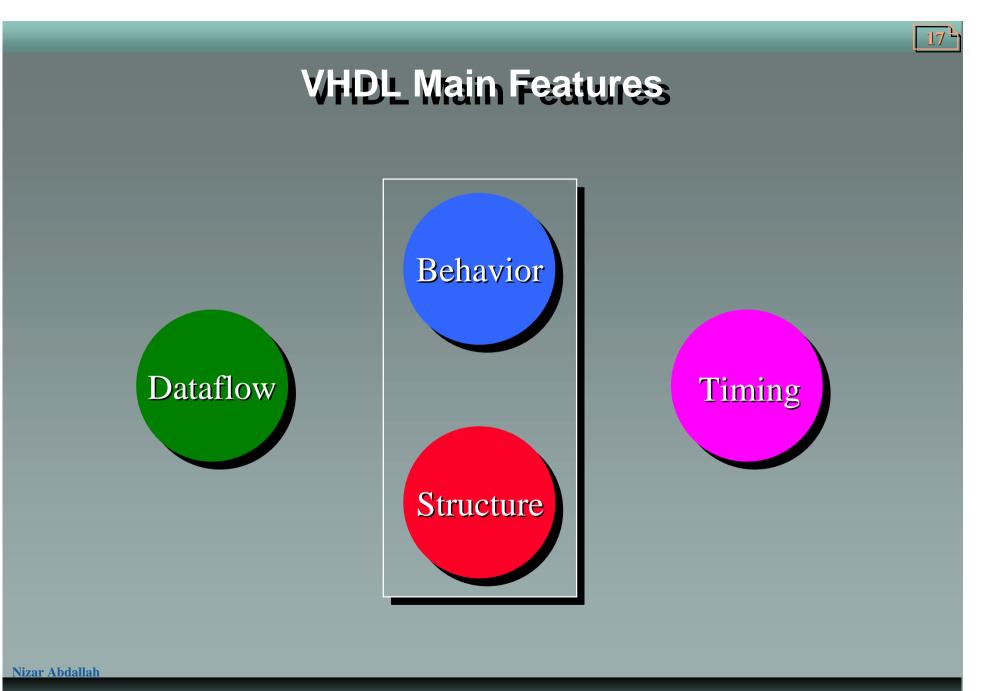

### VHDL Architectures

Nizar Abdallah

VHDL: A HARDWARE DESCRIPTION LANGUAGE VLSI Design Techniques

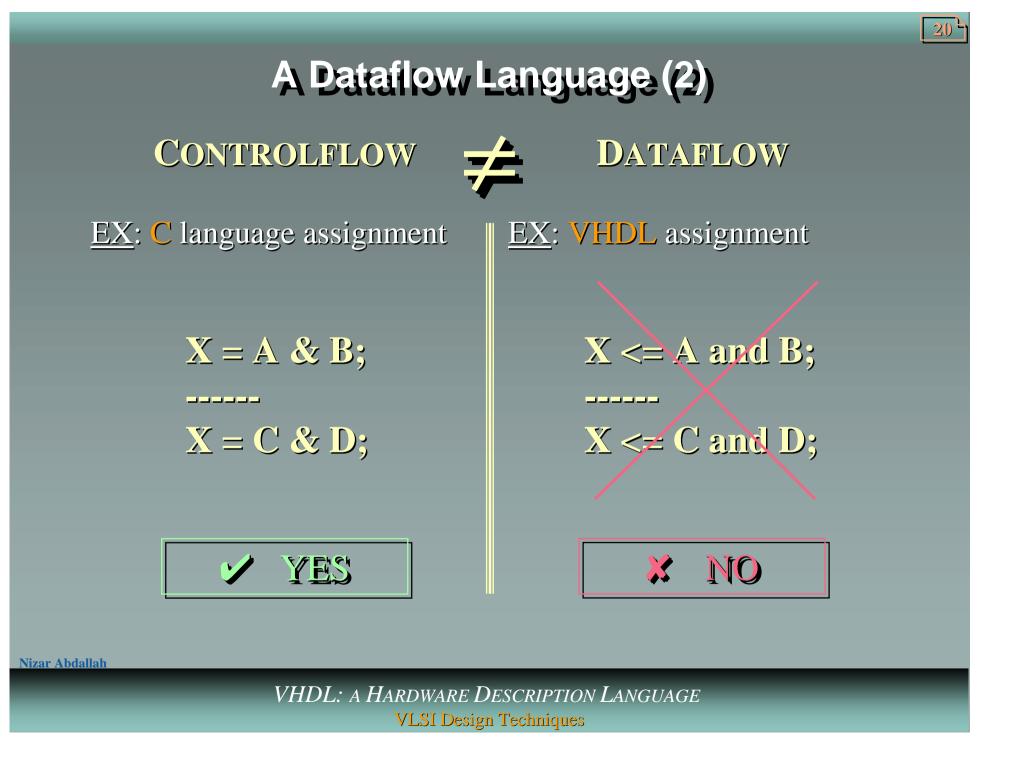

CONTROLFLOW

EX: C language assignment

$\mathbf{X} = \mathbf{A} \And \mathbf{B};$

X is computed out of A and B <u>ONLY</u> each time this assignment is executed EX: VHDL signal assignment

DATAFLOW

19

**X** <= **A** and **B**;

A <u>PERMANENT</u> link is created between A, B, and X

X is computed out of A and B <u>WHENEVER</u> A or B change

Nizar Abdallah