| $\widehat{\mathbb{H}}$                             |

|----------------------------------------------------|

| united national, scient and culti-<br>organization |

| (6                                                 |

| international ator                                 |

#### the

abdus salam international centre for theoretical physics

SMR.1073-2

## ICTP-UNU-Microprocessor Laboratory Fifth Course on Basic VLSI Design Techniques

9 November - 4 December 1998

VHDL, ALLIANCE

Nizar ABDALLAH Actel Corporation 955 East Arques Av. Sunnyvale, 94086-4533California U.S.A

These are preliminary lecture notes intended only for distribution to participants

| : .                                   |

|---------------------------------------|

|                                       |

|                                       |

| 4                                     |

| ,                                     |

|                                       |

|                                       |

| · •                                   |

|                                       |

|                                       |

| · · · · · · · · · · · · · · · · · · · |

| ;                                     |

|                                       |

|                                       |

| ;                                     |

The ALLANGE System

#### **NIZAR ABDALLAH**

#### LABORATOIRE MASI - EQUIPE CAO-VLSI

#### UNIVERSITE PIERRE ET MARIE CURIE (PARIS VI)

4, PLACE JUSSIEU, 75252 PARIS CEDEX 05 FRANCE

: Nizar.Abdallah@masi.ibp.fr

**2**:33 - 1 44 27 53 99

#### **OUTLINE**

- INTRODUCTION

- II DESIGN METHODOLOGY: AN OVERVIEW

- III ABSTRACTION LEVELS IN ALLIANCE

- IV VHDL: A HARDWARE DESCRIPTION LANGUAGE

- Y YHDL: THE ALLIANCE SUBSET

- VI ALLIANCE: A COMPLETE DESIGN SYSTEM

- VII- TODAY'S CHALLENGES IN CAD TOOLS

### THE MASI LABORATORY

#### UNIVERSITY PIERRE ET MARIE CURIE NATIONAL CENTRE OF SCIENTIFIC RESEARCH

#### 168 RESEARCHERS

| ARCHITECTURE               | 59 | <b>NETWORKS &amp; PERFORMANCES</b> | <b>30</b> |

|----------------------------|----|------------------------------------|-----------|

| <b>DISTRIBUTED SYSTEMS</b> | 36 | PARALLEL ALGORITHMS                | 17        |

#### THE MASI LABORATORY

# UNIVERSITY PIERRE ET MARIE CURIE NATIONAL CENTRE OF SCIENTIFIC RESEARCH

#### 168 RESEARCHERS

| • Architecture | 59 | <ul> <li>Networks &amp; Performances</li> </ul> | 30 |

|----------------|----|-------------------------------------------------|----|

|----------------|----|-------------------------------------------------|----|

• DISTRIBUTED SYSTEMS 36 • PARALLEL ALGORITHMS 17

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

SLIDE 3

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

# THE ARCHITECTURE GROUP

| CAD FOR VLSI           |   | ARCHITECTURE          |   |

|------------------------|---|-----------------------|---|

| PORTABLE LIBRARIES     | 9 | SUPERSCALAR PROCESSOR | 5 |

| VERIFICATION           | 7 | RCUBE ROUTER          | 8 |

| LOGIC SYNTHESIS        | 5 | RAPID COPROCESSOR     | 6 |

| ARCHITECTURE SYNTHESIS | 4 |                       |   |

| TEST                   | 5 |                       |   |

|                        |   |                       |   |

UPMC/MASI, Paris - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

SLIDE 4

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

#### **EDUCATION TARGET**

- Undergraduate Students: (≈ 80 Students and 72 Hours)

- **◆ ELECTRICAL ENGINEERING**

- **◆ COMPUTER SCIENCE**

- Postgraduate Students (≈ 60 Students and 300 Hours)

- **♦ DEA MEMI**

- ♦ DESS CIMI

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

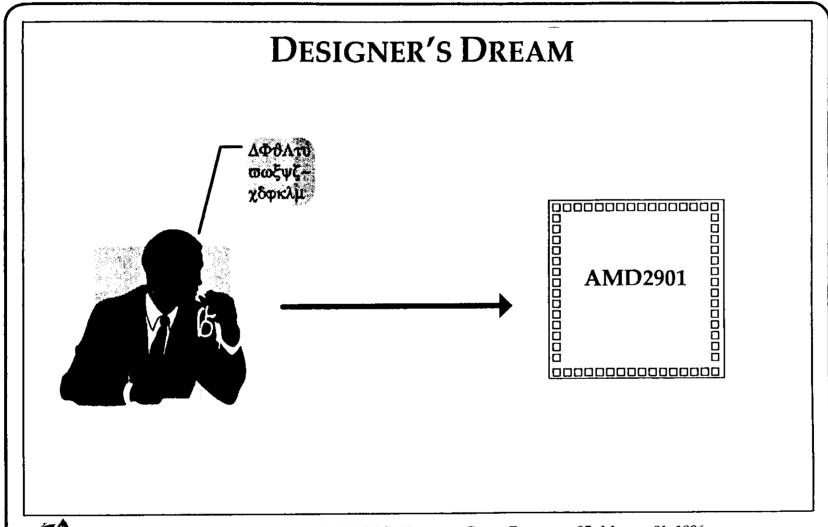

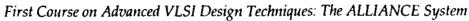

## THE ALLIANCE SYSTEM

- A COMPLETE SET OF CAD TOOLS FOR DIGITAL CMOS VLSI DESIGN.

- PROPOSES A DESIGN METHODOLOGY.

- PORTABLE, COMPACT AND EASY TO LEARN.

- ALLIANCE IS TOTALLY FREE.

UPMC/MASI, Paris - ICTP/UNESCO, Havana, Cuba, February 05- March 01, 1996 First Course on Advanced VLSI Design Techniques: The ALLIANCE System

#### **OUTLINE**

I - INTRODUCTION.

II - DESIGN METHODOLOGY: AN OVERVIEW.

III - ABSTRACTION LEVELS IN ALLIANCE.

IV - VHDL: AN OVERVIEW.

V - VHDL: THE ALLIANCE SUBSET.

VI - ALLIANCE: A COMPLETE DESIGN SYSTEM.

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

## MILLIONS OF SEGMENTS PUT TOGETHER.

## HOW TO DEAL WITH SUCH COMPLEXITY?

UPMC/MASI, Paris - ICTP/UNESCO, Havana, Cuba, February 05- March 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

### ONE MILLION OF TRANSISTORS CONNECTED TOGETHER.

ß STILL TOO COMPLEX....!!!

UPMC/MASI, Paris - ICTP/UNESCO, Havana, Cuba, February 05- March 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

#### HUNDRED THOUSAND OF CELLS CONNECTED TOGETHER.

#### **★ STILL TOO COMPLEX....!!!**

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

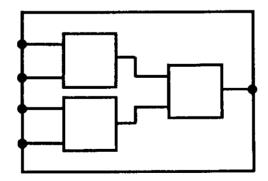

# DOZEN OF FUNCTIONAL BLOCKS THAT COMMUNICATE TOGETHER.

✓ I UNDERSTAND (OUF!!!)

UPMC/MASI, Paris - ICTP/UNESCO, Havana, Cuba, February 05- March 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

# A SET OF EQUATIONS THAT REFLECT THE WHOLE FUNCTIONALITY OF THE CIRCUIT.

```

entity adder is

port (

a, b: Bit;

c, d: bit

);

architecture adder is

a <= b or c

d <= b and c;

end;

```

✓ I UNDERSTAND WHAT THIS CIRCUIT IS SUPPOSED TO DO.

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

SO,

#### HOW TO DEAL WITH SUCH COMPLEXITY?

- **✓ ABSTRACTION**

- **✓** HIERARCHY

UPMC/MASI, Paris - ICTP/UNESCO, Havana, Cuba, February 05- March 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

## LEVELS OF ABSTRACTION

TO GO ACROSS THESE DIFFERENT LEVELS OF ABSTRACTION

I NEED

# A DESIGN METHODOLOGY

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

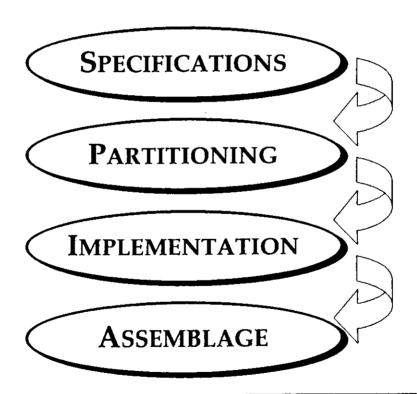

# DESIGN METHODOLOGY TOP-DOWN METHODOLOGY

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

# STEP 1: SPECIFICATIONS (1)

PUT DOWN THE CIRCUIT CONCEPT.

#### TWO REASONS:

- TO BE ABLE TO CHECK IT BEFORE MANUFACTURING.

- TO HAVE A REFERENCE MANUAL FOR COMMUNICATION.

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

#### STEP 1: SPECIFICATIONS (2)

COMMUNICATION LANGUAGE.

BETWEEN DIFFERENT PEOPLE ON THE PROJECT AND BETWEEN PEOPLE AND COMPUTERS.

- \* NO ORDINARY LANGUAGE.

- ✓ ACCURATE LANGUAGE.

- ✓ A LANGUAGE THAT CAN BE SIMULATED.

UPMC/MASI, Paris - ICTP/UNESCO, Havana, Cuba, February 05- March 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

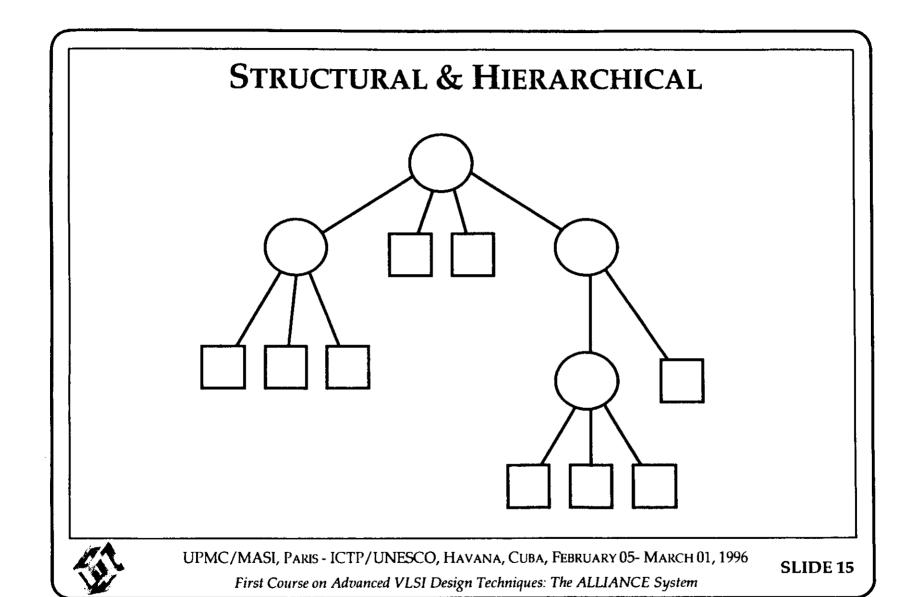

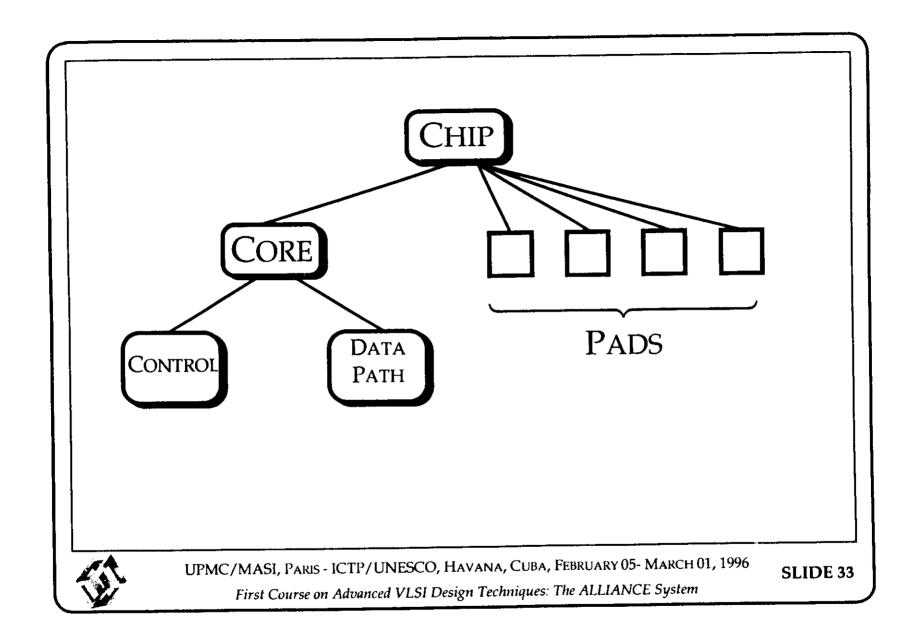

## **STEP 2: How To ?(1)**

VERY DIFFICULT STEP: RELAYS ON THE KNOW-HOW OF THE DESIGNER.

MAIN IDEA: TO SPLIT INTO SEVERAL SMALL PARTS.

DIVIDE AND CONQUER STRATEGY.

HIERARCHY.

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

### **STEP 2: How To ? (2)**

THE CUTTING IS GUIDED BY:

1. REGULARITY OR NOT.

- IDENTIFY REGULAR BLOCKS.

- IDENTIFY RANDOM LOGIC BLOCKS.

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

### **STEP 2: How To? (3)**

THE CUTTING IS GUIDED BY:

- 2. TIMING ASPECTS.

- COARSE ESTIMATION OF TIMING.

- LOOKING FOR A GOOD BALANCE.

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

#### **STEP 2: How To? (4)**

THE CUTTING IS GUIDED BY:

3. Topology.

- ALREADY IN MIND THE CIRCUIT FORM.

- AN IDEA ABOUT THE SIZE OF EACH PART.

- AN IDEA ABOUT THE ROUTING.

- OPTIMIZING SILICON AREA USAGE.

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

## **STEP 2: How To? (5)**

THE CUTTING IS GUIDED BY:

4. TECHNOLOGY.

- Using GAAS or CMOS?

- USING PALS OR STANDARD CELLS?

UPMC/MASI, Paris - ICTP/UNESCO, Havana, Cuba, February 05- March 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

#### **STEP 2: How To ? (6)**

THE CUTTING IS GUIDED BY:

5. CAD TOOLS.

• What tools do I have to make my circuit?

EX: NO SYNTHESIS TOOLS SO I TRY TO REDUCE THE RANDOM LOGIC PART.

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

## **STEP 3: IMPLEMENTATION**

EACH PART WILL BE IMPLEMENTED USING A PARTICULAR METHOD. WHEN I SPLIT MY CIRCUIT, I HAVE ALREADY DECIDED WHICH ONE.

UPMC/MASI, Paris - ICTP/UNESCO, Havana, Cuba, February 05- March 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

#### **STEP 4: ASSEMBLAGE**

THE ASSEMBLAGE IS DONE IN A HIERARCHICAL WAY, STARTING FROM THE LOWEST LEVEL.

## **CONCLUSION (1)**

AT EACH STEP, THE INFORMATION IS ENHANCED:

- 1. From the idea down to the specifications.

- 2. WHEN STRUCTURING THE MODEL IN AN OTHER WAY.

- 3. .....

- $\Rightarrow$  AT EACH STEP, A <u>VERIFICATION</u> IS TO BE DONE.

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

#### **CONCLUSION (2)**

ALL ALONG THE METHODOLOGY, WE HANDLED DIFFERENT VIEWS:

- 1. EQUATIONS.

- 2. Netlists.

- 3. LAYOUT.

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

SLIDE 23

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

## **CONCLUSION (3)**

THERE IS A METHOD.

UPMC/MASI, Paris - ICTP/UNESCO, Havana, Cuba, February 05- March 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

#### **OUTLINE**

I - INTRODUCTION.

II - DESIGN METHODOLOGY: AN OVERVIEW.

III - ABSTRACTION LEVELS IN ALLIANCE.

IV - VHDL: AN OVERVIEW.

V - VHDL: THE ALLIANCE SUBSET.

VI - ALLIANCE: A COMPLETE DESIGN SYSTEM.

UPMC/MASI, Paris - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

## 3 DIFFERENT VIEWS

ALL ALONG THE METHODOLOGY, WE HANDLED DIFFERENT VIEWS:

- 1. BEHAVIORAL VIEW (EQUATIONS).

- 2. STRUCTURAL VIEW (NETLISTS).

- 3. LAYOUT VIEW.

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

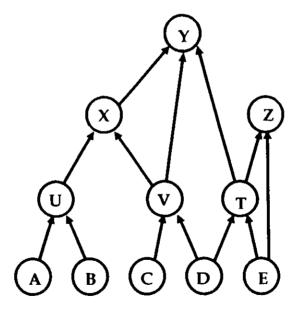

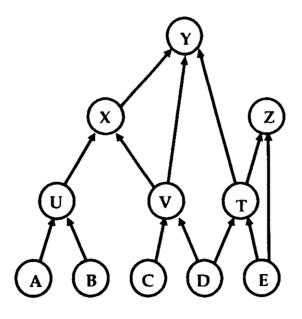

### **BEHAVIORAL VIEW (1)**

#### LOGICAL EQUATIONS

• DESCRIPTION FORMALISM.

A SET OF LOGICAL EQUATIONS (BOOLEAN) REPRESENTING BOOLEAN FUNCTIONS.

EXAMPLE:

$$U = A.(A+B)$$

$V = C.D$   $T = D \oplus E$

$$X = U.V$$

$Y = V + T + X$   $Z = T.E$

#### BEHAVIORAL VIEW (2)

#### LOGICAL EQUATIONS

• REPRESENTATION.

A DIRECTED ACYCLIC GRAPH INCLUDING THREE KINDS OF NODES: INPUT, INTERMEDIARY, OUTPUT.

EACH INTERMEDIARY OR OUTPUT NODE IS ASSOCIATED TO A LOGICAL EXPRESSION.

EACH NODE IS ASSOCIATED TO A VARIABLE NAME.

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

### **BEHAVIORAL VIEW (3)**

#### **BOOLEAN NETWORK**

• REPRESENTATION.

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

### STRUCTURAL VIEW (1)

FOR ALL THESE VIEWS, WE ARE LOOKING FOR BASIC CONCEPTS: COMPLETELY INDEPENDENT FROM A GIVEN LANGUAGE.

#### IN THE STRUCTURAL VIEW:

- CONNECTORS: ID, DIRECTION, ETC....

- SIGNALS: ID, TYPE (EXTERNAL OR NOT), ETC....

- INSTANCE: ID, MODEL NAME, PORTS, ETC....

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

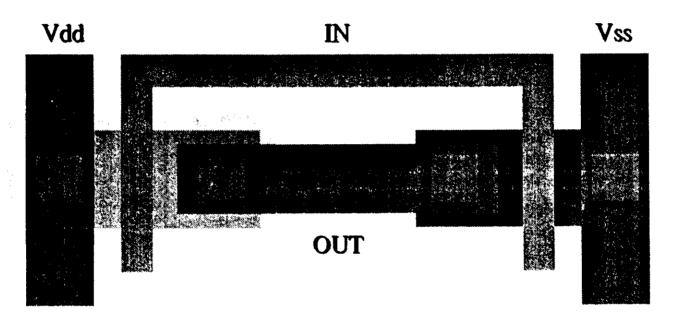

### LAYOUT VIEW (1)

SYMBOLIC LAYOUT: PRINCIPLES

- PORTABILITY

- SIMPLICITY

- ROBUSTNESS

UPMC/MASI, Paris - ICTP/UNESCO, Havana, Cuba, February 05- March 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

### LAYOUT VIEW (2)

SYMBOLIC LAYOUT: OUR APPROACH

THIN FIXED GRID, SYMBOLIC LAYOUT.

DISTANCES FORM CENTER TO CENTER  $\Rightarrow$  GOOD DENSITIES.

SPECIAL SYMBOLIC LAYOUT EDITOR.

AUTOMATIC TRANSLATION FROM SYMBOLIC TO PHYSICAL.

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

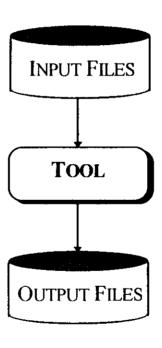

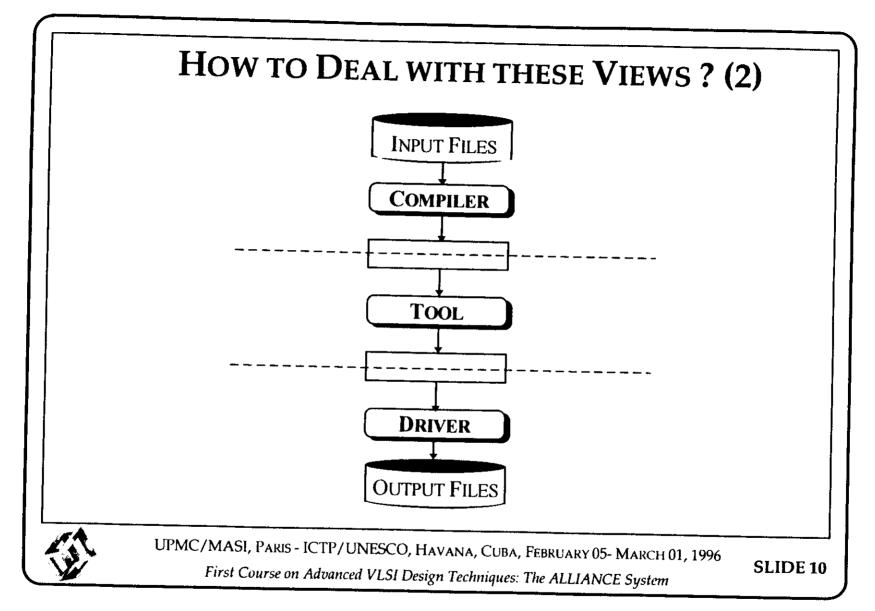

### How to Deal with these Views? (1)

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

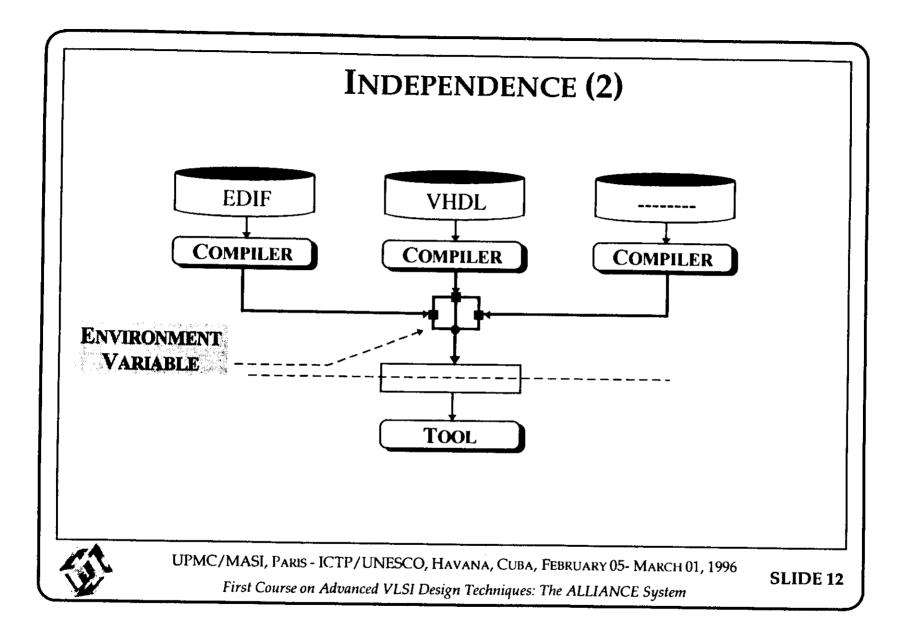

#### INDEPENDENCE (1)

A MAJOR IDEA IN ALLIANCE IS ITS <u>INDEPENDENCE</u> FROM ANY GIVEN LANGUAGE.

**IDENTIFY THE CONCEPTS THAT:**

- DO NOT DEPEND ON A LANGUAGE.

- ✓ DEPENDS ON THE ABSTRACTION LEVEL.

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

### OMITTIME

- I INTRODUCTION

- II DESIGN METHODOLOGY: AN OVERVIEW

- III ABSTRACTION LEVELS IN ALLIANCE

- IV VHDL: A HARDWARE DESCRIPTION LANGUAGE

# **Why an hat** ?(小)

**X** Hardware Solutions Limits

I NPUT

WAVEFORM

GENERATOR

DIGITAL ANALYZER

# May 410 HDL ? (2)

- **✗** Increasing Complexity

- ✗ Increasing Cost in Time & Investment

- ✗ Increasing Knowledge Requirement

A Software Solution is Needed

# **Why 部肿**(多)

\* Programming Language not Suited

A Special Purpose Language: HDL

#

Circuit Manufacturers

Fully Satisfied with their

Proprietary HDLs...

# Why VHDL ?(2)

### Problems for system manufacturers

- ★ Different vendors different incompatible HDLs

- ✗ Impossible to verify a whole mixed-system

## **Why KHIDIT** 5 (39)

- ✗ Vendor dependency

- ✗ Design documentation exchange

A Standard HDL from the System Manufacturer's Point of View: V H D L

### **VHDL**

## **Very High Speed Integrated Circuits (VHSIC)**

Hardware

**Description**

Language

## History

- 1981: an Extensive Public Review (DOD)

- 1983: a Request for Proposal

(Intermetrics, IBM, and Texas Instruments)

- 1986: VHDL in the Public Domain

- 1987: a Standard Language VHDL'87 (IEEE-1076)

- 1992: a New Standard VHDL'92

# Advantages & Drawbacks

Standard

Open language

- ✓ Vendor independent

- ✓ User definable

- ✓ Wide capabilities

- **X** Complex tools

- **X** Slow tools

i d**ala i da i limba di** differenti

### Abstraction revels (4)

### Algorithmic Lexel

- > Very High Abstraction Level

- > Functional Interpretation of a Discrete System

- > No Implementation Details

- > Sequential Program-Like Description

- > Programmer's Point of View

# Abstraction Levels (2)

### Finite State Machine Level

ck.

- ➤ Controller Part of a Digital Design

- > Internal States

- > State Changement Driven by:

- **♦** Status Information

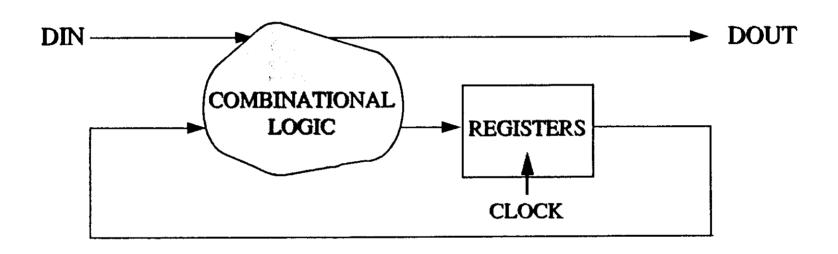

## Abstraction Levels (3)

### Register-Transfer-Level

- > Registers Connected by Combinational Logic

- > Very Close to the Hardware

# Abstraction Levels (4)

### Gate Level

➤ A Gate Net-List Describing Instantiation of Models

## Appetraction revele (2)

### **Чахоны Чехен**

➤ A Set of Segments and Layers

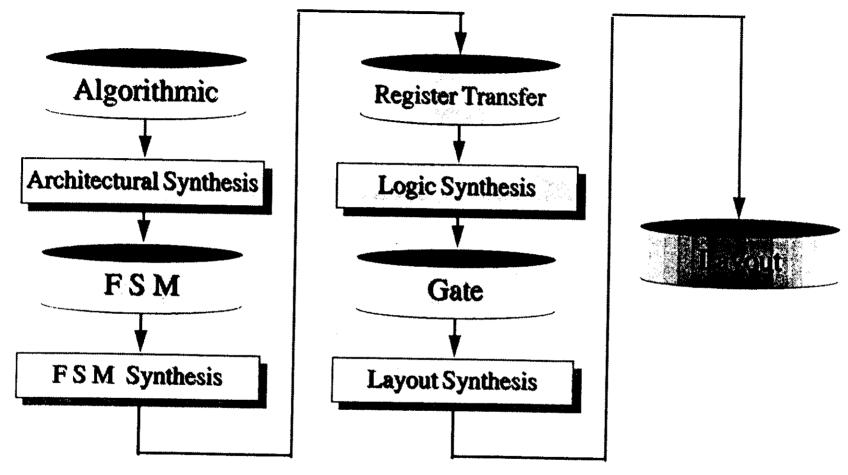

# Synthesis Flow

## VHPL Wain Features

# WHADIT VAIGHIFFE STATION TRAINER

**ALLIANCE VIEWS**

and the first of the

VHDL ARCHITECTURES

**DESIGN LEVELS**

Algorithmic

FSM

Register Transfer

Gate

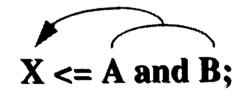

# A Dataflow Language (11)

#### **CONTROLFLOW**

#### **DATAFLOW**

EX: C language assignment

X = A & B;

X is computed out of A and B ONLY each time this assignment is executed

**EX:** VHDL signal assignment

A PERMANENT link is created between A, B, and X

X is computed out of A and B WHENEVER A or B change 5

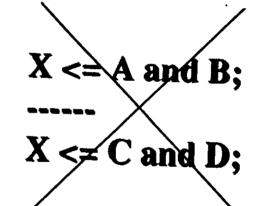

# A Peterrow Language (2)

## **CONTROLFLOW**

### **DATAFLOW**

EX: C language assignment

$$X = A \& B$$

;

X = C & D;

EX: VHDL assignment

### Basic Structures

### Basic Building Blocks

- > Entity

- > Architecture

- > Configuration

- > Package

- > Library

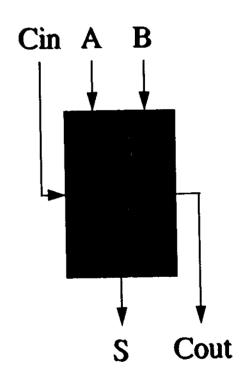

# Entity Declaration (4)

## The External Aspect of a Pesign Unit

# Entity Declaration (2)

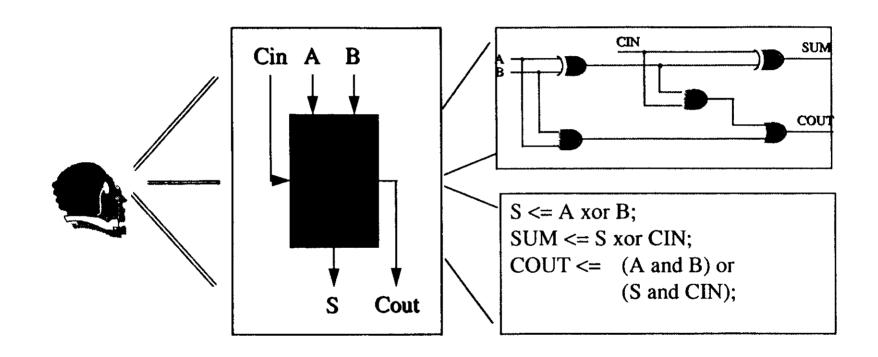

### Example

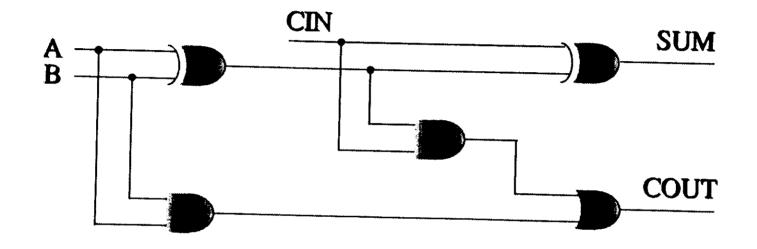

entity FULL\_ADDER is port (A, B, Cin: in BIT; :(out)BIT S, Cout end FULL\_ADDER; MODE: in, out, inout... **DATA TYPE**

# Arichitectures (11)

# The Internal Aspect of a Design Unite

architecture architecture\_name of entity\_name is

{architecture\_declarative\_part}

begin

{architecture\_descriptive\_part}

end [architecture\_name];

- Collection of <u>CONCURRENT</u> Statements Executed in <u>PARALLEL</u>

- ➤ Concurrent Statements Communicate through <u>SIGNALS</u>

## Arichitectures (2)

### A Behavioral Style

```

entity FULL_ADDER is

port (A, B, Cin: in BIT;

S, Cout : out BIT);

end FULL_ADDER;

architecture DATAFLOW of FULL_ADDER is

signal X : BIT;

begin

X \ll A \times B;

S <= S xor Cin after 10 ns;

Cout <= (A and B) or (X and Cin) after 5 ns;

end DATAFLOW;

```

## Arichitectures (3)

### A Structurali Style

architecture STRUCTURE of FULL\_ADDER is component HALF\_ADDER

port (I1, I2 : in BIT;

Carry, S: out BIT);

end component;

component OR\_GATE

port (I1, I2 : in BIT;

O : out BIT);

end component;

signal X1, X2, X3: BIT;

PARTINA; PARTI

### · ...

### Arichitectures (4)

### A Striucturali Style

```

begin

```

HA1: HALF\_ADDER port map (

I1 => A, I2 => B, Carry => X1, S => X2);

HA2: HALF\_ADDER port map (

I1 => X2, I2 => Cin, Carry => X3, S => S);

OR1: OR\_GATE port map (

I1 => X1, I2 => X3, O => Cout);

end STRUCTURE;

DESCRIPTIVE PART

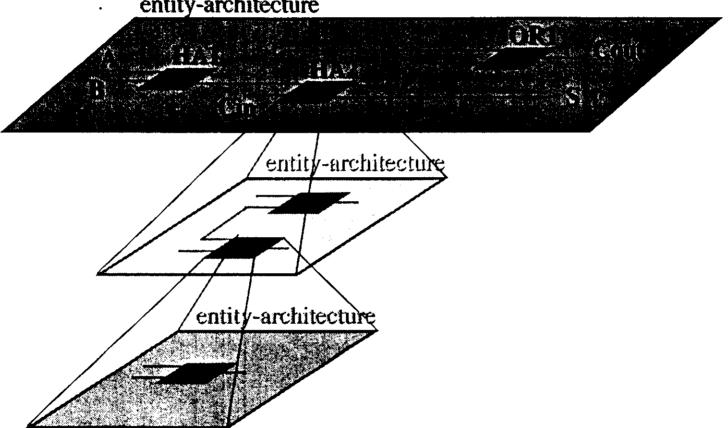

### Arichitectures (5)

Structural Style to represent Hierarchy

entity-architecture

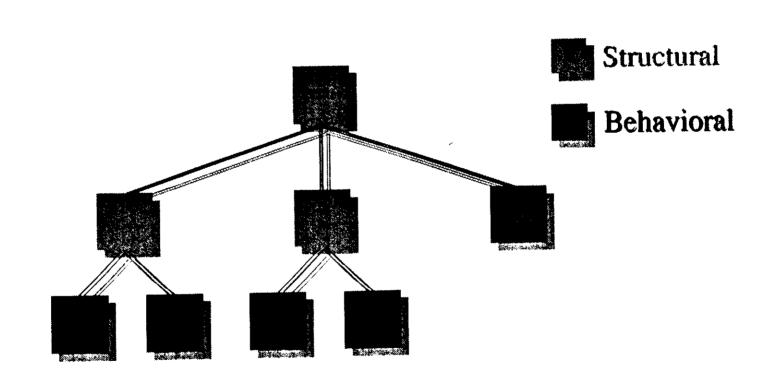

### Arichitectures (6)

### Structural & Behavioral in a Design Tree

### Arichitectures (77)

### entity/architecture: a One to Many Relationship

### Configurations (4)

Specification Inside the Architecture Body

for instantiation\_list: component\_name use binding\_indication;

use library\_name.entity\_name [(architecture\_name)];

> Binding a couple "entity/architecture" to each instance

### Configurations (2)

### Peclaration as a Separate Design Unit

configuration configuration\_name of entity\_name is

for { architecture | component } binding\_indication;

end [configuration\_name];

- > Can be compiled separately and stored in a library

- > It defines a configuration for a particular entity

### Packages

### Globali Pesign Unik

- > Same declarations visible by a number of design entities

- > May contain subprograms, components, signals, ...

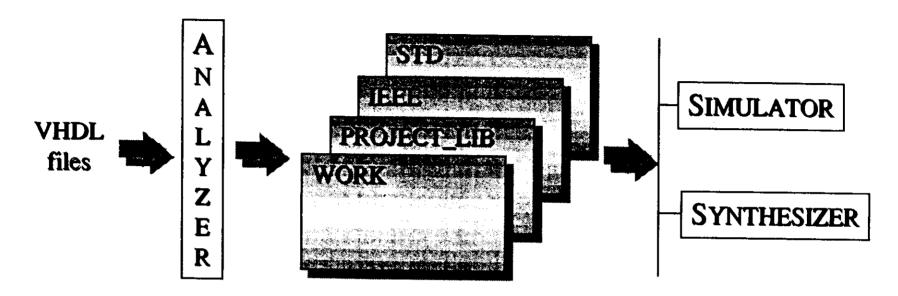

### Design Libraries

library library\_name;

use library\_name.package\_name.all;

> May contain: packages, entities, architectures, configurations

### Optifects (4))

### Three Classes

- > Constants

- ♦ Initialized to a specific value and never modified constant MSB : INTEGER := 5;

- > Variables

- ♦ Used to hold temporary data

- ♦ Only used within processes & subprograms variable DELAY : INTEGER range 0 to 15 := 0;

### Dette Objects (2)

### Three Classes.

- > Signals

- **♦ Used to communicate between processes**

- **♦ When declared in a package : Global Signals**

- **♦** Also declared within entities, blocks, architectures

- Can be used but not defined in processes and subprograms

signal CLK: BIT;

# Pate Trypes (h) Frumeration Types

> The first identifier is the default value

type COLOR is (RED, ORANGE, YELLOW);

type TERNARY is ('1', '0', 'X');

variable X: COLOR;

signal Y: TERNARY;

### Poetra Trypes (2)

Integer Types

- > The range must be specified

- ➤ No logical operations on integer type MEMORY\_SIZE is range 1 to 2048;

### Dette Trypes (3)

### Predefined VHDL Data Types IEEE 1076-1987 Standard Package

- > BOOLEAN: (false, true)

- > BIT: ('0', '1')

- > CHARACTER

- > INTEGER: range -2 147 483 647 to +2 147 483 647

- > NATURAL : Subtype of INTEGER (Non Negative)

- > POSITIVE : Subtype of INTEGER (positive)

- > BIT\_VECTOR: array of BIT values

- > STRING: array of CHARACTERS

- > REAL: range -1.0E+38 to +1.0E+38

- > TIME: Physical type used for simulation

### Dette Trypes (41)

## Array Types

> Constrained Array

type VEC\_64 is array (0 to 63) of INTEGER;

variable S: VEC\_64;

variable S1: INTEGER;

S1 := S(1);

> Unconstrained Array

type BIT\_VECTOR is array (POSITIVE range <>) of BIT; signal S : BIT\_VECTOR (4 downto 0);

Multiple Dimentional Arrays type TWO\_D is array (0 to 7, 0 to 3) of INTEGER;

# Pete Types (5) Record Types

type DATE is

record

YEAR: INTEGER range 1900 to 1999;

MONTH: INTEGER range 1 to 12;

DAY: INTEGER range 1 to 31;

end record;

signal S: DATE;

variable Y: INTEGER range 1900 to 1999;

Y := S.YEAR;

### Poetra Trypes (6)

### STD\_4.061C Pata Types IFFF 1164-1993 Standard 4.0gic Package

| type STD_ULOG | IC is ( |                              |

|---------------|---------|------------------------------|

| ${f U}'$      | ***     | Uninitialized                |

| <b>'X'</b>    |         | Forcing Unknown              |

| <b>'O'</b>    |         | Forcing Low                  |

| '1'           |         | Forcing High                 |

| <b>'Z'</b>    |         | High Impedance // Unresolved |

| 'W'           |         | Weak Unknown // Pata Type    |

| <b>'L'</b>    |         | Weak Low                     |

| Ή'            |         | Weak High                    |

| (1-1)         |         | Don't Care                   |

| 7.            |         | Used in Synthesis            |

VHDL: A HARDWARE DESCRIPTION LANGUAGE

# Dete Types (7)) STD\_4964C Data Types IFFF 4164-1993 Standard 49gic Package

- > STD\_LOGIC: Resolved (Resolution Function provided)

- > STD\_LOGIC\_VECTOR

- > STD\_ULOGIC\_VECTOR

### Dette Trypes (77)

### Also,

- > FILE: Useful for RAM Values or Stimuli Files

- > ACCESS: Like "pointers" in High Level Languages

- > TEXT: FILE of STRING (TEXTIO package)

- > LINE: access STRING (TEXTIO package)

### Subtypes

## Subsets of Other Types

- > To Insure Valid Assignments

- > Inherit All Operators and Subprograms from the Parent Type

subtype DIGIT is INTEGER range 0 to 9;

# Operators Six Classes

| LOGIC OPERATOR         | and, or, nand, nor, xor |

|------------------------|-------------------------|

| RELATIONAL OPERATOR    | =,/=,<,<=,>,>=          |

| ADDING OPERATOR        | +,-,&                   |

| SIGN                   | +,-                     |

| MULTIPLYING OPERATOR   | * , / , mod , rem       |

| MISCELLANEOUS OPERATOR | **, abs, not            |

### PRECEDENCE ORDER

- > Literals: 'x', "1100", 752, B"11001", O"277", X"4C"

- ♦ numeric, character, enumeration, or string

- > Identifiers:

- ♦ starts with (a-z) followed by letters, '\_', or digits

- **♦ Not case-sensitive**

- **♦** Some are reserved words

- > Indexed Names: S(3), DATA (ADDR)

### Operands (2)

- > Slice Names: variable ORG: BIT\_VECTOR (7 downto 0)

- **♦ Sequence of elements of an array object**

- > Aliases: alias MSB: BIT is ORG (7)

- ♦ New name for a part of a range of an array

- > Aggregates

- > Qualified Expressions

- > Function Calls

- > Type Conversions

### Operands (3)

## Attributes Names A Pata Attached to VHD4 Objects

- > S'LEFT: Index of the leftmost element of the data type

- > S'RIGHT: Index of the rightmost element of the data type

- > S'HIGH: Index of the highest element of the data type

- > S'LOW: Index of the lowest element of the data type

- > S'RANGE: Index range of the data type

- > S'REVERSE\_RANGE : Reverse index range

- > S'LENGTH: Number of elements of an array

### Operands (4)

## Attributes Names A Data Attached to VHDL Signals

- > S'EVENT : A change value at the current simulation time

- > S'STABLE : No change value at the current simulation time if (CK = 0 and not CK'STABLE)

**>** .....

### Natural Concept for Describing Hardware

- > Concurrent Signal Assignment

- > Conditional Signal Assignment

- > Selected Signal Assignment

- **▶** Block Statement

- > Concurrent Assertion Statement

- > Process Statement

### Concurrent Signal Assignment

### Represent an Equivalent Process Statement

target <= expression [ after time\_expression ];</pre>

- > Signals are associated with <u>Time</u>

- > With "after", the assignment is scheduled to a future simulation time

- ➤ Without "after", the assignment is scheduled at a <u>Delta</u> <u>Time</u> after the current simulation time

### Conditional Signal Assignment

More than One Expression.

```

target <= { expression [ after time_exp ] when condition else }

expression [ after time_exp ];

```

- > Condition / expression except for the last expression

- > One and only one of the expressions is used at a time

### Selected Signal Assignment

### Only One Target

> "when others" is used when all the cases were not treated

### Block Statement (1)

A Set of Concurrent Statements

> Used to organize a set of concurrent statements hierarchically

### Block Statement (2)

### In Synchronous Descriptions.

latch: block (CLK = '1')

begin

$Q \leftarrow GUARDEDD;$

end block latch;

计有9067年42

### Assertion Statement

### Only One Target

### assert condition

```

[ report error_message ] [ severity_level ];

```

- > If the condition is false, it reports a diagnostic message

- > Useful for detecting condition violation during simulation

- > Not used in synthesis

### Process Statement (11)

### A Set of Sequential Statements.

- > All processes in a design executes **CONCURRENTLY**

- > At a given time, <u>ONLY ONE</u> sequential statement executed within each process

- > Communicates with the rest of a design through signals

### Process Statement (2)

A Pseudo, Infinite Loop,

```

process

begin

sequential_st_inent_1;

sequential_s = rent_12;

sequential_st_nent_n;

end process;

```

> A Synchronization Mecanism is Needed

## Process Statement (3) Synchronization, Mecanism,

wait

```

[ on signal_name { signal_name } ]

[ until boolean_expression ]

[ for time_expression ];

```

> Objects being waited upon should be **SIGNALS**

### Process Statement (4)

The Sensitivity List

Equivalent to a "wait" statement as the last statement wait on sensitivity\_list;

### Sequential Statement

### Insight Into Statements within Processes.

- > Variable Assignment

- > Loop

> Signal Assignment

> Next

> **If**

> Exit

> Case

> Wait

> Null

> Procedure Calls

> Assertion

> Return

# Variable Assignment Statement

# Immediate Assignment

target\_variable := expression;

- > Always executed in **ZERO SIMULATION TIME**

- > Used as temporary storages

- > Can not be seen by other concurrent statements

# Signal Assignment Statement (1)) Defines a DRIXER of the Signal

target\_signal <= [ transport ] expression [ after time\_expression ];

- > Within a process, **ONLY ONE** driver for each signal

- ➤ When assigned in multiple processes, it has <u>MULTIPLE</u> <u>DRIVERS</u>. A <u>RESOLUTION FUNCTION</u> should be defined

# **CONCLUSION (1)**

VHDL IS AN OPEN LANGUAGE WITH MANY FEATURES.

WITH VHDL, ANY DISCRETE SYSTEM CAN BE MODELED.

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

# CONCLUSION (2)

EACH USER HAS ITS OWN NEEDS DEPENDING ON:

- HIS BACKGROUND.

- HIS ENVIRONMENT.

WE DEFINED A SUBSET OF VHDL.

UPMC/MASI, Paris - ICTP/UNESCO, Havana, Cuba, February 05- March 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

# CONCLUSION (3)

WHY?

Complex language  $\Rightarrow$  Developing a compiler is hard and time consuming.

UPMC/MASI, Paris - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

SLIDE 22

# **CONCLUSION (4)**

WHY?

#### **EDUCATIONAL NEEDS:**

- Understanding time.

- Univocal (One way for describing a register).

UPMC/MASI, Paris - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

SLIDE 23

# **CONCLUSION (5)**

WHY?

OUR ENVIRONMENT: VLSI.

UPMC/MASI, Paris - ICTP/UNESCO, Havana, Cuba, February 05- March 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

#### **OUTLINE**

- I INTRODUCTION.

- II DESIGN METHODOLOGY: AN OVERVIEW.

- III ABSTRACTION LEVELS IN ALLIANCE.

- IV VHDL: AN OVERVIEW.

- V VHDL: THE ALLIANCE SUBSET.

- VI ALLIANCE: A COMPLETE DESIGN SYSTEM.

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

SLIDE 1

#### WHY AND How?

#### WHY?

- DEVELOPMENT TIME.

- EDUCATION CONSTRAINTS.

- THE CURRENT ENVIRONMENT.

CRITERIONS FOR THE SUBSET DEFINITION.

UPMC/MASI, Paris - ICTP/UNESCO, Havana, Cuba, February 05- March 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

# **TOOLS REQUIREMENTS (1)**

#### WHICH TOOLS USE VHDL?

- SYNTHESIS.

- FORMAL PROOVER.

- PLACER & ROUTER.

- SIMULATOR.

- FUNCTIONAL ABSTRACTOR.

UPMC/MASI, Paris - ICTP/UNESCO, Havana, Cuba, February 05- March 01, 1996 First Course on Advanced VLSI Design Techniques: The ALLIANCE System

# TOOLS REQUIREMENTS (2)

#### SYNTHESIS TOOLS.

- \* A REGISTER MUST BE IDENTIFIED IN A SYNTACTICAL WAY.

- \* A BUS MUST BE IDENTIFIED IN A SYNTACTICAL WAY.

- SIGNALS MUST HAVE THE **BIT** TYPE ('0', '1').

- X NO TIMING.

#### FORMAL PROOVER.

- A REGISTER MUST BE IDENTIFIED IN A SYNTACTICAL WAY.

- A BUS MUST BE IDENTIFIED IN A SYNTACTICAL WAY.

UPMC/MASI, Paris - ICTP/UNESCO, Havana, Cuba, February 05- March 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

# **TOOLS REQUIREMENTS (3)**

#### FUNCTIONAL ABSTRACTOR.

THE VHOL SUBSET MUST BE AS CLOSE AS POSSIBLE TO THE HARDWARE.

PLACER & ROUTER.

NO MIXING BETWEEN STRUCTURAL AND BEHAVIORAL VIEWS. SIMULATOR.

- NO ABSTRACT TYPES.

- X NO TIMING.

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

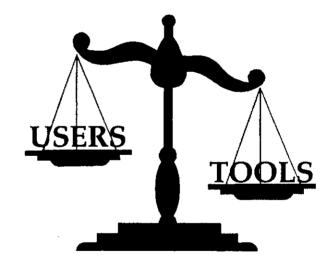

# **USERS REQUIREMENTS**

LOOKING FOR THE LARGEST SUBSET.

#### THE GOOD VHDL SUBSET:

- ✓ LETS THE USER DESCRIBE HIS CIRCUIT EASILY.

- DO NOT DETERIORATE THE TOOL WITH A COMPLEX LANGUAGE.

UPMC/MASI, Paris - ICTP/UNESCO, Havana, Cuba, February 05- March 01, 1996

SLIDE 6

#### THE EXTERNAL ASPECT

IN VHDL A CIRCUIT (DESIGN UNIT) HAS TWO ASPECTS:

1. The external aspect: (External visibility)

**ALLIANCE**

**✓**NAME

✓INTERFACE (PORT)

**×**COLOR

**≭** Temperature

X \_\_\_\_\_

UPMC/MASI, Paris - ICTP/UNESCO, Havana, Cuba, February 05- March 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

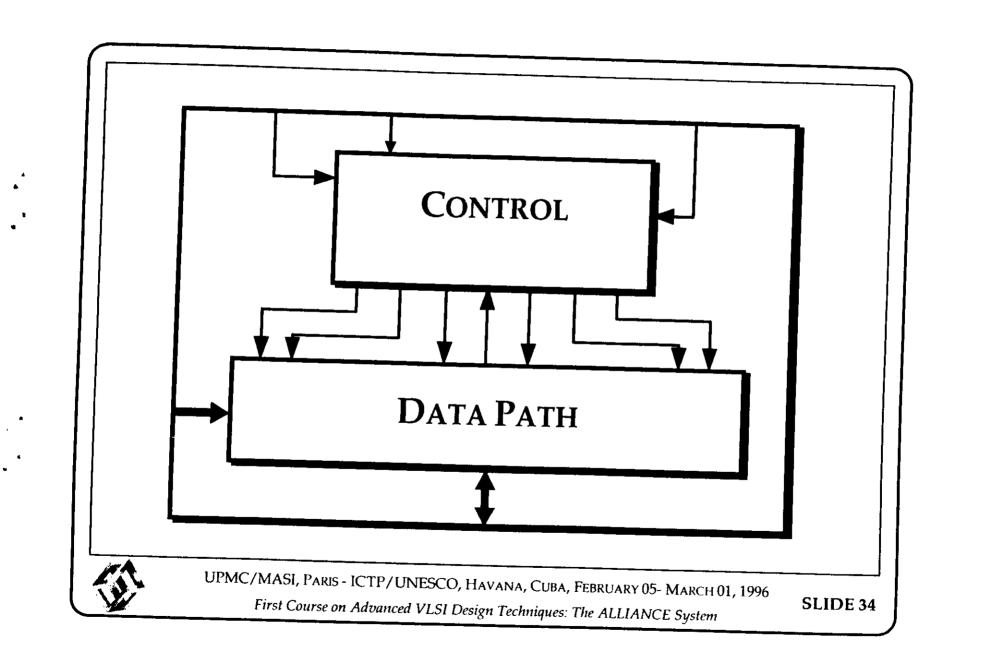

# THE INTERNAL ASPECT (1)

IN VHDL A CIRCUIT (DESIGN UNIT) HAS TWO ASPECTS:

2. THE INTERNAL ASPECT: (FUNCTIONALITY)

**ALLIANCE**

**✓**STRUCTURAL

✓ DATA FLOW

how it works

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

#### THE INTERNAL ASPECT (2)

IN THE STRUCTURAL INTERNAL ASPECT, WE DESCRIBE THE CIRCUIT AS A NETWORK OF SMALLER CIRCUITS.

THE FOLLOWING OBJECTS ARE USED:

- SIGNAL.

- COMPONENT (MODEL).

- INSTANCE.

UPMC/MASI, Paris - ICTP/UNESCO, Havana, Cuba, February 05- March 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

# EXTERNAL ASPECT: EXAMPLE (1) ENTITY PARITY IS PORT ( Input/output mode A: IN BIT; C: IN BIT; C: IN BIT; P: OUT BIT

END PARITY;

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

**SLIDE 10**

```

EXTERNAL ASPECT: EXAMPLE (2)

ENTITY ADDER_32 IS

PORT (

A: IN BIT_VECTOR (31 DOWNTO 0);

B: IN BIT_VECTOR (31 DOWNTO 0);

CIN: IN BIT;

SUM: OUT BIT_VECTOR (31 DOWNTO 0);

COUT: OUT BIT

END;

```

UPMC/MASI, Paris - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

SLIDE 11

# **INTERNAL STRUCTURAL EXAMPLE (1)** ARCHITECTURE PSTRUCT OF PARITY IS COMPONENT XOR\_Y PORT ( I0: IN BIT; I1 : IN BIT; T: OUT BIT **DECLARATIVE PART** END COMPONENT; SIGNAL PARITY\_AB : BIT; SIGNAL PARITY\_CD : BIT;

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

# **INTERNAL STRUCTURAL EXAMPLE (2)**

```

BEGIN

INSTANCE_AB: XOR_Y

PORT MAP (

I0 \Rightarrow A

I1 \Rightarrow B,

T \Rightarrow PARITY\_AB

DESCRIPTION

PART

INSTANCE_CD: XOR_Y

PORT MAP (

I0 \Rightarrow C

I1 \Rightarrow D,

T \Rightarrow PARITY\_CD

```

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

# **INTERNAL STRUCTURAL EXAMPLE (3)**

```

INSTANCE_ABCD: XOR_Y

PORT MAP (

I0 \Rightarrow PARITY\_AB,

I1 \Rightarrow PARITY\_CD,

T \Rightarrow P

);

END;

```

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

# INTERNAL BEHAVIORAL ASPECT (1)

DESCRIBING EQUATIONS BETWEEN INPUTS AND OUTPUTS.

- BOOLEAN FUNCTIONS:

- **♦** AND

- ♦OR

- **♦**XOR

- **♦NAND**

- **♦**NOR

- **♦**NOT

ALWAYS USE BRACKETS.

UPMC/MASI, Paris - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

### **INTERNAL BEHAVIORAL ASPECT (2)**

DESCRIBING EQUATIONS BETWEEN INPUTS AND OUTPUTS.

• ASSERT (CONDITION)

REPORT "MESSAGE"

SEVERITY LEVEL;

VERY USEFUL IN LARGE-SCALE DESIGN.

- ◆ ALLOWS ENCODING SPECIFIC CONSTRAINTS AND ERROR CONDITIONS

- ◆ PROVIDE USEFUL MESSAGES.

- ◆ STOP THE SIMULATION WHEN CONSTRAINTS ARE NOT MET.

UPMC/MASI, Paris - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

# **INTERNAL BEHAVIORAL ASPECT (3)**

• THREE KINDS OF ASSIGNMENTS:

**SIMPLE ASSIGNMENT:**

$$S \leq A AND B$$

;

**CONDITIONAL ASSIGNMENT:**

Always

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996 First Course on Advanced VLSI Design Techniques: The ALLIANCE System

### **INTERNAL BEHAVIORAL ASPECT (4)**

**SELECTIVE ASSIGNMENT:**

WITH ADDRESS(3 DOWNTO 0) SELECT

OUT <= "000100" WHEN "0000",

"000101" WHEN "0001",

"000000" WHEN OTHERS;

UPMC/MASI, Paris - ICTP/UNESCO, Havana, Cuba, February 05- March 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

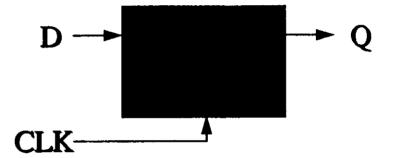

# INTERNAL BEHAVIORAL ASPECT (5)

• REGISTERS:

SIGNAL MYREGISTER: REG\_BIT REGISTER;

STORE: BLOCK (CK = '0' AND NOT CK'STABLE)

**BEGIN**

MYREGISTER <= GUARDED I0;

END BLOCK STORE;

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

# **INTERNAL BEHAVIORAL ASPECT (6)**

• <u>Bus</u>:

SIGNAL MY\_BUS1 : MUX\_BIT BUS;

ONLY ONE DRIVER ACTIVE AT THE SAME TIME.

SIGNAL MY\_BUS2: WOR\_BIT BUS; MANY DRIVERS DRIVE THE SAME VALUE.

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

#### INTERNAL BEHAVIORAL EXAMPLE

```

ARCHITECTURE DATA_FLOW OF PARITY IS

SIGNAL PARITY_AB: BIT;

SIGNAL PARITY_CD: BIT;

BEGIN

PARITY_AB <= A XOR B;

PARITY_CD <= C XOR D;

P <= PARITY_AB XOR PARITY_CD;

End;

```

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

SLIDE 22

#### **OUTLINE**

I - INTRODUCTION.

II - DESIGN METHODOLOGY: AN OVERVIEW.

III - ABSTRACTION LEVELS IN ALLIANCE.

IV - VHDL: AN OVERVIEW.

V - VHDL: THE ALLIANCE SUBSET.

VI - ALLIANCE: A COMPLETE DESIGN SYSTEM.

UPMC/MASI, Paris - ICTP/UNESCO, Havana, Cuba, February 05- March 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

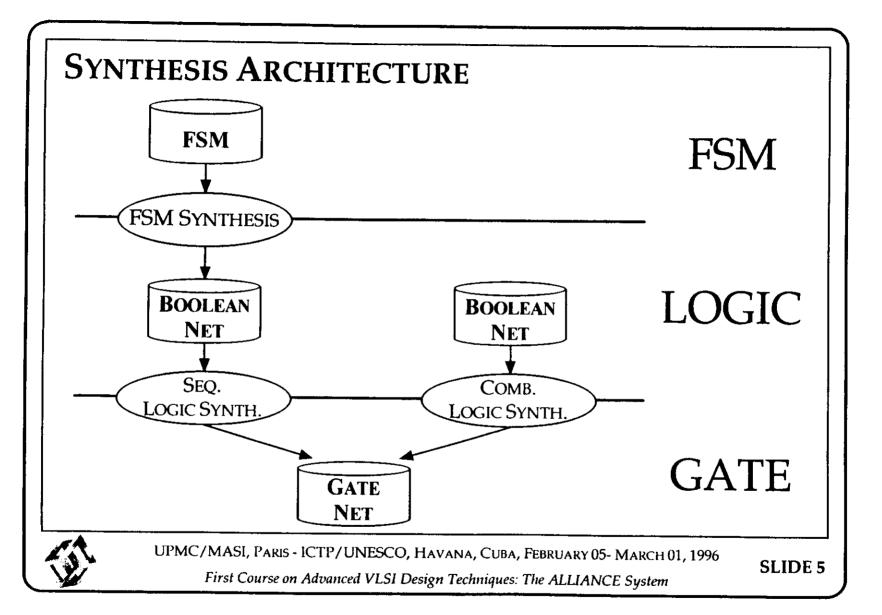

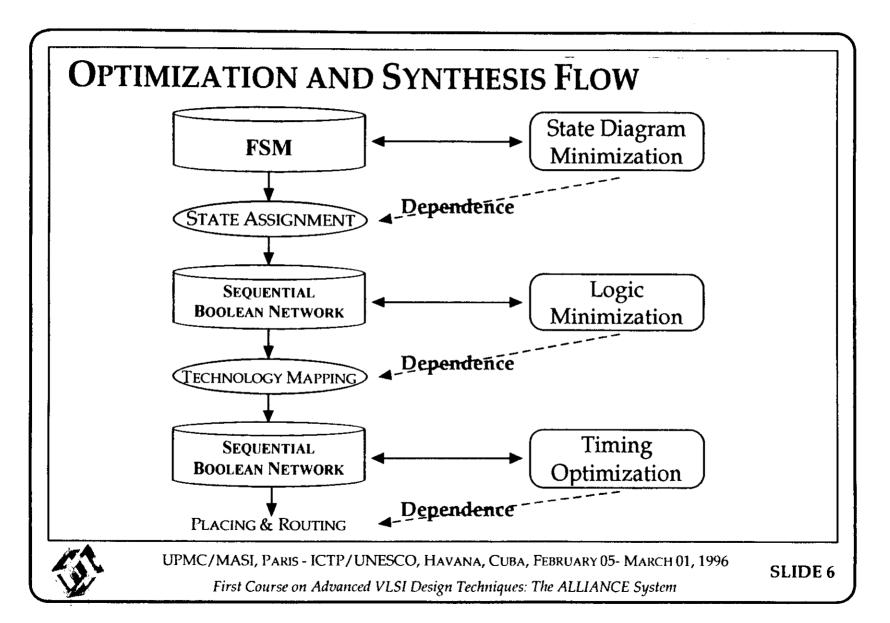

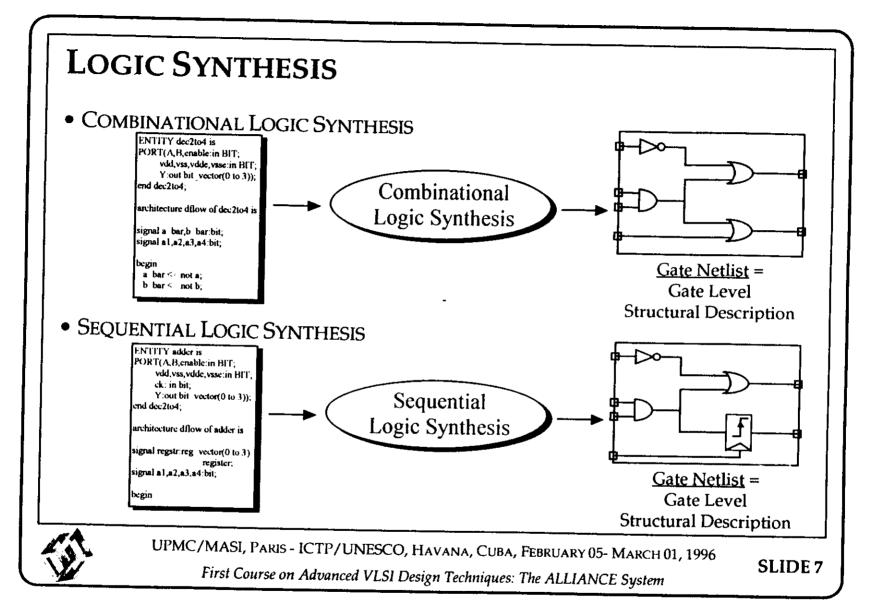

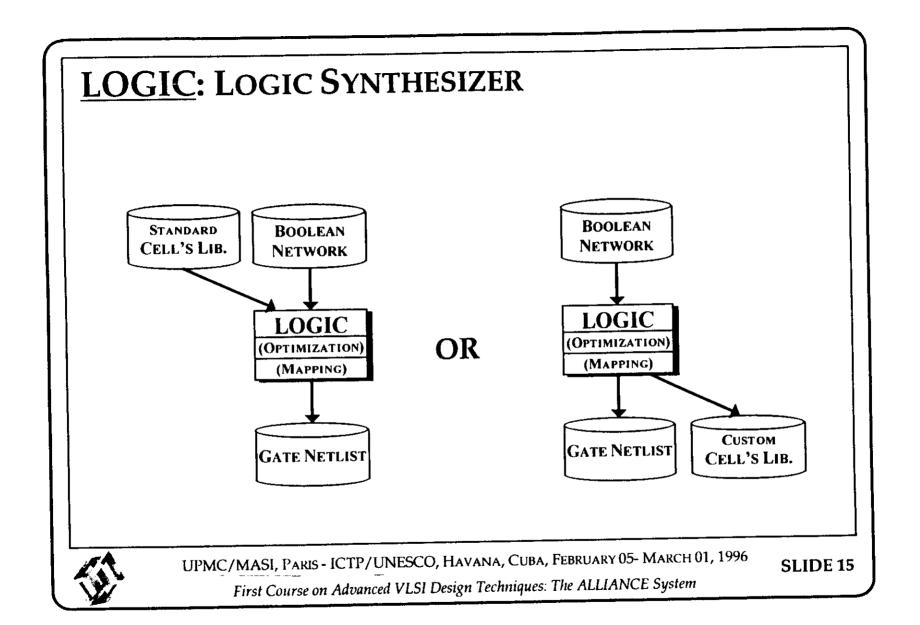

# **SYNTHESIS LEVELS**

- ARCHITECTURAL

- FINITE STATE MACHINE

- LOGIC

- LAYOUT

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

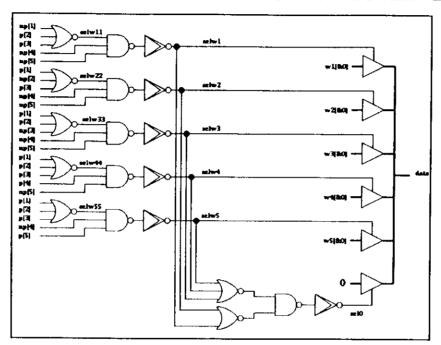

#### SYNTHESIS AREA

- CONTROL LOGIC

EVERY CIRCUIT THAT MAY BE DESCRIBED AS FSM

(NB STATES < 1000).

- RANDOM LOGIC

EVERY CIRCUIT THAT MAY NOT BE DESCRIBED WITH REGULAR LOGIC.

#### **OPTIMIZATION**

✓ IMPROVE DESCRIPTION AT EQUIVALENT LEVEL.

$$\begin{cases} X = A + \overline{A}.C.D \\ Y = C.D \end{cases} \Rightarrow \begin{cases} X = A + Y \\ Y = C.D \end{cases}$$

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

## REPRESENTATION (1)

#### LOGICAL EQUATIONS

A DIRECTED ACYCLIC GRAPH INCLUDING THREE KINDS OF NODES: INPUT, INTERMEDIARY, OUTPUT.

EACH INTERMEDIARY OR OUTPUT NODE IS ASSOCIATED TO A LOGICAL EXPRESSION.

EACH NODE IS ASSOCIATED TO A VARIABLE NAME.

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

## REPRESENTATION (2)

**BOOLEAN NETWORK**

UPMC/MASI, Paris - ICTP/UNESCO, Havana, Cuba, February 05- March 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

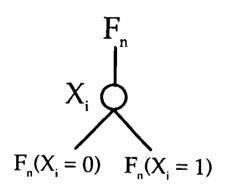

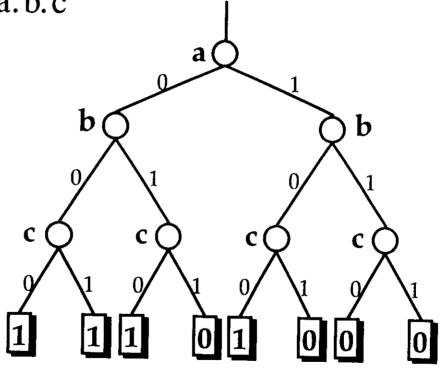

## **BDD (BINARY DECISION DIAGRAM) (1)**

BASED ON THE **SHANNON** THEOREM:

$$F(X_1, X_2,..., X_n) = \overline{X_1}.F(0, X_2,..., X_n) + X_1.F(1, X_2,..., X_n)$$

✓ CANONICAL REPRESENTATION OF A BOOLEAN EQUATION.

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

## BDD (BINARY DECISION DIAGRAM) (2)

$$\underline{Ex}: F(a,b) = a + b$$

$$F = \overline{a}.F(0,b) + a.F(1,b)$$

$$= \overline{a}.(0+b) + a.(1+b)$$

$$= \overline{a}.(b) + a.(1)$$

$$= \overline{a}.(\overline{b}.(0) + b.(1)) + a.(\overline{b}.(1) + b.(1))$$

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

## BDD (BINARY DECISION DIAGRAM) (3)

So...  $F = \overline{a}.(\overline{b}.(0) + b.(1)) + a.(\overline{b}.(1) + b.(1))$

UPMC/MASI, Paris - ICTP/UNESCO, Havana, Cuba, February 05- March 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

# BDD (BINARY DECISION DIAGRAM) (4)

$\underline{Ex}$ :  $F = \overline{a}.\overline{b} + \overline{a}.b.\overline{c} + a.\overline{b}.\overline{c}$

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

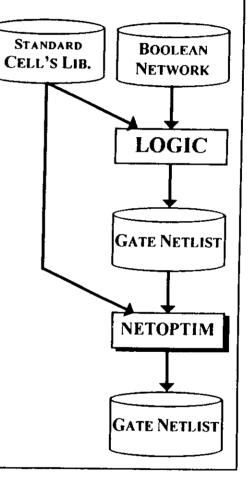

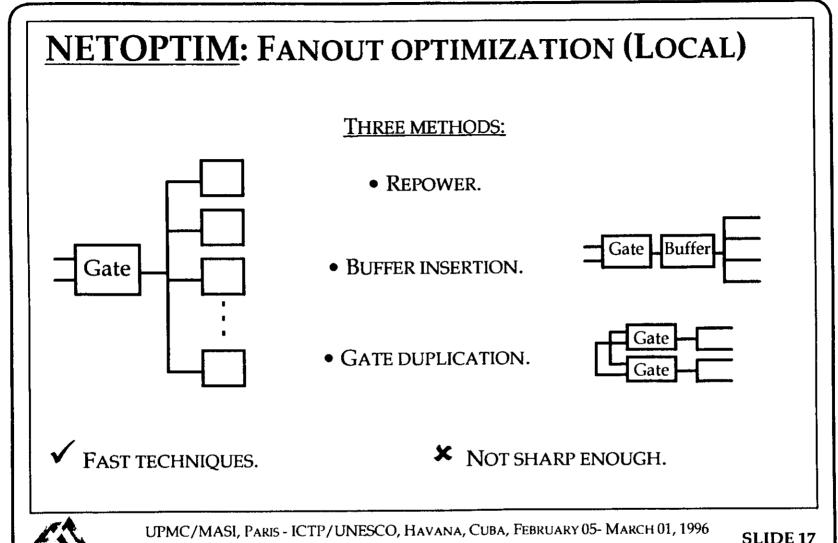

## **NETOPTIM:** TIMING OPTIMIZER

TIMING OPTIMIZATION WITH LIMITED SURFACE LOSS.

#### TWO OPTIMIZATION OPTIONS:

- FANOUT OPTIMIZATION (LOCAL VIEW).

- DELAY OPTIMIZATION WITH TIMING ANALYSIS (GLOBAL VIEW).

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

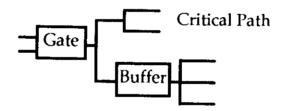

# **NETOPTIM:** DELAY OPTIMIZATION (GLOBAL)

THE TIMING ANALYSIS COMPUTES THE CRITICAL PATH OF THE CIRCUIT.

TWO METHODS TO OPTIMIZE THE CRITICAL PATH:

- REPOWER.

- BUFFER INSERTION.

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

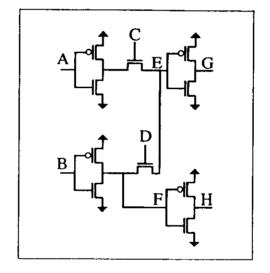

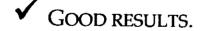

## **DESB:** FUNCTIONAL ABSTRACTOR (1)

- ✓ GENERATES BEHAVIORAL DATA FLOW VHDL.

- ✓ PROVIDES FUNCTIONAL VERIFICATIONS.

- ✓ DOES NOT USE ANY CELL LIBRARY.

- ACCEPTS STANDARD TRANSISTOR NETLIST FORMAT (VTI, SPICE).

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

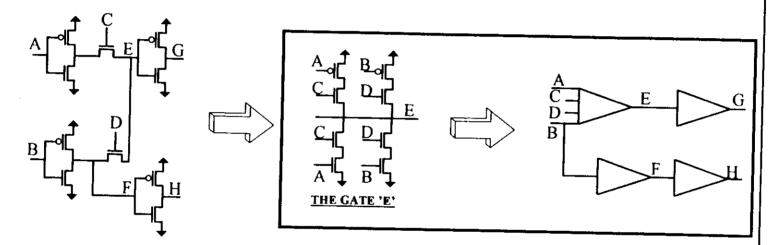

# **DESB:** FUNCTIONAL ABSTRACTOR (2)

$E \leftarrow (NOT A AND C) OR (NOT B AND D);$

$H \le NOTF$ ;

G <= NOT E;

$F \le NOT B$ ;

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

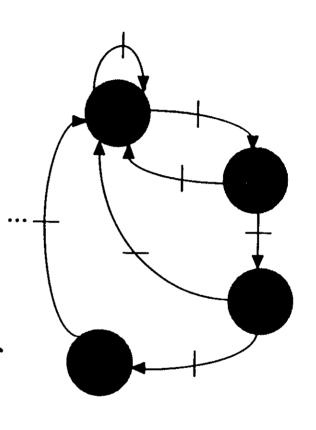

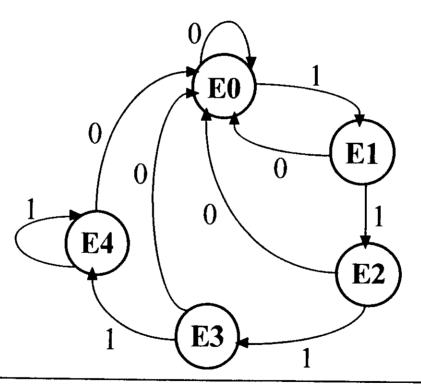

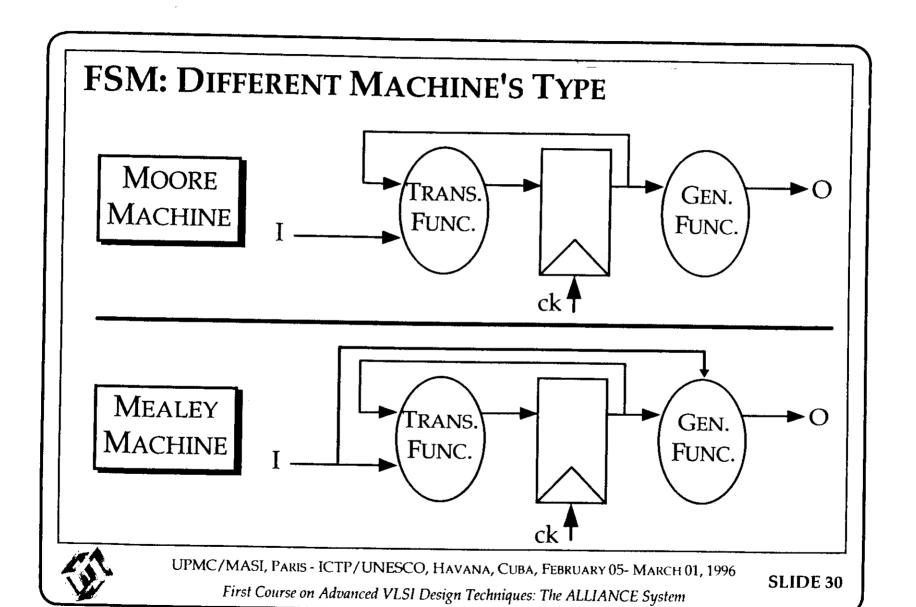

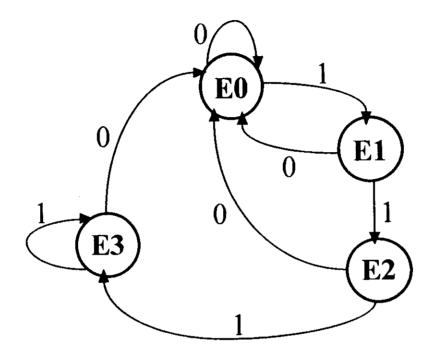

## FSM (FINITE STATE MACHINE) (1)

- MODELS SEQUENTIAL CIRCUITS.

- Two Kinds of FSM.

- GRAPH REPRESENTATION.

- DEFINITION:

STATE(T+1)

$$\langle F(I_1,...,I_n,STATE(T))\rangle$$

OUTPUT<sub>i</sub>

$$\langle = F(I_1,...,I_n,STATE(T))$$

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

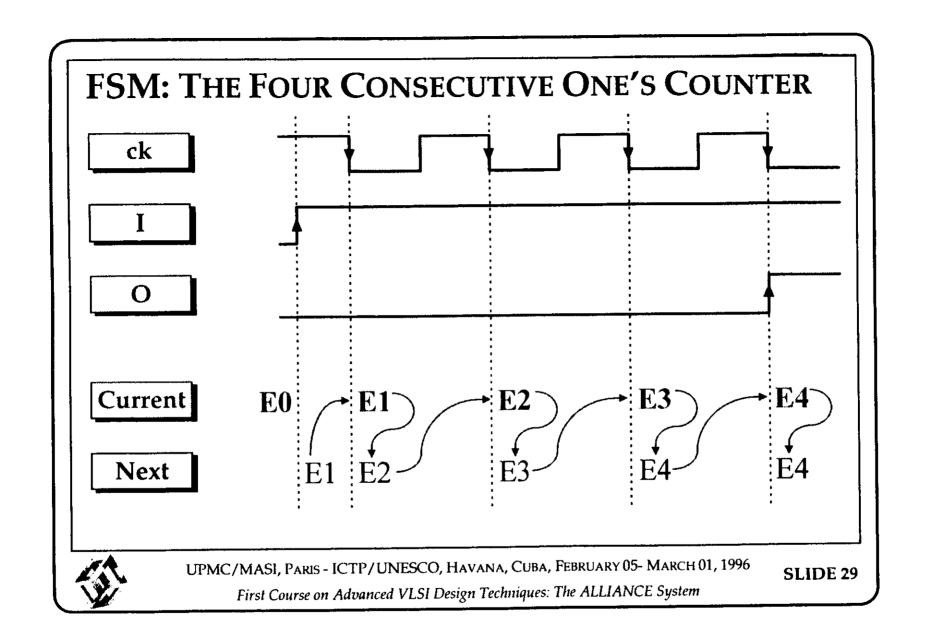

## FSM (FINITE STATE MACHINE) (2)

**EXAMPLE:** FOUR CONSECUTIVE ONE'S COUNTER

UPMC/MASI, Paris - ICTP/UNESCO, Havana, Cuba, February 05- March 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

#### **FSM:** THE DESCRIPTION LANGUAGE

- •STANDARD.

- VHDL SUBSET.

- THE STATES ARE ENUMERATED TYPE.

- Two Special Signals.

- Two Processes.

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

```

Entity counter is port (ck, I, reset: in bit; O: out bit);

End counter;

Architecture automate of counter is

type STATE_TYPE is (E0, E1, E2, E3, E4);

signal CURRENT_STATE, NEXT_STATE: STATE_TYPE;

-- pragma CUR_STATE CURRENT_STATE;

-- pragma NEX_STATE NEXT_STATE;

-- pragma CLOCK ck;

begin

Process(CURRENT_STATE, I, reset)

begin

if (reset = '1') then

NEXT_STATE <= E0;

O \le '0';

else

```

UPMC/MASI, Paris - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

```

case CURRENT_STATE is

WHEN E0 =>

if (I='1') then

NEXT_STATE <= E1;</pre>

else

NEXT_STATE <= E0;

end if;

O<= '0';

WHEN E1 =>

if (I='1') then

NEXT_STATE <= E2;

else

NEXT_STATE <= E0;

end if;

O<= '0';

```

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

```

WHEN E2 =>

if (I='1') then

NEXT_STATE <= E3;

else

NEXT_STATE <= E0;

end if;

O <= '0';

WHEN E3 =>

if (I='1') then

NEXT_STATE <= E4;

else

NEXT_STATE <= E0;

end if;

O<= '0';

```

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

```

WHEN E4 =>

if (I='1') then

NEXT_STATE <= E4;

else

NEXT_STATE <= E0;

end if;

O<= '1';

WHEN others =>

assert('1')

report "Illegal State";

end case;

end if;

end process;

```

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

SLIDE 27

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

```

Process(ck)

begin

if (ck = '0' and not ck'stable) then

CURRENT_STATE <= NEXT_STATE;

end if;

end process;

end counter;

```

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

**SLIDE 28**

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

## FSM: THE COUNTER WITH THE MEALEY MACHINE

UPMC/MASI, PARIS - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

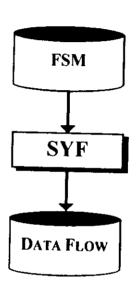

# **SYF:** AN FSM SYNTHESIZER

- VERIFICATION.

- ENCODING.

- OPTIMIZATION.

- DRIVING DATA FLOW DESCRIPTION.

## TIMING VERIFICATION

- **♦** SIMULATORS

- CIRCUIT-LEVEL.

- TIMING.

- SWITCH-LEVEL.

- LOGIC-LEVEL.

- ◆ VERIFIERS (PATTERN INDEPENDENT)

- TIMING.

UPMC/MASI, Paris - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996

First Course on Advanced VLSI Design Techniques: The ALLIANCE System

It was a real pleasure working with you. T hope that our ALLIANCE tools will help you in teaching VLSI once back home and 7 look forward to your feedback.

Very truly yours...

UPMC/MASI, Paris - ICTP/UNESCO, HAVANA, CUBA, FEBRUARY 05- MARCH 01, 1996