|  |  | • |

|--|--|---|

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

|  |  |   |

INTERNATIONAL ATOMIC ENERGY AGENCY UNITED NATIONS EDUCATIONAL, SCIENTIFIC AND CULTURAL ORGANIZATION

### INTERNATIONAL CENTRE FOR THEORETICAL PHYSICS I.C.T.P., P.O. BOX 586, 34100 TRIESTE, ITALY, CABLE: CENTRATOM TRIESTE

### UNITED NATIONS INDUSTRIAL DEVELOPMENT ORGANIZATION

INTERNATIONAL CENTRE FOR SCIENCE AND HIGH TECHNOLOGY

(10 INTERNATIONAL CENTRE FOR THEORETICAL PHYSICS MIND TRESTE (THALT), VIA GERMAND, 9 (ADDITATION PALACE) P.O. BOX 5M TELEPHONE OND MITT. TELEFAX ORD MINT. TELEFAX ORD MINT.

8MR/474 - 16

### "THE DESIGN OF REAL-TIME CONTROL SYSTEMS" 1 - 26 October

### PARALLEL PROCESSING

I. WILLERS

Advanced Computing Group

CERN

CH-1211 Geneva 23

Switzerland

These are preliminary lecture notes, intended only for distribution to participants.

Parallel Computing

lan Willers

**Parallel Processing**

Why is it interesting?

Classification of Architectures;

Common Practical Models;

Three concrete examples.

Ian Willers

College on

The Design of Real-Time

Control Systems

### Why is it interesting?

### A Super Computer

CRAY X-MP/48 – 4 processors, shared memory

Intel iPSC/860 - 128 i860 processors distributed memory

Connection Machine – 65,535 simple processors

Is a Super Computer cost effective?

Compare with -

Apollo DN10000 - 4x3 units (Cray 4x8)

Silicon Graphics SGI 240 – 4xMIPS 2000 processors

We do need all this power.

### **FERMILAB:**

High Energy Physicists have always wanted more computer power than they could afford to buy in the commercial market place.

CERN: Computing in the 90's:

Total needs in 1991-92 = 600 units

150 in CERN computer center 300 from outside laboratories 150 by parallel farms

Present computer center has:

Cray X/MP 48 = 32 units IBM 3090-600E = 39 units

What is the success of vectorization and parallelization of algorithms?

How can we benefit from automatic tools such as:

compilers

process schedulers

session schedulers

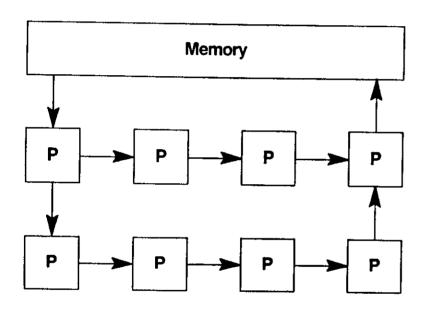

FARMING: Identical code on many processors each receiving a single physics event.

The IBM emulators (the original)

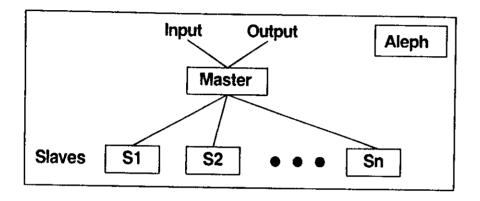

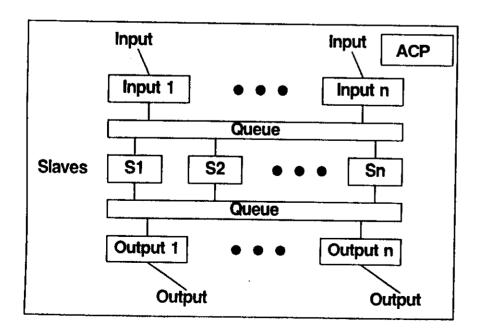

FERMILAB ACP (the ultimate)

L3 Lepics (compromise)

Aleph FALCON (system building)

### FARMING: Identical code on many processors each receiving a single physics event.

### **On-line Applications**

IBM Parallel Processing Computer Server (PPCS)

**RISC Sparc on FASTBUS**

MEIKO Transputers (+ i860's)

HP-Apollo, Cresco-Data (+DSP's)

**ASPEX**

**AMT DAP**

### Parallel Computing lan Willers

Why is it interesting?

Classification of Architectures;

**Common Practical Models;**

Three concrete examples.

### **TRANSPUTERS**

Used in the experiments:

Jetset

**OPAL Jets**

UA6

**ZEUS**

### **Definition**

### **Parallel Architecture:**

A parallel architecture provides an explicit, high-level framework for the development of parallel programming solutions by providing multiple processors, whether simple or complex, that cooperate to solve problems through concurrent execution.

### Flynn's taxonomy

- SISD Single Instruction, Single Data stream Defines serial computers

- MISD Multiple Instruction, Single Data stream

Multiple processors applying different instructions

to a single data stream.

Possible but impractical.

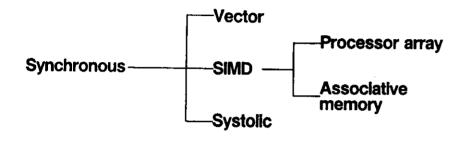

- SIMD Single Instruction, Multiple Data streams

Multiple processors simultaneously executing

the same instruction on different data.

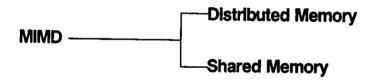

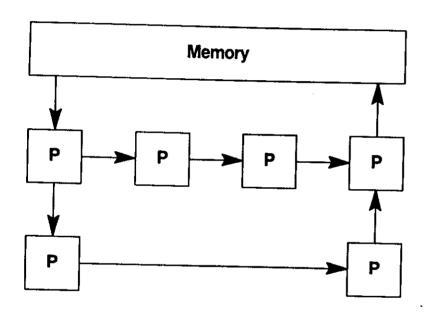

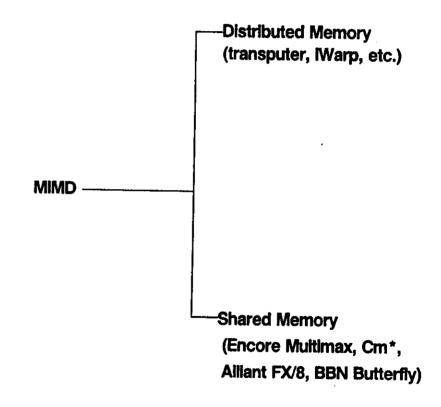

- MIMD Multiple Instruction, Multiple Data streams

Multiple processors autonomously executing

diverse instructions on diverse data.

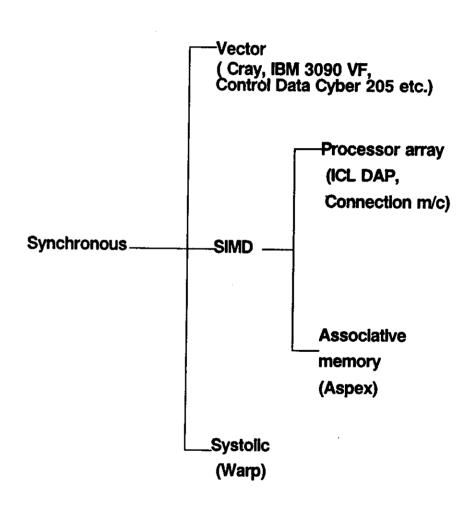

### **Duncan's taxonomy**

### **Duncan's taxonomy**

### **Pipelined Vector Processors**

### Vector register A a1 a9 a10 Vector addition pipeline Vector register C stages 3 4 5 6 C1 a8 a7 a6 a5 **c2** c4 c3 Vector register B b8 b7 b6 b5 b1 ••• b9 **b10**

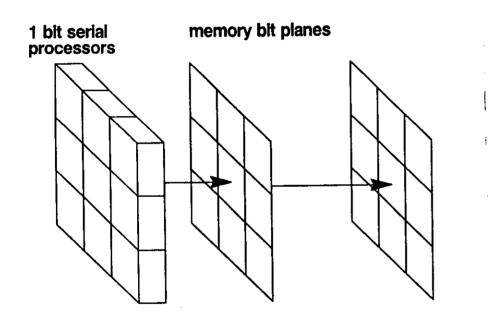

### SIMD architectures

### Bit-plane array processing

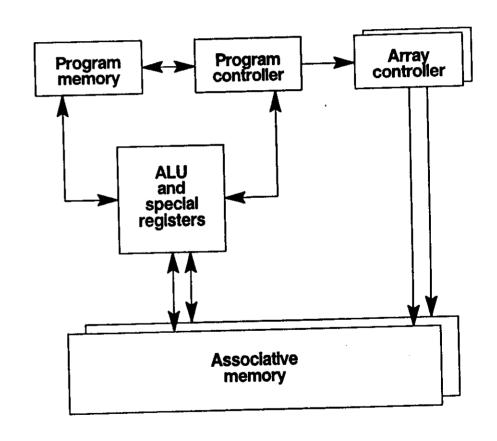

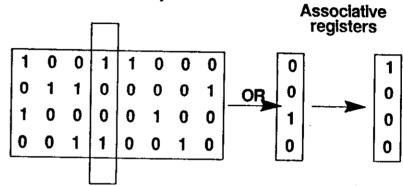

### Associative memory processing

### Associative memory processing

### Comparison register

| 1   | _    | ^  | 4 | 4 | _    | _ | _ |

|-----|------|----|---|---|------|---|---|

|     | - 17 | IJ | 1 | 1 | - (1 | 7 | n |

| , , | •    | •  |   |   | v    |   | v |

| L.  |      |    |   |   |      |   | _ |

### Mask register

| ı | 4 | -4 | - 4 | - | ^    | _ | _ | _ |

|---|---|----|-----|---|------|---|---|---|

| ı |   |    | ı   | 1 | - () | Λ | Λ | n |

| 1 | • | •  | •   | • | •    | v | v | v |

|   |   |    |     |   |      |   |   |   |

### Associative memory

| 1 | 0 | 0 | 1 | 1 | 0                | 0 | 0 |

|---|---|---|---|---|------------------|---|---|

| 0 | 1 | 1 | 0 | 0 | 0<br>0<br>1<br>0 | 0 | 1 |

| 1 | 0 | 0 | 0 | 0 | 1                | 0 | 0 |

| 0 | 0 | 1 | 1 | 0 | 0                | 1 | 0 |

### Associative register

### Associative memory processing

### Associative memory

bit column search window mask register

### **Systolic Arrays**

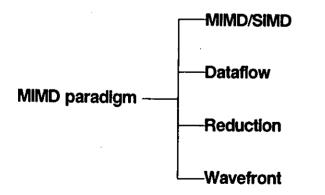

### **Duncan's taxonomy**

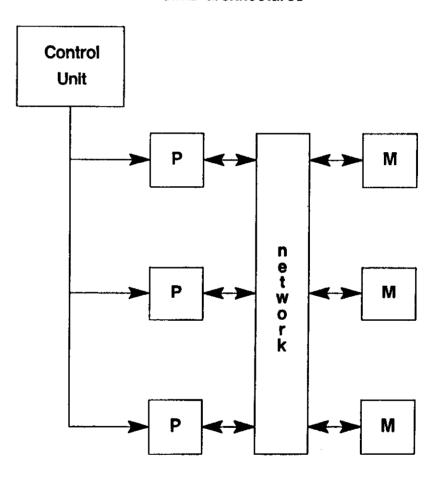

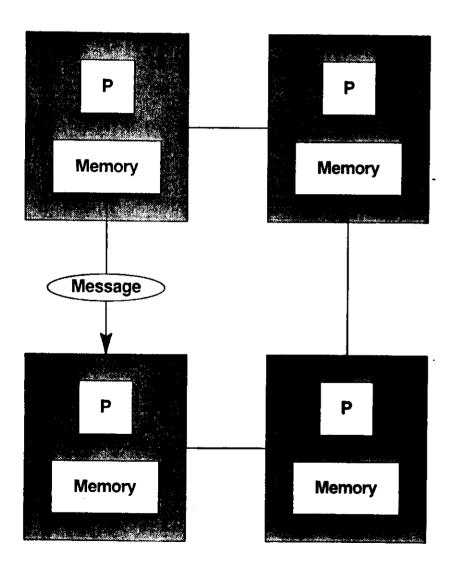

### MIMD - distributed memory

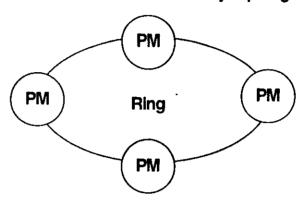

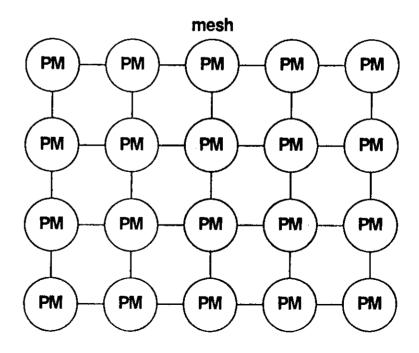

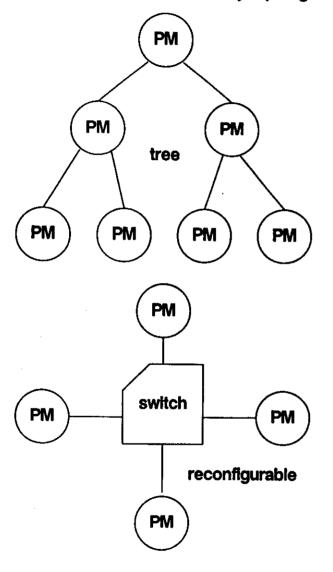

### MIMD – distributed memory topologies

MIMD – distributed memory topologies

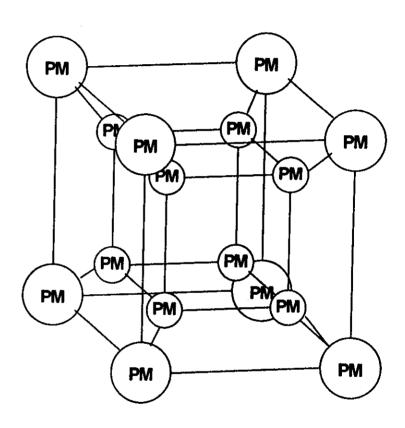

MIMD – distributed memory hypercube

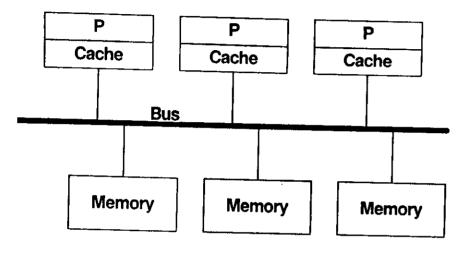

### MIMD - shared memory

# P Cache S S P Cache S Memory Memory

### MIMD - shared memory

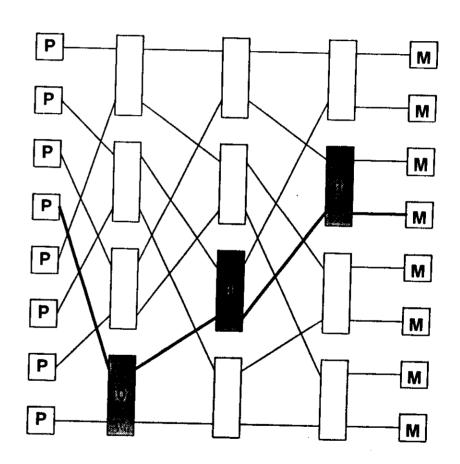

Multistage Interconnection network

### **Duncan's taxonomy**

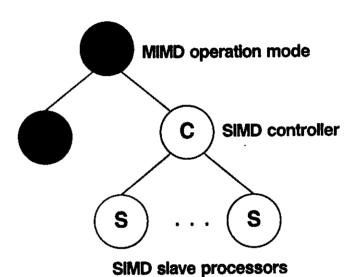

-MIMD/SIMD (Non-Von) -Dataflow (Manchester Dataflow Computer, MIT Tagged Token Dataflow Computer, Toulouse LAU, etc.) . MIMD paradigm . **Reduction** (Newcastle Reduction Machine) -Wavefront (RSRE Wavefront Machine)

### MIMD/SIMD

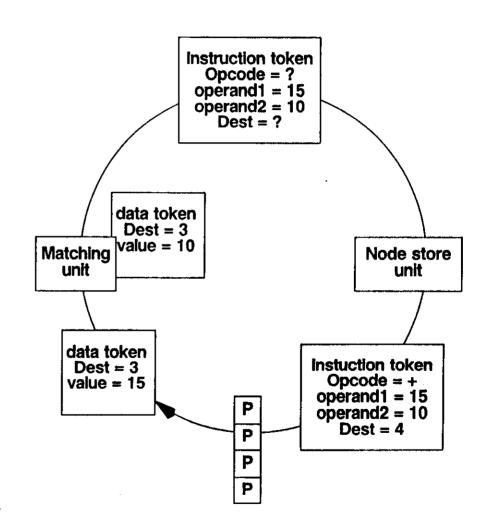

### **Dataflow**

# Node 4 + Node 3 Node 1 \* Node 2 3 a=? 5 b=?

### a=5 b=2

### **Dataflow using tokens**

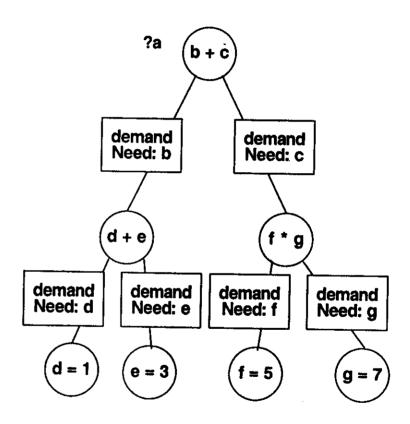

### Reduction (or Demand Driven)

### Like functional languages

$$a = b + c$$

$$b = d + e$$

$$c = f * g$$

$$d = 1$$

;  $e = 3$ ;  $f = 5$ ;  $g = 7$

?a

### **Graph Reduction**

### **Waveform Array**

Dataflow in systolic arrays.

Parallel Computing

lan Willers

Why is it interesting?

Classification of Architectures;

**Common Practical Models;**

Three concrete examples.

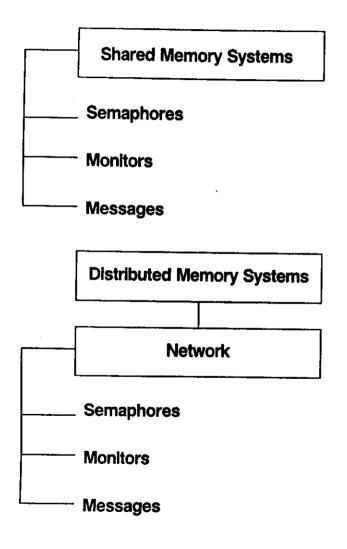

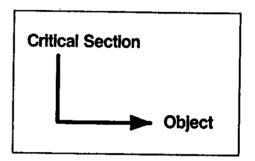

### **Restrict Access to an Object**

Like turning off interupts in a sequential computer

### Semaphores

P(s): Wait until s>0

s = s-1

V(s): s = s+1

Binary Semaphore restricts value to (0,1)

General Semaphore has any value >=0

### Critical Section

P(s)

<critical section>

V(s)

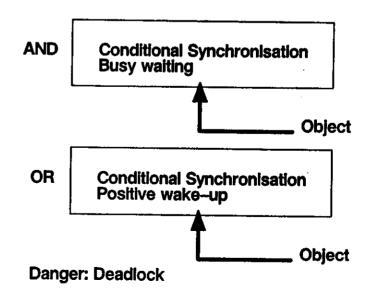

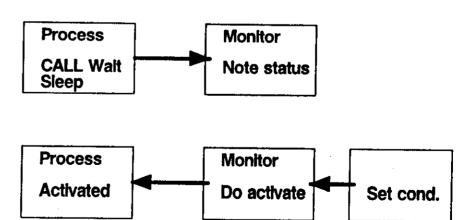

### **Conditional Synchronisation**

When condition true V(s)

h/w: Fetch&Add or ReadTestWrite

s/w: Difficult to make deadlock free programs

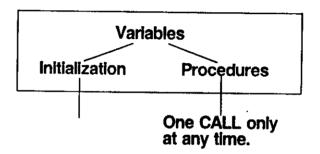

### **Monitors**

Critical Section (based on Object Oriented Programming) called a monitor.

### **Conditional Synchronisation**

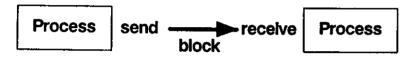

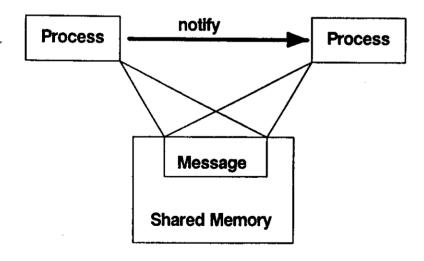

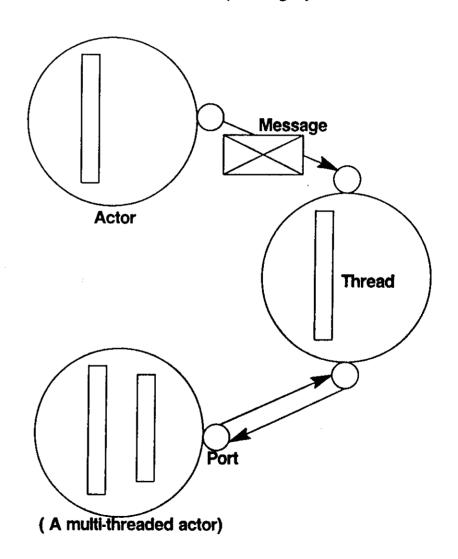

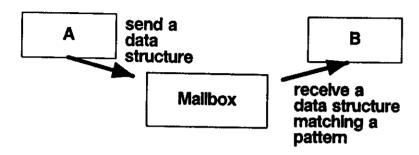

### **Message Passing (Examples)**

### Transputer (distributed memory)

### MACH operating system using shared memory

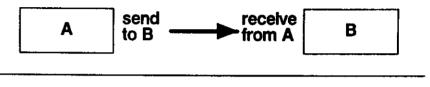

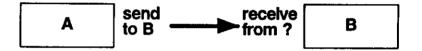

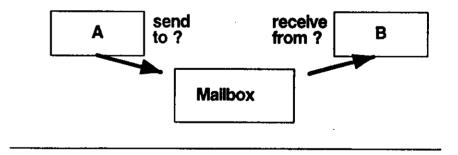

### Message Passing (models for naming)

### **Direct Naming**

### Client/Server

### Global Naming

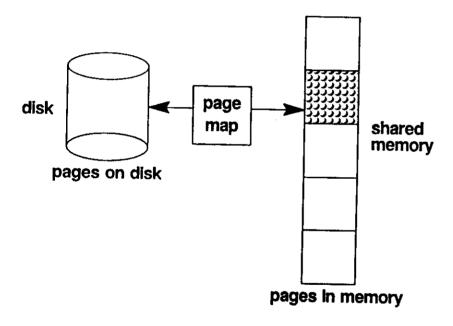

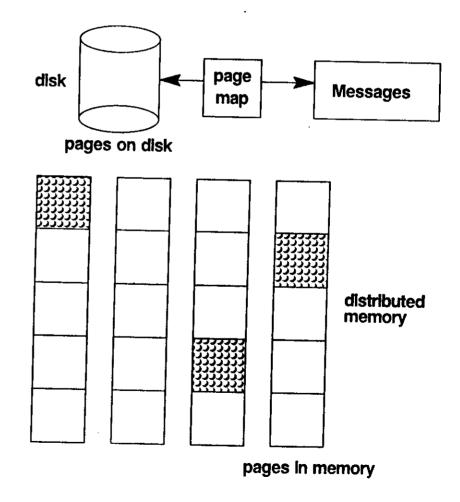

### Models - shared and distributed memory

### virtual memory with paging in shared memory model

### Distributed memory looking like Shared memory

Leslie Vallent proved – with parallel slackness the communication can be hidden.

Parallel Computing lan Willers

Why is it interesting?

Classification of Architectures;

Common Practical Models;

Three concrete examples.

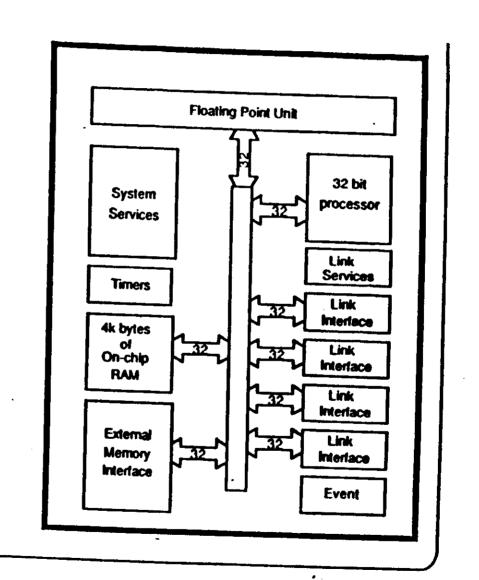

## IMST801 transputer

- 32 bit architecture

- 30 MIPS (peak)

- On-chip IEEE 754 FPU

- 4.3 Mflops (peak)

- 630 ns interrupt response

- De-mulitplexed address and data bus

- 60 Mbytes/sec data rate to external memory

- 4 Kbytes on-chip SRAM

- 4 high speed serial links (5/10/20 Mbits/sec)

- 20 , 25 AND 30 MHz

- 100 pin PGA packages

- Inventing the future

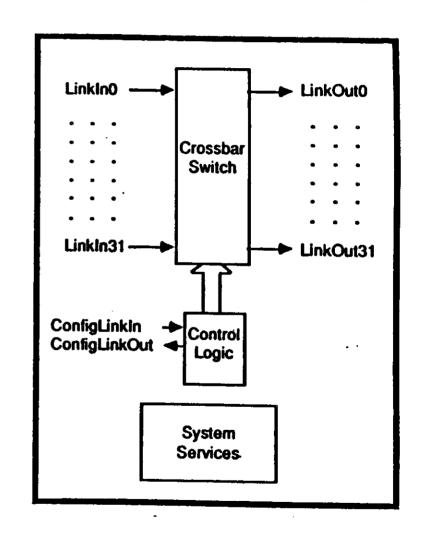

# IMS C004 programmable link switch

- Standard INMOS serial links

- 32 way crossbar switch

- Cascadable

- 10 or 20 Mbits/sec

- 84 pin PGA package

inventing the future

### Occam Tony Hoare: Communicating Sequential Processes, CSP.

### 1) Sequential code:

**SEQ**

a = 1

b = 2

### 2) Parallel code:

PAR

a = 1

b = 2

### 3) Messages:

a!3

and

a? value

### 4) Atemative routes:

**ALT**

(d=0) a ? value

<code>

( d > 0 ) b ? value

<code>

( d > 0 ) c ? value

<code>

### **The Chorus Operating System**

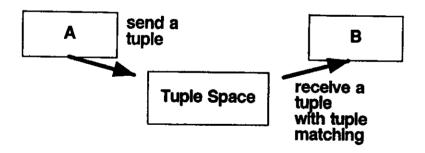

### LINDA

### LINDA

To put a tuple in tuple space:

To get a tuple from tuple space:

in (1, 1.5, 2) succeeds in (1, 1.5, 3) blocks

in (1, f, 2) succeeds and sets f to 1.5

To read a tuple from tuple space:

rd (1, 1.5, 2) succeeds etc.

Note: type and value matches are required

1) One can acheive high performance on essentially all scientific computations which are:

large (necessary condition)

loosely synchronous – MIMD or

synchronous – SIMD

- 2) Domain decomposition or data parallelism is a universal source of parallelism that scales to a large number of nodes

- 3) Greatest success has come from 1'000 to 10'000 line codes written from scratch for a particular machine. Usually the application scientist can specify parallelism from the natural geometrical structure of the problem.

4) Performance rules :-

Performance scales linearly in number of nodes at constant grain size (problem size proportional to machine size).

Fixed problem size does not scale by Amdahl's law.

5) A key question is: 'What is the appropriate productive standard programming environment for parallel machines?'

New languages and approaches (e.g. graphical techniques);

Compiler generated parallelism;

Application specific high-level environments;

Explicit user decomposition.

Parallel Computing

lan Willers

Why is it interesting?

Classification of Architectures;

Common Practical Models;

Three concrete examples.

The End