the

#### abdus salam

international centre for theoretical physics

4 manniversary

# Third Workshop on

# Distributed Laboratory Instrumentation Systems

22 November - 17 December 2004

Abdus Salam ICTP - Trieste, Italy

1594/10

# **Embedded Systems in Distributed**

**Environment**

Chu Suan Ang

GMS Technology Petaling Jaya, Malaysia

# Embedded Systems in Distributed Environment

Chu Suan ANG<sup>†\*</sup>

† Kuala Lumpur **Malaysia**

Lecture given at the:

Third Workshop on

Distributed Laboratory Instrumentation Systems

Trieste, 22 November — 17 December 2004

**LNS**

<sup>\*</sup>csang@pc.jaring.my

#### **Abstract**

Several embedded system core components, ranging from small single chip microcontrollers to large CPU modules, are described in the first part of these lectures. Embedded systems networking in a distributed environment is covered in the second part with a bias towards techniques used in the laboratory environment, taking into account both legacy and new systems.

Keywords: Microprocessors, Embedded Systems, WEB, Linux.

PACS numbers: 64.60.Ak, 64.60.Cn, 64.60.Ht, 05.40.+j

# **Contents**

| 1 | Embedde  | ed System Processors and Modules                          | 1  |

|---|----------|-----------------------------------------------------------|----|

|   | 1.1      | Introduction                                              | 1  |

|   | 1.2      | PICmicro© MCUs                                            | 3  |

|   | 1.3      | An Example of PICmicro© MCUs PIC12F675                    | 4  |

|   | 1.4      | PIC12F675 Memories and Registers                          | 5  |

|   | 1.5      | PIC12F675 I/O Port                                        | 7  |

|   | 1.6      | PIC12F675 Timers                                          | 8  |

|   | 1.7      | PIC12F675 Analog Comparator                               | 10 |

|   | 1.8      | PIC12F675 Analog-to-Digital Converter                     | 10 |

|   | 1.9      | PIC12F675 EEPROM Memory                                   | 11 |

|   | 1.10     | PIC12F675 Special Features                                | 12 |

|   | 1.11     | PIC12F675 Instruction Set                                 | 13 |

|   | 1.12     | PIC12F675 Development Environment                         | 15 |

|   | 1.13     | PIC Application — Motion Detector                         | 16 |

| 2 | Micropro | ocessors by Rabbit Semiconductor                          | 20 |

|   | 2.1      | RabbitCores                                               | 20 |

|   | 2.2      | RCM3700 Hardware                                          | 21 |

|   | 2.3      | RCM3700 Memory & I/O Bus                                  | 25 |

|   | 2.4      | RCM3700 Serial, Ethernet & Programming Ports              | 26 |

|   | 2.5      | RCM3700 Special Features                                  | 27 |

|   | 2.6      | A RabbitCore Application – Mass Storage using MultiMedi-  |    |

|   |          | aCard (MMC)                                               | 28 |

| 3 | ETRAX S  | System-on-Chip by Axis Semiconductor                      | 31 |

|   | 3.1      | ETRAX 100LX                                               | 32 |

|   | 3.2      | ETRAX 100LX MCM 2+8                                       | 33 |

|   | 3.3      | Axis 82 — Development Board                               | 34 |

|   | 3.4      | ETRAX 100LX Software and Development Tools                | 35 |

| 4 | PC/104   | & PC/104-Plus                                             | 37 |

|   | 4.1      | PC/104 and PC/104-Plus Standards                          | 38 |

|   | 4.2      | PC/104 & PC/104-Plus Products                             | 38 |

| 5 | Embedde  | ed Systems Networking in Distributed Environment          | 41 |

|   | 5.1      | Introduction                                              | 41 |

|   | 5.2      | Non-Internet Connection                                   | 43 |

|   | 5.3      | The Parallel Port                                         | 43 |

|   | 5.4      | The Serial Ports                                          | 46 |

|   | 5.5      | Differential Drive Serial Communication Standards (RS422, |    |

|   |          | RS485)                                                    | 52 |

|   | 5.6      | Universal Serial Bus (USB)                                | 54 |

|   | 5.7      | IEEE 1394 Bus                                             | 58 |

|   | 5.8      | Controller Area Network (CAN)                             | 60 |

|   | 5.9      | Inter-IC Serial Buses                                 | 62 |

|---|----------|-------------------------------------------------------|----|

|   | 5.10     | I2C-Inter Integrated Circuit Bus                      | 62 |

|   | 5.11     | SPI (Serial Peripheral Interface)                     | 62 |

|   | 5.12     | SCI (Serial Communications Interface)                 | 63 |

|   | 5.13     | Microwire                                             | 63 |

|   | 5.14     | 1-Wire Bus                                            | 63 |

| 6 | Web-base | d Embedded Systems                                    | 64 |

|   | 6.1      | Introduction                                          | 64 |

|   | 6.2      | Migration to Web-based Systems                        | 66 |

|   | 6.3      | Hardware Connection to the Internet                   | 67 |

|   | 6.4      | Ethernet Connection                                   | 69 |

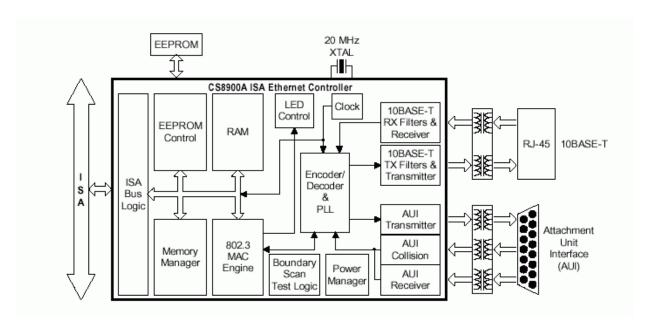

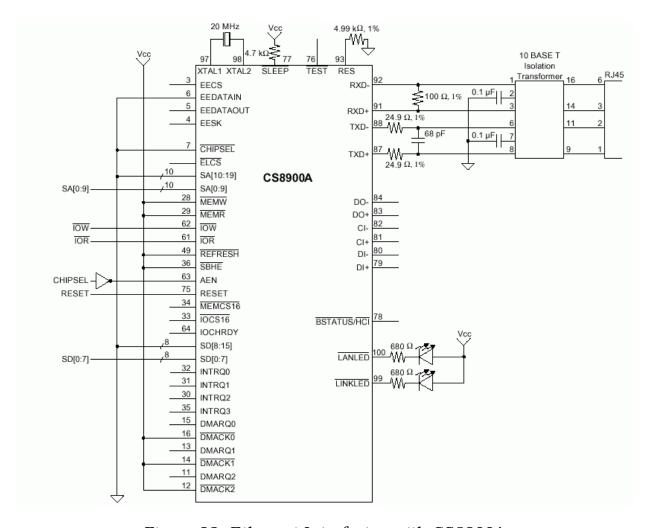

|   | 6.5      | Ethernet Controller                                   | 69 |

|   | 6.6      | On Simple Laboratory Measurements Using Embedded Pro- |    |

|   |          | cessors                                               | 73 |

|   | 6.7      | An Example of a Distributed Embedded System           | 75 |

# 1 Embedded System Processors and Modules

#### 1.1 Introduction

The overall objectives of these lectures are (1) to introduce the current embedded system hardware components or subsystems that are both available and affordable, and (2) to introduce the rudiments of networking various small embedded systems including both new and old (legacy) components.

The scene of embedded processors has changed significantly. Motorola, Intel and Zilog are no longer the obvious choices for most small research or teaching laboratories. Instead, Dallas Semiconductor, Atmel, Microchip, Rabbit Semiconductor and others are getting more and more competitive and have been widely adopted in laboratories. Several types of embedded processors suitable for embedded systems, spanning a wide range of capabilities and thus costs, are introduced here.

It is of course impossible to deal exhaustively with the available processors or subsystems in the market in a few lectures. One may tend to group them and do a generalized treatment. But a general idea of hardware is not sufficient for building an embedded system. At the end of the Workshop, it is hoped that participants will acquire sufficient knowledge to design and build their own systems. General treatment will not achieve that. The devil is in the detail.

Hardware or hardware subsystems for five different processors, ranging from the very small and simple to the complex but affordable, are chosen as examples of processors in the different embedded system classes.

- 1. PIC

- 2. TINI

- 3. Rabbit Core

- 4. Etrax MCM

- 5. ICOP PC/104 Embedded CPU Module

The PIC family of microcontrollers by Microchip has been extremely successful for small embedded system applications. The smaller members of PIC are under one dollar which is truly low cost. Of course a tiny eight-legged MCU is not quite a full embedded system but you will be surprised how little more is required to make it so. With an additional few dollars one can have a small PCB, connectors and a small line driver to make it a fully-fledged embedded system, which can be networked together via a serial bus such as the RS485. It will count events, it will control LEDs, it will also sense switches, and it will even read analogue voltages. Many of them can be distributed over a large area and connected to a PC or bigger system using a serial bus which is just a twisted pair of wires. This makes distributed systems in laboratories really feasible at low cost. A PIC system as small as a match box costing under 5 dollars has really more or less the capabilities of the Motorola board used in the early microprocessor colleges that preceded this Workshop in the 1980s.

TINI is the workhorse in this Workshop. It is one of the rising stars in the not-so-small embedded microcontrollers and it falls in the category of 50-100 dollar systems. The processor together with its many virtues is dealt with separately in another series of lectures and shall not be covered here.

The Rabbit Cores by Rabbit Semiconductor fall in the same category as the TINI. With an early successful entry in the market, there are now many different configurations and accessories available to suit different requirements. With an on-board Ethernet connector on the core module, the extension board can usually be quite simple, and therefore possible for participants to produce in their home. It is also a good candidate to use for interfacing to legacy serial equipment. It is of course a rather powerful embedded system in its own right and can be used in many localized tasks that require hard real-time control, using a real-time kernel such as uCOS. A software development environment under the Linux platform is being carried out by two members of the Workshop.

It was realized several years ago that a complete system, including memories and peripherals on a single chip with processing power equivalent to a low end PC, was feasible. Well, one such processor is now available. It is the ETRAX 100LX Multi Chip Module (MCM) by Axis Communications. At 70 dollars, the chip has the processing power and hardware resources to run Linux and other OS of similar complexity. It is a good candidate for complex real-time systems in a distributed environment in view of its high level OS capabilities and low cost.

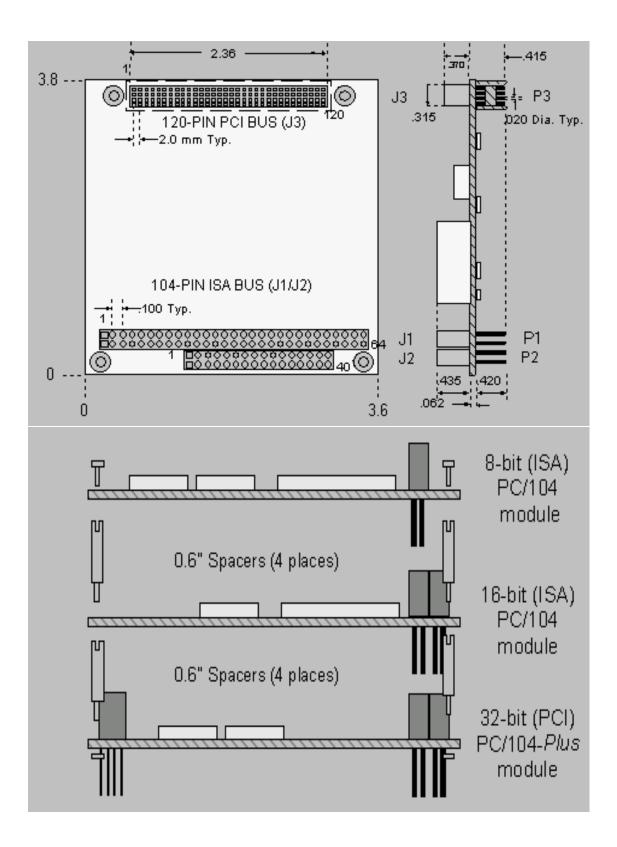

It is not true that one has to go for the cheapest possible hardware all the time. Many a time it is wiser to acquire appropriate hardware to do the job irrespective of the cost. Off-the-shelf subsystems are often more cost effective in the end because of the time saved in using them. In embedded systems, one such group is the commercially available high end embedded CPU modules. They are, in general, entire PCs in cards called single board computers (SBC). Many standards and form factors have appeared over the years, including the STB Bus, PC/104, EBX, half-size SBC, and 3.5" embedded module. The large number of manufacturers each producing a myriad of boards makes the choice of such boards difficult. PC/104 is a small form-factor (3.6 x 3.8 inches, 90 x 96 mm) worldwide standard now gaining popularity. It supports both ISA and PCI expansion in self-stacking modules, at 0.6 inch spacing. One such card is the Vortex86-6070 by ICOP Technology.

If you compare the above board with that of Axis 82 using Etrax 100LX MCM, you will see that it is definitely more suitable for bigger jobs. While the raw processing power of the two is comparable, the Vortex86 has significantly larger on-board memory. Expansion is straightforward with PC/104 modules. A display controller is also embedded, which may be required in some embedded applications (e.g. mimic diagram or synoptic panel of the railway network on a high resolution colour LCD panel?).

Basically such an embedded processor is more or less like a desktop PC in terms of computing power and peripherals such as mass storage and display. The programming environment is practically identical to that of a desktop PC and cross development becomes straightforward or perhaps unnecessary for the system itself can be a development environment. The differences lie in its com-

pactness and economy – the whole embedded system can be held in a palm and probably costs half that of the desktop PC doing the same job.

### 1.2 PICmicro® MCUs

PICmicro MCUs are RISC-based devices produced by Microchip Technology Inc. that have had tremendous success in replacing older microcontrollers in small embedded system applications in recent years. The family of MCUs has more than 140 products featuring a variety of memory configurations, low voltage and power, small footprints and ease-of-use. These products can be grouped into six families of 8-bit MCUs:

**PIC10FXXX family:** 6/8-pin 12-bit program word There are smallest mCUs using RISC-based PICMICO architecture housed in 6-pin or 8-pin packages. They have 12-bit program word with either 384 or 768 bytes of flash program memory. Operating oltage rate is 2.0 to 5.5V. Price varies from \$0.5 to \$1.0.

#### PIC12CXXX/PIC12FXXX Family: 8-pin 12-bit/14-bit program word

These are the smallest MCUs using RISC-based PICmicro architecture housed in 8-pin DIP and SOIC packages. They are available with either a 12-bit or 14-bit wide instruction set, a low operating voltage of 2.5V, small package footprints, interrupt handling, a deeper hardware stack, multiple A/D channels, FLASH, OTP or ROM program memory, and EEPROM data memory.

#### PIC16C5X Family: 12-bit program word

These are very popular MCUs because they offer cost-effective solutions in many embedded system applications. They have a 12-bit wide instruction sets and are currently offered in 14-, 18-, 20- and 28-pin packages, in the SOIC and SSOP packaging options. Low-voltage operation, down to 2.0V for OTP MCUs, makes this family ideal for battery-operated applications. The PIC16HV5XX can operate up to 15 volts for use directly with a 12-volt battery.

#### PIC16CXXX/PIC16FXXX Family: 14-bit program word

A new family that provides high performance Analog-to-Digital Converter capability at 12-bits for an MCU. The family offers a wide-range of options, from 18- to 68-pin packages as well as low to high levels of peripheral integration. This family has a 14-bit wide instruction set, interrupt handling capability and a deep, 8-level hardware stack.

#### PIC17CXXX Family: 16-bit program word

This family has a 16-bit instruction word, enhanced instruction set and powerful vectored interrupt-handling capabilities. A powerful array of precise on-chip peripheral features provides the performance for more demanding applications.

#### PIC18CXXX/PIC18FXXX Family: enhanced 16-bit program word

Top of the line of the PIC devices. The family has enhanced core features, ADC, 32 level-deep stacks, and multiple internal and external interrupts sources. Other nice features include programmable Low Voltage Detect (LVD) and programmable Brown-Out Detect (BOD). The separate instruction and data busses

of the Harvard architecture allow a 16-bit wide instruction word with the separate 8-bit wide data. The two-stage instruction pipeline allows all instructions to execute in a single cycle, except for program branches, which require two cycles. A total of 77 instructions (reduced instruction set) are available. The MCU operates up to 10 MIPS.

# 1.3 An Example of PICmicro© MCUs PIC12F675

This is a CMOS Flash-based 8-bit microcontroller using the Microchip PIC architecture housed in an 8-pin package and featuring 4 channels of 10-bit Analog-to-Digital (A/D) converter, 1 channel Comparator, and 128 bytes of EEPROM data memory. It is used for small applications, especially when field re-programming is necessary.

The RISC CPU has only 35 instructions and they execute in one cycle except branches which require two. The clock or oscillator operates from DC to 20 MHz while the instruction cycle is DC to 200 ns. An 8-level deep hardware stack is available. Addressing modes are Direct, Indirect, and Relative.

Other secondary hardware related features are:

- Internal and external oscillator options

- External Oscillator support for crystals and resonators

- 5  $\mu$ s wake-up from SLEEP

- Power saving SLEEP mode

- Wide operating voltage range: 2.0V to 5.5V

- Industrial and Extended temperature range

- Low power Power-on Reset (POR)

- Power-up Timer (PWRT) and Oscillator Start-up Timer (OST)

- Brown-out Detect (BOD)

- Watchdog Timer (WDT) with independent oscillator

- Multiplexed MCLR/Input-pin

- Interrupt-on-pin-change

- Individual programmable weak pull-ups

- Programmable code protection

- FLASH/EEPROM Cell

- 100.000 write FLASH endurance

- 1,000,000 write EEPROM endurance

- FLASH/Data EEPROM Retention: > 40 years

- Standby Current:

- 1 nA @ 2.0V, typical

- Operating Current:

- $8.5\mu A @ 32 \text{ kHz}, 2.0V, typical}$

- $100\mu A @ 1 MHz, 2.0V$ , typical

- Watchdog Timer Current

- **-** 300 nA @ 2.0V, typical

- Timer1 oscillator current:

- 4  $\mu$ A @ 32 kHz, 2.0V, typical

- Peripheral Features:

- 6 I/O pins with individual direction control

- High current sink/source for direct LED drive

- Analog comparator module with:

- One analog comparator

- Programmable on-chip comparator voltage reference (CVREF)

- Programmable input multiplexing from device inputs

- Comparator output is externally accessible

- Analog-to-Digital Converter module:

- 10-bit resolution

- Programmable 4-channel input

- Voltage reference input

- Timer0: 8-bit timer/counter with 8-bit programmable prescalar

- Enhanced Timer1:

- 16-bit timer/counter with prescaler

- External Gate Input mode

- In-Circuit Serial ProgrammingTM (ICSPTM) via two pins

# 1.4 PIC12F675 Memories and Registers

In PIC, memories are divided into program and data sections. PIC12F675 has a 13-bit program counter capable of addressing an 8K x 14 program memory space. Only the first 1K x 14 (0000h - 03FFh) is physically implemented. Accessing a location above these boundaries will cause a wrap around within the first 1K x 14 space. The RESET vector is at 0000h and the interrupt vector is at 0004h.

The data memory is partitioned into two banks, which contain the General Purpose registers and the Special Function registers. The Special Function registers are located in the first 32 locations of each bank. Register locations 20h-5Fh are General Purpose registers, implemented as static RAM and mapped across both banks. All other RAM is unimplemented and returns '0' when read. RP0 is the bank select bit. RP0=0 selects Bank 0; RP0=1 selects Bank 1.

The register file is organized as 64x8 in the PIC12F629/675 devices. Each register is accessed, either directly or indirectly, through the File Select Register FSR.

The Special Function registers are static RAM used by the CPU and peripheral functions for controlling the desired operation of the device. Details of the core and peripheral assignment of these registers can be found in the data sheet.

The STATUS register contains the arithmetic status of the ALU, the RESET status, and the bank select bits for data memory. The STATUS register can be the destination for any instruction, like any other register. However, if the STATUS register is the destination for an instruction that affects the Z, DC or C bits, then the write to these three bits is disabled. These bits are set or cleared according to the device logic.

The OPTION register is a read/write register that contains various control bits to configure TMR0/WDT prescaler, external GP2/INT interrupt, TMR0, and weak pull-ups on GPIO.

The INTCON register is a read/write register that contains the various enable and flag bits for TMRO register overflow, GPIO port change and external GP2/INT pin interrupts.

The PIE1 register contains the peripheral interrupt enable bits. The PIR1 register contains the interrupt flag bits. The Power Control (PCON) register contains flag bits to differentiate between a:

- Power-on Reset (POR)

- Brown-out Detect (BOD)

- Watchdog Timer Reset (WDT)

- External MCLR Reset

The program counter (PC) is 13-bits wide. The low byte comes from the PCL register, which is a read/write register. The high bits (PC<12:8>) are not directly accessible and they come from PCLATH. On any RESET, the PC is cleared.

The stack is 8 levels deep and 13 bits wide. It is not part of either program or data space and the stack pointer is not directly accessible. The PC is PUSHed onto the stack when a CALL instruction is executed, or an interrupt causes a branch. The stack is POPed in the event of a RETURN, RETLW or a RETFIE instruction execution. PCLATH is not affected by a PUSH or POP operation. The stack operates as a circular buffer. This means that after the stack has been PUSHed eight times, the ninth push overwrites the value that was stored from the first push. There are no status bits to indicate stack overflow or underflow. There are no instructions/mnemonics called PUSH or POP. These are actions that occur from the execution of the CALL, RETURN, RETLW and RETFIE instructions, or the vectoring to an interrupt address.

Indirect Addressing is achieved by addressing the INDF register which is not a physical register. Any instruction using the INDF register will access data pointed to by the File Select register (FSR). Reading INDF itself indirectly will produce 00h. Writing to the INDF register indirectly results in a no operation (although STATUS bits may be affected). An effective 9-bit address is obtained by concatenating the 8-bit FSR register and the IRP bit (STATUS<7>).

# 1.5 PIC12F675 I/O Port

There are six general purpose I/O pins available. Depending on which peripherals are enabled, some or all of the pins may not be available as general purpose I/O. In general, when a peripheral is enabled, the associated pin may not be used as a general purpose I/O pin.

GPIO is a 6-bit wide, bi-directional port. The corresponding data direction register is TRISIO. Setting a TRISIO bit (=1) will make the corresponding GPIO pin an input (i.e., put the corresponding output driver in a Hi-impedance mode). Clearing a TRISIO bit (=0) will make the corresponding GPIO pin an output (i.e., put the contents of the output latch on the selected pin). The exception is GP3, which is input only and its TRISIO bit will always read as '1'.

Reading the GPIO register reads the status of the pins, whereas writing to it will write to the port latch. All write operations are read-modify-write operations. Therefore, a write to a port implies that the port pins are read, this value is modified, and then written to the port data latch. GP3 reads '0' when MCLREN=1. The TRISIO register controls the direction of the GP pins, even when they are being used as analog inputs. The user must ensure the bits in the TRISIO register are set when using them as analog inputs. I/O pins configured as analog inputs always read '0'.

Every GPIO pin has an interrupt-on-change option and every GPIO pin, except GP3, has a weak pull-up option. Control bits WPUx enable or disable each pull-up. Each weak pull-up is automatically turned off when the port pin is configured as an output. The pull-ups are disabled on a Power-on Reset by the GPPU bit (OPTION<7>).

For enabled interrupt-on-change pins, the values are compared with the old value latched on the last read of GPIO. The 'mismatch' outputs of the last read are OR'd together to set the GP Port Change Interrupt flag bit (GPIF) in the INT-CON register. This interrupt can wake the device from SLEEP. The user, in the Interrupt Service Routine, can clear the interrupt by reading or writing of GPIO, or by clearing the flag bit GPIF. A mismatch condition will continue to set flag bit GPIF. Reading GPIO will end the mismatch condition and allow the flag bit GPIF to be cleared.

Each GPIO pin is multiplexed with several other functions. The pins and their combined functions are briefly described below.

- GPO/ANO/CIN+

- a general purpose I/O

- an analog input for the A/D

- an analog input to the comparator

- GP1/AN1/CIN-/VREF

- as a general purpose I/O

- an analog input for the A/D

- an analog input to the comparator

- a voltage reference input

- GP2/AN2/T0CKI/INT/COUT

- a general purpose I/O

- an analog input for the A/D

- the clock input for TMRO

- an external edge triggered interrupt

- a digital output from the comparator

- GP3/MCLR/Vpp

- a general purpose input

- as Master Clear Reset

- GP4/AN3/T1G/OSC2/CLKOUT

- a general purpose I/O

- an analog input for the A/D (PIC12F675 only)

- a TMR1 gate input

- a crystal/resonator connection

- a clock output

- GP5/T1CKI/OSC1/CLKIN

- a general purpose I/O

- a TMR1 clock input

- a crystal/resonator connection

- a clock input

#### 1.6 PIC12F675 Timers

The timer/counter module Timer0 has the following features:

- 8-bit timer/counter

- Read/Write

- 8-bit software programmable prescaler

- Internal or external clock select

- Interrupt on overflow from FFh to 00h

- Edge select for external clock

Timer mode is selected by clearing the TOCS bit (OPTION\_REG<5>). In Timer mode, the Timer0 module will increment every instruction cycle (without

prescaler). If TMR0 is written, the increment is inhibited for the following two instruction cycles. The user can work around this by writing an adjusted value to the TMR0 register.

Counter mode is selected by setting the TOCS bit (OPTION\_REG<5>). In this mode, the Timer0 module will increment either on every rising or falling edge of

Pin GP2/T0CKI. The incrementing edge is determined by the source edge (T0SE) control bit (OPTION\_REG<4>). Clearing the T0SE bit selects the rising edge.

A TimerO interrupt is generated when the TMRO register timer/counter over-flows from FFh to 00h. This overflow sets the TOIF bit. The interrupt can be masked by clearing the TOIE bit (INTCON<5>). The TOIF bit (INTCON<2>) must be cleared in software by the TimerO module Interrupt Service Routine before re-enabling this interrupt. The TimerO interrupt does not wake the processor from SLEEP since the timer itself is shut-off during SLEEP.

An 8-bit counter is available as a prescaler for the Timer0 module, or as a postscaler for the Watchdog Timer. The prescaler assignment is controlled in software by the control bit PSA (OPTION\_REG<3>). Clearing the PSA bit will assign the prescaler to Timer0. Prescale values are selectable via the PS2:PS0 bits (OPTION\_REG<2:0>). The prescaler is not accessible directly. When assigned to the Timer0 module, all instructions writing to the TMR0 register (e.g., CLRF 1, MOVWF 1, BSF 1, x... etc.) will clear the prescaler. When assigned to WDT, a CLRWDT instruction will clear the prescaler along with the Watchdog Timer. The prescaler assignment is under software control and it can be changed on the fly during program execution.

The PIC12F675 has a second timer module Timer1 with the following features:

- 16-bit timer/counter (TMR1H:TMR1L)

- Readable and writable

- Internal or external clock selection

- Synchronous or asynchronous operation

- Interrupt on overflow from FFFFh to 0000h

- Wake-up upon overflow (Asynchronous mode)

- Optional external enable input (T1G)

- Optional LP oscillator

The Timer1 Control register (T1CON) is used to enable/disable Timer1 and select the various features of the Timer1 module. There are three modes of operation for Timer1:

- 16-bit timer with prescaler

- 16-bit synchronous counter

- 16-bit asynchronous counter

In Timer mode, Timer1 is incremented on every instruction cycle. In Counter mode, Timer1 is incremented on the rising edge of the external clock input T1CKI. In addition, the Counter mode clock can be synchronized to the microcontroller system clock or run asynchronously. In Counter and Timer modules, the counter/timer clock can be gated by the T1G input. If an external clock oscillator is needed (and the microcontroller is using the INTOSC w/o CLKOUT), Timer1 can use the LP oscillator as a clock source.

The Timer1 register pair (TMR1H:TMR1L) increments to FFFFh and rolls over to 0000h. When Timer1 rolls over, the Timer1 interrupt flag bit (PIR1<0>) is set. To enable the interrupt on rollover, these bits must be set:

- Timer1 interrupt Enable bit (PIE1<0>)

- PEIE bit (INTCON<6>)

- GIE bit (INTCON<7>)

The interrupt is cleared by clearing the TMR1IF in the Interrupt Service Routine.

Timer1 has four prescaler options allowing 1, 2, 4, or 8 divisions of the clock input. The T1CKPS bits (T1CON<5:4>) control the prescale counter. The prescale counter is not directly read or written; and it is cleared upon a write to TMR1H or TMR1L.

Time1 is in asynchronous counter mode if control bit T1SYNC (T1CON<2>) is set. In this mode the timer increments without synchronizing to the internal clock. And it will continue to run during SLEEP mode and generate an interrupt on overflow.

A crystal oscillator circuit is built-in between pins OSC1 (input) and OSC2 (amplifier output). It is enabled by setting control bit T1OSCEN (T1CON<3>). The oscillator is a low power oscillator rated up to 37 kHz. It will continue to run during SLEEP. It is primarily intended for a 32 kHz crystal.

## 1.7 PIC12F675 Analog Comparator

The PIC12F675 has an analog comparator which compares the inputs at GPO and GP1 by multiplexing. There is an on-chip Comparator Voltage Reference that can also be applied to an input of the comparator. The comparator output is read through the CMCON register which is read only. In addition, GP2 can be configured as the comparator output (digital). The Comparator Control Register (CMCON) contains the bits to control the comparator. The analog input must be between Vss and Vdd and the source impedance not larger than 10K ohms.

Both the comparator and voltage reference, if enabled before entering SLEEP mode, remain active during SLEEP. This results in higher SLEEP currents.

The comparator interrupt flag is set whenever there is a change in the output value of the comparator. Software will need to maintain information about the status of the output bits, as read from CMCON<6>, to determine the actual change that has occurred. The CMIF bit, PIR1<3>, is the comparator interrupt flag. This bit must be reset in software by clearing it to '0'. Since it is also possible to write a '1' to this register, a simulated interrupt may be initiated.

# 1.8 PIC12F675 Analog-to-Digital Converter

The PIC12F675 has a 10-bit analog-to-digital converter (A/D). Four analog inputs are multiplexed into one sample and hold circuit. The output of the sample and hold is connected to the input of the converter. The converter generates a binary result via successive approximation and stores the result in a 10-bit register. The voltage reference used in the conversion is software selectable to either Vdd or a voltage applied by the Vref pin.

The ANS3:ANS0 bits (ANSEL<3:0>) and the TRISIO bits control the operation of the A/D port pins.

The A/D conversion cycle requires 11 Tad. The source of the conversion clock is software selectable via the ADCS bits (ANSEL<6:4>). There are seven possible clock options:

- Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- FRC (dedicated internal RC oscillator)

For correct conversion, the A/D conversion clock (1/Tad) must be selected to ensure a minimum Tad of 1.6  $\mu$ s. The minimum acquisition time is approximately 20  $\mu$ s. The A/D converter module can operate during SLEEP.

### 1.9 PIC12F675 EEPROM Memory

The PIC12F675 has 128 bytes of EEPROM data memory. This memory is not directly mapped in the register file space. Instead, it is indirectly addressed through the Special Function Registers. There are four SFRs used to read and write this memory:

- EECON1

- EECON2 (not a physically implemented register)

- EEDATA

- EEADR

EEDATA holds the 8-bit data for read/write, and EEADR holds the address of the EEPROM location being accessed. A byte write automatically erases the location and writes the new data (erase before write). The write time is controlled by an on-chip timer. When the data memory is code protected, the CPU may continue to read and write the data EEPROM memory while the device

EECON1 is the control register with four low order bits physically implemented. The upper four bits are not implemented and read as '0's. Control bits RD and WR initiate read and write, respectively. These bits cannot be cleared, only set, in software. They are cleared in hardware at completion of the read or write operation. The WREN bit, when set, will allow a write operation. On power-up, the WREN bit is clear. EECON2 is not a physical register. Reading EECON2 will read all '0's. The EECON2 register is used exclusively in the Data EEPROM write sequence.

Data memory can be code protected by programming the CPD bit to '0'. When the data memory is code protected, the CPU is still able to read and write data to the Data EEPROM. It is recommended to code protect the program memory when code protecting data memory. This prevents anyone from programming zeroes over the existing code (which will execute as NOPs) to reach an added routine, programmed in unused program memory, which outputs the contents of data memory. Programming unused locations to '0' will also help to prevent data memory code protection from being breached.

## 1.10 PIC12F675 Special Features

A number of features that make the PIC12F675 useful in real-time applications are also included:

- Oscillator selection

- RESET

- Power-on Reset (POR)

- Power-up Timer (PWRT)

- Oscillator Start-up Timer (OST)

- Brown-out Detect (BOD)

- Interrupts

- Watchdog Timer (WDT)

- SLEEP

- Code protection

- ID Locations

- In-Circuit Serial Programming

The PIC12F629/675 has a Watchdog Timer that is controlled by configuration bits. It runs off its own RC oscillator for added reliability. There are two timers that offer necessary delays on power-up. One is the Oscillator Start-up Timer (OST), intended to keep the chip in RESET until the crystal oscillator is stable. The other is the Power-up Timer (PWRT), which provides a fixed delay of 72 ms (nominal) on power-up only, designed to keep the part in RESET while the power supply stabilizes. There is also circuitry to reset the device if a brown-out occurs, which can provide an at least 72 ms RESET. With these three functions on-chip, most applications need no external RESET circuitry. The SLEEP mode is designed to offer a very low current Power-down mode. The user can wake-up from SLEEP through:

- External RESET

- Watchdog Timer wake-up

- An interrupt

Several oscillator options are also made available to allow the part to fit the application. The INTOSC option saves system cost while the LP crystal option saves power.

If the code protection bit(s) have not been programmed, the on-chip program memory can be read out for verification purposes.

Four memory locations (2000h-2003h) are designated as ID locations where the user can store checksum or other code identification numbers. These locations are not accessible during normal execution but are read and written during Program/Verify phase. Only the Least Significant 7 bits of the ID locations are used.

In-Circuit Serial Programming is done with two lines for clock and data, and three other lines for:

- power

- ground

- programming voltage

This allows one to produce boards with unprogrammed devices, and then program the microcontroller just before use. It thus allows the most recent firmware or a custom firmware to be programmed. The device is placed into a Program/Verify mode by holding the GPO and GP1 pins low, while raising the MCLR (Vpp) pin from VIL to VIHH. GPO becomes the programming data and GP1 becomes the programming clock. Both GPO and GP1 are Schmitt Trigger inputs in this mode. After RESET, to place the device into Programming/Verify mode, the program counter (PC) is at location 00h. A 6-bit command is then supplied to the device. Depending on the command, 14-bits of program data are then supplied to or from the device, depending on whether the command was a load or a read.

#### 1.11 PIC12F675 Instruction Set

The PIC12F629/675 instruction set is highly orthogonal and is comprised of three basic categories:

- Byte-oriented operations

- Bit-oriented operations

- Literal and control operations

Each PIC12F629/675 instruction is a 14-bit word divided into an **opcode**, which specifies the instruction type, and one or more **operands**, which further specify the operation of the instruction.

One instruction cycle consists of four oscillator periods; for an oscillator frequency of 4 MHz, this gives a normal instruction execution time of 1  $\mu$ s. All instructions are executed within a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of an instruction. When this occurs, the execution takes two instruction cycles, with the second cycle executed as a NOP.

Any instruction that specifies a file register as part of the instruction performs a Read-Modify-Write (R-M-W) operation. The register is read, the data is modified, and the result is stored according to either the instruction, or the destination designator 'd'. A read operation is performed on a register even if the instruction writes to that register.

Table 1 shows a summary of the instruction set. The different fields in the table 1 are shown in the table 2  $\,$

Table 1: Instruction set for PIC12F675

| Mnemonic Description |                                        |                              |  |  |  |  |

|----------------------|----------------------------------------|------------------------------|--|--|--|--|

|                      | BYTE-ORIENTED FILE REGISTER OPERATIONS |                              |  |  |  |  |

| ADDWF f, d           |                                        | Add W and f                  |  |  |  |  |

| ANDWF                | f, d                                   | AND W with f                 |  |  |  |  |

| CLRF                 | f                                      | Clear f                      |  |  |  |  |

| CLRW                 | _                                      | Clear W                      |  |  |  |  |

| COMF                 | f, d                                   | Complement f                 |  |  |  |  |

| DECF                 | f, d                                   | _                            |  |  |  |  |

| DECFSZ               | f, d                                   | Decremen f, Skip if 0        |  |  |  |  |

| INCF                 | f, d                                   | _                            |  |  |  |  |

| INCFSZ               | f, d                                   | Increment f, Skip if 0       |  |  |  |  |

| IORWF                | f, d                                   | _                            |  |  |  |  |

| MOVF                 | f, d                                   | Move f                       |  |  |  |  |

| MOVWF                | f                                      | Move W to f                  |  |  |  |  |

| NOP                  | _                                      | No Operation                 |  |  |  |  |

| RLF                  | f, d                                   | Rotate Left f trgought Carry |  |  |  |  |

| RRF                  | f, d                                   |                              |  |  |  |  |

| SUBWF                | f, d                                   | Subtract W from f            |  |  |  |  |

| SWAPF                | f, d                                   | Swap nibbles in f            |  |  |  |  |

| XORWF                | f, d                                   | Exclusive OR W with f        |  |  |  |  |

| BIT-ORIE             | ENTE                                   | D FILE REGISTER OPERATIONS   |  |  |  |  |

| BCF                  | f, b                                   | Bit Clear f                  |  |  |  |  |

| BSF                  | f, b                                   | Bit Set f                    |  |  |  |  |

| BTFSC                | f, b                                   | Bit Test f, Skip if Clear    |  |  |  |  |

| BTFSS                | f, b                                   | Bit Test f, Skip if Set      |  |  |  |  |

| LITE                 | LITERAL AND CONTROL OPERATIONS         |                              |  |  |  |  |

| ADDLW                | k                                      | Add literal and W            |  |  |  |  |

| ANDLW                | k                                      | AND literal with W           |  |  |  |  |

| CALL                 | k                                      | Call subroutine              |  |  |  |  |

| CLRWDT               | -                                      | Clear Watchdog Timer         |  |  |  |  |

| GOTO                 | k                                      | Go to address                |  |  |  |  |

| IORLW                | k                                      | Inclusive OR literal with W  |  |  |  |  |

| MOVLW                | k                                      | Move literal to W            |  |  |  |  |

| RETFIE               | -                                      | Return from interrupt        |  |  |  |  |

| RETLW                | k                                      | Return with literal in W     |  |  |  |  |

| RETURN               | -                                      | Return from Subroutine       |  |  |  |  |

| SLEEP                | -                                      | Go into Standby mode         |  |  |  |  |

| SUBLW                | k                                      | Subtract W from literal      |  |  |  |  |

| XORLW                | k                                      | Exclusive OR literal with W  |  |  |  |  |

Field | Description |

f | Register file address (0x00 to 0x7F) |

W | Working register (accumulator) |

b | Bit address within an 8-bit file register |

k | Literal field, constant data or label |

d | Destination select: |

d = 0: store result in W, |

d = 1: store result in file register f. |

Default d = 1

Table 2: Fields description for table 1

### 1.12 PIC12F675 Development Environment

Program development support from the manufacturer of PICmicro©, Microchip Technology Inc. is good. They consist of a number of hardware and software development tools:

- Integrated Development Environment

- Assemblers/Compilers/Linkers

- Simulators

- Emulators

- In-Circuit Debugger

- Device Programmers

- Low Cost Demonstration Boards

- Evaluation Kits

The manufacturer's web site (http://www.microchip.com) has very comprehensive information including product datasheets, product guides, application notes, prices and information on related products or systems.

Because of the popularity of these devices, there are now a host of third party suppliers for hardware and software products based on these MCUs. Amongst them is Basic Stamps produced by Parallax, Inc. (http://www.parallax.com).

The company released a stamp sized microcomputer using PIC chip that was programmed in BASIC. These BASIC Stamps have been very popular because of their ease of use, and relative low cost. It allows many beginners to program a microcontroller for the first time. Parallax's customers include everyone from scientists and hobbyists to engineers and entrepreneurs. By 2002 there were over three million BASIC Stamps in use.

There are also books aiming at introducing these devices and their use. John Iovine's "PIC Microcontroller Project Book" (McGraw-Hill, 2000, ISBN 0-07-135479-4) is an introductory book on the subject. It does not assume any prior knowledge on microcontrollers. The author simplifies the programming of these devices by using a BASIC compiler produced by microEngineering Lab, Inc. (http:

//www.melabs.com). A dozen simple projects are described in the book, including simple I/O control, speech synthesizer, LCD display, sensor monitoring and motor control.

While the majority of compilers and development environment for PIC are MS Windows or DOS based, there are now versions available under Linux environment. Information can be found at: http://www.eg3.com/pic.htm

Finally, the cost of the PIC12F675 varies from about \$1.25 to \$1.65, depending on the type of packaging. A PDIP 300mil package type (PIC12F675-I/P) is available at \$1.25 per piece.

# 1.13 PIC Application — Motion Detector

Small microcontrollers such as the PICs are well suited for a large range of applications in laboratories. They are particular useful in implementing small real-time applications. Real-time requirements mean tasks must be executed at precise times or over specific durations. Such requirements are difficult to fulfil if there are a large number of concurrent tasks in the system. However, if one can partition the system into small modules or sub-systems, the problem is much simple to handle. This is similar to the principle of encapsulation used in object oriented programming.

Many tasks that requires very stringent timing, e.g. monitoring the output of a sensor accurately every second and doing so for exactly 10 ms each time, are very easy to implement using small microcontrollers which have crystal oscillators, timers and perhaps real-time clock.

A one dollar microcontroller can easily resolve time to within microseconds and typically has long term time stability of one part in  $10^5$  using crystal oscillator. In the event that this produces unacceptable drift in a distributed environment, one simple solution is to synchronise with a master clock in the system, or implement isochronous clock for the entire distributed system.

This section describes a small project using a PIC12LC672 microcontroller to illustrative the simplicity in using this type of device. The timing requirement in the project makes it a small real-time system in a way. The objective is to construct a simple, lightweight and low cost motion detector. There are many situations when movements of personnel, animals or other objects in rooms under normal lighting conditions may be of interest. And there are many ways of detecting such motions, ranging from applying video pattern recognition to using mechanical sensors or accelerometers.

A conceptually very simple method is to monitor the change of light intensity with a sensor affixed to the object of interest, and hence reduce the status of whether the object is stationary or moving. This method is attractive because cadmium sulphide (CdS) light dependent resistors (LDRs) can be used as light sensor and they are small, low cost, readily available and easy to handle. Several LDRs are shown in the picture below; the smallest one has a diameter of about 4 mm and costs less than \$1 each. Unfortunately, a practical motion detector using a LDR requires a fair bit of signal processing. Before the arrival of low cost

microcontrollers such as PICs, analogue and digital circuits were used for this signal processing. The situation has changed dramatically with the use of small microcontroller as embedded processor. Most of the signal conditioning can be done in software now.

The common LDR has a nonlinear resistance range of just under  $1k\Omega(at\ 10\ lux)$  to  $20\ M\Omega(dark)$ . These are five orders of magnitude change, which is good. However, in normal use, one cannot expect changes from  $10\ lux$  to complete darkness when moving about in a room! The resultant resistance change while one is moving about is considerably smaller. By having a tunnel or telescopic view from the LDR, the light and hence resistance change can be enhanced to a certain extent. However, there is a limit to the improvement possible. An overall change of  $0.1\ to\ 10\ times$  in resistance is more likely the case. This magnitude of change is sufficiently large for an 8-bit ADC to be used, since a resolution of  $256\ levels$  can be achieved with 8 bits.

The difficulty lies in the dynamic range of the ambient light intensity. Even in offices, the brightness of areas under lamps, when sunlight shines through windows and at dark corners varies considerably, resulting in orders of magnitude change in resistance. Thus when an 8-bit ADC is used in a straightforward manner, it will not function properly. If a large dynamic range is set, it is insensitive to changes due to normal movement. On the other hand, if the dynamic range is small, it will not work in bright or dark areas which produce extreme resistance values.

One possible solution to the dynamic range problem is to use potential divider arrangement with a fixed resistor connected in series with the LDR. The potential across one of the resistors is measured with the ADC of the microcontroller. By switching in different fixed resistors, one can cover practically any range of

resistance value of the LDR. There are however a couple of shortcomings with this arrangement. First, the fixed resistor will typically have resistance value of the same order of magnitude as the LDR. This may mean unnecessary drain on power, which has to be kept as small as possible for such battery operated devices. Second, most modern lighting in offices uses fluorescent lamps which produce fluctuating light intensity at twice the mains frequency (f) due to the mercury discharge characteristic. Thus when the mains is 50-Hz, the light in a room actually various between zero and maximum every 10 ms or half the period (t= 1/f), even though not discernable to us due to persistence of vision of our eyes. This, however, is detected by the LDR. Spot measurement of the resistance of LDR thus reflects both flickering of the fluorescent lamp (when measurement is taken) and motion of the sensor (where the sensor points to).

An average or integration over multiple t (half period) is needed to overcome this problem. This can be done by accurate sampling many times within the period mentioned and take the average.

There is however a better solution to the problem. An integration can be done with ease by using an RC charging technique. Instead of using a DC potential arrangement, a capacitor is connected to the LDR in series. By charging the capacitor via the LDR over a period of t or multiple t, the voltage on the capacitor is an indication of the integration over the period. This will eliminate the fluctuating light output problem of fluorescent lamps.

If different capacitances can be switched in, the dynamic range of five orders of magnitude can be achieved quick easily. This arrangement has the added advantage that even when the LDR resistance is low, the current through the circuit is kept low, limited by the charging characteristic of the RC circuit.

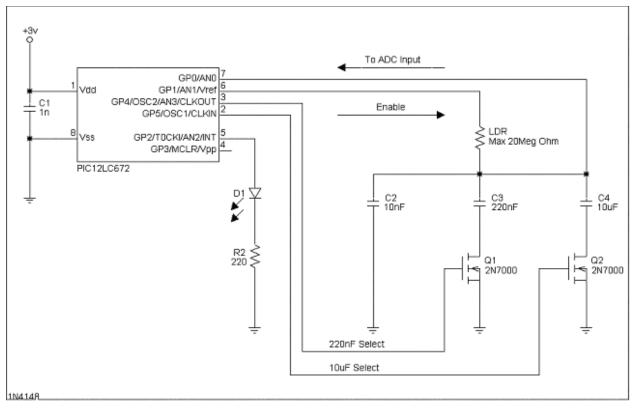

A practical arrangement using the above technique for motion detection is shown below. The circuit consists of a PIC12LC672, an LDR, an LED, two MOSFETs, 4 capacitors and a resistor. The whole circuit is powered by a 3 V lithium ion coin battery such as the CR2032. One output pin GP2 is used to control the indicator LED; the series resistor R2 limits the current through the LED to several mA. The Vref output provides the charging current through the LDR while the voltage across the capacitor(s) is measured by analog input pin AN1. GP0 is configured as an input to discharge the capacitors. GP4 and GP5 act as output, controlling the MOSFET switches for capacitors C3 and C4.

It can be seen that the LDR is always connected in series with C2 to ground. Two other capacitors C3 and C4 may be switched in (in parallel to C2) via MOS-FET Q1 and Q2 respectively. The voltage across the capacitors and ground is measured by the ADC of the microcontroller. Vref controls the charging of the capacitor(s). Normally it is kept at 0 V. When a measurement is needed, it is turned to high for t second thus charging the capacitor(s) for exactly half the period of the mains. The ADC reading is taken and the resistance of the LDR can be deduced.

Adaptive measurement to cover a wide dynamic range by selectively switching in C3 or C4 when necessary. When it is bright and LDR resistance low, C2 will charged up to saturation rapidly, well within t second. If this condition is detected, C3 is switched in before the next sampling. The same procedure is repeated for C4 if necessary. Similarly, C3 and C4 may be switch out when the ADC reading is too low, indicating too high a LDR resistance.

After each measurement, the capacitors are discharged to 0V by turning GP0 to low.

The LED acts as an indicator in this simple example. It is turned on momentarily when motion is detected.

Since light intensity is sensed in this circuit, we can use it to monitor changing lighting condition. Interesting enough, this may pose a problem when the circuit is used as a motion detector. Changing ambient light intensity due of switching on or off of lamps, gradual brightening or dimming of rooms due to external light variation (e.g. sun rising) may be misconstrued as resulting from motion. This can be avoided by appropriate algorithms. Gradual changing of

room brightness may be software filtered. The rate of change of the light input can be used as a criterion. The sudden switching on and off of lamps will produce strictly step changes in light intensity which again can be identified by software.

# 2 Microprocessors by Rabbit Semiconductor

A Z-80 based high performance 8-bit microcontroller Rabbit 2000 was first introduced in 1999 by Rabbit Semiconductor, a fabless semiconductor company in Davis, California. The subsequent RabbitCore line of products introduced in 2001 has been very well received and it is one of the most popular MCU modules for embedded systems. Now a relatively wide range of cores are available that are very cost effective while offering a wide variety of form factors, memory capacities and functionalities.

Amongst the major attractions of this family of processors are the relatively large memory size of 1 Mbytes, Ethernet and TCP/IP support, and an integrated software development environment using Dynamic C.

Like other semiconductor manufacturers, Rabbit Semiconductor offers a range of products from simple components to full development systems. They are Rabbit Microprocessors, Microprocessor Core Modules, Development Kits, Peripherals and Accessories, and Software. Due to the complexity of the range of Rabbit Microprocessors, they are no longer simple to implement. These processors, by virtue of their processing power and resources, are generally large chips with 100 or 128 leads using quad flat package (QFP) or ball grid array (BGA) housings. These surface mount packages are generally beyond the means of ordinary laboratories that are not working in microelectronics.

Microprocessor core modules that contain the processor and necessary peripheral components including connectors on a small PCB are therefore more suitable for laboratory use. It turns out that the core modules produced by manufacturers such are Rabbit Semiconductor are generally very cost effective. We shall therefore introduce the core modules instead of the basic processors.

#### 2.1 RabbitCores

Two series of core modules based on the Rabbit 2000 and 3000 processors respectively are produced to cater for a wide range of applications and requirements. The RCM2000 cores have the following main features:

- Rabbit 2000 processor

- 256K Flash memory

- 128-512K SRAM

- 40 general purpose I/O

- 18-25 MHz clock

- 1.9" x 2.3" x 0.5"

#### • 5V operation

The smallest member, RCM2020 with 128K SRAM, operates at 18.432 MHz and is retailing at \$39 per unit while the RCM2000 with 256K SRAM and 25.8MHz clock is at \$69. These are extremely powerful modules requiring very few external components for many laboratory or other applications.

One of the major attractions of the RabbitCores is the incorporation of 10Base-T Ethernet capability including an RJ45 socket, as in the case of RCM2200 series. Based on the same processor, the other features are similar, other than a smaller number (26) of I/O pins are available to the users.

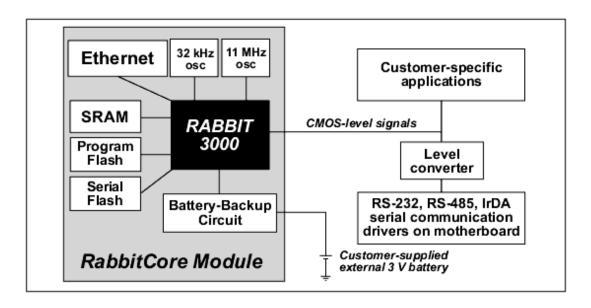

The high end series by Rabbit Semiconductor is the RCM3000. This series has 10Base-T Ethernet, up to 512K each of Flash and SRAM, encoder inputs, PWM outputs, and pulse capture and measurement capabilities. Two 34-pin connection headers provide 52 digital I/O shared with 6 serial ports and alternate I/O features. It also features a battery-backed real-time clock, glueless memory and I/O interfacing, and low power "sleepy" modes (<2mA). A fully enabled slave port permits easy master-slave interfacing with another processor-based system, and an alternate I/O bus can be configured for 8 data lines and 6 address lines sharing with parallel I/O.

#### 2.2 RCM3700 Hardware

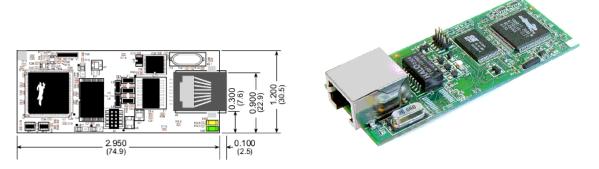

We shall now look at the hardware of one of the RabbitCores, RCM3700, in more detail. A picture and the dimensions are shown below. The main hardware and physical specifications are given in the manufacturer's datasheet and are tabulated below (table 3) for reference.

Table 3: Specifications for RCM 3700/3710 Hardware

| Parameter      | RCM3700                         | RCM3710 |  |

|----------------|---------------------------------|---------|--|

| Microprocessor | Low-EMI Rabbit 3000 at 22.1 MHz |         |  |

| Ethernet Port  | 10Base-T, RJ-45, 2 LEDs         |         |  |

| Flash Memory   | 512K                            | 256K    |  |

| SRAM           | 512K                            | 256K    |  |

Table 3: Continued

| Serial Flash Memory   | 1Mbyte                                             |  |  |  |

|-----------------------|----------------------------------------------------|--|--|--|

| Backup Battery        | Connection for user-supplied backup battery        |  |  |  |

|                       | (to support RTC and SRAM)                          |  |  |  |

| General-Purpose I/O   | 33 parallel digital I/0 lines:                     |  |  |  |

|                       | • 31 configurable I/O                              |  |  |  |

|                       | • 2 fixed outputs                                  |  |  |  |

| Additional I/O        | Reset                                              |  |  |  |

| Auxiliary I/O Bus     | Can be configured for 8 data lines and             |  |  |  |

|                       | 5 address lines (shared with parallel I/O lines),  |  |  |  |

|                       | plus I/O read/write                                |  |  |  |

| Serial Ports          | Four 3.3 V CMOS-compatible ports configurable as:  |  |  |  |

|                       | <ul> <li>4 asynchronous serial ports</li> </ul>    |  |  |  |

|                       | (with IrDA) or                                     |  |  |  |

|                       | • 3 clocked serial ports (SPI) plus 1 HDLC         |  |  |  |

|                       | (with IrDA) or                                     |  |  |  |

|                       | • 1 clocked serial port (SPI) plus 2 HDLC          |  |  |  |

|                       | serial ports (with IrDA)                           |  |  |  |

| Serial Rate           | Maximum asynchronous baud rate = CLK/8             |  |  |  |

|                       | A slave port allows the RCM3700 to be used as      |  |  |  |

| Slave Interface       | an intelligent peripheral device slaved to         |  |  |  |

|                       | a master processor, which may either be            |  |  |  |

|                       | another Rabbit 3000 or any other type of processor |  |  |  |

| Real-Time Clock       | Yes                                                |  |  |  |

| Timers                | Ten 8-bit timers (6 cascadable), one 10-bit timer  |  |  |  |

|                       | with 2 match registers                             |  |  |  |

| Watchdog/Supervisor   | Yes                                                |  |  |  |

| Pulse-Width           | 4 PWM output channels with 10-bit free-running     |  |  |  |

| Modulators            | counter and priority interrupts                    |  |  |  |

|                       | 2-channel input capture can be used to time        |  |  |  |

|                       | input signals from various port pins               |  |  |  |

| Input Capture/        | • 1 quadrature decoder unit accepts inputs         |  |  |  |

| Quadrature Decoder    | from external incremental encoder modules or       |  |  |  |

|                       | • 1 quadrature decoder unit shared                 |  |  |  |

|                       | with 2 PWM channels                                |  |  |  |

|                       | 4.75-5.25 V DC                                     |  |  |  |

| Power                 | 100 mA @ 22.1 MHz, 5 V;                            |  |  |  |

|                       | 78 mA @ 11.05 MHz, 5 V                             |  |  |  |

| Operating Temperature | -40C to +70C                                       |  |  |  |

| Humidity              | 5% to 95%, noncondensing                           |  |  |  |

| Connectors            | One 2 x 20, 0.1" pitch                             |  |  |  |

| Board Size            | 1.20" x 2.95" x 0.88" (30 mm x 75 mm x 22 mm)      |  |  |  |

| Price                 | \$59 \$45                                          |  |  |  |

A simplified block diagram of the RCM3700 is show in the figure 1. page 23.

Figure 1: RCM3700 Block Diagram

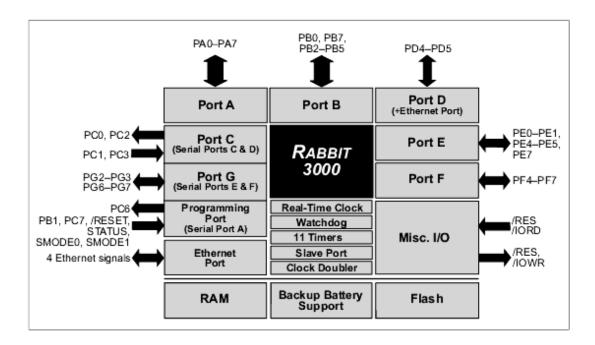

The various ports and I/O lines are shown in the figure 2.

Figure 2: Rabbit 3000 ports and I/O lines

Most of the I/O lines on the Rabbit 3000 microprocessor are dual function.

The factory defaults and the alternate configurations are shown in the following (4) table:

Table 4: I/O of Rabbit 3000

| F | Pin | Pin Name | Default Use   | Alternate Use               | Notes              |

|---|-----|----------|---------------|-----------------------------|--------------------|

|   |     |          |               | External data bus (ID0-ID7) | Externa            |

|   | 1-8 | PA[7:0]  | Parallel I/O  | Slave port data bus         | Data               |

|   |     |          | ,             | (SD0-SD7)                   | Bus                |

|   | 9   | PF1      | Input/Output  | QD1A/CLKC                   |                    |

|   | 10  | PF0      | Input/Output  | QD1B/CLKD                   |                    |

|   | 11  | PB0      | Input/Output  | CLKB                        |                    |

|   |     |          |               |                             | External           |

|   |     |          |               |                             | Address 0          |

|   | 12  | PB2      | Input/Output  | IAO/SWR                     | Slave port         |

|   |     |          |               |                             | write              |

| Н |     |          |               |                             | External           |

| e |     |          |               |                             | Address 1          |

| a | 13  | PB3      | Input/Output  | IA1/SWD                     | Slave port         |

| d |     |          |               | ,                           | read               |

| e |     |          |               |                             | External           |

| r |     |          |               |                             | Address 2          |

|   | 14  | PB4      | Input/Output  | IA2/SA0                     | Slave port         |

| J |     |          | 1 1 1, 1 1, 1 | ,                           | address 0          |

| 1 |     |          |               |                             | External           |

|   |     |          |               |                             | Address 3          |

|   | 15  | PB5      | Input/Output  | IA3/SA1                     | Slave port         |

|   |     |          |               | ,                           | address 1          |

|   |     |          |               |                             | External           |

|   |     |          |               |                             | Address 5          |

|   | 16  | PB7      | Input/Output  | IA5/SLAVEATTN               | Slave port         |

|   |     |          |               | ,                           | Attention          |

|   | 17  | PF4      | Input/Output  | AQD1B/PWM0                  |                    |

|   | 18  | PF5      | Input/Output  | AQD1A/PWM1                  |                    |

|   | 19  | PF6      |               | AQD2B/PWM2                  |                    |

|   | 20  | PF7      | Input/Output  | AQD2A/PWM3                  |                    |

|   | 21  | PC0      | Output        | TXD                         | Serial Port D      |

|   | 22  | PC1/PG2  | Input/Output  | RXD/TXF                     | Serial Port D      |

|   |     |          |               |                             | Serial Port F      |

|   | 23  | PC2      | Output        | TXC                         | Serial Port C      |

|   | 24  | PC3/PG3  | Input/Output  | RXC/RXF                     | Serial Port C      |

|   |     | -        |               | -                           | Serial Port F      |

|   |     |          |               | I7/SCS                      | External Address 7 |

|   | 25  | PE7      | Input/Output  |                             | Slave Port         |

| Pin |    | Pin Name | Default Use  | Alternate Use | Notes             |

|-----|----|----------|--------------|---------------|-------------------|

|     |    |          |              |               | hip Select        |

|     | 26 | PE5      | Input/Output | I5/INT1B      |                   |

|     | 27 | PE4      | Input/Output | I4/INT0B      |                   |

|     | 28 | PE1      | Input/Output | I1/INT1A      | I/O Strobe 1      |

|     |    |          |              |               | Interrupt 1A      |

|     | 29 | PE0      | Input/Output | IO/INTOA      | I/O Strobe 0      |

|     |    |          |              |               | Interrupt 0A      |

|     | 30 | PG7      | Input/Output | RXE           | Serial Port E     |

|     | 31 | PG6      | Input/Output | TXE           | Serial Port E     |

|     | 32 | IOWR     | Output       |               | External          |

| Н   |    |          | _            |               | write strobe      |

| e   | 33 | /IORD    | Input        |               | External          |

| a   |    |          |              |               | read strobe       |

| d   | 34 | PD4      | Input/Output | ATXB          | Alternate         |

| e   |    |          |              |               | Serial Port B     |

| r   | 35 | PD5      | Input/Output | ARXB          | Alternative       |

|     |    |          |              |               | Serial Port B     |

|     | 36 | /RES     | Reset output | Reset input   | Reset output from |

| J   |    |          |              |               | Reset Generator   |

| 1   | 37 | VBAT     |              |               |                   |

|     | 38 | GND      |              |               |                   |

|     | 39 | +5V      |              |               |                   |

|     | 40 | GND      |              |               |                   |

Table 4: I/O of Rabbit 3000, continued

# 2.3 RCM3700 Memory & I/O Bus

The core module typically comes with onboard memories large enough for your application. In this case they are 512 KB of flash memory and 512 KB of SRAM (RCM3700) or 256 KB each (RCM3710). A Flash Memory Bank Select jumper configuration option based on 0  $\Omega$  surface-mounted resistors exists at header JP1 on the RCM3700 modules. This option, used in conjunction with some configuration macros, allows Dynamic C to compile two different co-resident programs for the upper and lower halves of the 512K flash in such a way that both programs start at logical address 0000. This is useful for applications that require a resident download manager and a separate downloaded program.

An additional 1 MB of serial flash memory is available for mass storage purposes such as data and web pages.

Thus the address lines (A0-A18) and all the data lines (D0-D7) are routed internally to the onboard flash memory and SRAM chips. However, I/O write (/IOWR) and I/O read (/IORD) are available for interfacing to external devices.

Parallel Port A can be used as an external I/O data bus to isolate external I/O

from the main data bus. Parallel Port B pins PB2-PB5 and PB7 can also be used as an auxiliary address bus.

It is noted that /RES is an output from the reset circuitry that can be used to reset other peripheral devices. This pin can also be used to reset the microprocessor.

## 2.4 RCM3700 Serial, Ethernet & Programming Ports

The core module provides five serial ports designated as Serial Ports A, C, D, E, and F. All five serial ports can operate in an asynchronous mode up to the baud rate of the system clock divided by 8. An asynchronous port can handle 7 or 8 data bits. A 9th bit address scheme, where an additional bit is sent to mark the first byte of a message, is also supported.

Serial Port A is normally used as a programming port, but may be used either as an asynchronous or as a clocked serial port once the RCM3700 has been programmed and is operating in the Run Mode.

Serial Ports C and D can also be operated in the clocked serial mode. In this mode, a clock line synchronously clocks the data in or out. Either of the two communicating devices can supply the clock. Serial Ports E and F can also be configured as HDLC serial ports. The IrDA protocol is also supported in SDLC format by these two ports.

It is noted that Serial Ports C and D, and Serial Port F share some common pins on header J1 and hence only one of the two can be used at any one time. The choice of port(s) depends on the application. Serial Ports C and D are for clock serial links while Serial Port F is for an HDLC serial link.

The core module has an Ethernet port (J3) complete with an RJ45 socket. Two LEDs are placed next to the RJ-45 Ethernet socket, one to indicate an Ethernet link (LINK) and one to indicate Ethernet activity (ACT). The RJ-45 connector is shielded to minimize EMI effects to/from the Ethernet signals.

Serial Port A has special features that allow it to cold-boot the system after reset. Serial Port A is also the port that is used for software development under Dynamic C. The RCM3700 is accessed using a 10-pin program header labeled J2. The programming port uses the Rabbit 3000's Serial Port A for communication, and is used for the following operations:

- Programming/debugging

- Cloning

- Remote program download/debug over an Ethernet connection

The Rabbit 3000 startup-mode pins (SMODE0, SMODE1) are available at the programming port so that an externally connected device can force the RCM3700 to start up in an external bootstrap mode. The RCM3700 can be reset by Dynamic C via the /RESET line on the programming port.

The clock line for Serial Port A is presented to the programming port, which makes synchronous serial communication possible.

The programming port is used to start the RCM3700 in a mode where the RCM3700 will download a program from the port and then execute the program. It is also used during debugging. The programming port may also be used as an application port when necessary.

All three clocked Serial Port A signals are available as:

- a synchronous serial port;

- an asynchronous serial port, with the clock line usable as a general CMOS input;

- two general-purpose CMOS inputs and one general-purpose CMOS output.

The two startup-mode pins, SMODE0 and SMODE1, are available as general CMOS inputs after they are read during the initial boot-up. The logic state of these two pins determines the startup procedure after a reset. The status pin may also be used as a general-purpose CMOS output.

For convenience, the RCM3700 is automatically set into program mode when the PROG connector on the programming cable is attached, and automatically into run mode when no programming cable is attached. The DIAG connector of the programming cable may be used on header J2 of the RCM3700 Prototyping Board with the RCM3700 operating in the run mode. This allows the programming port to be used as a regular serial port.

It is noted that the RCM3700 board does not have any serial transceivers directly on the board. These transceivers may be incorporated on the mother-board the RCM3700 is mounted on. The manufacturer has Prototyping Boards with RS232, RS-485 and IrDA transceiver chips mounted. However, it is quite straightforward to build your own.

# 2.5 RCM3700 Special Features

The RCM3700 uses the Rabbit 3000 microprocessor's internal clock doubler that allows half-frequency crystals to be used to reduce radiated emissions. The 22.1 MHz frequency specified for the RCM3700 is generated using an 11.06 MHz resonator. The clock doubler may be disabled if 22.1 MHz clock speed is not required. This will reduce power consumption and reduce radiated emissions.

Another special feature is spectrum spreading. The Rabbit 3000 uses a spectrum spreader unit that modifies the clock by shortening and lengthening clock cycles. The effect of this is to spread the spectral energy of the clock harmonics over a fairly wide range of frequencies. This limits the peak energy of the harmonics and reduces EMI that may interfere with other devices as well as reducing the readings in government mandated EMI tests. The spectrum spreader has two operating modes, normal spreading and strong spreading. The spreader can also be turned off.

# 2.6 A RabbitCore Application – Mass Storage using MultiMediaCard (MMC)

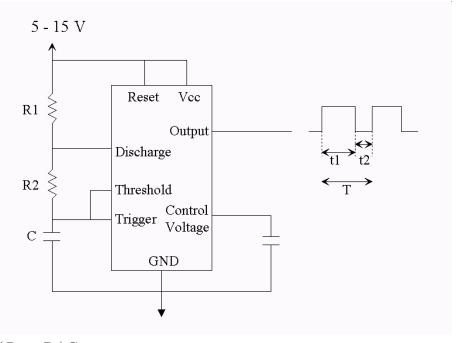

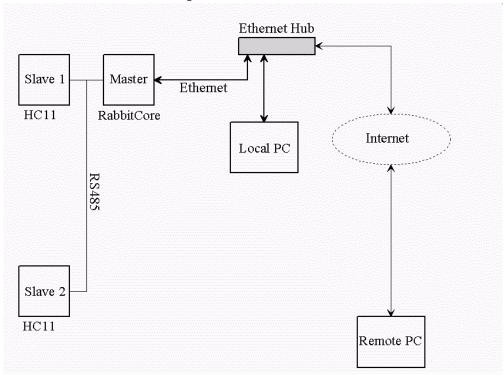

In a later section of this series of lectures, a demonstration system is set up using a Rabbit Core as a web server accessible in the Internet. The Rabbit Core acts as an embedded Ethernet Module talking to two separate legacy boards (HC11) via an RS485 network. Each legacy board is a thermometer using a thermistor with a 555 timer circuit to measure resistance. It demonstrates quite a few elements in a distributed laboratory instrumentation system. In this section an memory extension to the RabbitCore is described. It is hoped that it provides some useful information for those who require mass data storage in small embedded systems.

Embedded processors such as RabbitCores and TINIs are really powerful workhorses in embedded systems around laboratories. Many laboratory experiments and projects do not require any more processing power than what is available in these processors. However, being 8-bit processors, these systems usually lacks mass storage capabilities. RabbitCore is typically limited to 1MB of Flash and SRAM. The inclusion of an additional 1 MB of serial Flash memory in the newer core such as RCM3700 is a much welcomed feature.

There are many situations when more mass storage capacity is required. A field data logging system is a classic example. While the process of data logging is straightforward and can be handled by a RabbitCore easily, the amount of data to be collected often prove too much for such a core module. If the embedded system can be networked to other computers, data collected by the former can be transferred to the mass storage of a PC. A better solution is to implement local mass storage on the embedded system itself.

In PCs, hard disks have been standard mass storage all along. Unfortunately, connecting standard hard disks to a RabbitCore system, while tempting in terms of costs, is rather complicated in both software and hardware. One is thus forced to use the PC itself as a secondary storage. This is acceptable in many applications. However, it leaves an umbilical cord between the embedded system and the PC.

The recent crop of miniature USB Flash memories, emulating disk drives (called by different names including Pen Drive) in PC systems, is another tempting solution. Unfortunately, yet again, the implementation of USB host in systems like RabbitCore or TINI is difficult if not practically impossible.

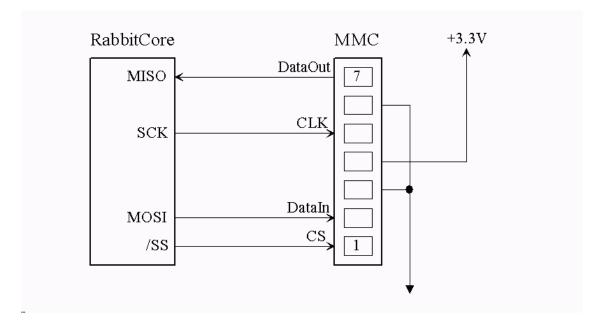

There is another solution though. It turns out that commercially available Flash memories designed typically for consumer products such as digital cameras are readily available and are affordable. For a few tens of dollars one can get a 128 Mbytes of Flash card. There are several types of such cards in the market. One candidate best suited for interfacing to a small embedded system is the MultiMediaCard (MMC) because it requires only a few lines for interfacing. A high speed serial interface using Serial Peripheral Interface (SPI) allows data to be transferred.

This section describes a small project to incorporate an MMC mass storage device on a RabbitCore thereby enhancing the power of this 8-bit embedded processor significantly. With the possible of having 512 MB of removable storage

| MultiMediaCard                                              | SPI                                                                                            |

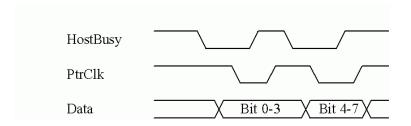

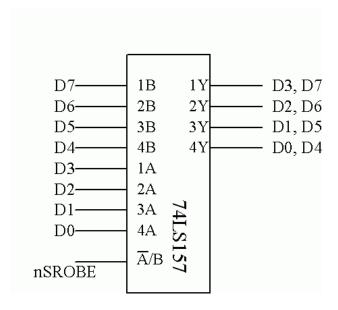

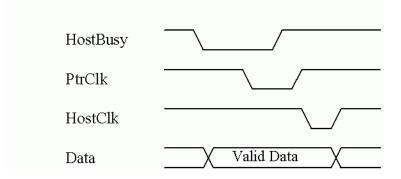

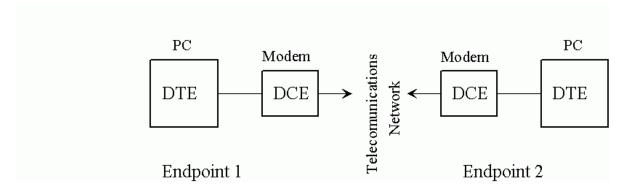

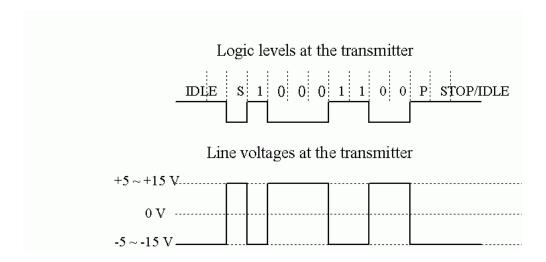

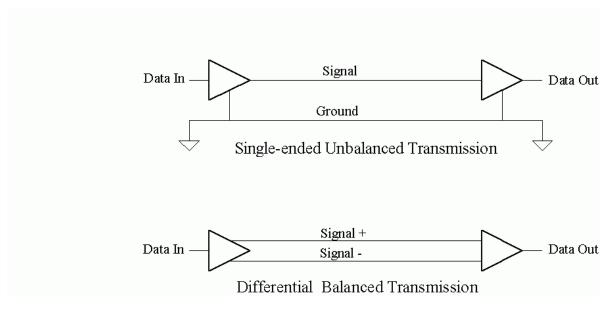

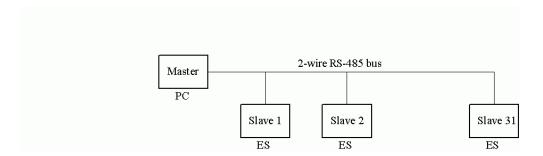

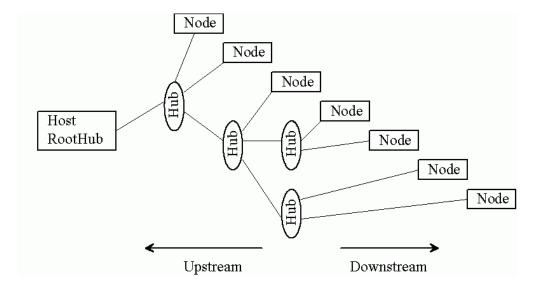

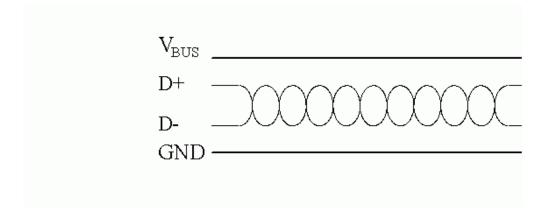

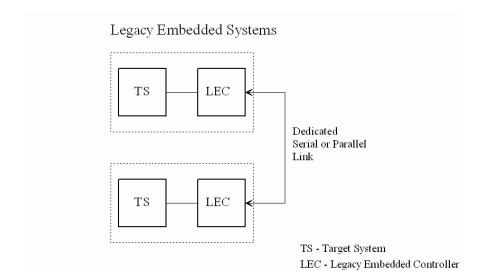

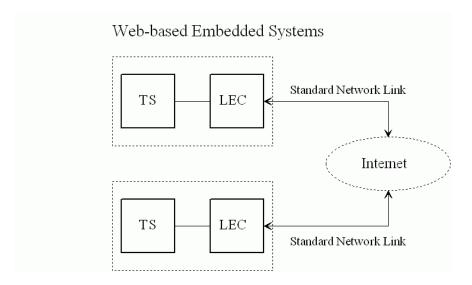

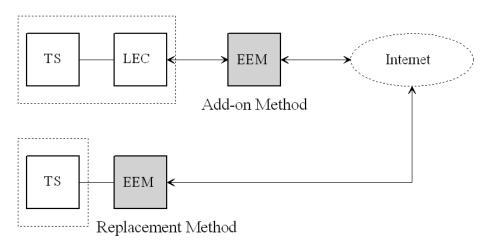

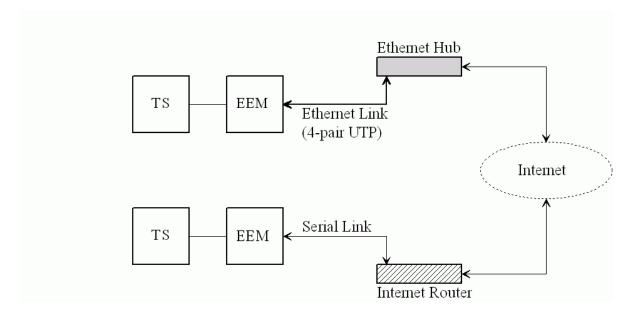

|-------------------------------------------------------------|------------------------------------------------------------------------------------------------|