## Outline

- Introduction "Is there a limit?"

- Transistors "CMOS building blocks"

- Parasitics I "The [un]desirables"

- Parasitics II "Building a full MOS model"

- The CMOS inverter "A masterpiece"

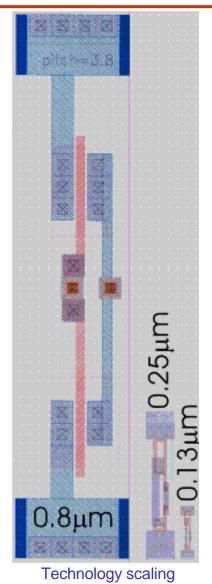

- Technology scaling "Smaller, Faster and Cooler"

- Technology "Building an inverter"

- Gates I "Just like LEGO"

- The pass gate "An useful complement"

- Gates II "A portfolio"

- Sequential circuits "Time also counts!"

- DLLs and PLLs " A brief introduction"

- Storage elements "A bit in memory"

- Scaling objectives

- Scaling variables

- Scaling consequences:

- Device area

- Transistor density

- Gate capacitance

- Drain current

- Gate delay

- Power

- Power density

- Interconnects

### Scaling, why is it done?

Paulo Moreira

- Technology scaling has a <u>threefold objective</u>:

- Increase the transistor density

- Reduce the gate delay

- Reduce the power consumption

- At present, between two technology generations, the objectives are:

- Doubling of the transistor density;

- Reduction of the gate delay by 30% (43% increase in frequency);

- Reduction of the power by 50% (at 43% increase in frequency);

- How is scaling achieved?

- All the device dimensions (lateral and vertical) are reduced by  $1/\alpha$

- Concentration densities are increased by  $\boldsymbol{\alpha}$

- Device voltages reduced by  $1/\alpha$  (not in all scaling methods)

- Typically  $1/\alpha = 0.7$  (30% reduction in the dimensions)

#### • The **scaling variables** are:

| <ul> <li>Supply voltage:</li> </ul>       | $V_{dd}$        | $\rightarrow$ | V <sub>dd</sub> / $lpha$   |

|-------------------------------------------|-----------------|---------------|----------------------------|

| <ul> <li>Gate length:</li> </ul>          | L               | $\rightarrow$ | L/α                        |

| <ul> <li>Gate width:</li> </ul>           | W               | $\rightarrow$ | W/α                        |

| <ul> <li>Gate-oxide thickness:</li> </ul> | t <sub>ox</sub> | $\rightarrow$ | t <sub>ox</sub> / $\alpha$ |

| <ul> <li>Junction depth:</li> </ul>       | X <sub>j</sub>  | $\rightarrow$ | $X_j$ / $lpha$             |

| <ul> <li>Substrate doping:</li> </ul>     | N <sub>A</sub>  | $\rightarrow$ | $N_A \times \alpha$        |

This is called **<u>constant field</u>** scaling because the electric field across the gate-oxide does not change when the technology is scaled

If the power supply voltage is maintained constant the scaling is called **<u>constant voltage</u>**. In this case, the electric field across the gate-oxide increases as the technology is scaled down.

Due to gate-oxide breakdown, below 0.8µm only "constant field" scaling is used.

Some consequences of 30% scaling in the constant field regime ( $\alpha = 1.43$ ,  $1/\alpha = 0.7$ ):

• Device/die area:

$$W \times L \rightarrow (1/\alpha)^2 = 0.49$$

- In practice, microprocessor <u>die size grows</u> about 25% per technology generation! This is a result of added functionality.

- Transistor density:

(unit area) /(W  $\times$  L)  $\rightarrow \alpha^2$  = 2.04

In practice, <u>memory density</u> has been scaling as expected. (not true for microprocessors...)

• Gate capacitance:

$$W \times L / t_{ox} \rightarrow 1/\alpha = 0.7$$

• Drain current:

$$(W/L)\times(V^2/t_{ox})\rightarrow 1/\alpha=0.7$$

• Gate delay:

$(C \times V) / I \rightarrow 1/\alpha = 0.7$ Frequency  $\rightarrow \alpha = 1.43$

In practice, microprocessor frequency has doubled every technology generation (2 to 3 years)! This faster increase rate is due to highly pipelined architectures ("less gates per clock cycle")

• Power:

$$C \times V^2 \times f \rightarrow (1/\alpha)^2 = 0.49$$

• Power density:

$$1/t_{ox} \times V^2 \times f \rightarrow 1$$

Active capacitance/unit-area: Power dissipation is a function of the operation <u>frequency</u>, the power <u>supply voltage</u> and of the <u>circuit size</u> (number of devices). If we normalize the power density to V<sup>2</sup> × f we obtain the <u>active</u> <u>capacitance per unit area</u> for a given circuit. This parameter can be compared with the oxide capacitance per unit area:

$$1/t_{ox} \rightarrow \alpha = 1.43$$

In practice, for microprocessors, the active capacitance/unitarea only increases between 30% and 35%. Thus, the twofold improvement in logic density between technologies is not achieved.

Paulo Moreira

- Interconnects scaling:

- Higher densities are only possible if the interconnects also scale.

- Reduced width  $\rightarrow$  increased resistance

- Denser interconnects  $\rightarrow$  higher capacitance

- To account for <u>increased parasitics</u> and <u>integration</u> <u>complexity</u> more interconnection layers are added:

- thinner and tighter layers  $\rightarrow$  local interconnections

- thicker and sparser layers  $\rightarrow$  global interconnections and power

Interconnects are scaling as expected

| Parameter                               | <b>Constant Field</b> | Constant Voltage |                        |  |

|-----------------------------------------|-----------------------|------------------|------------------------|--|

| Supply voltage (V <sub>dd</sub> )       | 1/α                   | 1                | <b>↑</b>               |  |

| Length (L)                              | 1/α                   | 1/α              |                        |  |

| Width (W)                               | 1/α                   | 1/α              | Scaling<br>Variables   |  |

| Gate-oxide thickness (t <sub>ox</sub> ) | 1/α                   | 1/α              |                        |  |

| Junction depth (X <sub>j</sub> )        | 1/α                   | 1/α              |                        |  |

| Substrate doping (N <sub>A</sub> )      | α                     | α                | $\mathbf{I}$           |  |

| Electric field across gate oxide (E)    | 1                     | α                | Device<br>Repercussion |  |

| Depletion layer thickness               | 1/α                   | 1/α              |                        |  |

| Gate area (Die area)                    | $1/\alpha^2$          | 1/α <sup>2</sup> |                        |  |

| Gate capacitance (load) (C)             | 1/α                   | 1/α              |                        |  |

| Drain-current (I <sub>dss</sub> )       | 1/α                   | α                |                        |  |

| Transconductance (g <sub>m</sub> )      | 1                     | α                | $\checkmark$           |  |

| Gate delay                              | 1/α                   | 1/α <sup>2</sup> | Circuit                |  |

| Current density                         | α                     | $\alpha^3$       |                        |  |

| DC & Dynamic power dissipation          | 1/α <sup>2</sup>      | α                |                        |  |

| Power density                           | 1                     | $\alpha^3$       | Repercussion           |  |

| Power-Delay product                     | 1/α <sup>3</sup>      | 1/α              |                        |  |

| Paulo Moreira                           | Technology scaling    |                  | 1                      |  |