### Outline

- Introduction "Is there a limit?"

- Transistors "CMOS building blocks"

- Parasitics I "The [un]desirables"

- Parasitics II "Building a full MOS model"

- The CMOS inverter "A masterpiece"

- Technology scaling "Smaller, Faster and Cooler"

- Technology "Building an inverter"

- Gates I "Just like LEGO"

- The pass gate "An useful complement"

- Gates II "A portfolio"

- Sequential circuits "Time also counts!"

- DLLs and PLLs " A brief introduction"

- Storage elements "A bit in memory"

## "Building an inverter"

- Lithography

- Physical structure

- CMOS fabrication sequence

- Advanced CMOS process

- Process enhancements

- Yield

- Layout design rules

### CMOS technology

- An Integrated Circuit is an electronic network fabricated in a single piece of a semiconductor material

- The semiconductor surface is subjected to various processing steps in which impurities and other materials are added with specific geometrical patterns

- The fabrication steps are sequenced to form three dimensional regions that act as transistors and interconnects that form the switching or amplification network

Lithography: process used to transfer patterns to each layer of the IC

Lithography sequence steps:

- <u>Designer</u>:

- Drawing the "layer" patterns on a layout editor

- <u>Silicon Foundry</u>:

- Masks generation from the layer patterns in the design data base

- Printing: transfer the mask pattern to the wafer surface

- Process the wafer to physically pattern each layer of the IC

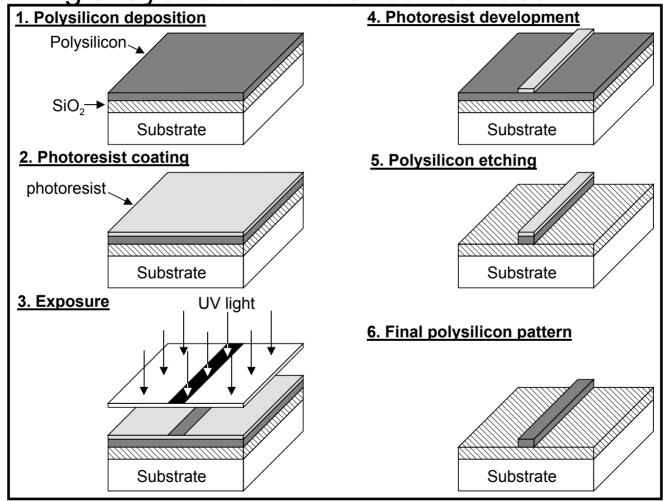

### **Basic sequence**

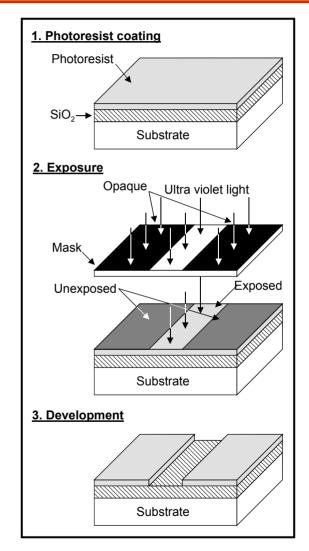

- The surface to be patterned is:

- spin-coated with photoresist

- the photoresist is dehydrated in an oven (photo resist: light-sensitive organic polymer)

- The photoresist is exposed to ultra violet light:

- For a positive photoresist exposed areas become soluble and non exposed areas remain hard

- The soluble photoresist is chemically removed (development).

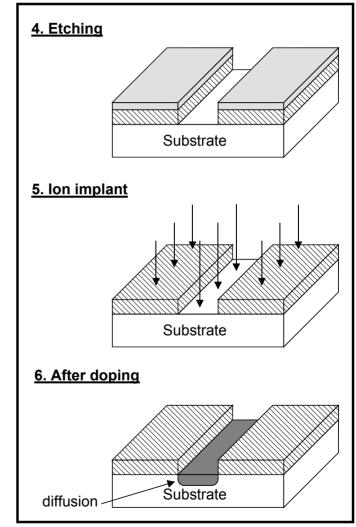

- The patterned photoresist will now serve as an etching mask for the SiO<sub>2</sub>

- The SiO<sub>2</sub> is etched away leaving the substrate exposed:

- the patterned resist is used as the etching mask

- Ion Implantation:

- the substrate is subjected to highly energized donor or acceptor atoms

- The atoms impinge on the surface and travel below it

- The patterned silicon SiO<sub>2</sub> serves as an implantation mask

- The doping is further driven into the bulk by a thermal cycle

- The lithographic sequence is repeated for each physical layer used to construct the IC. The sequence is always the same:

- Photoresist application

- Printing (exposure)

- Development

- Etching

#### Patterning a layer above the silicon surface

Paulo Moreira

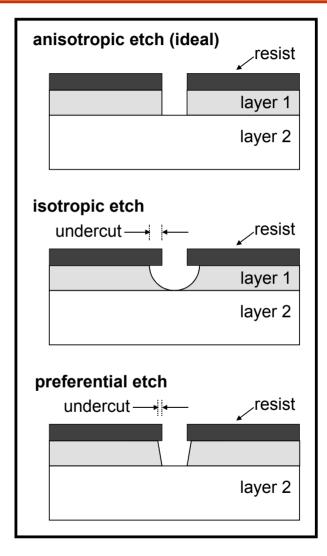

- Etching:

- Process of removing unprotected material

- Etching occurs in all directions

- Horizontal etching causes an under cut

- "preferential" etching can be used to minimize the undercut

- Etching techniques:

- Wet etching: uses chemicals to remove the unprotected materials

- Dry or plasma etching: uses ionized gases rendered chemically active by an rfgenerated plasma

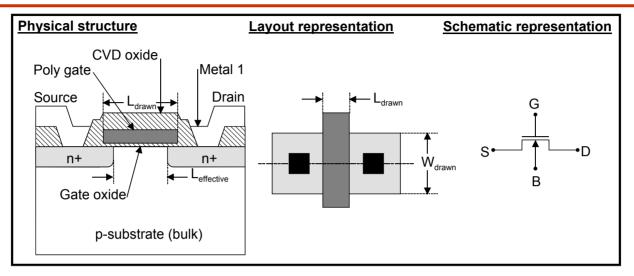

### **Physical structure**

NMOS physical structure:

- p-substrate

- n+ source/drain

- gate oxide (SiO<sub>2</sub>)

- polysilicon gate

- CVD oxide

- metal 1

- L<sub>eff</sub> < L<sub>drawn</sub> (lateral doping effects)

NMOS layout representation:

- Implicit layers:

- oxide layers

- substrate (bulk)

- Drawn layers:

- n+ regions

- polysilicon gate

- oxide contact cuts

- metal layers

#### Paulo Moreira

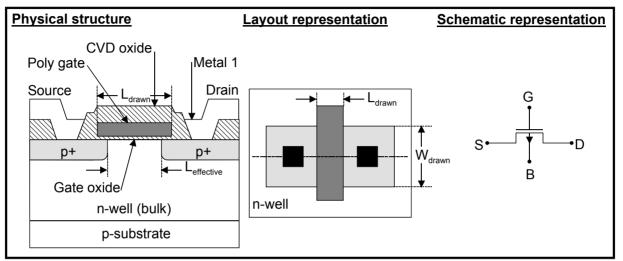

### **Physical structure**

PMOS physical structure:

- p-substrate

- n-well (bulk)

- p+ source/drain

- gate oxide (SiO<sub>2</sub>)

- polysilicon gate

- CVD oxide

- metal 1

PMOS layout representation:

- Implicit layers:

- oxide layers

- Drawn layers:

- n-well (bulk)

- n+ regions

- polysilicon gate

- oxide contact cuts

- metal layers

#### Paulo Moreira

Technology

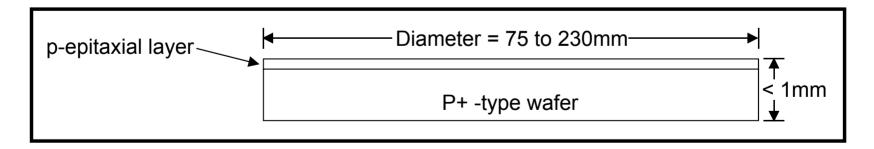

- 0. Start:

- For an n-well process the starting point is a p-type silicon wafer:

- wafer: typically 75 to 230mm in diameter and less than 1mm thick

#### 1. Epitaxial growth:

- A single p-type single crystal film is grown on the surface of the wafer by:

- subjecting the wafer to high temperature and a source of dopant material

- The epi layer is used as the base layer to build the devices

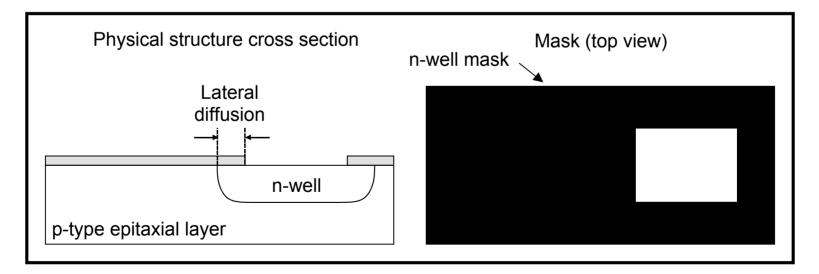

#### 2. N-well Formation:

- PMOS transistors are fabricated in n-well regions

- The first mask defines the n-well regions

- N-well's are formed by ion implantation or deposition and diffusion

- Lateral diffusion limits the proximity between structures

- Ion implantation results in shallower wells compatible with today's fine-line processes

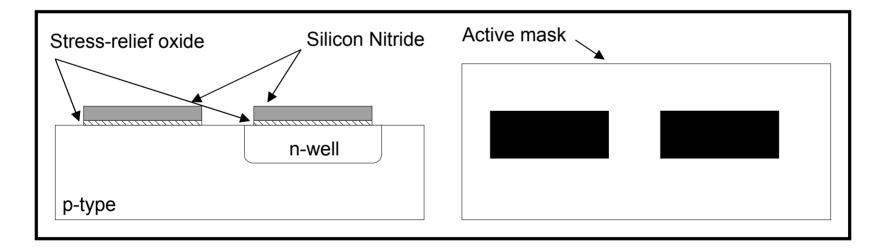

#### **3. Active area definition:**

- Active area:

- · planar section of the surface where transistors are build

- defines the gate region (thin oxide)

- defines the n+ or p+ regions

- A thin layer of SiO<sub>2</sub> is grown over the active region and covered with silicon nitride

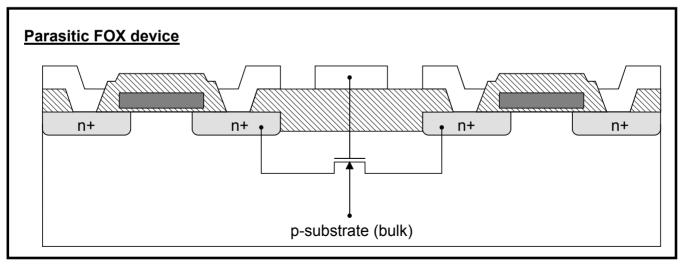

#### 4. Isolation:

- Parasitic (unwanted) FET's exist between unrelated transistors (Field Oxide FET's)

- Source and drains are existing source and drains of wanted devices

- Gates are metal and polysilicon interconnects

- The threshold voltage of FOX FET's are higher than for normal FET's

- FOX FET's threshold is made high by:

- introducing a channel-stop diffusion that raises the impurity concentration in the substrate in areas where transistors are not required

- making the FOX thick

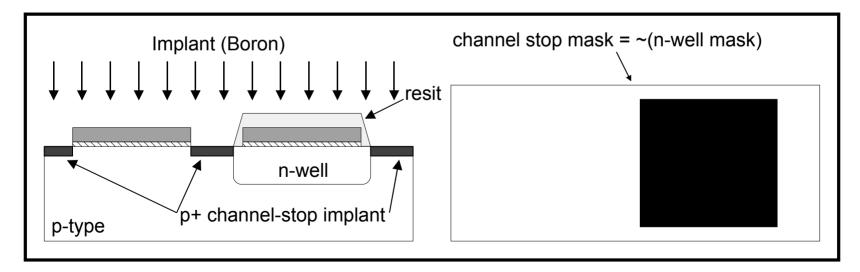

#### 4.1 Channel-stop implant

The silicon nitride (over n-active) and the photoresist (over n-well) act as masks for the channel-stop implant

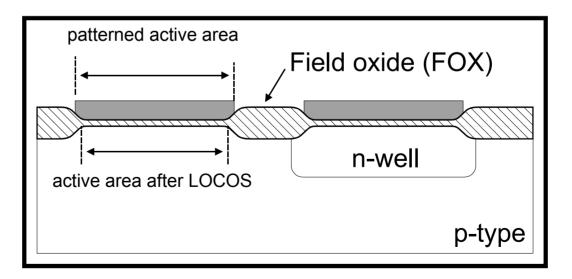

#### 4.2 Local oxidation of silicon (LOCOS)

- The photoresist mask is removed

- The SiO<sub>2</sub>/SiN layers will now act as a masks

- The thick field oxide is then grown by:

- exposing the surface of the wafer to a flow of oxygen-rich gas

- The oxide grows in both the vertical and lateral directions

- This results in a active area smaller than patterned

- Silicon oxidation is obtained by:

- Heating the wafer in a oxidizing atmosphere:

- Wet oxidation: water vapor, T = 900 to 1000°C (rapid process)

- Dry oxidation: Pure oxygen, T = 1200°C (high temperature required to achieve an acceptable growth rate)

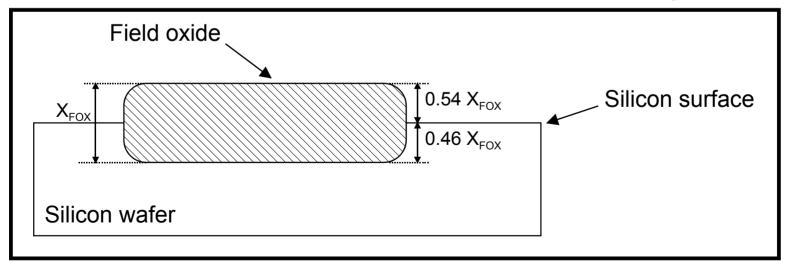

- Oxidation consumes silicon

- SiO<sub>2</sub> has approximately twice the volume of silicon

- The FOX is recedes below the silicon surface by  $0.46X_{FOX}$

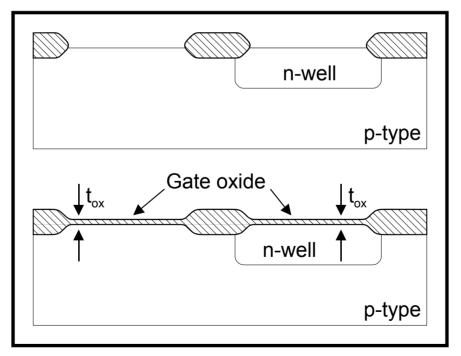

#### 5. Gate oxide growth

- The nitride and stress-relief oxide are removed

- The devices threshold voltage is adjusted by:

- adding charge at the silicon/oxide interface

- The well controlled gate oxide is grown with thickness t<sub>ox</sub>

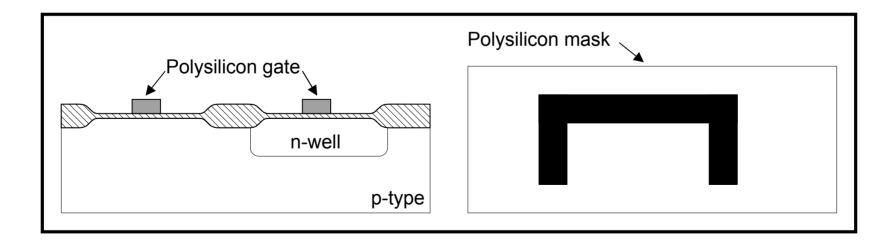

#### 6. Polysilicon deposition and patterning

- A layer of polysilicon is deposited over the entire wafer surface

- The polysilicon is then patterned by a lithography sequence

- All the MOSFET gates are defined in a single step

- The polysilicon gate can be doped (n+) while is being deposited to lower its parasitic resistance (important in high speed fine line processes)

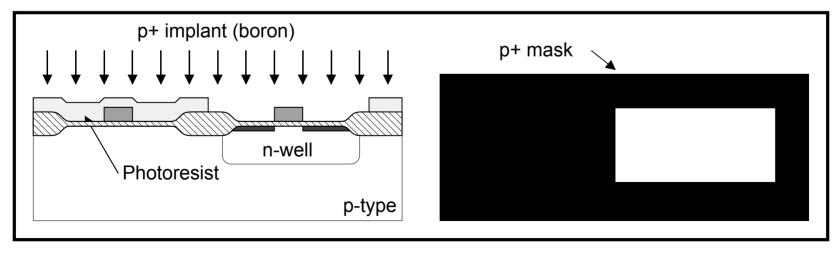

### 7. PMOS formation

- Photoresist is patterned to cover all but the p+ regions

- A boron ion beam creates the p+ source and drain regions

- The polysilicon serves as a mask to the underlying channel

- This is called a self-aligned process

- · It allows precise placement of the source and drain regions

- During this process the gate gets doped with p-type impurities

- Since the gate had been doped n-type during deposition, the final type (n or p) will depend on which dopant is dominant

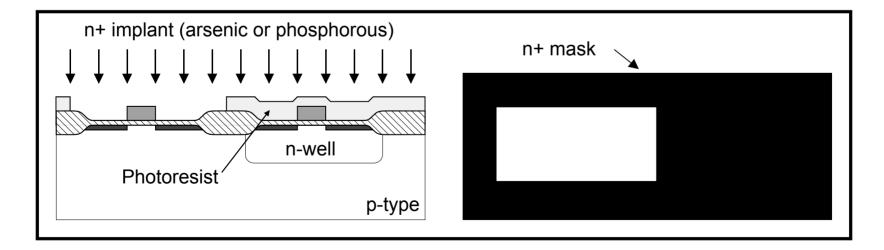

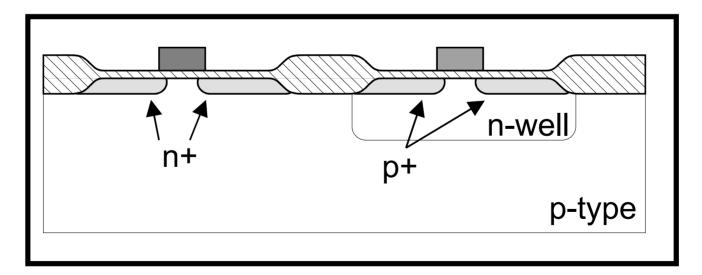

#### 8. NMOS formation

- Photoresist is patterned to define the n+ regions

- Donors (arsenic or phosphorous) are ion-implanted to dope the n+ source and drain regions

- The process is self-aligned

- The gate is n-type doped

#### 9. Annealing

- After the implants are completed a thermal annealing cycle is executed

- This allows the impurities to diffuse further into the bulk

- After thermal annealing, it is important to keep the remaining process steps at as low temperature as possible

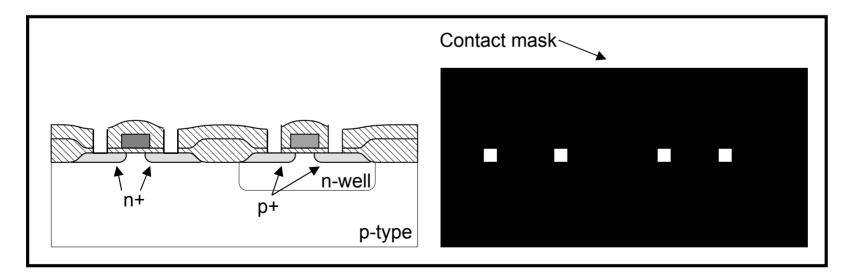

#### **10. Contact cuts**

- The surface of the IC is covered by a layer of CVD oxide

- The oxide is deposited at low temperature (LTO) to avoid that underlying doped regions will undergo diffusive spreading

- Contact cuts are defined by etching SiO<sub>2</sub> down to the surface to be contacted

- These allow metal to contact diffusion and/or polysilicon regions

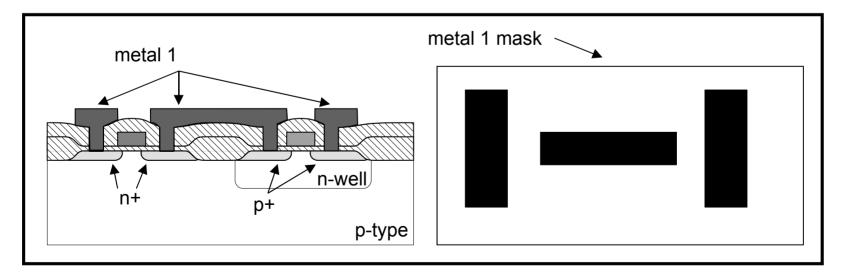

#### 11. Metal 1

A first level of metallization is applied to the wafer surface and selectively etched to produce the interconnects

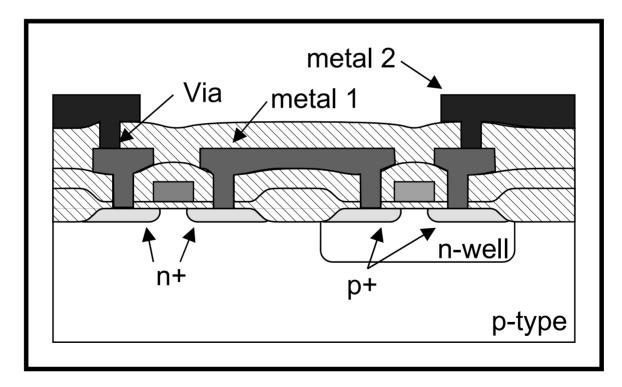

#### 12. Metal 2

- Another layer of LTO CVD oxide is added

- Via openings are created

- Metal 2 is deposited and patterned

#### 13. Over glass and pad openings

- A protective layer is added over the surface:

- The protective layer consists of:

- A layer of SiO<sub>2</sub>

- Followed by a layer of silicon nitride

- The SiN layer acts as a diffusion barrier against contaminants (passivation)

- Finally, contact cuts are etched, over metal 2, on the passivation to allow for wire bonding.

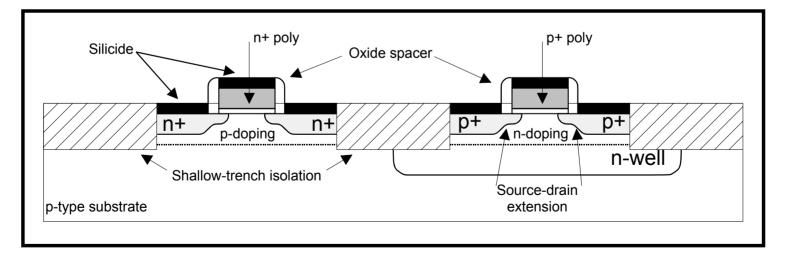

### Advanced CMOS processes

- Shallow trench isolation

- n+ and p+-doped polysilicon gates (low threshold)

- source-drain extensions LDD (hot-electron effects)

- Self-aligned silicide (spacers)

- Non-uniform channel doping (short-channel effects)

### **Process enhancements**

- Up to six metal levels in modern processes

- Copper for metal levels 2 and higher

- Stacked contacts and vias

- Chemical Metal Polishing for technologies with several metal levels

- For analogue applications some processes offer:

- capacitors

- resistors

- bipolar transistors (BiCMOS)

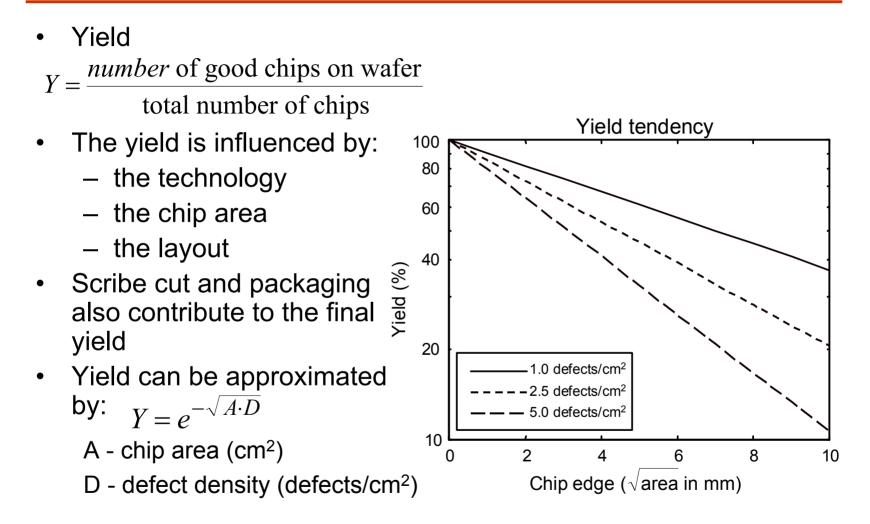

# Yield

- The limitations of the patterning process give rise to a set of mask design guidelines called <u>design rules</u>

- Design rules are a set of guidelines that specify the minimum dimensions and spacings allowed in a layout drawing

- Violating a design rule might result in a <u>non-functional</u> circuit or in a <u>highly reduced yield</u>

- The design rules can be expressed as:

- A list of minimum feature sizes and spacings for all the masks required in a given process

- Based on single parameter  $\lambda$  that characterize the linear feature (e.g. the minimum grid dimension).  $\lambda$  base rules allow simple scaling

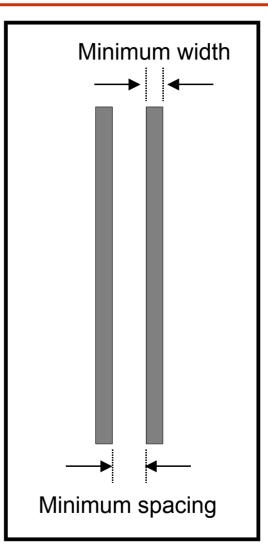

- Minimum line-width:

- smallest dimension permitted for any object in the layout drawing (minimum feature size)

- Minimum spacing:

- smallest distance permitted between the edges of two objects

- This rules originate from the resolution of the optical printing system, the etching process, or the surface roughness

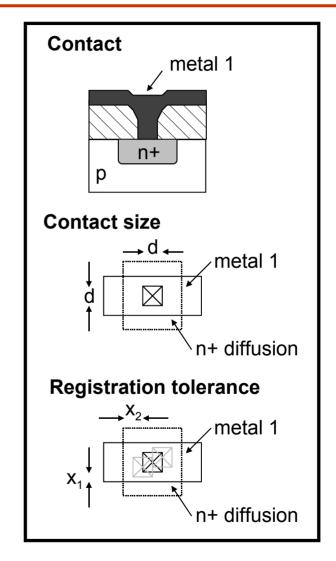

- Contacts and vias:

- minimum size limited by the lithography process

- large contacts can result in cracks and voids

- Dimensions of contact cuts are restricted to values that can be reliably manufactured

- A minimum distance between the edge of the oxide cut and the edge of the patterned region must be specified to allow for misalignment tolerances (registration errors)

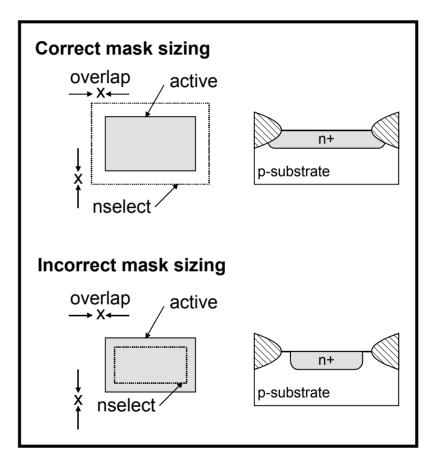

- MOSFET rules

- n+ and p+ regions are formed in two steps:

- the <u>active</u> area openings allow the implants to penetrate into the silicon substrate

- the <u>nselect</u> or <u>pselect</u> provide photoresist openings over the active areas to be implanted

- Since the formation of the diffusions depend on the overlap of two masks, the nselect and pselect regions must be larger than the corresponding active areas to allow for misalignments

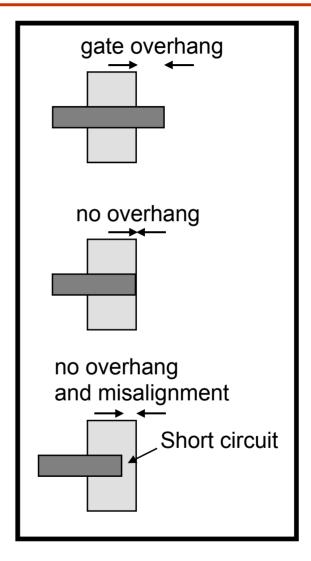

- Gate overhang:

- The gate must overlap the active area by a minimum amount

- This is done to ensure that a misaligned gate will still yield a structure with separated drain and source regions

- A modern process have thousands of rules to be verified

- Programs called <u>D</u>esign <u>R</u>ule <u>C</u>heckers assist the designer in that task