### OUTLINE

- I INTRODUCTION

- **II DESIGN METHODOLOGY: AN OVERVIEW**

- **III ABSTRACTION LEVELS IN ALLIANCE**

- **IV VHDL: A HARDWARE DESCRIPTION LANGUAGE**

- **V VHDL**: THE ALLIANCE SUBSET

Nizar Abdallah

### Why a Subset ? (1)

1 - Complex Language

Developing a compiler is hard and time consuming

2

Nizar Abdallah

### Why a Subset ? (2)

2 - Educational Needs

3

Understanding Time

Univocal (Ex: One way in describing a register)

Nizar Abdallah

### Why a Subset ? (3)

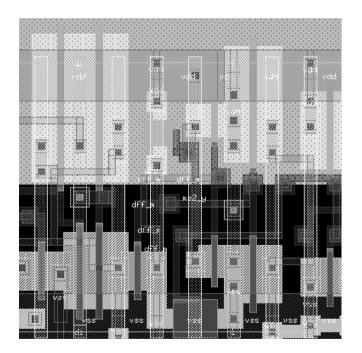

### 3 - Our Environment

4

Nizar Abdallah

### 5 **Criterions** Users versus Tools Requirements Finding the Good Balance <u>USERS</u> TOO

Nizar Abdallah

### **Tools' Requirements (1)**

Which Tools use VHDL?

- Simulator

- Synthesis Tools

- Placer & Router

- Functional Abstractor

- Formal Proover

6

Nizar Abdallah

### **Tools' Requirements (2)**

### > Synthesis Tools

- ★ A register must be identified in a syntactical way

- ★ A bus must be identified in a syntactical way

- $\checkmark$  Signals must have the BIT type ('0', '1')

- **✗** No timing

### **FORMAL PROOVER**

- ★ A register must be identified in a syntactical way

- X A bus must be identified in a syntactical way

Nizar Abdallah

### **Tools' Requirements (3)**

### PLACER & ROUTER

★ No mixing between structural and behavioral views

8

### **FUNCTIONAL ABSTRACTOR**

★ VHDL subset as close as possible to the hardware

### **SIMULATOR**

- ✗ No abstract types

- $\checkmark$  No timing

Nizar Abdallah

### **Users' Requirements**

## Looking for the Largest Subset ...

9

Nizar Abdallah

### **The Good Subset**

10 🖱

✓ Lets the user describe his circuit easily

✓ Do not deteriorate the tool with a complex language

Nizar Abdallah

### **Alliance Internal & External Aspects**

### External Aspect

- ✓ Name

✓ Interface

X Color

X Temperature

- × -----

# ANN attes visiture

### Internal Aspect

- ✔ Structural✔ Behavioral

- ✔ Signal✔ Component

- ✓ Instance

Nizar Abdallah

12

Nizar Abdallah

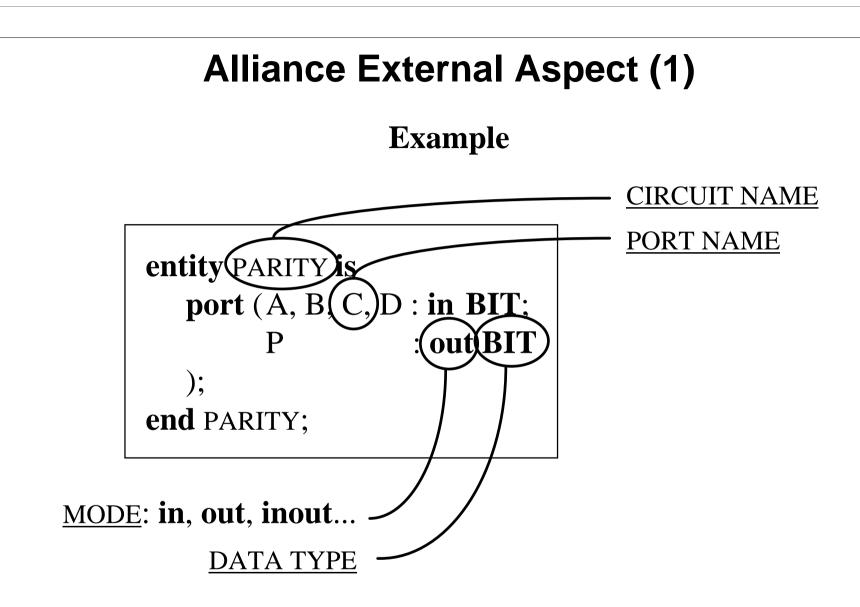

### Alliance External Aspect (2)

Example

Nizar Abdallah

VHDL: THE ALLIANCE SUBSET VLSI Design Techniques **13**<sup>₽</sup>

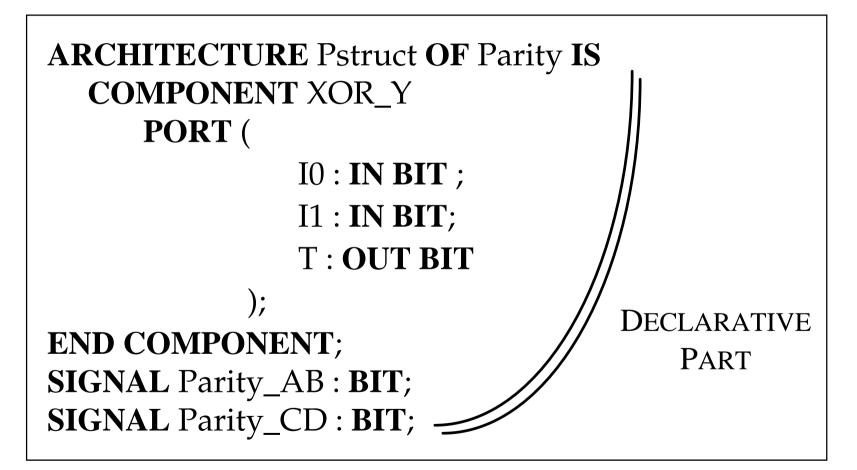

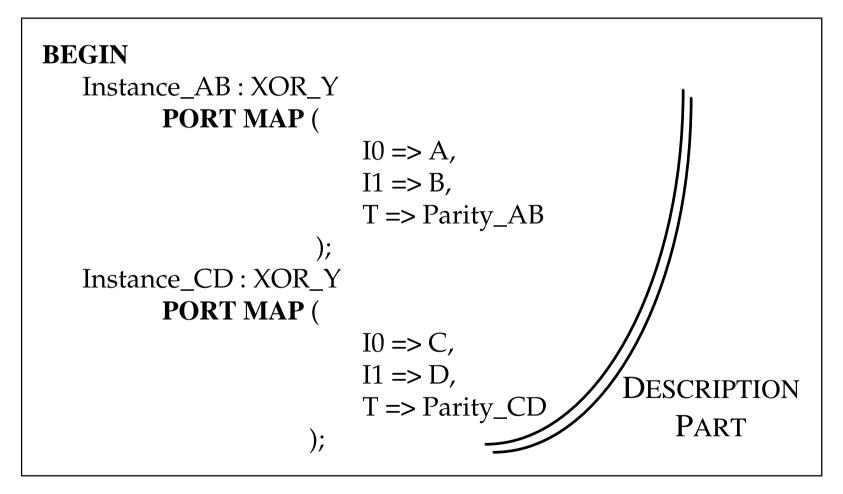

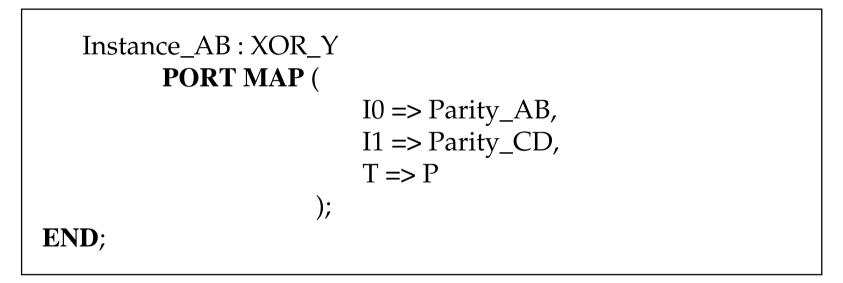

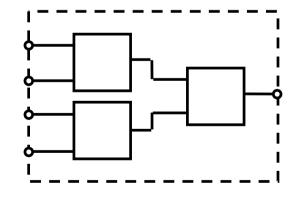

### Alliance Internal Aspect (1)

Structural

Nizar Abdallah

VHDL: THE ALLIANCE SUBSET VLSI Design Techniques 14<sup>®</sup>

### **Alliance Internal Aspect (2)**

Structural

Nizar Abdallah

VHDL: THE ALLIANCE SUBSET VLSI Design Techniques 15<sup>®</sup>

### **Alliance Internal Aspect (3)**

#### **Structural**

Nizar Abdallah

VHDL: THE ALLIANCE SUBSET VLSI Design Techniques 16

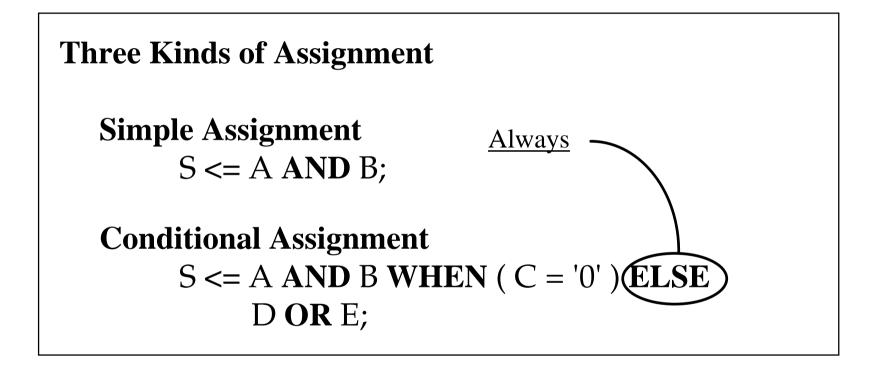

### **Alliance Internal Aspect (1)**

17 🖣

**Behavioral**

Nizar Abdallah

### Alliance Internal Aspect (2)

18<sup>4</sup>

### **Behavioral**

### • ASSERT ( Condition ) REPORT "Message" SEVERITY Level;

Very useful in large-scale design.

- •Allows encoding specific constraints and error conditions

- Provide useful messages.

- •Stop the simulation when constraints are not met.

Nizar Abdallah

### **Alliance Internal Aspect (3)**

19<sup>4</sup>

**Behavioral**

Nizar Abdallah

### Alliance Internal Aspect (4)

20<sup>4</sup>

**Behavioral**

**Selective Assignment**

WITH Address(3 downto 0) SELECT Out <= "000100" WHEN "0000", "000101" WHEN "0001",

\_\_\_\_\_

"000000" WHEN Others;

Nizar Abdallah

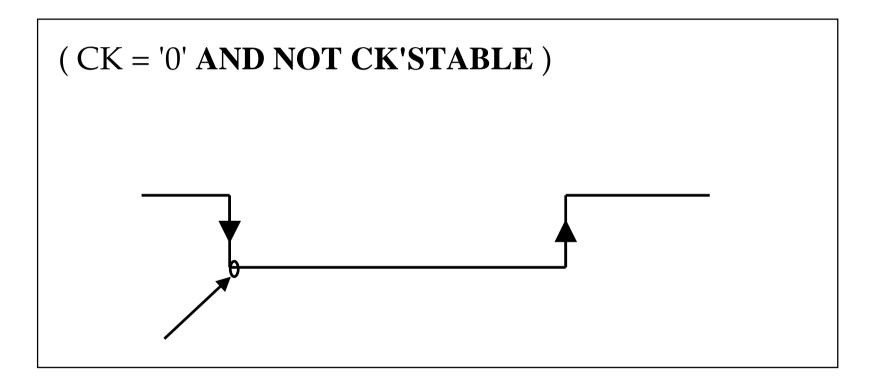

### **Alliance Internal Aspect (5)**

21<sup>4</sup>

**Behavioral**

```

REGISTERS

SIGNAL myregister : REG_BIT REGISTER;

store : BLOCK ( CK = '0' AND NOT CK'STABLE )

BEGIN

myregister <= GUARDED I0;

END BLOCK store;

```

Nizar Abdallah

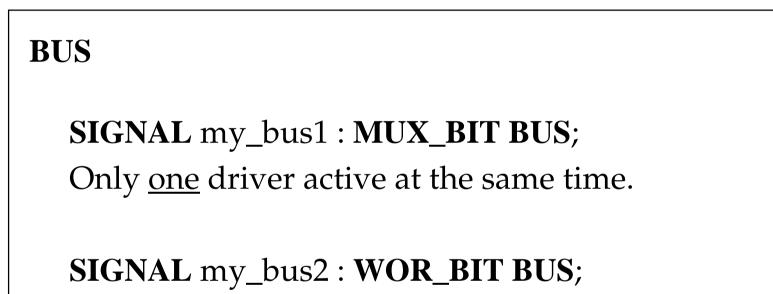

### **Alliance Internal Aspect (6)**

**Behavioral**

Nizar Abdallah

VHDL: THE ALLIANCE SUBSET VLSI Design Techniques 22 ₽

### **Alliance Internal Aspect (7)**

23<sup>4</sup>

**Behavioral**

Many drivers drive the same value.

Nizar Abdallah