# Outline

- Introduction "Is there a limit?"

- Transistors "CMOS building blocks"

- Parasitics I "The [un]desirables"

- Parasitics II "Building a full MOS model"

- The CMOS inverter "A masterpiece"

- Technology scaling "Smaller, Faster and Cooler"

- Technology "Building an inverter"

- Gates I "Just like LEGO"

- The pass gate "An useful complement"

- Gates II "A portfolio"

- Sequential circuits "Time also counts!"

- DLLs and PLLs " A brief introduction"

- Storage elements "A bit in memory"

# "CMOS building blocks"

- "Making Logic"

- Silicon switches:

- The NMOS

- Its mirror image, the PMOS

- Electrical behavior:

- Strong inversion

- Model

- How good is the approximation?

- Weak inversion

- Gain and inversion

# "Making Logic"

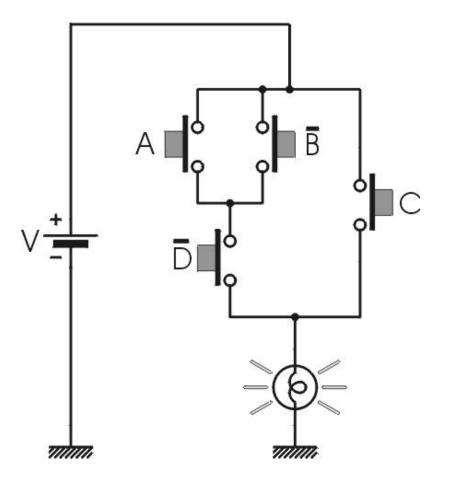

- Logic circuit "ingredients":

- Power source

- Switches

- Power gain

- Inversion

- Power always comes from some form of external EMF generator.

- NMOS and PMOS transistors:

- Can perform the last three functions

- They are the building blocks of CMOS technologies!

$$\_ight ON = (A + \overline{B}) \overline{D} + C$$

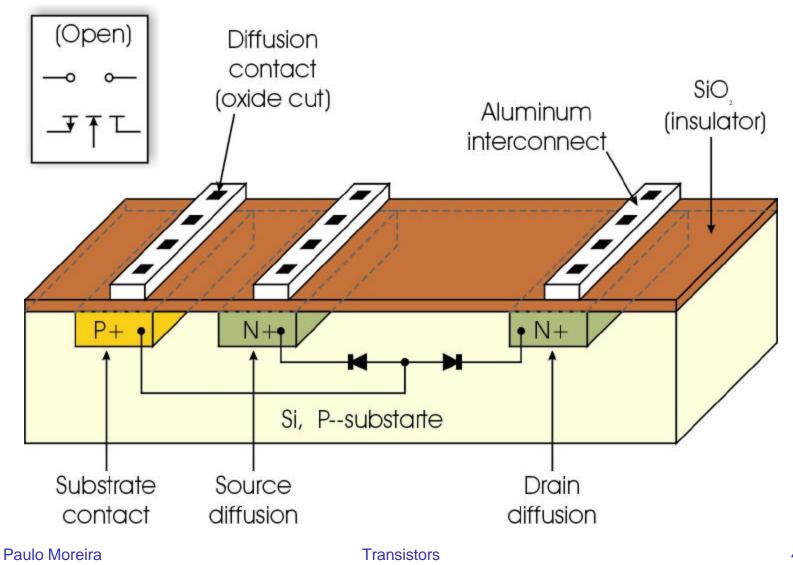

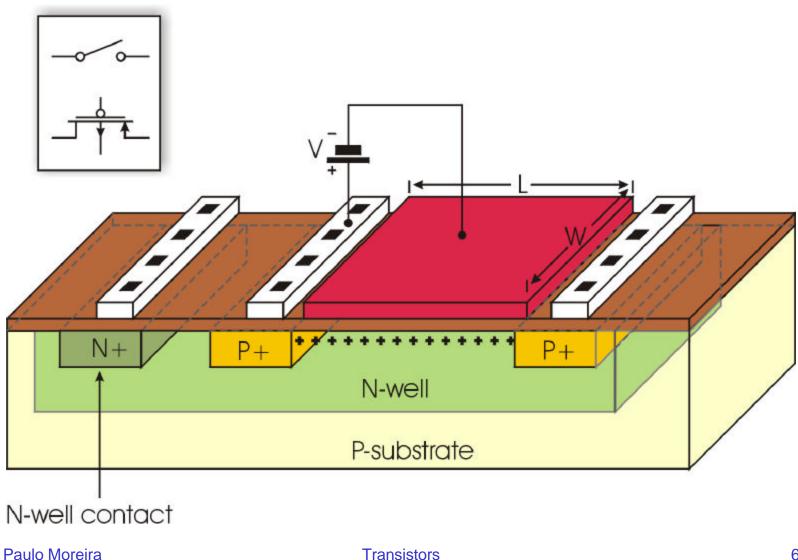

### Silicon switches: the NMOS

### Silicon switches: the NMOS

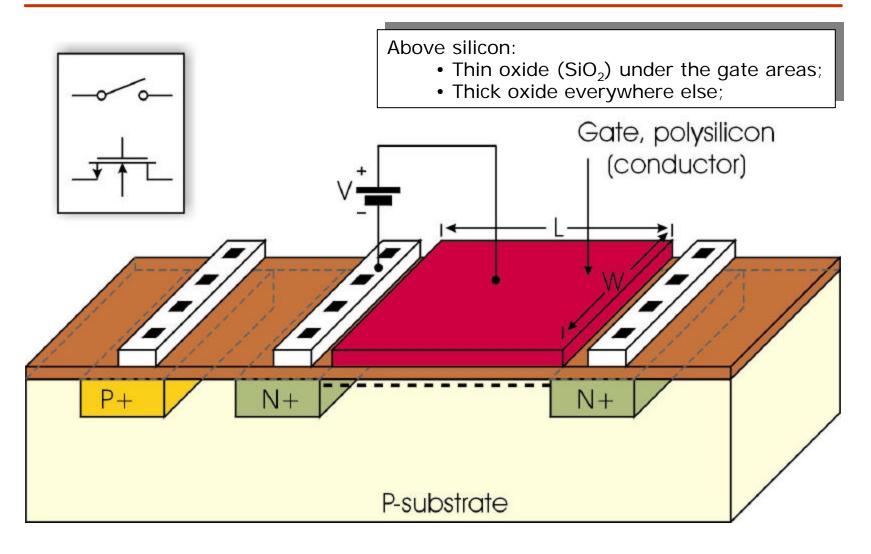

### Silicon switches: the PMOS

## **MOSFET** equations

Cut-off region

$$U_{ds} = 0 \quad \text{for} \quad V_{gs} - V_T < 0$$

Linear region

$$I_{ds} = \mathbf{m} \cdot C_{ox} \cdot \frac{W}{L} \cdot \left[ \left( V_{gs} - V_T \right) \cdot V_{ds} - \frac{V_{ds}^2}{2} \right] \cdot \left( 1 + \mathbf{I} \cdot V_{ds} \right) \text{ for } 0 < V_{ds} < V_{gs} - V_T$$

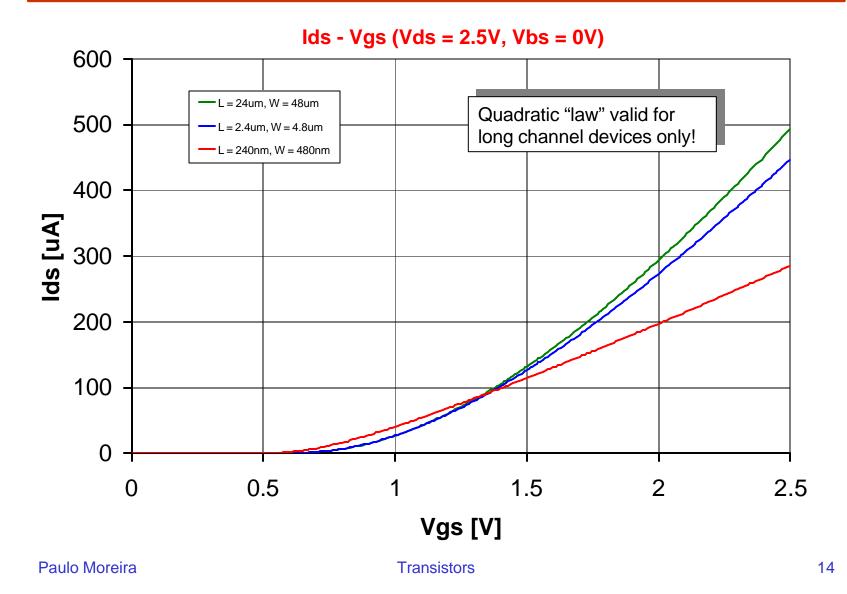

Saturation

$$I_{ds} = \frac{\mathbf{m} \cdot C_{ox}}{2} \cdot \frac{W}{L} \cdot \left( V_{gs} - V_T \right)^2 \cdot \left( 1 + \mathbf{I} \cdot V_{ds} \right) \text{ for } V_{ds} > V_{gs} - V_T$$

0.24µm process

$C_{ox} = 5.6 fF/\mu m^2$

t<sub>ox</sub> = 5nm (~10 atomic layers)

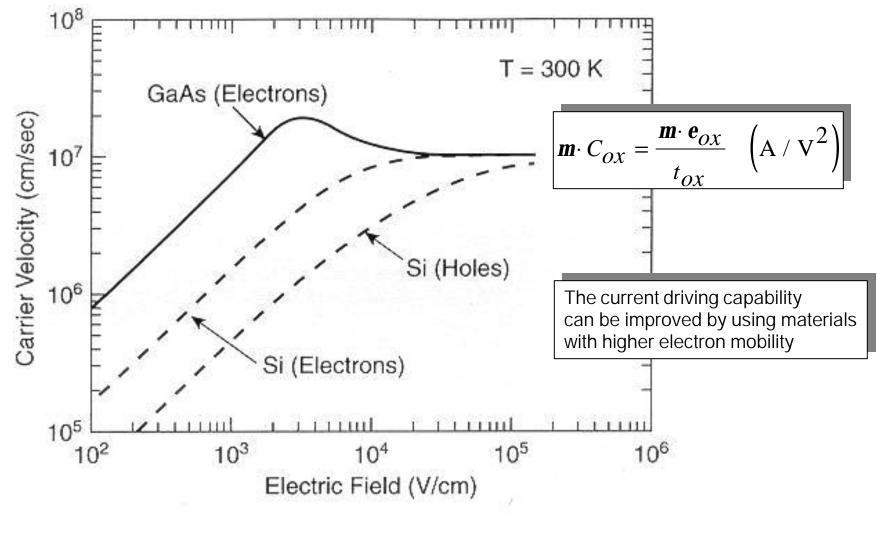

- Oxide capacitance  $C_{ox} = \frac{e_{ox}}{t_{ox}} \quad (F / m^2)$ • Process "transconductance"

$$\boldsymbol{m} \cdot \boldsymbol{C}_{OX} = \frac{\boldsymbol{m} \cdot \boldsymbol{e}_{OX}}{t_{OX}} \quad \left( \boldsymbol{A} / \boldsymbol{V}^2 \right)$$

Paulo Moreira

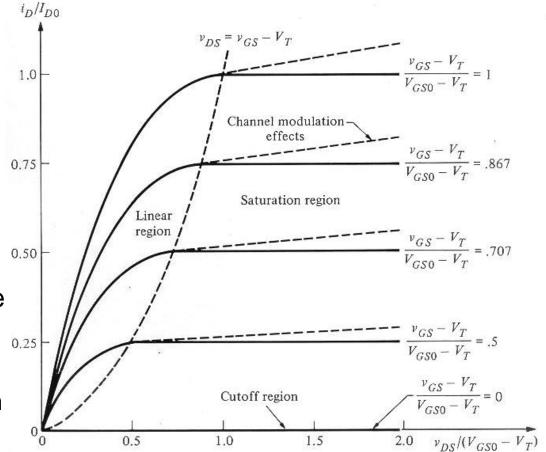

### MOS output characteristics

- Linear region: V<sub>ds</sub><V<sub>gs</sub>-V<sub>T</sub>

- Voltage controlled resistor

- Saturation region:

V<sub>ds</sub>>V<sub>gs</sub>-V<sub>T</sub>

- Voltage controlled current source

- Curves deviate from the ideal current source behavior due to:

- Channel modulation effects

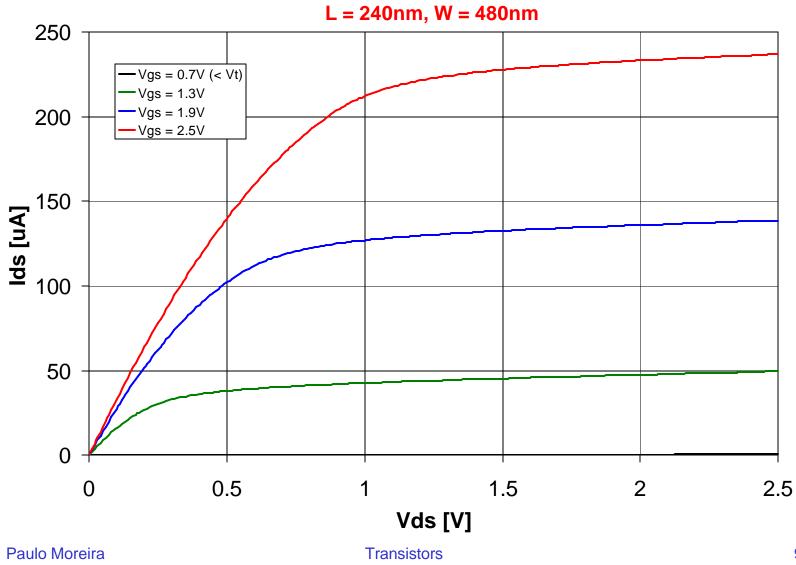

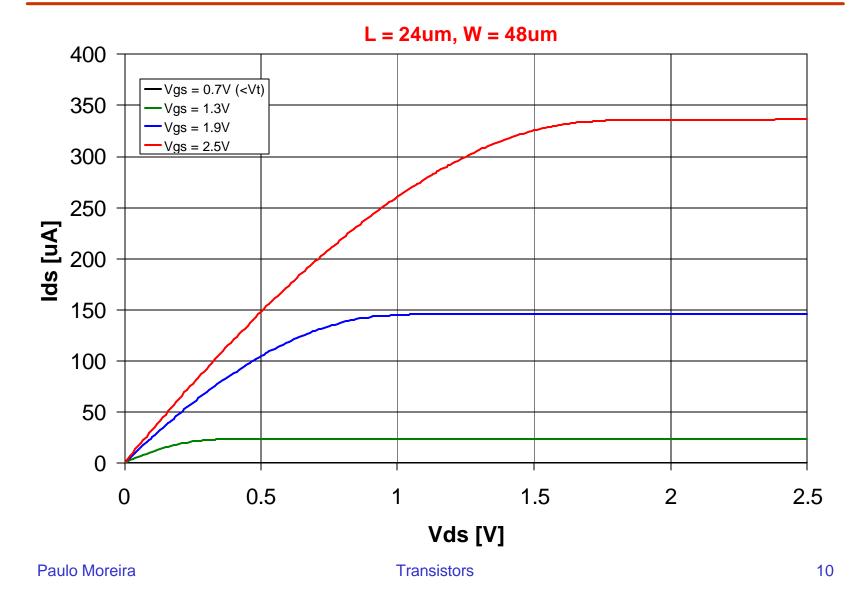

#### MOS output characteristics

9

#### MOS output characteristics

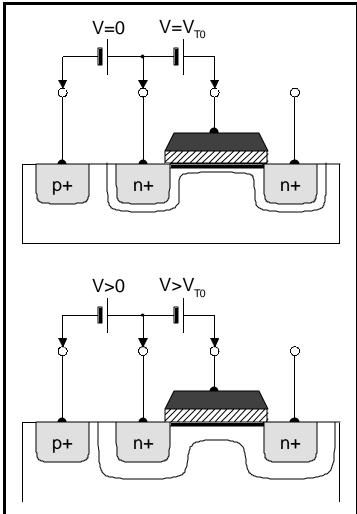

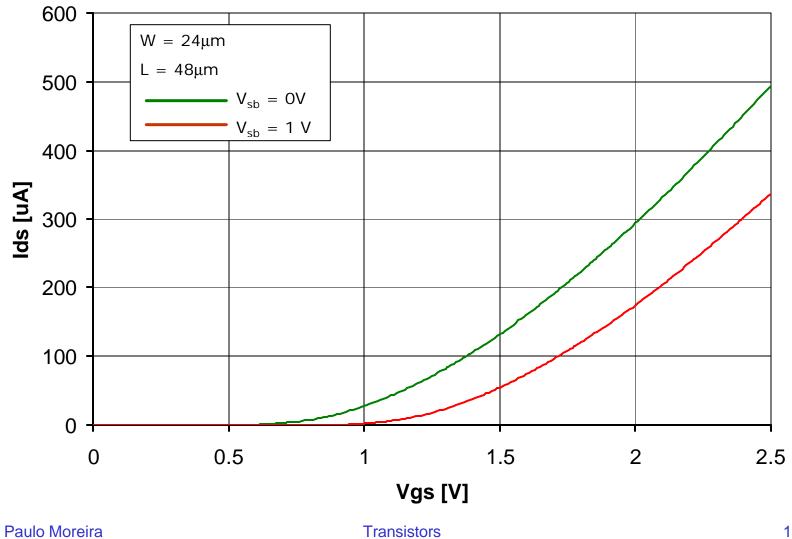

# Bulk effect

- The threshold depends on:

- Gate oxide thickness

- Doping levels

- Source-to-bulk voltage

- When the semiconductor surface inverts to n-type the channel is in "strong inversion"

- $V_{sb} = 0 \Rightarrow$  strong inversion for:

- surface potential >  $-2\phi_F$

- $V_{sb} > 0 \Rightarrow$  strong inversion for:

- surface potential >  $-2\phi_{F+}V_{sb}$

### Bulk effect

# Mobility

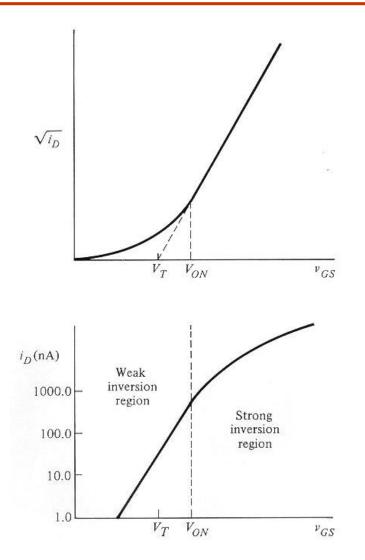

#### Is the quadratic law valid?

### Weak inversion

- Is  $I_d=0$  when  $V_{gs} < V_T$ ?

- For V<sub>gs</sub><V<sub>T</sub> the drain current depends exponentially on V<sub>gs</sub>

- In weak inversion and saturation (V<sub>ds</sub> > ~150mV):

$$I_d \cong \frac{W}{L} \cdot I_{do} \cdot e^{\frac{q \cdot V_{gs}}{n \cdot k \cdot T}}$$

where

$$I_{do} = e^{\frac{q \cdot v_T}{n \cdot k \cdot T}}$$

Used in very low power designs

a U

• Slow operation

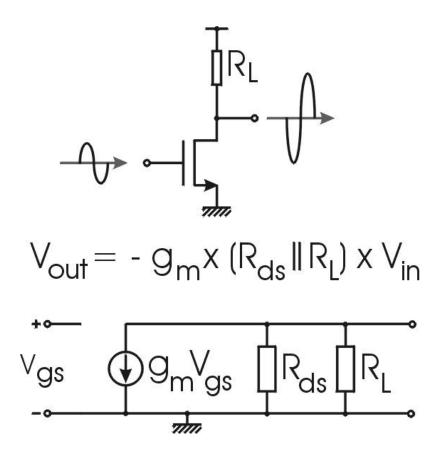

## Gain & Inversion

- Gain:

- Signal regeneration at every logic operation

- "Static" flip-flops

- "Static" RW memory cells

- Inversion:

- Intrinsic to the commonsource configuration

- The gain cell load can be:

- Resistor

- Current source

- Another gain device (PMOS)