2384-13

#### ICTP Latin-American Advanced Course on FPGADesign for Scientific Instrumentation

19 November - 7 December, 2012

Starting to make an FPGA project

KLUGE Alexander

PH ESE FE Division, CERN 385, rte Meyrin CH-1211 Geneva 23 SWITZERLAND

# Starting to make an FPGA project

# **FPGA** specifications

- How to make an FPGA?

- What should it do?

- How should it do it?

- Systems / Requirements define detailed implementation scheme/architecture

- Specification need to be worked out before even one thinks about the FPGA type or code.

- Specification: understand user needs

- define specification of system together with user/costumer

- re-discuss, re-negotiate

- understand

- task of designer to understand and translate specifications

# **FPGA** specifications

- Costumer/boss says: "I need a system which receives an input value each 25 ns and calculates a result."

- What you might understand is: "The calculation needs to be finished within 25 ns"

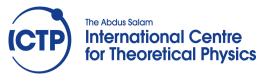

#### Adder

#### • Example:

#### - add 16 16-bit values in 25 ns

| <pre>library ieee;<br/>use ieee.std_logic_1164.all;<br/>use ieee.numeric_std.all;</pre> |                                        |                                                                                        |

|-----------------------------------------------------------------------------------------|----------------------------------------|----------------------------------------------------------------------------------------|

| entity ac<br>port                                                                       | dd16x28bit <b>i</b> s<br>(             | 3                                                                                      |

|                                                                                         | olk                                    | :in std_logic;                                                                         |

|                                                                                         | reset_i                                | :in std_logic;                                                                         |

|                                                                                         | data0                                  | :in integer range C to 2 ** 16 - 1;                                                    |

|                                                                                         | data1<br>data2                         | <pre>:in integer range C to 2 ** 16 - 1;<br/>:in integer range C to 2 ** 16 - 1;</pre> |

|                                                                                         | data3                                  | <pre>:in integer range C to 2 ** 16 - 1;<br/>:in integer range C to 2 ** 16 - 1;</pre> |

|                                                                                         | data4                                  | : in integer range $C$ to $2 \times 16 - 1;$                                           |

|                                                                                         | data5                                  | :in integer range C to 2 ** 16 - 1;                                                    |

|                                                                                         | data6                                  | :in integer range C to 2 ** 16 - 1;                                                    |

|                                                                                         | data?                                  | :in integer range C to 2 ** 16 - 1;                                                    |

|                                                                                         | data8                                  | :in integer range C to 2 ** 16 - 1;                                                    |

|                                                                                         | data9_                                 | :in integer range C to 2 ** 16 - 1;                                                    |

|                                                                                         | data10                                 | : in integer range $C$ to 2 $\uparrow\uparrow$ 16 - 1;                                 |

|                                                                                         | data11                                 | : in integer range $C$ to $2 \star 16 - 1;$                                            |

|                                                                                         | data12<br>data13                       | <pre>:in integer range C to 2 ** 16 - 1;<br/>:in integer range C to 2 ** 16 - 1;</pre> |

|                                                                                         | data14                                 | <pre>:in integer range C to 2 ** 16 - 1;<br/>:in integer range C to 2 ** 16 - 1;</pre> |

|                                                                                         | data15                                 | in integer range C to 2 ** 16 - 1;                                                     |

|                                                                                         |                                        | ···· ·································                                                 |

|                                                                                         | sum<br>);                              | :out integer range 0 to 2 ** 20 - 1                                                    |

| end add1                                                                                | 6x28bit;                               |                                                                                        |

| architect                                                                               | <b>ture</b> behavion                   | ral $\mathbf{of}$ add16x28bit $\mathbf{is}$                                            |

| signal                                                                                  | data0_int                              | <b>:integer range</b> C <b>to</b> 2 <b>**</b> 16 - 1;                                  |

| signal                                                                                  |                                        | : integer range $C$ to $2 \star 16 - 1$ ;                                              |

| signal                                                                                  | data2_int                              | : integer range $0$ to $2 ** 16 - 1;$                                                  |

| signal<br>signal                                                                        | data3_int<br>data4 int                 | <pre>:integer range 0 to 2 ** 16 - 1;<br/>:integer range 0 to 2 ** 16 - 1;</pre>       |

| signal                                                                                  | data5 int                              | : integer range $C$ to $2 ** 16 - 1;$                                                  |

| signal                                                                                  | data6 int                              | : integer range $C$ to $2 ** 16 - 1;$                                                  |

| signal                                                                                  | data6_int<br>data7_int<br>data8_int    | :integer range C to 2 ** 16 - 1;                                                       |

| signal                                                                                  | data8_int                              | <pre>:integer range C to 2 ** 16 - 1;</pre>                                            |

| signal                                                                                  | data9 int                              | <pre>:integer range C to 2 ** 16 - 1;</pre>                                            |

| signal                                                                                  | data10_int                             | : integer range $0$ to $2 \star 16 - 1$ ;                                              |

| signal                                                                                  | data10_int<br>data11_int<br>data12_int | : integer range $C$ to 2 ** 16 - 1;                                                    |

| signal                                                                                  | data_2_int                             | <pre>:integer range C to 2 ** 16 - 1;<br/>:integer range C to 2 ** 16 - 1;</pre>       |

| signal<br>signal                                                                        | data13_int<br>data14_int               | : integer range $C$ to $2 \times 10 - 1;$<br>: integer range $C$ to $2 \times 16 - 1;$ |

| signal                                                                                  | data15_int                             | integer range C to 2 ** 16 1;                                                          |

| signal                                                                                  | _                                      | :integer range 0 to 2 ** 20 - 1;                                                       |

```

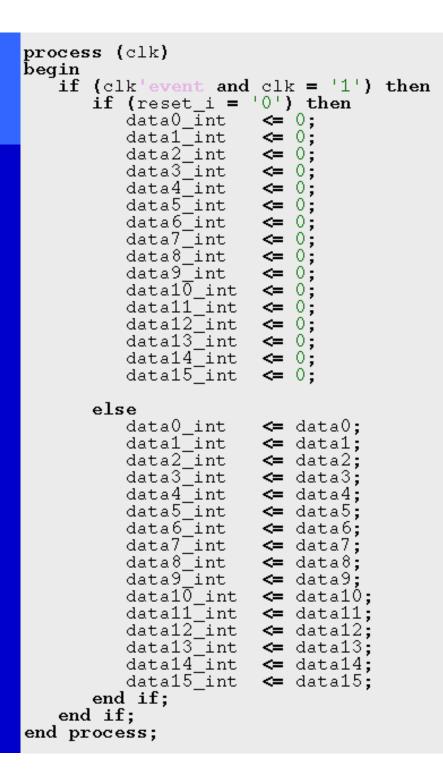

process (clk)

begin

if (ciklevent and clk = 111) then

if (reset : = C') then

dataC int

<= 0;

data1 int

<= 0;

data2_int

<= 0;

data3 int

<= 0;

data4 int

<= 0;

data5 int <= 0;

data6 int <= 0;

data7<sup>--</sup>int

<= 0;

data8<sup>-</sup>int

<= 0;

dataS_int

0;

<=

data10 int

<= 0;

data11 int

<= 0;

data12_int

<= 0;

data13 int

<= 0:

data14 int <= 0;

data15_int

<= 0;

else

dataC int

<= data0;

data1 int

- <≕ datai;

data2 int

<= data2;

data3 int

<= data3;

data4 int <= data4;

data5 int

<= data5;

data6 int <= data6;

data7 int <= dota7:

data8 int

<= data8;

data9 int

– <≕ data9;

data10 int <= data10;

data11_int

data11:

data12 int

data12:

data13_irt <= data13;

data14_int <= data14;

data15 int <= dota15;

end if;

end if;

end process;

```

```

ena process,

process (clk)

begin

if (clk'event and clk = '1') then

if (reset_i = '0') then

sum int <= 0;

else

sum int <= data0 int +

data1 int +

data2 int +

data3 int +

data4 int +

data5 int +

data6 int +

data7 int +

data8 int +

data9 int +

data10 int +

data11 int +

data12 int +

data13 int +

data14 int +

data15 int;

end if;

end if;

end process;

sum <= sum int;

end behavioral;

```

- 533 logic elements, 6%

- 278 pins, 74%

- 29.7 MHz => 33.6 ns

- 33.6 ns > 25 ns -> too slow

#### Adder

- 533 logic elements, 6%

- 278 pins, 74%

- 29.7 MHz => 33.6 ns

- 33.6 ns > 25 ns -> too slow

- Ask boss to buy faster, more expensive FPGA

- Work (manually) on FPGA placing&routing

- Help synthesizer to make faster adder

- Ask whether you have understood specification

# **FPGA** specifications

- Costumer/boss says: "I need a system which receives an input value each 25 ns and calculates a result."

- What you might understand is: "The calculation needs to be finished within 25 ns"

- What he means is:

"A new value needs to be processed every 25 ns. How long it takes to present the result does not matter"

• First case: might be impossible, maybe not. Second case: Processors in parallel or in pipeline

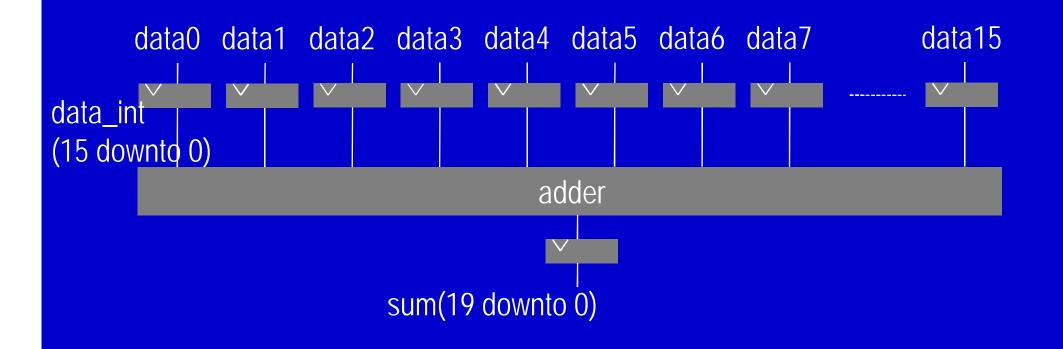

### **Pipeline architecture**

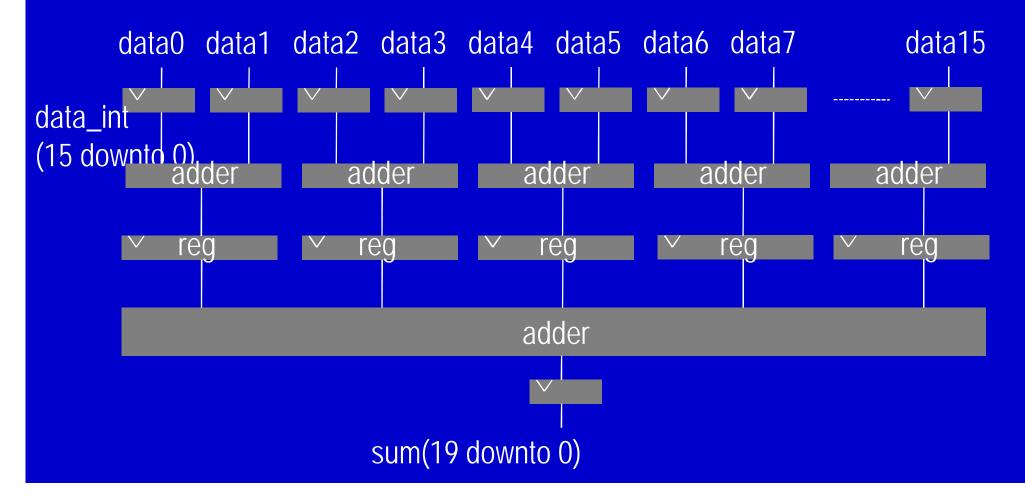

#### PIPELINE ARCHITECTURE

## **Adder with pipeline**

- Example:

- add 16 16-bit values every 25 ns

```

librarv ieee:

use ieee.std logic 1164.all:

use ieee.numeric std.all;

entity add16Pipeline is

port (

clk

:in std_logic;

:in std_logic;

reset i

data0

:in integer range 0 to 2 ** 16 - 1;

:in integer range 0 to 2 ** 16 - 1;

data1

:in integer range 0 to 2 ** 16 - 1;

data2

:in integer range 0 to 2 ** 16 - 1;

data3

:in integer range 0 to 2 ** 16 - 1:

data4

:in integer range 0 to 2 ** 16 - 1;

data5

:in integer range 0 to 2 ** 16 - 1;

data6

:in integer range 0 to 2 ** 16 - 1;

data7

:in integer range 0 to 2 ** 16 - 1;

data8

:in integer range 0 to 2 ** 16 - 1;

data9

:in integer range 0 to 2 ** 16 - 1;

data10

:in integer range 0 to 2 ** 16 - 1:

data11

:in integer range 0 to 2 ** 16 - 1;

data12

:in integer range 0 to 2 ** 16 - 1;

data13

data14

:in integer range 0 to 2 ** 16 - 1:

:in integer range 0 to 2 ** 16 - 1;

data15

:out integer range 0 to 2 ** 20 - 1

sum

);

end add16Pipeline;

architecture behavioral of add16Pipeline is

data0 int

:integer range 0 to 2 ** 16 - 1;

siqnal

:integer range 0 to 2 ** 16 - 1;

data1_int

signal

:integer range 0 to 2 ** 16 - 1;

siqnal

data2_int

:integer range 0 to 2 ** 16 - 1;

siqnal

data3 int

data4_int

:integer range 0 to 2 ** 16 - 1;

signal

data5_int

:integer range 0 to 2 ** 16 - 1;

signal

:integer range 0 to 2 ** 16 - 1;

signal

data6 int

:integer range 0 to 2 ** 16 - 1;

data7 int

signal

:integer range 0 to 2 ** 16 - 1;

data8 int

signal

data9_int

:integer range 0 to 2 ** 16 - 1;

signal

:integer range 0 to 2 ** 16 - 1;

data10 int

signal

:integer range 0 to 2 ** 16 - 1;

data11 int

signal

:integer range 0 to 2 ** 16 - 1;

data12 int

signal

:integer range 0 to 2 ** 16 - 1;

data13 int

signal

:integer range 0 to 2 ** 16 - 1;

data14_int

signal

data15 int

:integer range 0 to 2 ** 16 - 1:

signal

:integer range 0 to 2 ** 20 - 1;

signal

sum int

:integer range 0 to 2 ** 17 - 1;

signal

sum int0

:integer range 0 to 2 ** 17 - 1;

sum int1

signal

:integer range 0 to 2 ** 17 - 1:

signal

sum int2

:integer range 0 to 2 ** 17 - 1:

signal

sum int3

:integer range 0 to 2 ** 17 - 1:

signal

sum int4

:integer range 0 to 2 ** 17 - 1;

signal

sum int5

:integer range 0 to 2 ** 17 - 1;

signal

sum int6

:integer range 0 to 2 ** 17 - 1;

signal

sum_int7

begin

```

```

process (clk)

begin

if (clk'event and clk = '1') then

if (reset 1 = 10^{\circ}) then

sum into \leftarrow C;

else

sum int0 <= data0 int +

detal int;

end if:

end if;

end process;

process (clk)

begin

if \{clk'event and clk = '1'\} then

if (reset z = -0^{\circ}) then

sum int1 <= C;

alse

sum int1 <= dota2 int +

deta3<u>_</u>int;

end if;

end if;

end process;

process (clk)

begin

if \{clk | event and clk = '1'\} then

if (reset_1 = '0') then

sum int \leq 0;

else

sum int2 🦛 data4 int |

dota5_int;

end if;

and if;

```

```

process (clk)

heqin

if (clk'event and clk = '1') then

if {reset__ = '0'} then

sum_int3

<= 0;

else

sum int3 <= data6 int +

deta7_int;

end if;

end if;

end process;

process (cik)

beqin

if (clk'event and clk = '1') then

if (reset_: = (0)) then

sum int4 \ll 0;

else

sum int4 🛛 <= data8 int +

data9 int;

end if;

end if;

end process;

```

```

process (clk)

beqin

if (clk'event and clk = '1') then

if (reset i = 10 ) then

\operatorname{Rum} in \overline{L}5 \ll 0;

else

sum int5 🛛 <= data10 int +

data11 int;

end if;

end if;

end process;

process (cik)

beqin

if (clk'event and clk = '1') then

if (reset_i = 10 ) then

oum int6 <= 0;

else

sum int6 🛛 🗢 data12 int |

data13 int;

end if:

end if;

end process;

process (elk)

beqin

if (clk'event and clk = '1') then

if (reset i = '0 ) then

\operatorname{sum} in \overline{L}7 \ll 0;

else.

sum int7 🛛 <= data14 int +

data15 int;

end if:

end if;

end process;

```

```

process (clk)

begin

if (clk'event and clk = '1') then

if (reset_i = '0') then

sum int <= 0;

else

sum_int <= sum_int0 +</pre>

sum int1 +

sum int2 +

sum int3 +

sum int4 +

sum_int5 +

sum int6 +

sum int7

ş

end if;

end if;

end process;

sum <= sum_int;</pre>

end behavioral;

```

## Adder with pipeline

- Adder without pipeline

- 533 logic elements, 6%

- 278 pins, 74%

- 29.7 MHz => 33.6 ns

- Adder with pipeline

- 526 logic elements, 6%

- 278 pins, 74%

- 45.4 MHz => 22 ns

- 22ns < 25 ns, fast enough and less logic

# **FPGA** specifications

#### re-discuss, re-negotiate

- understand

- task of designer to understand and translate specifications

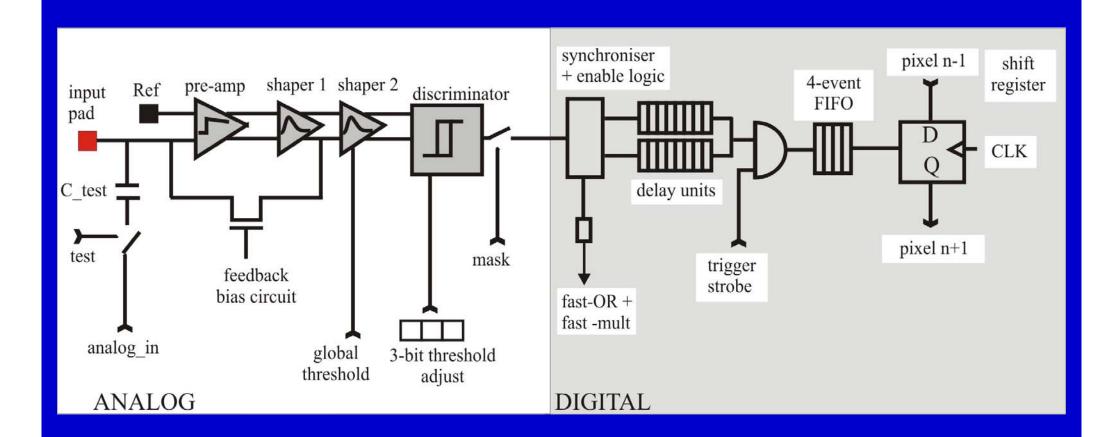

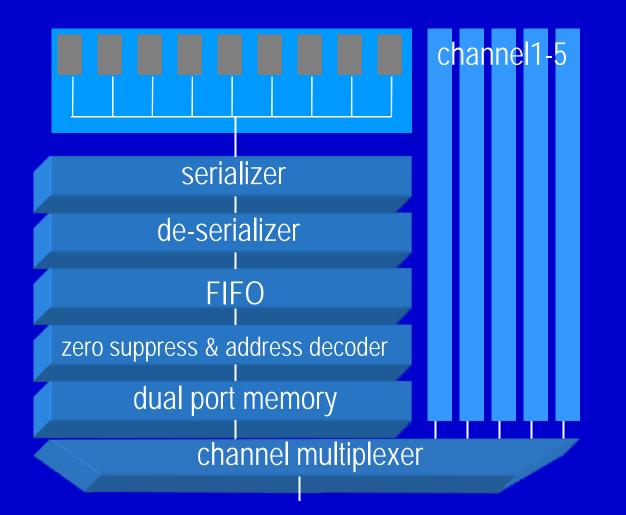

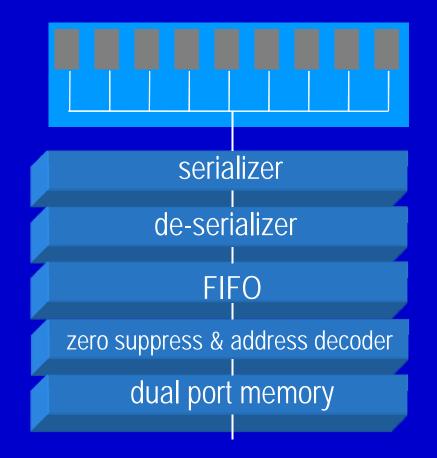

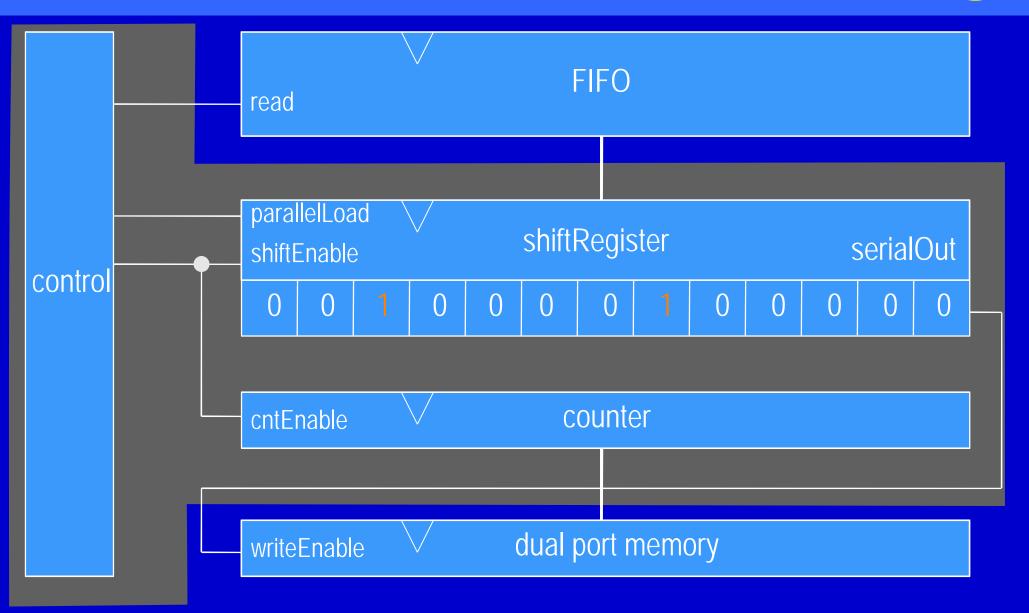

## **Readout Processors**

#### **Read-out processors**

#### Specification

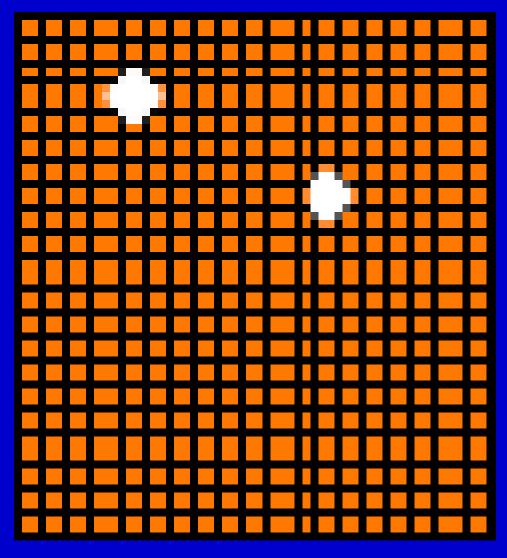

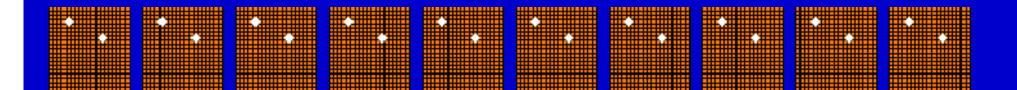

Challenge - many parallel inputs –

25 ns intervall - short processing time

- Storage during trigger decision time

- Data reduction/encoding (zero suppression)

- pipelining, buffering (FIFO, dual port RAM)

## What do we need to know?

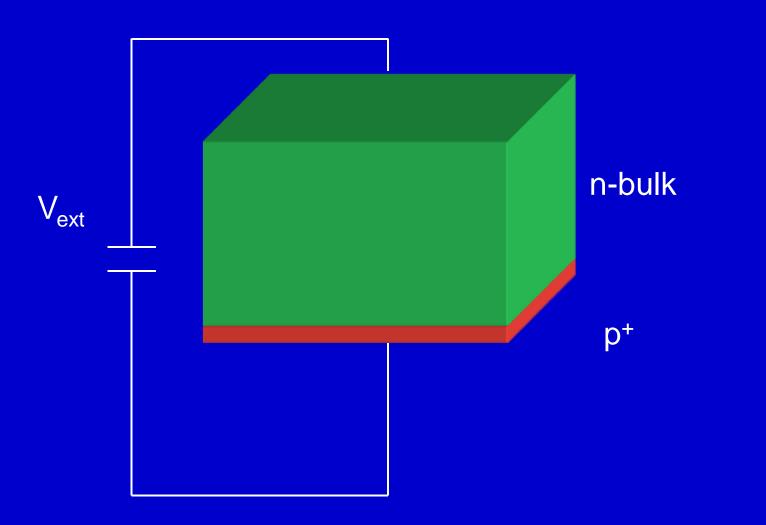

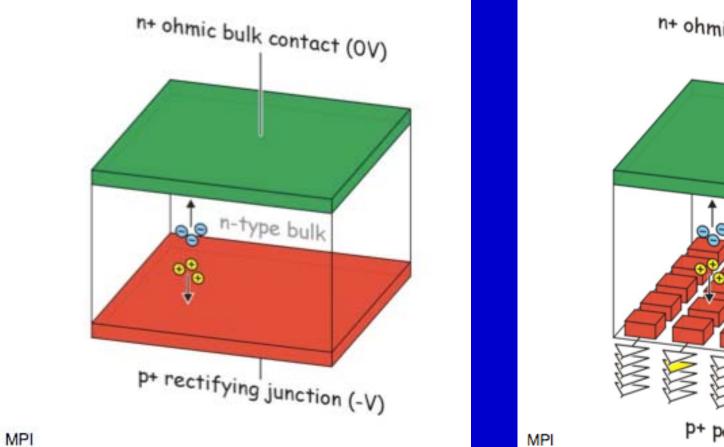

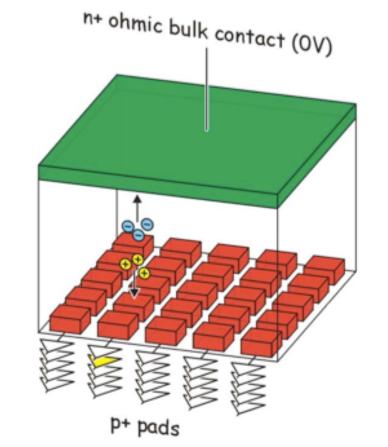

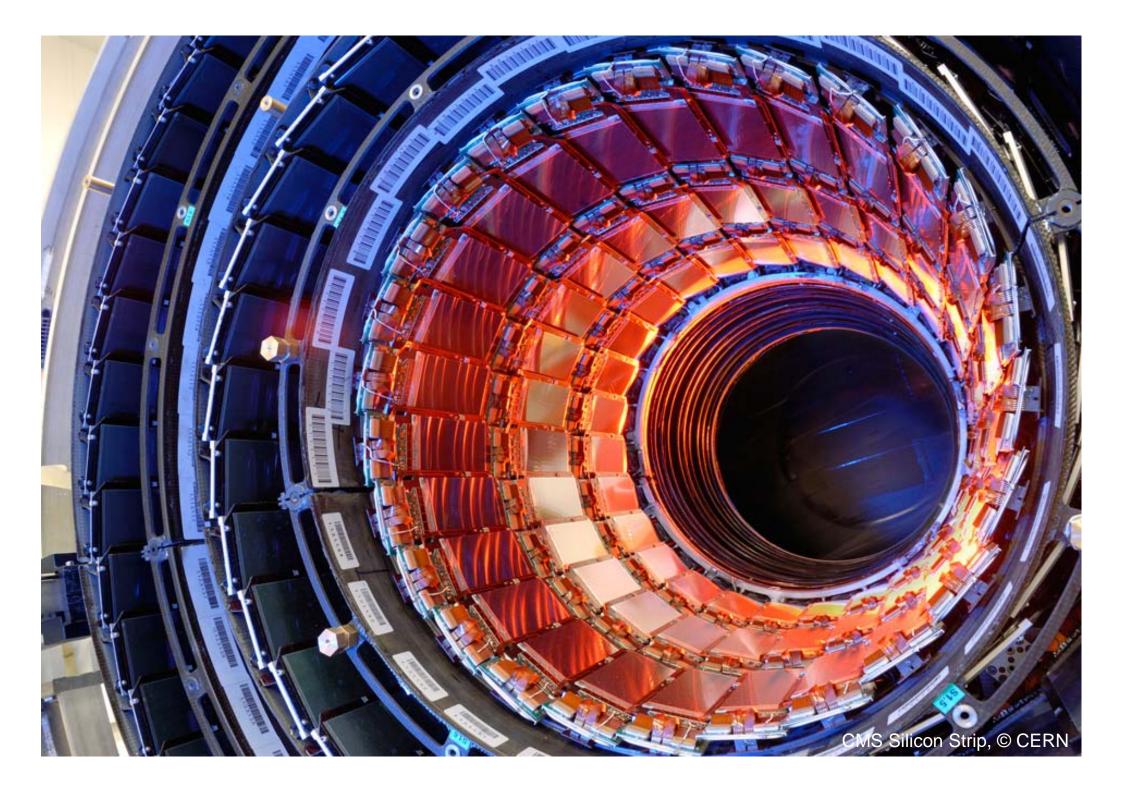

## **Silicon Sensor**

Position resolution: 10 μm light material: 1 % X<sub>0</sub> oder 2 mm

#### **Silicon Sensors**

Dez. 11, 2007

## Silicon Pixel sensors

### **Silicon Pixel Wafers**

P. Riedler

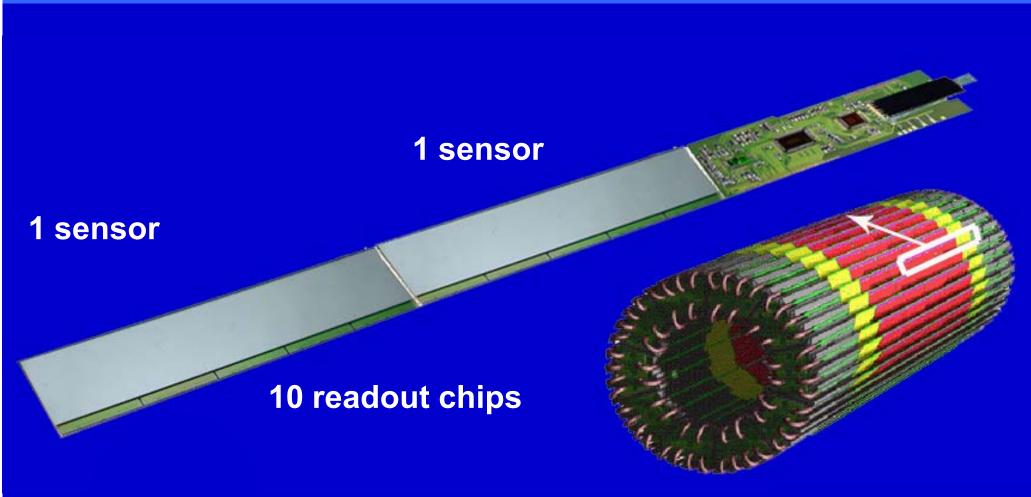

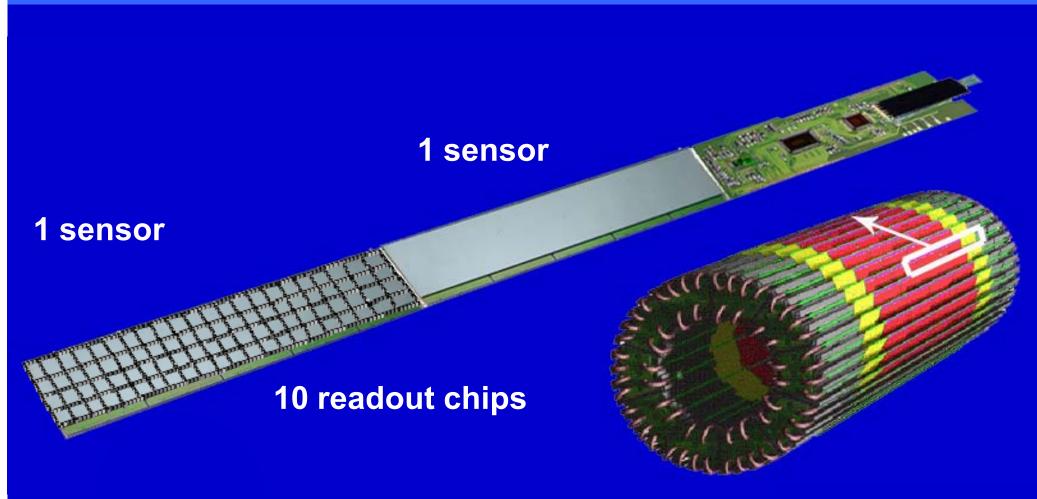

<u>silicon sensor</u> 72.72 mm x 13.92 mm 200 μm thin 160 x 256 pixel 425 μm x 50 μm

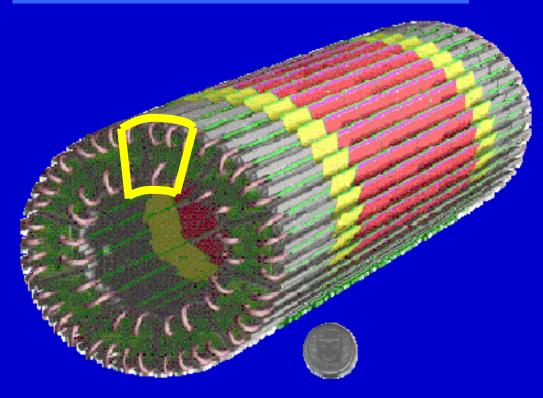

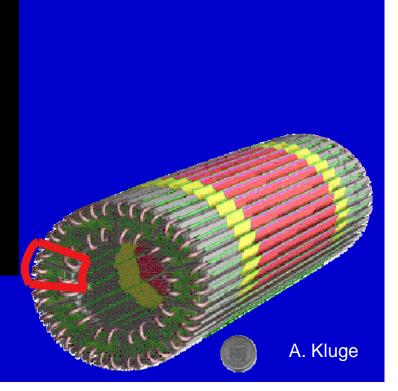

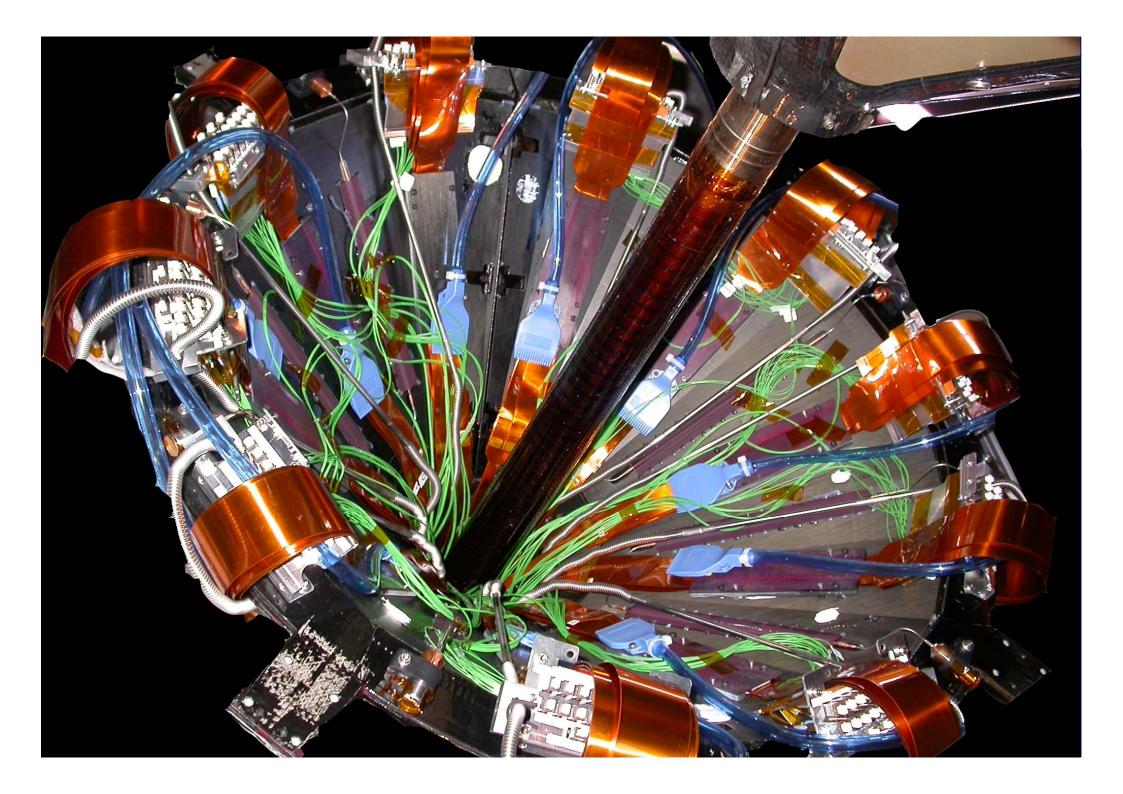

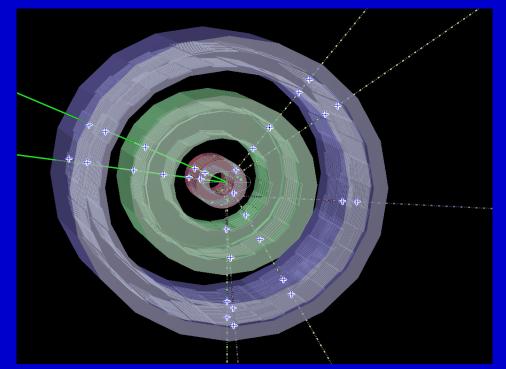

# **Detector configuration**

### Silicon pixel detector

#### ∆ z= 28.3 cm r= 3.9 cm & 7.6 cm

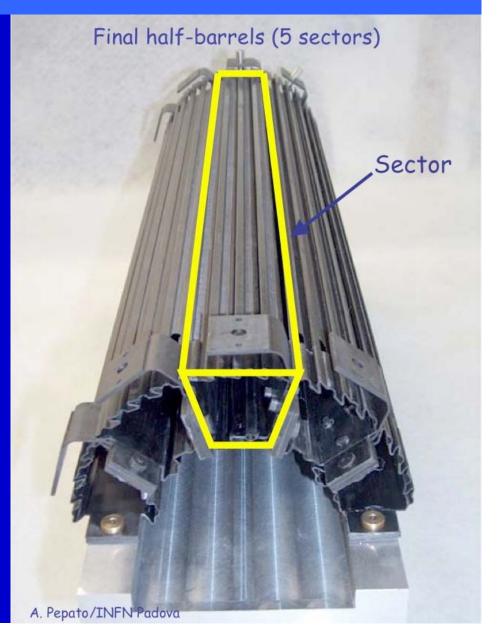

## SPD carbon fiber support

200 µm carbon fiber support

# 40 µm PHYNOX cooling tubes integrated

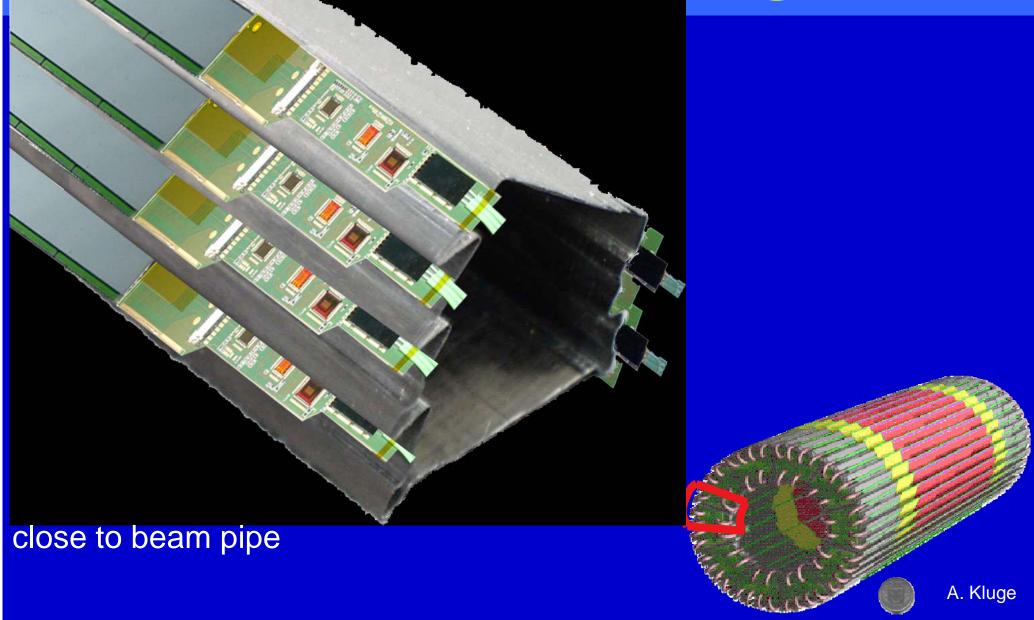

#### **Detector module**

#### dimensions = 200 mm x 15 mm x 2 mm

light materials =  $1\% X_0$ , no copper

1.3 kW power dissipation

distance to beam pipe 4 mm

120 modules

#### Image:INFN(Padova)

A. Kluge

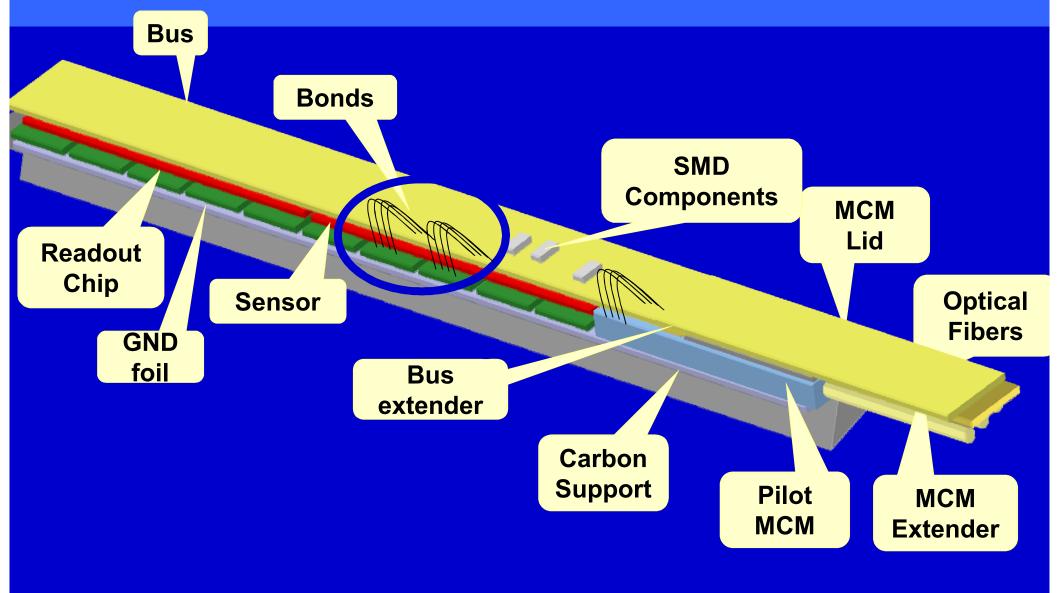

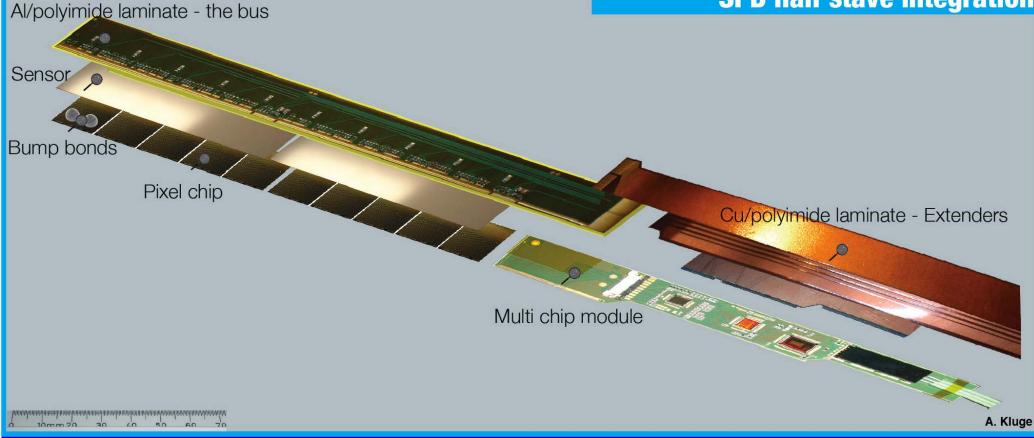

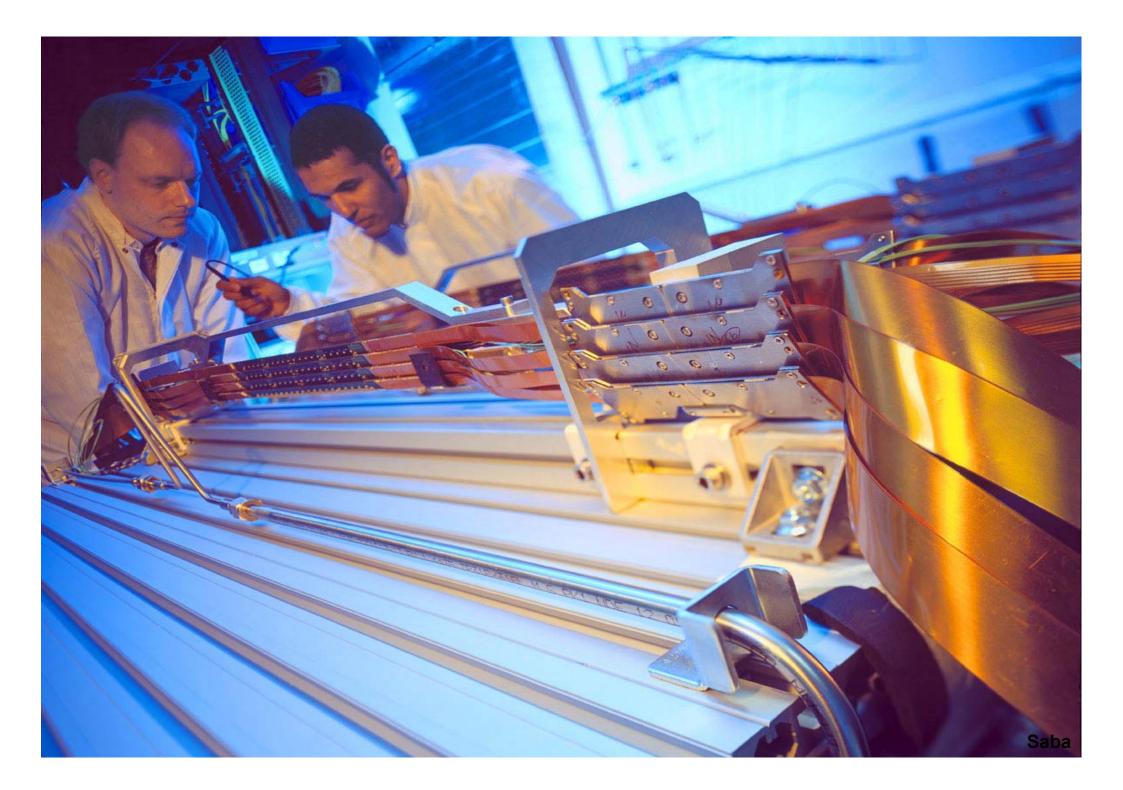

# Electro-mechanical integration

# Integration

#### Light carbon fiber support

## Integration

#### **Electronics integration**

A. Kluge

# **Electronics integration**

#### SPD half stave integration

# **Pixel read out chip**

Time resolution: 25 ns Repetition frequency: 40 MHz Storage time: > 3.2 µs

# **Pixel chip**

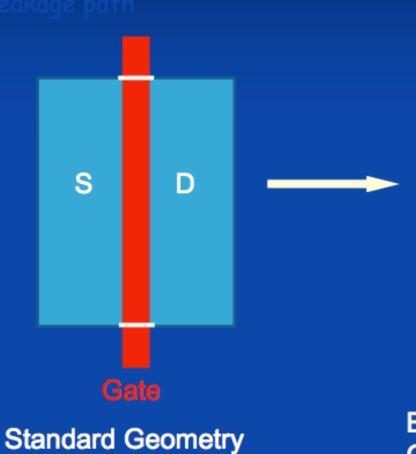

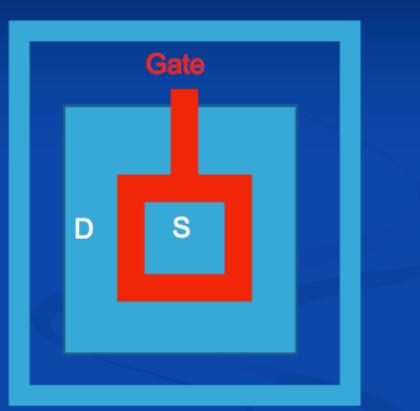

# Radiation tolerant electronics

# **Radiation tolerance**

#### Enclosed geometrie to avoid leakage

Enclosed gate (S-D leakage) Guard ring (leakage between devices)

A. Kluge

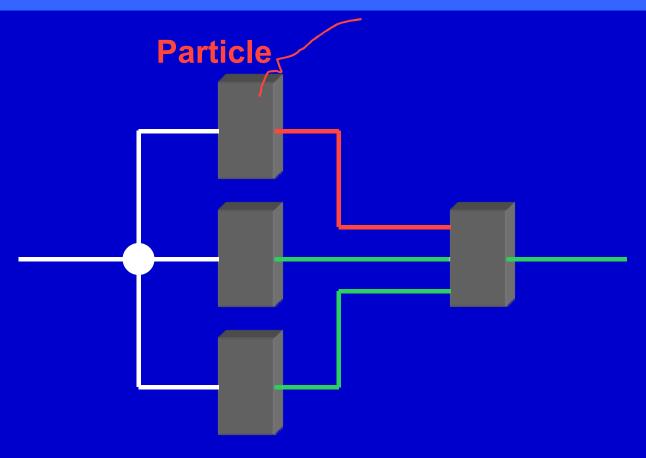

# **Triple voting**

3 Registers Voting unit

#### Image:INFN(Padova)

Sept 3-7, 2007

A. Kluge

#### Image:INFN(Padova)

Sept 3-7, 2007

A. Kluge

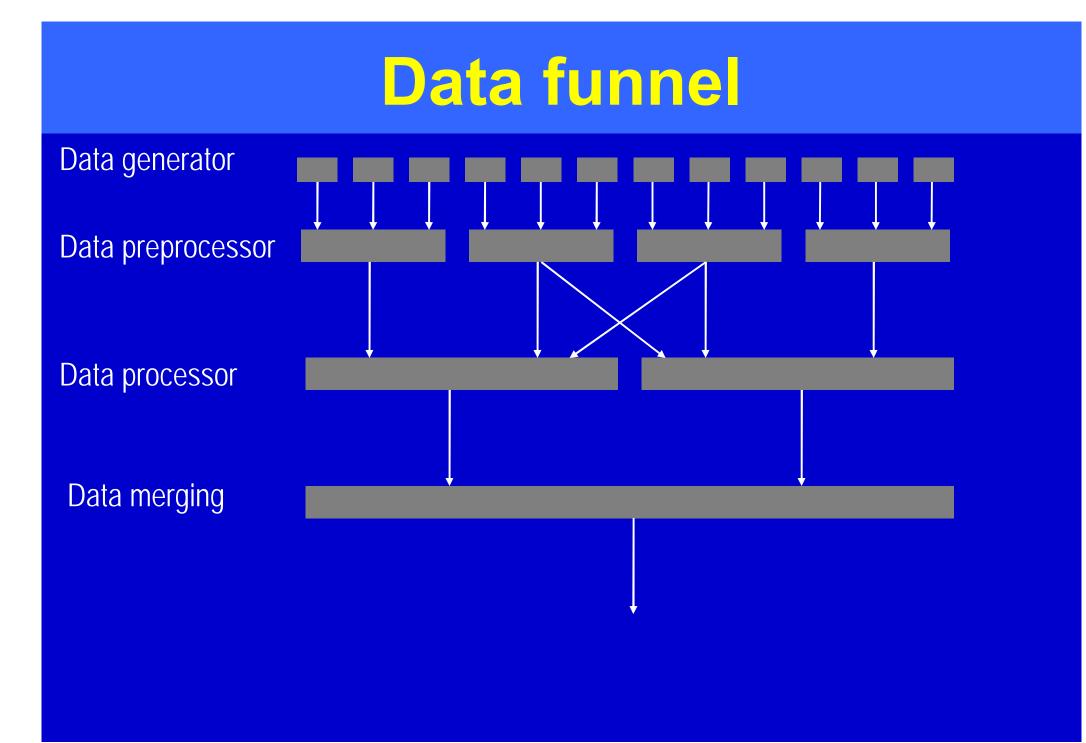

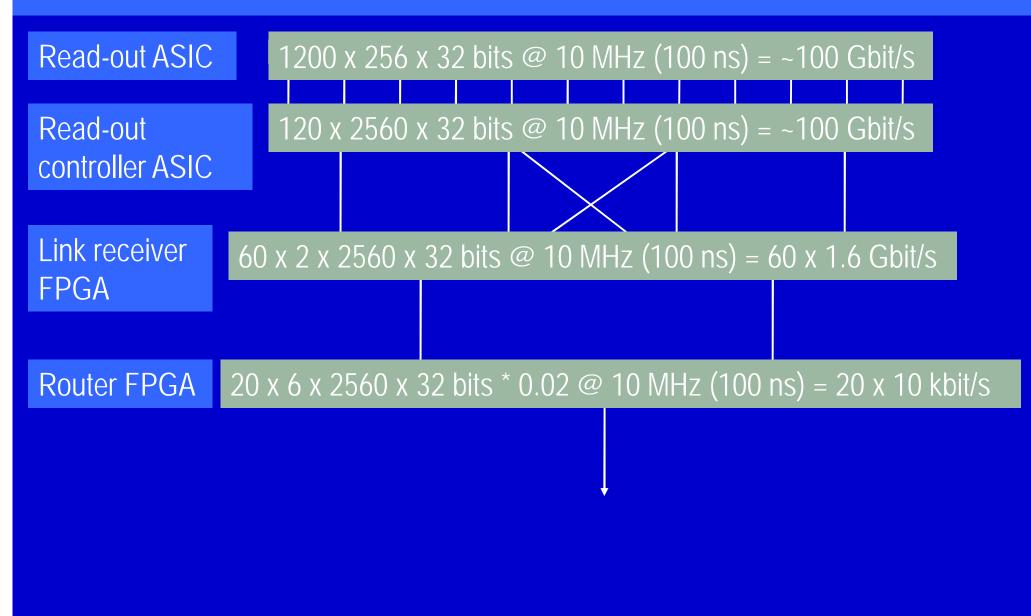

Full detector 120 x 2560 x 32 bits @ 10 MHz (100ns) = ~ 100 Gbits/s

Separate read-out for each detector module

# **Data funnel**

Data generator 2560 x 32 bits

#### What is the strategy?

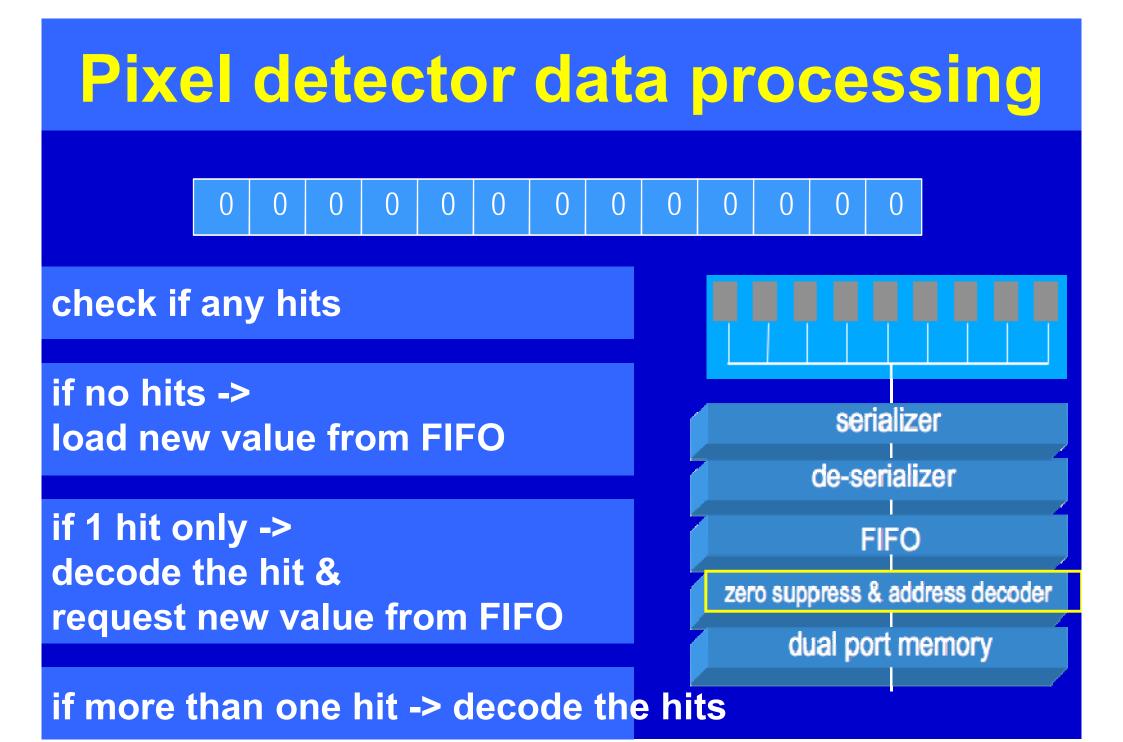

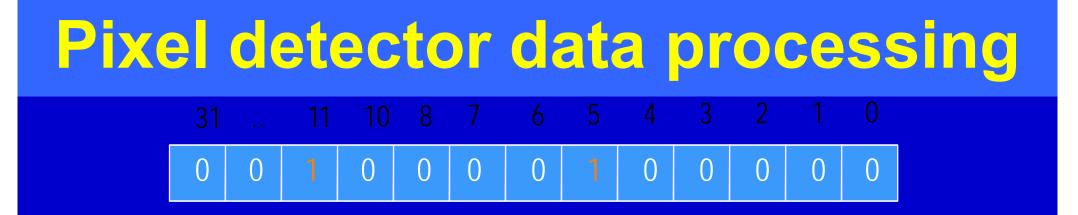

Pixel detector data processing

31

..

11

10

8

7

6

5

4

3

2

1

0

0

0

1

0

0

0

1

0

0

0

0

0

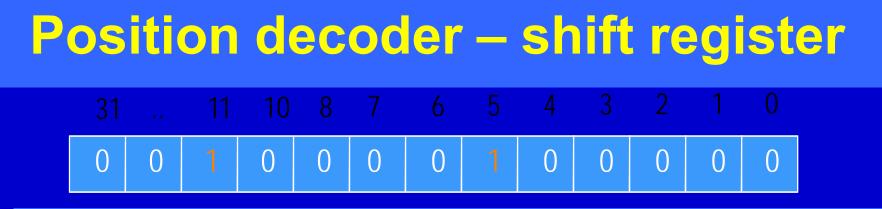

How to decode the address? this line has two hits the state machine must send two hits into the dual port memory

| row address | hit position = 5  |

|-------------|-------------------|

| row address | hit position = 11 |

Do we know enough to start the project? How do we encode the address?

| row address | hit position = 5  |

|-------------|-------------------|

| row address | hit position = 11 |

# **Pixel detector data processing**

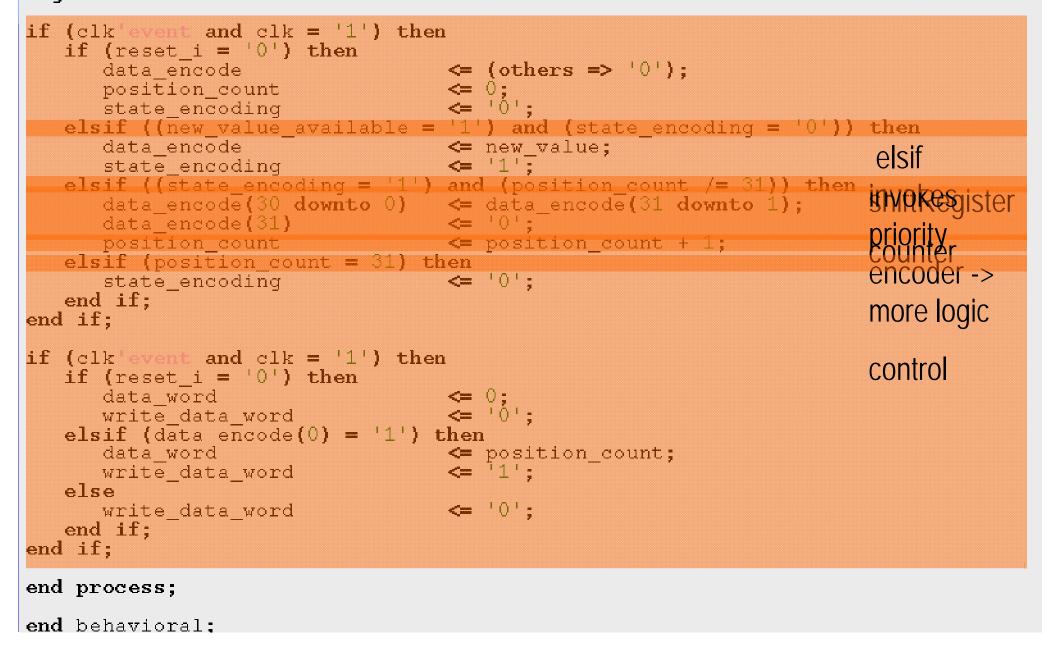

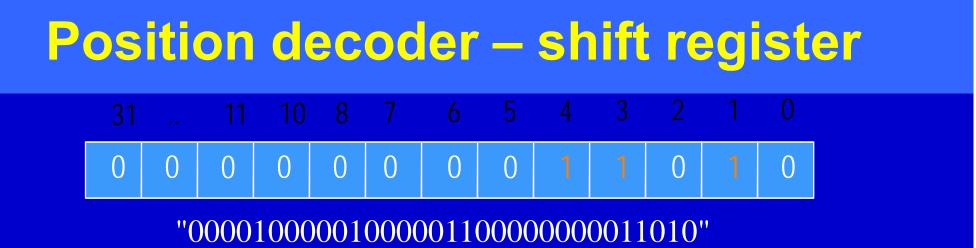

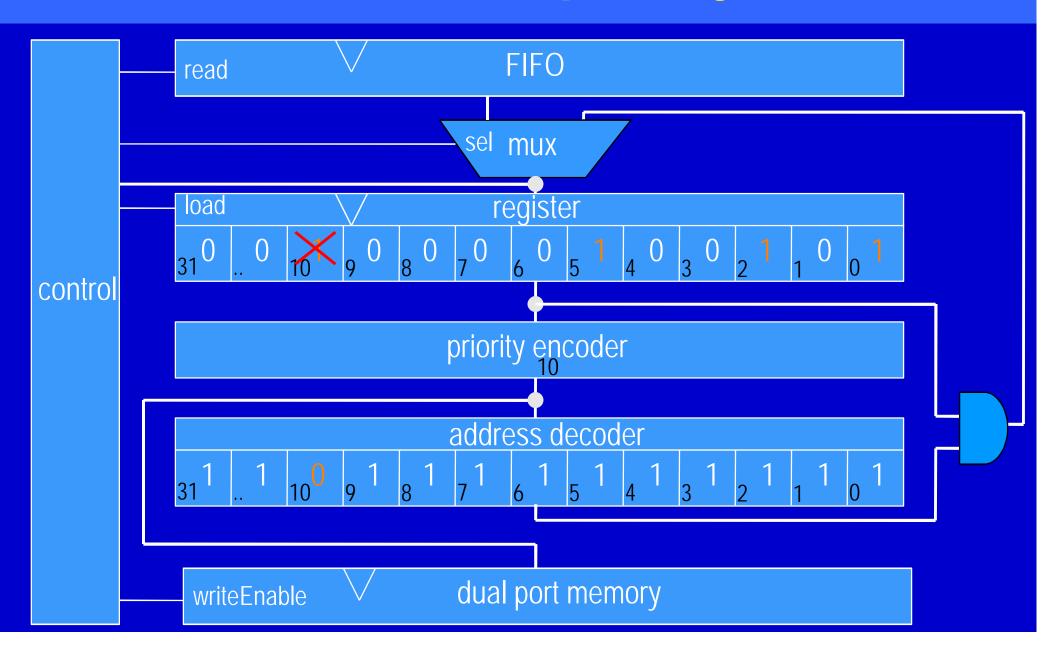

### Position decoder – shift register

```

000

X positionDecoderSR.vhd - /Volumes/akluge/cadence/div/test_vhdl/

File Edit Search Preferences Shell Macro Windows

Help

L:4 C:16

/Volumes/akluge/cadence/div/test_vhdl/positionDecoderSR.vhd_1418 bytes

library icee;

use ieee.std_logic_1164.all;

entity positionDecoderSR is

port ( clk

:in

std_logic;

std_logic;

reset i

:in

rew_value_available :in

std_logic;

rew_value

:in std_logic_vector (31 downto 0);

data word

:out

integer range 0 to 31;

write_data_word

:out std_logic);

end positionDecoderSR;

architecture behavioral of positionDecoderSR is

signal data encode

:std_logic_vector (31 downto 0);

signal position count

:integer range 0 to 31;

signal state_encoding :std_logic;

begin

process (clk, reset i)

begin

if (clk'event and clk = 11) then

if (reset_i = '0') then

data encode

\Leftarrow (others \Rightarrow '0');

<= 0;

<= '5';

pesition_count

state_encoding

elsif ((new_value_available = '1') and (state_encoding = '0')) then

data_encode

state_encoding

elsif ((state encoding = '1') and (position count /= 31)) then

data encode (30 downto 0)

<= data_encode(31 downto 1);

data_encode(31)

<= '0';

pcsition_count

> position_count + 1;

elsif (position_count = 31) then

<= '0';

state_encoding

end if;

end if;

if (clk'event and clk = '1') then

if (reset_i = '0') then

data_word

write_data_word

elsif (data_encode(0) = '1') then

data word

write_data_word

else

write data word

<= '0';

end if:

end 1f;

end process;

end behavioral;

```

### **Position decoder – shift register**

```

X positionDecoderSR.vhd - /Volumes/akluge/cadence/div/test vhdl/

File Edit Search Preferences Shell Macro Windows

/Volumes/akluge/cadence/div/test_vhdl/positionDecoderSR.vhd_1418_bytes

library ieee;

use ieee.std logic 1164.all;

entity positionDecoderSR is

port (

clk

std_logic;

:in

std_loqic;

:in

reset i

std logic

new value available :in

std_logic_vector (31 downto 0);

new value

:in

data word

:out

integer range 0 to 31;

write data word

:out

std logic):

end positionDecoderSR;

architecture behavioral of positionDecoderSR is

:std logic vector (31 downto 0);

signal data encode

signal position_count

:integer range 0 to 31:

signal state encoding

std logic:

begin

process (clk, reset i)

begin

if (clk'event and clk = '1') then

if (reset i = '0') then

```

begin

```

process (clk, reset_i)

begin

```

```

Process (CIK, reset I)

begin

state machine

if (clk'event and clk = '1') then

if (reset i = '0') then

<= (others => '0');

data encode

<= 0;

position count

<= 'Ò':

state encoding

else

case (state encoding) is

when '0' =>

if (new_value_available = '1') then

data encode

<- '1':

state encoding

end if;

when 1^{+} =>

if (position_count /= 31) then

data encode(30 downto 0) <= data encode(31 downto 1);</pre>

<= '0':

data encode(31)

position count

c= position count + 1;

elsif (position count = 31) then

<= '0':

state encoding

end if;

when others =>

data encode

<= (others => '0');

<= 0:

position count

⇐ '0';

state encoding

end case;

end if:

end if:

if (clk'event and clk = '1') then

if (reset i = '0') then

```

### • Shift register is a parallel load register

| x <sub>2</sub> TimeA = 937.5 |             |                | 07   🔴   🐼 | 7,012,437.5ns        | :+0     |                                            |            |                                 |           |                             |                     |          |         |                           |                   |      | ] Tim | e: 37 🛛   | 937.5ns : 184 | ¥7.79C 🛨 🔍 🕇 🔲       |

|------------------------------|-------------|----------------|------------|----------------------|---------|--------------------------------------------|------------|---------------------------------|-----------|-----------------------------|---------------------|----------|---------|---------------------------|-------------------|------|-------|-----------|---------------|----------------------|

| ×  Baseline = 1847           |             |                |            |                      |         |                                            |            |                                 |           |                             |                     |          |         |                           |                   |      |       |           | Page          | line = 1847.790948ns |

| Cursor-Baseline = -910       |             | TimeA = 937.5r |            |                      |         |                                            |            |                                 |           |                             |                     |          |         |                           |                   |      |       |           | Dase          |                      |

| Name ▼                       | Cursor 🔻    |                | 1000ns     |                      | 00ns    | 1200ns                                     |            | 1300ns                          |           | 1400                        | ns                  | 15       | 00ns    |                           | 1600ns            |      | 1     | 700ns     |               | 1800ns               |

| 🐣 🚽 🚽                        | 1           |                |            |                      |         |                                            |            |                                 |           |                             |                     |          |         |                           |                   |      |       |           |               |                      |

| 🔊 🦳 🦡 reset_i                | 1           |                |            |                      |         |                                            |            |                                 |           |                             |                     |          |         |                           |                   |      |       |           |               |                      |

|                              | vailable 0  |                |            |                      |         |                                            |            |                                 |           |                             |                     |          |         |                           |                   |      |       |           |               |                      |

| ⊞ <b>⊊</b> new_value         | 'h 00000000 | 00000000       | 082 000000 | 100                  |         |                                            |            |                                 |           |                             |                     |          |         |                           |                   |      |       |           |               |                      |

| 🕀 🌆 data_encode              | 'h 0000000  | 00000000       | 082 041    | ▶ 020 <b>▶ 0</b> 10▶ | 008 004 | • <b>(</b> 002 <b>• (</b> 001• <b>)</b> 00 | o▶ 000► 00 | 10 <b>•  </b> 000• <b> </b> 000 | P 000 00  | o▶ <b>(</b> 000► <b>)</b> ( | 000 <b>►  </b> 000► | 000 000  | 000 000 | ▶ <mark> 000▶  </mark> 00 | 10 <b>0  </b> 000 | 000  | 000   | 000000    | 000           |                      |

|                              | 'd 0        | 0              |            | 1                    | 3 4     |                                            |            |                                 |           | 14                          | 15                  |          |         | 21                        |                   |      |       | 27        |               |                      |

| 🗄 📲 position_count           | t 'd 0      | 0              | <u>)</u> 1 | 2 3                  | 4 5     | (6) (7) (8                                 | 9 /10      | 11 12                           | 13 14     | 15                          | 16 (17 )            | 18 19    | 20 21   | 22 23                     | 3 24              | 25 2 | 26 27 | (28       | 29 30         | 31                   |

| write_data_wo                | ord 0       |                |            |                      |         |                                            |            |                                 |           |                             |                     |          |         |                           |                   |      |       |           |               |                      |

|                              | g 0         |                |            |                      |         |                                            |            |                                 |           |                             |                     |          |         |                           |                   |      |       |           |               |                      |

|                              |             |                |            |                      |         |                                            |            |                                 |           |                             |                     |          |         |                           |                   |      |       |           |               |                      |

|                              |             | • 💭 👘          | · · · · ·  | 1,000,000            | )       | 2,000,                                     | 000        |                                 | 3,000,000 |                             | 4,0                 | . 00,000 |         | 5,000                     | 0,000             |      |       | 6,000,000 |               | 7,012,437.5ns 🕨      |

| ୭                            |             |                |            |                      |         |                                            |            |                                 |           |                             |                     |          |         |                           |                   |      |       |           |               | 1 object select      |

### **Position decoder – shift register**

### **Position decoder – shift register**

|     |      |     |          |     |      |     |     |          |      |     |     | ] Time: | 0<br>1<br>1<br>1<br>1 | 937.5n | ıs : 1847 | .790 💌 🦕   | 2 + -      | - k><br>9 Fr |

|-----|------|-----|----------|-----|------|-----|-----|----------|------|-----|-----|---------|-----------------------|--------|-----------|------------|------------|--------------|

|     |      |     |          |     |      |     |     |          |      |     |     |         |                       |        | Baselin   | ne = 1847. | 790948r    | 1S           |

| 14( | )Ons |     |          | 150 | )Ons |     |     | 160      | )Ons |     |     | 170     | )Ons                  |        |           | 1800       | Ons        |              |

|     |      |     |          |     |      |     |     |          |      |     |     |         |                       |        |           |            |            |              |

|     |      |     |          |     |      |     |     |          |      |     |     |         |                       |        |           |            |            |              |

|     |      |     |          |     |      |     |     |          |      |     |     |         |                       |        |           |            |            |              |

|     |      |     |          |     |      |     |     |          |      |     |     |         |                       |        |           |            |            |              |

| )•  | 000  | 000 | 000      | 000 | 000  | 000 | 000 | 000      | 000  | 000 | 000 | 000     | 00000                 | 0000   |           |            |            |              |

|     | 15   |     |          |     |      |     | 21  |          |      |     |     |         | 27                    |        |           |            |            |              |

|     | 16   | 17  | 18       | 19  | 20   | 21  | 22  | 23       | 24   | 25  | 26  | 27      | 28                    | 29     | X30       | X31        |            |              |

|     |      |     |          |     |      |     |     |          |      |     |     |         |                       |        |           |            |            |              |

|     |      |     |          |     |      |     |     |          |      |     |     |         |                       |        |           |            |            |              |

|     |      |     |          |     |      |     |     |          |      |     |     |         |                       |        |           |            |            | Ī            |

|     |      | 4   | ,000,000 |     |      |     | 5   | ,000,000 | )    |     |     | 6       | ,000,000,             | 0      |           | 7,012,43   | 37.5ns     | <u> </u>     |

|     |      |     |          |     |      |     |     |          |      |     |     |         |                       |        |           | 1 ol       | oject sele | ected        |

Shift register & counter (if then) Result in an FPGA from 2002: (Altera EP20k200FC484-3) 81 out of 8320 logic elements 44 registers

11% (41/376) of pins

10.6 ns (94.5 MHz) position\_count-> position\_count

| tco: | 8.0 ns: | data_word_reg -> data_word         |

|------|---------|------------------------------------|

| tsu: | 7.0 ns: | new_value_available -> data_encode |

Shift register & counter (case) Result in an FPGA from 2002: (Altera EP20k200FC484-3) 50 out of 8320 logic elements (with case statement) 44 registers

11% (41/376) of pins

9.1 ns (109.9 MHz) position\_count-> data\_encode

| tco: | 7.0 ns: | data_word_reg -> data_word         |

|------|---------|------------------------------------|

| tsu: | 6.3 ns: | new_value_available -> data_encode |

### Position decoder – shift register

- Task fulfilled?

- User requirements fulfilled?

- Did we ask enough to understand user needs?

- Maybe at the time of project start, but now is the time to rediscuss

### Position decoder – shift register

#### • Task fulfilled?

- Few logic cells

- Timing constraints fulfilled

- User requirements fulfilled?

- Processing per 32 bit line takes:

- 32 bits \* 25 ns = 800 ns

- Data comes each 100 ns -> 1 out of 2560 32 bit line

- Decoding time for all lines is: 2560 \* 800 ns => 2 ms

- Within 2 ms => 20480 data lines arrive

- input FIFO would need to be at least 20k \* 32 bit deep

- During 2 ms no other trigger acquisition can take place

dead time => max trigger rate: 488 Hz

User requirements not fulfilled

How to decode the address? this line has two hits the state machine must send two hits into the dual port memory

| row address | hit position = 5  |

|-------------|-------------------|

| row address | hit position = 11 |

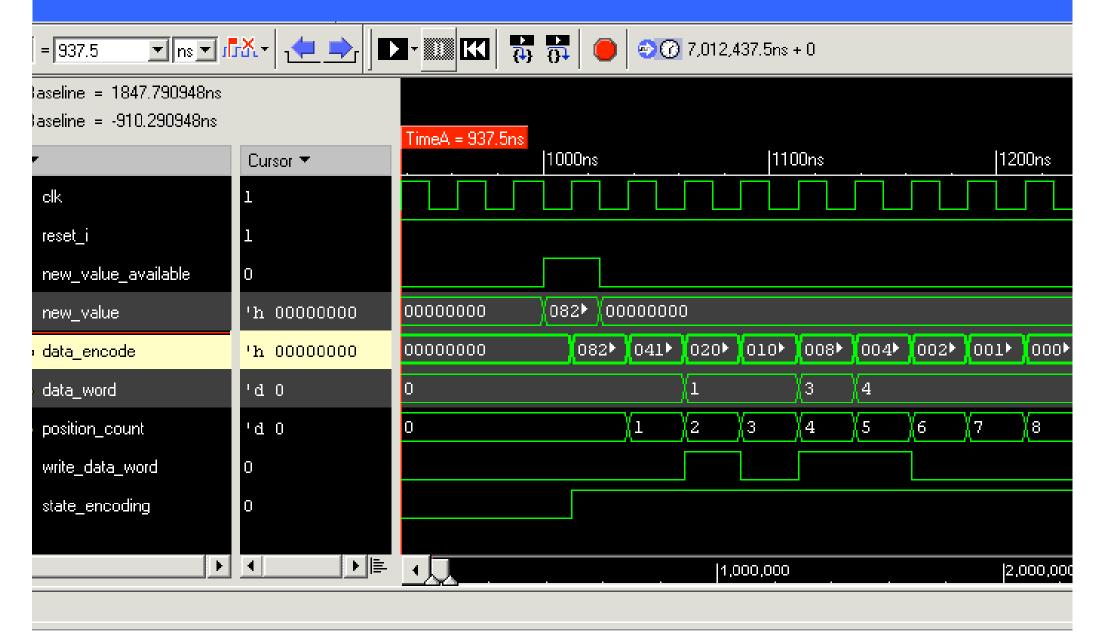

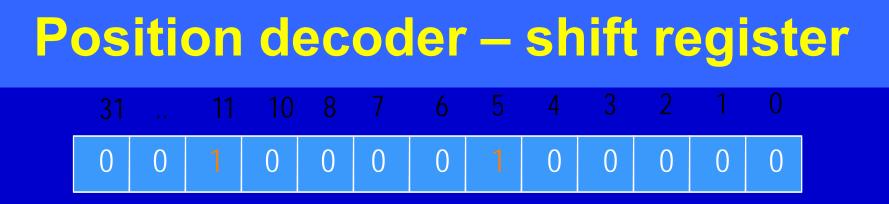

### Position decoder – priority encoder

### Position decoder – priority encoder

```

--postionDecoderPri

library ieee:

use ieee.std logic 1164.all;

use ieee.numeric std.all;

entity positionDecoder is

port (

std logic:

clk

:in

std logic.

:in

reset i

std_logic;

new value available

:in

std logic vector (31 downto 0);

new value

:in

integer range 0 to 31;

data word

:out

write data word

std logic);

:out

end positionDecoder;

architecture Priority of positionDecoder is

component prior32

std logic vector (31 downto 0);

port ( inp

:in

:out std_logic_vector (4 downto 0));

code

end component;

component addressDecoder

std_logic_vector (4 downto 0);

port ( inp

:in

:out std logic vector (31 downto 0));

code

end component;

:std_logic_vector (31 downto 0);

signal data encode

signal state encoding

std logic:

:std logic vector (4 downto 0);

signal hit address

:std_logic_vector (31 downto 0);

signal data encode actual

:std_logic_vector (31 downto 0);

signal data encode next

signal data encode next is 0

std logic

signal new value is 0

std logic

```

```

--postionDecoderPri

library ieee;

use ieee.std logic 1164.all;

use ieee.numeric std.all;

entity positionDecoder is

port (

clk

:in

std_logic;

std_logic,

:in

reset i

std_logic;

new value available

:in

std_logic_vector (31 downto 0);

new value

:in

:out integer range 0 to 31;

data word

:out std logic);

write data word

end positionDecoder;

architecture Priority of positionDecoder is

component prior32

std_logic_vector (31 downto 0);

port (

inp

:in

:out std logic vector (4 downto 0));

code

end component;

component addressDecoder

:in std_logic_vector (4 downto 0);

port (

inp

:out std logic vector (31 downto 0));

code

end component;

signal data encode

:std_logic_vector (31 downto 0);

signal state encoding

std_logic;

signal hit address

:std_logic_vector (4 downto 0);

signal data encode actual

:std_logic_vector (31 downto 0);

:std_logic_vector (31 downto 0);

signal data encode next

signal data encode next is 0

std_logic;

signal new value is 0

std logic.

```

```

data encode

<= data encode next;

<= '0';

state encoding

end if:

when others =>

(others => '0');

data encode

<= '0':

state encoding

end case;

end if;

end if;

end process;

<= data encode and data encode actual;</pre>

data encode next

write data word

<= state encoding:

<= to integer (unsigned(hit address));</pre>

data word -

a prior32: prior32

port map (data encode, hit address);

a addressDecoder: addressDecoder

1 1 1 1 1

6 5 4 3 2 1

port map (hit address, data encode actual);

process (data encode next)

begin

data encode next is 0 <= '1';

else

data_encode_next_is_0 <= '0';</pre>

end if:

end process;

process (new value)

begin

new value is 0 <= '1';

else

new value is 0 <= '0';

end if;

end process;

end Priority;

```

```

library ieee;

use ieee.std_logic_1164.all;

entity prior32 is

port ( inp

:in std_logic_vector (31 downto C);

:out std_logic_vector (4 downto 0));

code

end prior32;

architecture behavioral0 of prior32 is

--prior32

***************

begin

process {inp}

begin

if

\{inp\{0\} =

code <= '00000":

] then

elsif (inp(1) = elsif (inp(2) = fint)

code <= '00001";

then

code <= '00010"

then

elsif (inp(3) =

then

code <= '00011";

elsif(inp(4) =

code <= '0010C";

] then

elsif \{inp\{5\} =

code <= '00101"

) then

elsif (inp(6) =

) then

code <= '00110"

elsif (inp(7)) =

code <= '00111"

) then

code <= '01000";

elsif (inp(8) =

) then

elsif (inp(9) =

code <= '01001"

then

elsif (inp(10) =

code <= '01010")

') then

elsif (inp(11) =

code <= '01011"

then

elsif (inp(12)) =

code <= '01100";

then

elsif (inp(13)

then

code <= '01101"

=

- 1 I

elsif (inp('4)

then

code <= '01110"

=

elsif (inp(15)

- 1 Î

then

code <= '01111"

=

- 1 İ

elsif(inp(16)) =

then

code <= '10000"

elsif (inp{17}) =

elsif (inp{18}) =

111

code <= '10001";

then

211

then

code <= '10010"

E L

elsif (inp(19)

then

code 🗢 '10011"

-

elsif(inp(20) =

- 1 j

code <= '10100"

then

() then

elsif (inp(21) =

code 🕶 '10101";

elsif (inp(22)

code <= '10110"

=

then

elsif (inp(23)

(1)

then

code < '10111"

- 11

elsif(inp(24)) =

code <= '11000"

then

⊡i

elsif (inp{25}) =

then

codo <= '11001";

elsif(inp(26) =

___j

code <= '11010"

then

ΞĿi

elsif {inp{27}} =

then

codo <= '11011"

- 1 i

code <= '11100"

elsif (inp(2\delta) =

then

211

elsif (inp{29}) =

codo <= '11101"

then

() then

elsif (inp(30) =

code <= '11110":

1) then

elsif (inp(31) =

codo <= '111111";

code <= '11111':

else

end if;

end process;

end behavioral0;

```

```

--adressDecoder

library ieee;

use ieee.std_logic_1164.all;

entity addressDecoder is

port ( inp

std_logic_vector (4 downto 0);

:in

:out std_logic_vector (31 downto 0));

code

end addressDecoder;

architecture behavioral of addressDecoder is

beqin

process (inp)

begin

case (inp) is

when "00000" =>

<=

code

when "00001" =>

code

<=

when "00010" =>

code

when "00011" =>

code

<= .

when "00100"

=>

code

<=

when "00101"

code

<= .

=>

when "00110" =>

code

<= .

when "00111"

=>

code

<=

"111111111111111111111111111101111111

when "01000" =>

code

<=

when "01001" =>

code

<=

-"11111111111111111111111110111111

when "01010"

=>

code

<=

when "01011"

=>

code

<= .

"111111111111111111111111011111

when "01100" =>

code

<=

"111111111111111111111110111111

when "01101" =>

code

<=

"111111111111111111111011111111

when "01110" =>

code

<=

"11111111111111111111011111111111

when "01111"

=>

code

<=

"111111111111111111011111111

when "10000" =>

"11111111111111110111111111111111

code

<=

when "10001" =>

code

<=

"111111111111111101111111111111111111

when "10010"

"111111111111110111111111111111111

=>

code

<=

when "10011"

=>

code

<=

"11111111111101111111111111111111

when "10100" =>

"1111111111110111111111111111111111

code

<=

when "10101"

=>

code

<=

"1111111111101111111111111111111

when "10110"

=>

code

when "10111" =>

code

<= .

when "11000" =>

code

<=.

when "11001" =>

code

<=

when "11010" =>

code

<=

when "11011"

=>

code

<=.

"11110111111111111111111

when "11100" =>

code

when "11101" =>

code

<=

when "11110" =>

code

when "11111" =>

code

when others =>

code

end case;

end process;

end behavioral;

```

| đ                                                                                                                                              | ;<br>* 🚰 🗠 👒 🐇 🛍 🏔 🗙                                                 |            | M.,           |               |          |             |                   |                                         |             |         |                            |          |                 |            |                   | Send To: 💽    | X E 🖬 🖬 🗐             |

|------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|------------|---------------|---------------|----------|-------------|-------------------|-----------------------------------------|-------------|---------|----------------------------|----------|-----------------|------------|-------------------|---------------|-----------------------|

| Se.                                                                                                                                            | Search Names: Signal 🔻 💌 🛝 Search Times: Value 👻 🍂                   |            |               |               |          |             |                   |                                         |             |         |                            |          |                 |            |                   |               |                       |

| <b>         </b>                                                                                                                               | Time: 🐨 175,000,000 👔 🖅 🕅 🗱 👘 💭 🚛 🕅 🕅 🖏 🖏 👘 🌒 🚳 🔊 🖓 1,794,950 ns + 0 |            |               |               |          |             |                   |                                         |             |         |                            |          |                 |            |                   |               |                       |

| Baseline = 1,212,500,000/s         Euror-Baseline = -237,500,000/s         Euror-Baseline = 1,212,500,000/s         Baseline = 1,212,500,000/s |                                                                      |            |               |               |          |             |                   |                                         |             |         | Baseline = 1,212,500,000/s |          |                 |            |                   |               |                       |

| <b>R</b>                                                                                                                                       | Name ▼                                                               | Cursor 🔻   | 980,000,000fs | 1,000,000,000 |          | 0,000,000fs | 1,040,000,000fs   | 1,060,000,000fs                         | 1,080,000,0 |         | 1,100,000,000fs            | I,12     | ),000,000fs<br> | 1,140,000, | 1,160,000,000fs   | 1,180,000,000 | fs 1,200,000,00       |

| 3                                                                                                                                              | i eset_i                                                             | 1          |               |               |          |             |                   |                                         |             |         |                            |          |                 |            |                   |               |                       |

|                                                                                                                                                | ····→ new_value_available                                            | 0          |               |               |          |             |                   |                                         |             |         |                            |          |                 |            |                   |               |                       |

|                                                                                                                                                | 🗄 🎝 new_value                                                        | 'h 000000▶ | 0000000       | 0820C01A      |          | 00000000    |                   |                                         |             |         |                            |          |                 |            |                   |               |                       |

|                                                                                                                                                | 🕀 🐨 data_encode                                                      | 'h 000000▶ | 0000000       |               | 0820C01A |             | 0820C018          | 0820C010                                | χo:         | 8200000 |                            | 08208000 |                 | 08200000   | 0800000           | 000           | 00000                 |

|                                                                                                                                                | 🕀 🐨 💼 data_encode_actual                                             | 'h 7FFFFF∳ | 7FFFFFFF      |               | FFFFFFFD |             | FFFFFFF7          | FFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFFF | F           | FFFBFFF |                            | FFFF7FFF |                 | FFDFFFFF   | F7FFFFFF          | 7FF           | FFFFF                 |

|                                                                                                                                                | 🕀 📲 👘 data_encode_next                                               | 'h 000000▶ | 0000000       |               | 08200018 |             | 0820C010          | 0820000                                 | ) (or       | 8208000 | )                          | 08200000 |                 | 08000000   | 00000000          |               |                       |

|                                                                                                                                                | ⊕≪ <b>⊊</b> • hit_address                                            | 'h 1F      | 1F            |               | 01       |             | 03                | 04                                      | (O)         | E       | )                          | OF       |                 | 15         | (1B               | 1F            |                       |

|                                                                                                                                                | tata_word                                                            | 'd 31      | 31            |               | 1        |             | (з                | 4                                       | 1           | 4       | )                          | 15       |                 | 21         | 27                | 31            |                       |

|                                                                                                                                                | 🖽 data_encode_next_is_0                                              | 1          |               |               |          |             |                   |                                         |             |         |                            |          |                 |            |                   |               |                       |

|                                                                                                                                                |                                                                      | o          |               |               |          |             |                   |                                         |             |         |                            |          |                 |            |                   |               |                       |

|                                                                                                                                                | write_data_word                                                      | 0          |               |               |          |             |                   |                                         |             |         |                            |          |                 |            |                   |               |                       |

|                                                                                                                                                |                                                                      |            |               |               |          |             |                   |                                         |             |         |                            |          |                 |            |                   |               | _                     |

| J                                                                                                                                              | ۲. ()                                                                | ┥─▶⊫       | 1.0           |               |          |             | 1,000,000,000,000 |                                         |             |         | 2,000,000,000,0            | 00       |                 |            | 3,000,000,000,000 | )             | 3,794,950,000,000fs > |

| 6                                                                                                                                              |                                                                      |            |               |               |          |             |                   |                                         |             |         |                            |          |                 |            |                   |               | 0. objects selected   |

0

| Sea                                                                                     | Search Names: Signal 🔻 💽 🛝 Search Times: Value 🕶 🦓 🦓           |            |                                         |                          |          |             |              |        |               |       |  |  |  |

|-----------------------------------------------------------------------------------------|----------------------------------------------------------------|------------|-----------------------------------------|--------------------------|----------|-------------|--------------|--------|---------------|-------|--|--|--|

| ] 🔽 TimeA 💌 = 975,000,000 💌 fs 💌 rFX ▼   👥 ⇒r   💵 ▼ 📖 🔣   🖏 📅   🧆   🥸 🕜 3,794,950ns + 0 |                                                                |            |                                         |                          |          |             |              |        |               |       |  |  |  |

| × ()<br>Q                                                                               | Baseline = 1,212,500,000fs<br>Cursor-Baseline = -237,500,000fs | Surve =    | TimeA = 975,000,000fs<br> 980,000,000fs | <b> 1,000,000,000f</b> ; | 11 020   | 1,000,000fs | 1,040,000,0  | 006 11 | 060,000,000fs | 11.00 |  |  |  |

| <b>P</b>                                                                                | Name ▼<br>:→ clk                                               | Cursor 🔻   |                                         |                          | . 17,020 | ,           |              |        |               | 1,08  |  |  |  |

| Ð                                                                                       | ····→I reset_i<br>·····→I new_value_available                  | 1<br>0     |                                         |                          |          |             | J            |        |               |       |  |  |  |

|                                                                                         | ⊕ <b>⊊</b> new_value                                           | 'h 000000▶ | 0000000                                 | 0820C01A                 |          | 00000000    |              |        |               |       |  |  |  |

|                                                                                         |                                                                | 'h 000000⊧ | 0000000                                 |                          | 0820C01A | ·           | 0820C018     |        | 0820C010      |       |  |  |  |

|                                                                                         | ⊕ data_encode_actual                                           | 'h 7FFFFF∳ | 7FFFFFFF                                |                          | FFFFFFD  |             | FFFFFFF7     |        | FFFFFFEF      |       |  |  |  |

|                                                                                         | ⊞‱ data_encode_next                                            | 'h 000000▶ | 0000000                                 |                          | 0820C018 |             | 0820C010     |        | 0820000       |       |  |  |  |

|                                                                                         | ⊕                                                              | 'h lF      | lF                                      |                          | 01       |             | 03           |        | 04            |       |  |  |  |

|                                                                                         | ⊕                                                              | 'd 31      | 31                                      |                          | 1        |             | 3            |        | 4             |       |  |  |  |

|                                                                                         |                                                                | 1          |                                         |                          |          |             |              |        |               |       |  |  |  |

|                                                                                         | ······· <mark>··不·</mark> state_encoding                       | 0          |                                         |                          |          |             |              |        |               |       |  |  |  |

|                                                                                         | 🕞 write_data_word                                              | 0          |                                         |                          |          |             |              |        |               |       |  |  |  |

|                                                                                         |                                                                |            |                                         |                          |          |             |              |        |               |       |  |  |  |

| J                                                                                       |                                                                |            | •                                       |                          |          |             | 1,000,000,00 | 0,000  |               |       |  |  |  |

| ര                                                                                       |                                                                |            |                                         |                          |          |             |              |        |               |       |  |  |  |

####

#### 🕜 3,794,950ns + 0

| ),000fs  1,020,000,000 |                                        | ,000,000fs | 1,040,000,000fs1,   |  | ,060,000,000fs  1,080,000                     |   | 1,100,000,000,0                               |                 | Ofs  1,120,000,000fs |  | 1,140,000,000fs |  | 1,160    |

|------------------------|----------------------------------------|------------|---------------------|--|-----------------------------------------------|---|-----------------------------------------------|-----------------|----------------------|--|-----------------|--|----------|

| 1 0                    |                                        | V0000000   | J                   |  |                                               |   |                                               |                 | 1                    |  |                 |  |          |

|                        | 00000000 00000000000000000000000000000 |            | X0820C018           |  | (0820C010 X                                   |   | 0820C000                                      |                 | 08208000             |  | 08200000        |  | )<br>(08 |

|                        | FFFFFFFD                               |            | FFFFFFF7            |  | FFFFFFFF                                      |   | FFFFBFFF                                      |                 | FFFF7FFF             |  | VFFDFFFFF       |  | (0,<br>  |

|                        | \0820C018                              |            | 0820C010            |  | (0820C000                                     |   | 08208000                                      |                 | X08200000            |  | X08000000       |  | <br>Xoc  |

|                        | ∑01                                    |            | Λ<br>χοз            |  | //04                                          |   | OE                                            |                 |                      |  |                 |  | )<br> 1F |

|                        | χ <u>1</u>                             |            | λ<br>χ <sub>3</sub> |  | γ<br>γ_4                                      |   | 14                                            |                 | λ<br>λ15             |  |                 |  | )<br>21  |

|                        |                                        |            | 0                   |  | ۱ <u>ــــــــــــــــــــــــــــــــــــ</u> | , | ۰ <u>ــــــــــــــــــــــــــــــــــــ</u> | ,               | n                    |  | ^               |  |          |

|                        |                                        |            |                     |  |                                               |   |                                               |                 |                      |  |                 |  |          |

|                        |                                        |            |                     |  |                                               |   |                                               |                 |                      |  |                 |  |          |

|                        |                                        |            |                     |  |                                               |   |                                               |                 |                      |  |                 |  |          |

| 1,000,000,000,000      |                                        |            |                     |  |                                               |   |                                               | 2 000 000 000 0 | 200                  |  |                 |  | 12.00    |

|                        |                                        |            |                     |  |                                               |   |                                               |                 |                      |  | 3,00            |  |          |

|                        |                                        |            |                     |  |                                               |   |                                               |                 |                      |  |                 |  |          |

| Posi                     | tion de                 | coder               | – prio          | r <mark>ity enc</mark>   | oder                         |

|--------------------------|-------------------------|---------------------|-----------------|--------------------------|------------------------------|

|                          |                         |                     |                 | Send To:                 | 🐼 🎇 🗈 🏗 🌃 🖩                  |

|                          |                         |                     |                 | Time: Se S               | 75,000,000fs : 1,2 🗹 🔍 = 🗉 🏧 |

| 1,060,000,000fs 1,080,00 | 10,000fs  1,100,000,000 | fs  1,120,000,000fs | 1,140,000,000fs | 1,160,000,000fs  1,180,0 | Baseline = 1,212,500,000fs   |

|                          |                         |                     |                 |                          |                              |

|                          |                         |                     |                 |                          |                              |

| 0820C010                 | 0820000                 | 08208000            | 08200000        | 08000000                 | <u>x00000000</u>             |

|                          | FFFFBFFF                | FFFF7FFF            | FFDFFFF         | F7FFFFFF                 | (7FFFFFFF                    |

| (0820C000                | 08208000                | <u> </u>            | <u> </u>        | <u> </u>                 |                              |

| <u></u> 04               | (OE                     | OF                  | X15             | <u>1B</u>                | )[1F                         |

| 4                        | 14                      | 15                  | ) <sup>21</sup> | 27                       | 31                           |

|                          |                         |                     |                 |                          | ]                            |

|                          | . [2,000,000,000,       | 000                 |                 | 3,000,000,000            | ▼<br>3,794,950,000,000fs     |

|                          |                         |                     |                 |                          | 0 objects selected           |

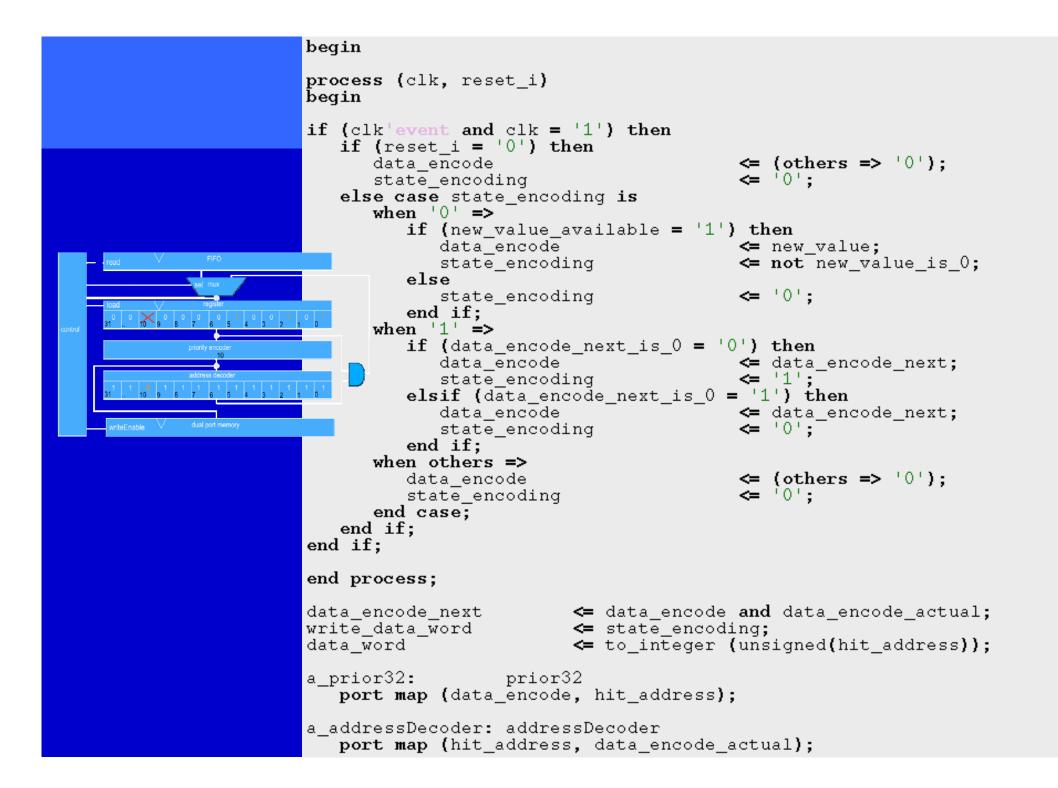

Shift register & counter (case) Result in an FPGA from 2002: (Altera EP20k200FC484-3) 50 with case out of 8320 logic elements 44 registers

11% (41/376) of pins

9.1 ns (109.9 MHz) position\_count-> data\_encode

tco: 7.0 ns: data\_word\_reg -> data\_word tsu: 6.3 ns: new\_value\_available -> data\_encode

**Priority encoder** Result in an FPGA from 2002: (Altera EP20k200FC484-3) 172 (out of 8320) logic elements 33 registers addressDecoder: 16 54 prior32: 11% (41/376) of pins 20.8 ns (48.0 MHz) data\_encode -> state\_encoding 17.1 ns: data\_encode -> data\_word tco: 14.9 ns: new\_value -> state\_encoding tsu:

Shift register & counter (case) Result in an FPGA from 2002: (Altera EP20k200FC484-3) 50 with case out of 8320 logic elements 44 registers

11% (41/376) of pins

9.1 ns (109.9 MHz) position\_count-> data\_encode

tco: 7.0 ns: data\_word\_reg -> data\_word tsu: 6.3 ns: new\_value\_available -> data\_encode

Priority encoder Result in an FPGA from 2002: (Altera EP20k200FC484-3) 172 (out of 8320) logic elements -> more logic cells 33 registers addressDecoder: 16 prior32: 54 11% (41/376) of pins

20.8 ns (48.0 MHz) data\_encode -> state\_encoding -> slower state machine, but faster processing tco: 17.1 ns: data\_encode -> data\_word tsu: 14.9 ns: new\_value -> state\_encoding

#### • Task fulfilled?

- Many logic cells

FPGA Timing constraints fulfilled

User requirements fulfilled?

Processing per 32 bit line takes:

numbHits per line \* 25 ns = ?

Data comes each 100 ns -> one out of 2560 32 bit line

- Decoding time for all lines is: 2560 \* ? ns => ? ms

- Within ? ms => ? data lines arrive

input FIFO would need to be at least ? \* 32 bit deep

- During ? ms no other trigger acquisition can take place

dead time => max trigger rate: ? Hz

User requirements fulfilled ?

#### • Task fulfilled?

- Physics simulation:

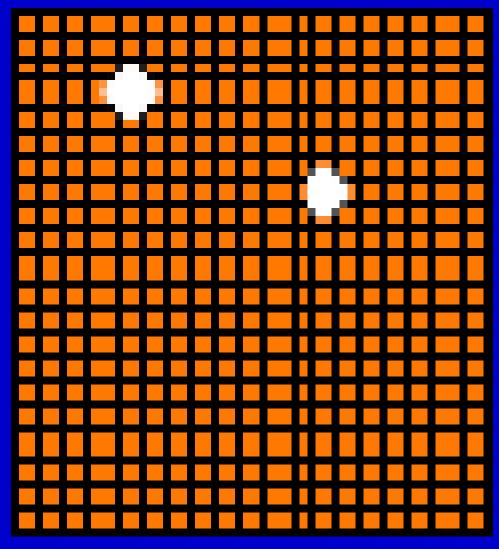

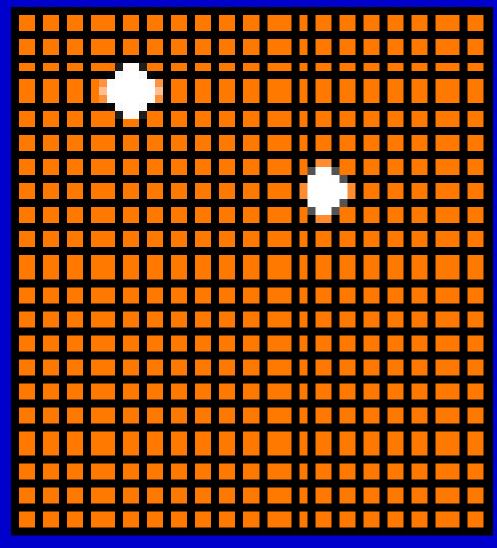

- max 2% of all pixels will be hit in one acquisition

- User requirements fulfilled?

- Processing per 32 bit line takes:

- (numbHits per line) \* 25 ns = (32 \* 0.02) \* 25 ns = <25 ns

- Data comes each 100 ns -> one out of 2560 32 bit line

- One line with up to 4 hits can be decoded before the next line arrives

- Input FIFO of 1000 \* 32 bits implemented to buffer statistical fluctuations or calibration sequences

- Dead time defined by transmission of data stream

- 2560 lines with each 100 ns => 256 µs => 3900 Hz

- dead time => max trigger rate: 3900 Hz

- User requirements fulfilled: yes

# Position decoder – priority encoder 31 .. 11 10 8 7 6 5 4 3 2 1 0 0 0 1 0 0 0 1 0 0 0 0

Priority encoder Result in an FPGA from 2002: (Altera EP20k200FC484-3) 172 (out of 8320) logic elements -> more logic cells

20.8 ns (48.0 MHz) data\_encode -> state\_encoding -> slower state machine, but faster processing

Slower and more logic can mean more elegant and effective

- User requirements fulfilled: yes

- Can we do better?

- Can we do faster or with less logic?

- Do we know something which the synthesizer does not know?

- Knowledge of implementation in target technology is important

- Knowledge of what the synthesizer is doing is important

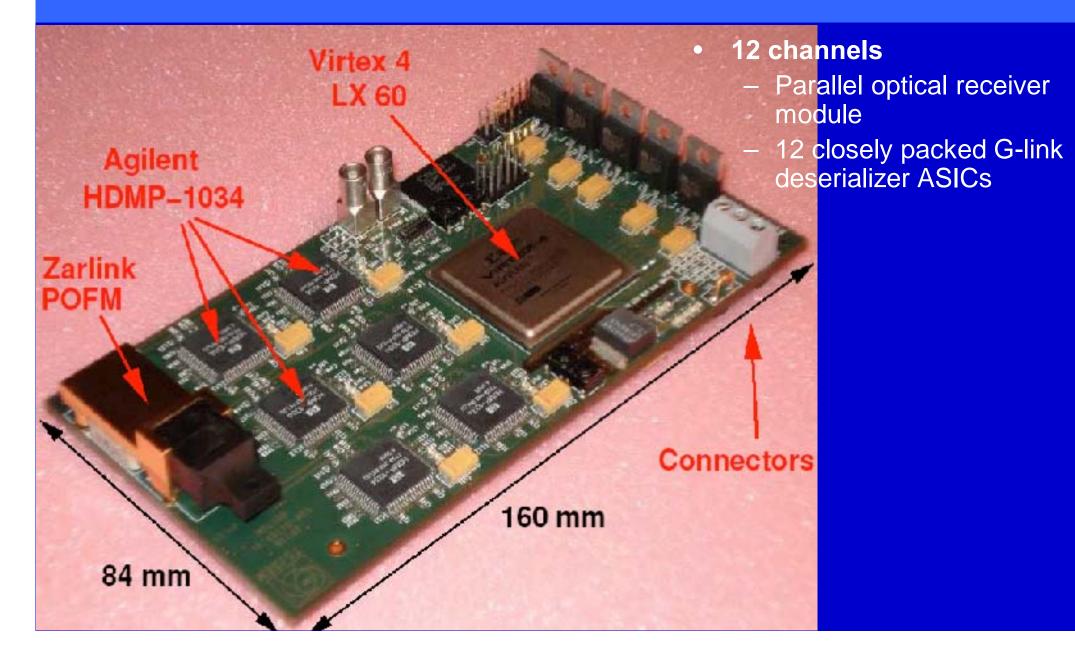

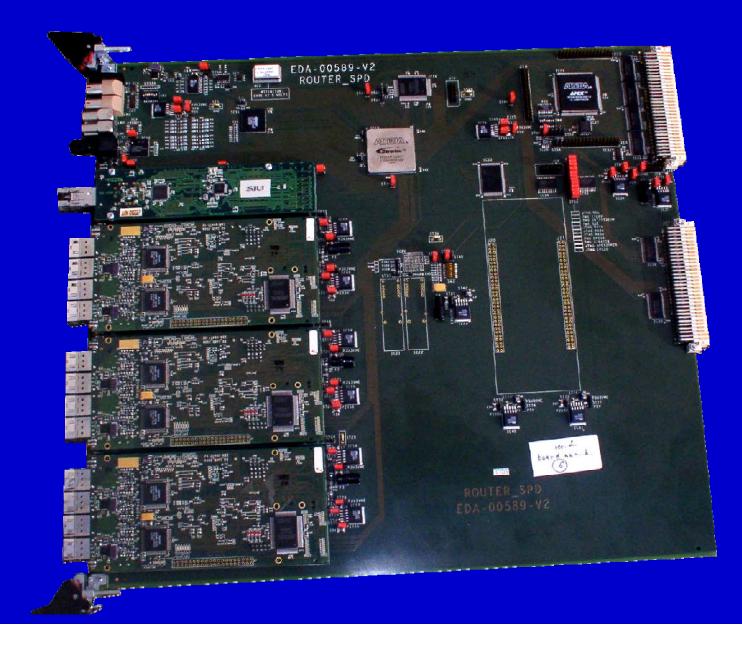

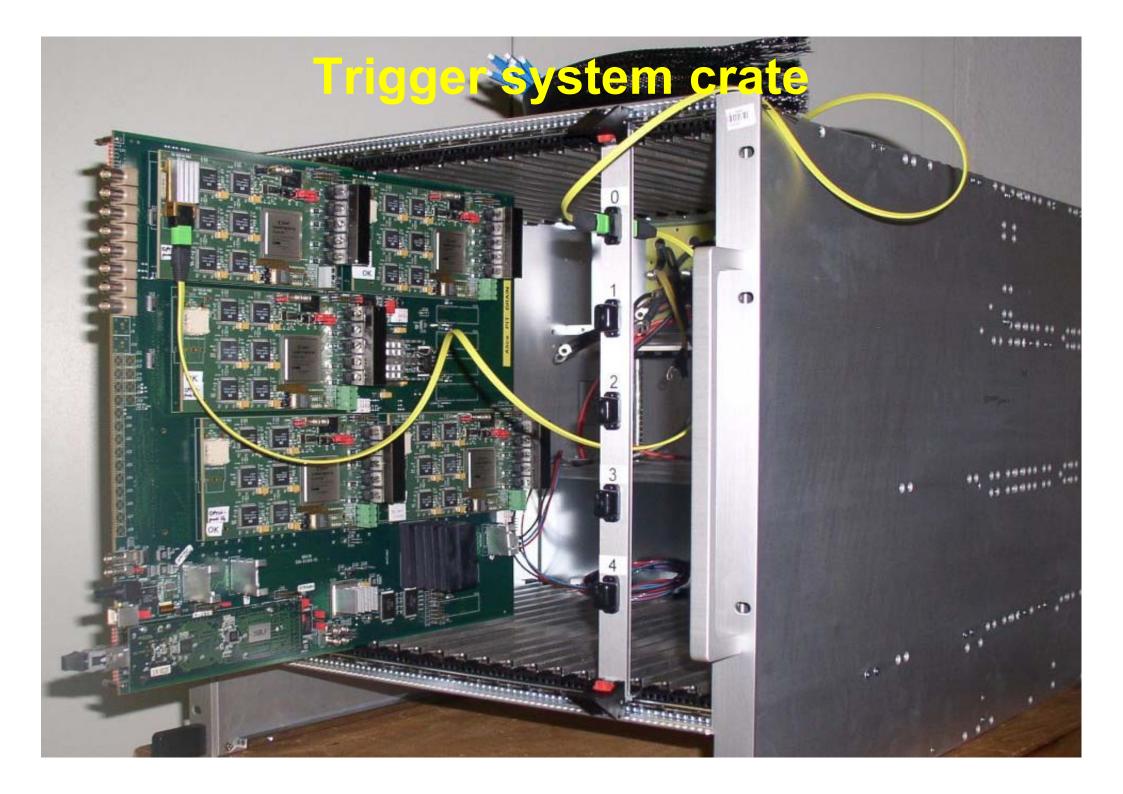

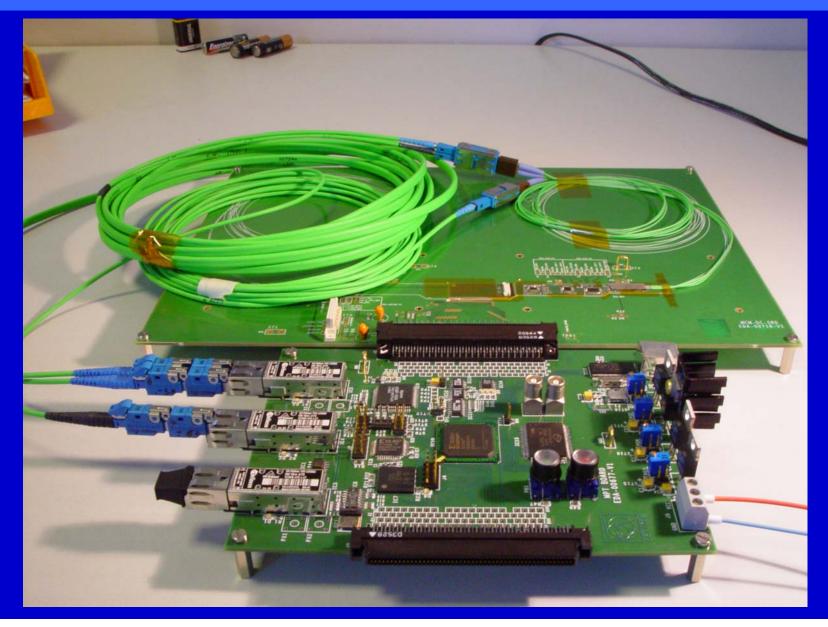

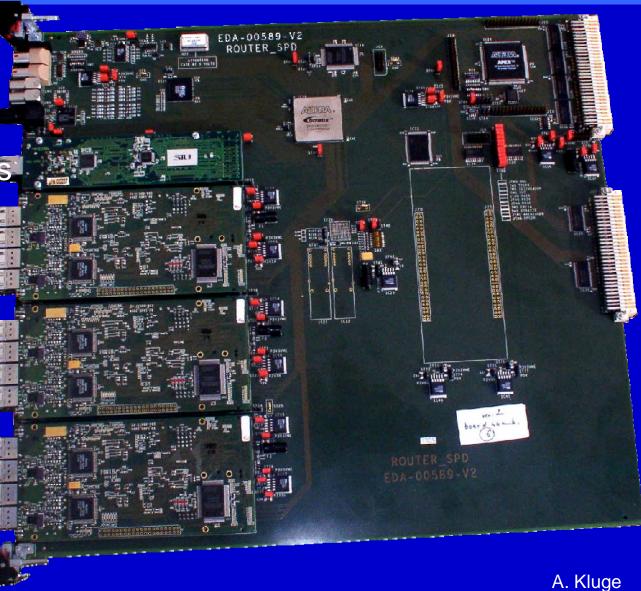

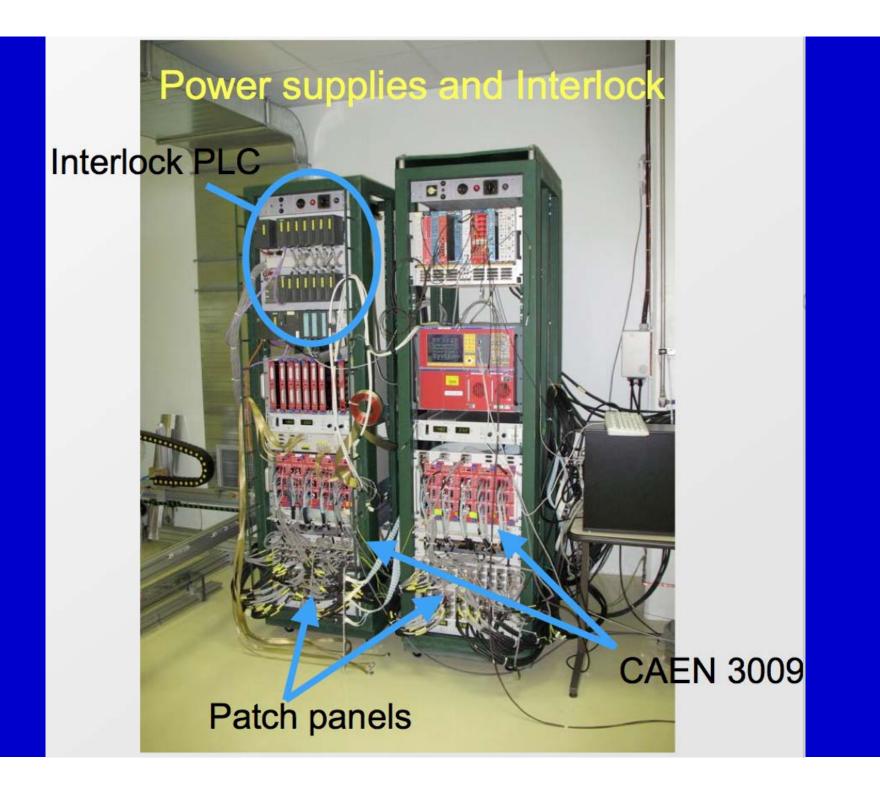

#### **Processor board with optical inputs**

# **Readout processor**

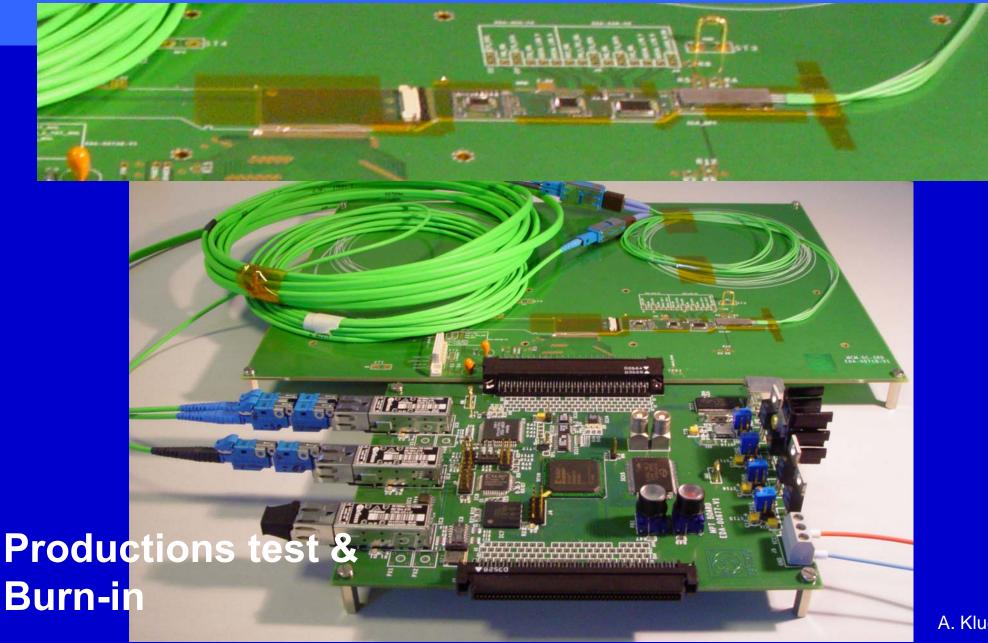

# **Production tests & verification**

# Simulation & Development

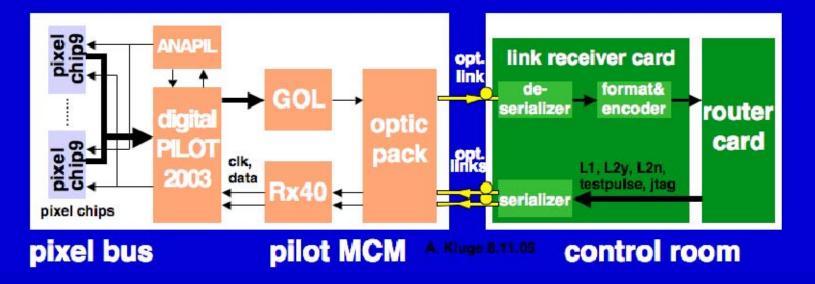

Full system VHDL/Verilog simulation ASIC -> MCM -> optical link -> FPGAs -> PCBs Functional test: Board level -> ASIC level Design handled by different engineers SEU Simulation

A. Kluge

## MCM

A. Kluge

# **Boundary scan**

Example: 12 FPGAs with1500 pins 11 SRAMs with>100 pins 40 connectors with 40 pins

Automated and remote tests

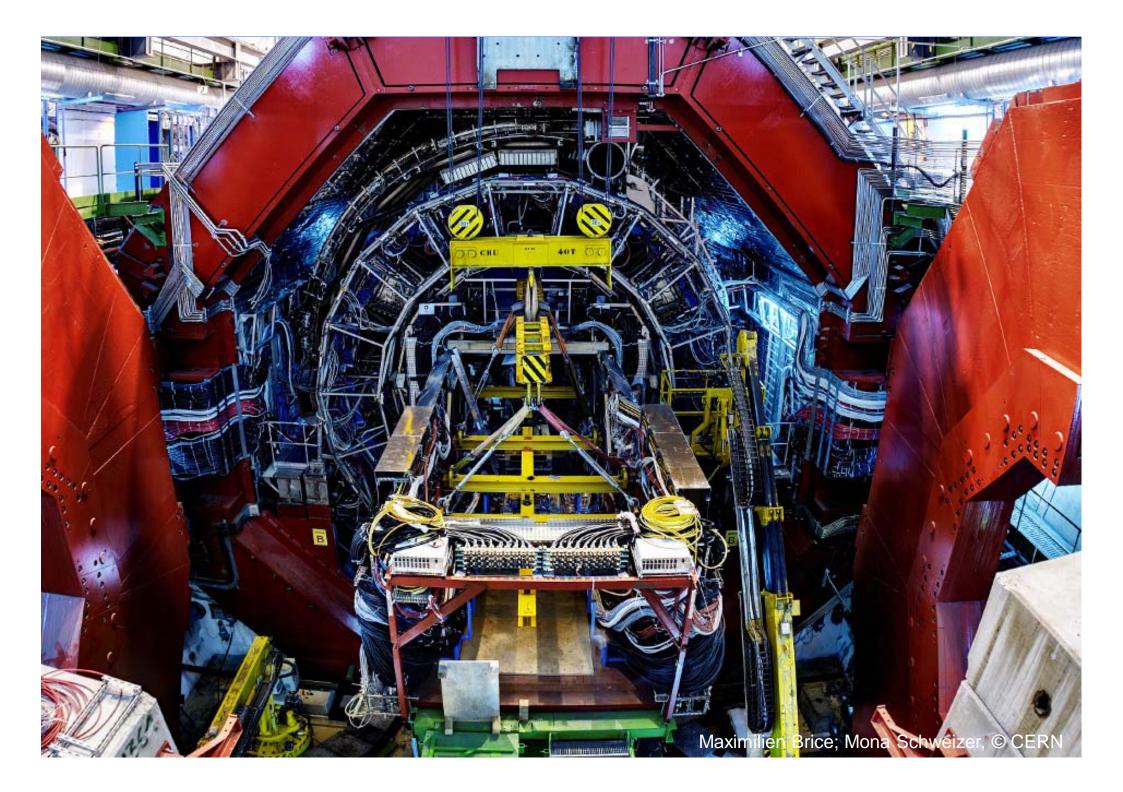

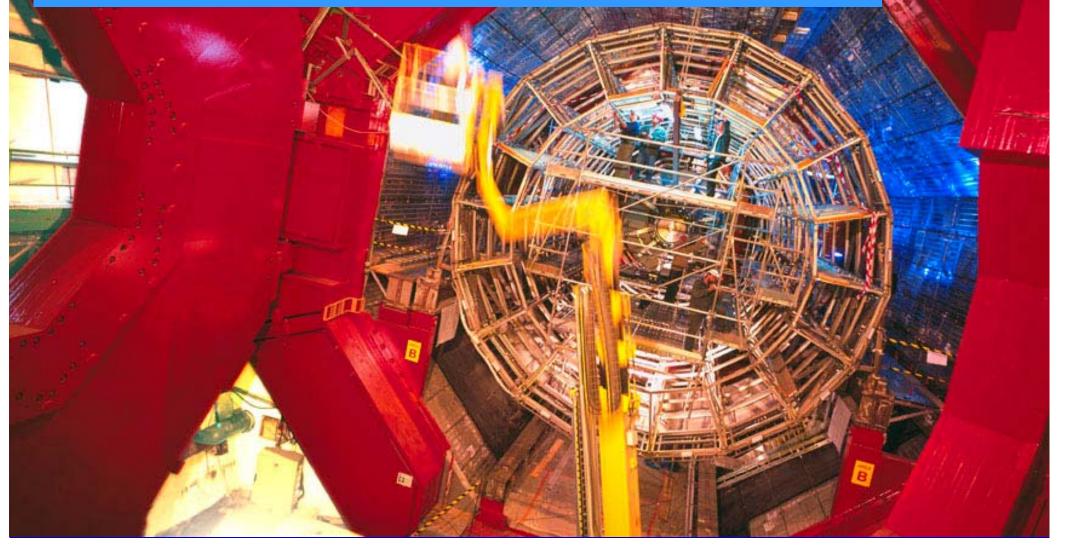

#### **System and Detector Integration**

# Assembly

# Half stave assembly station

Interconnections, electrical, optical fibers

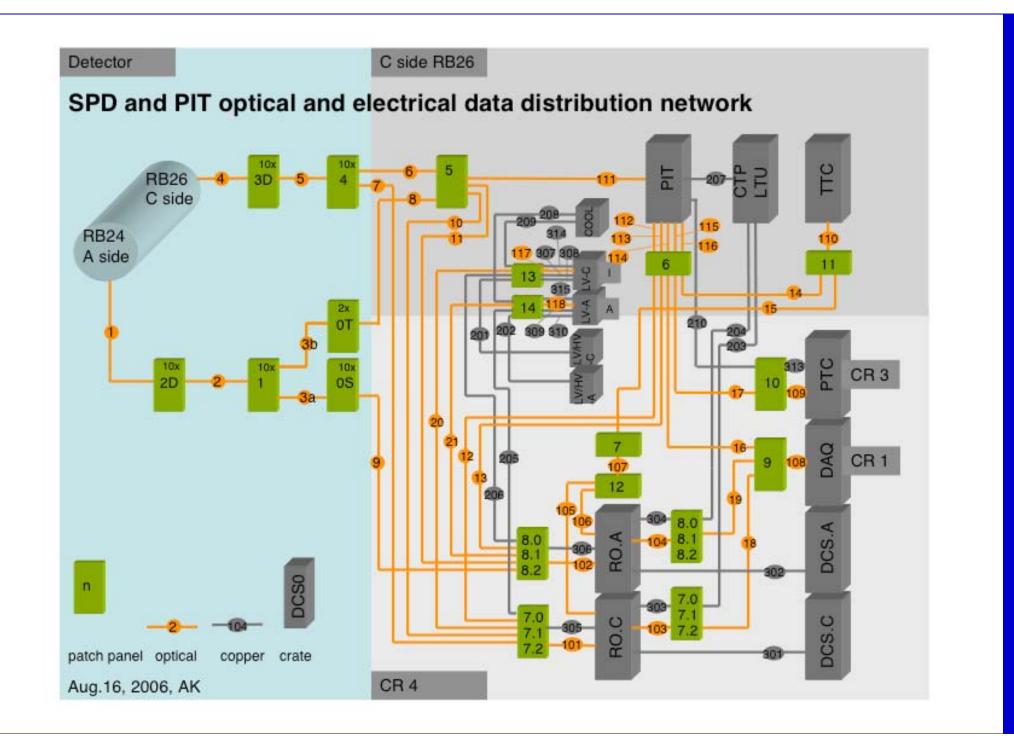

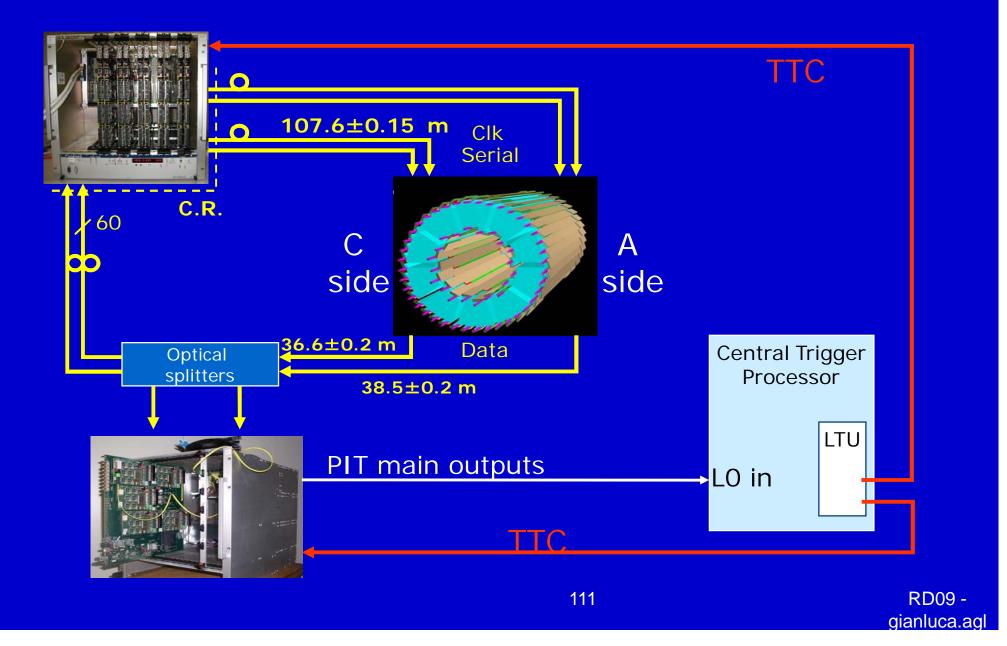

## Installation in ALICE experiment

- Voltage supply over 40m

- data path over 130m

- Distributed processors (130m)

- Mixture: Miniaturized electronics Civil engineering

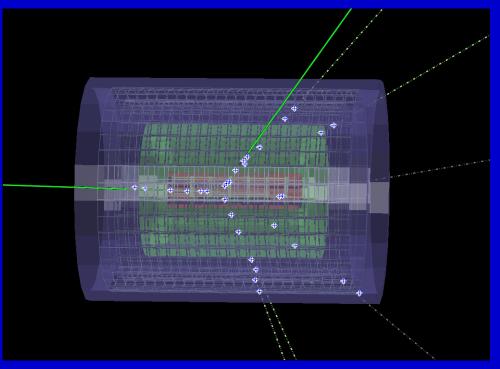

# **Particle collisions**

## **Beam events**

# Events from LHC circulating beam 11<sup>th</sup> September 2009

#### Pb+Pb @ sqrt(s) = 2.76 ATeV

2010-11-08 11:30:46 Fill : 1482 Run : 137124 Event : 0x00000000D3BBE693