# INTRODUCCIÓN AL DISEÑO FPGA-DSP

Cristian Sisterna, MSc UNSJ-C7T

#### **AGENDA**

- Introducción

- Bloques DSPs en Xilinx FPGAs

- MatLab/Simulink

- Simulink

- Xilinx System Generator

- o Ejemplo de Diseño con SysGen

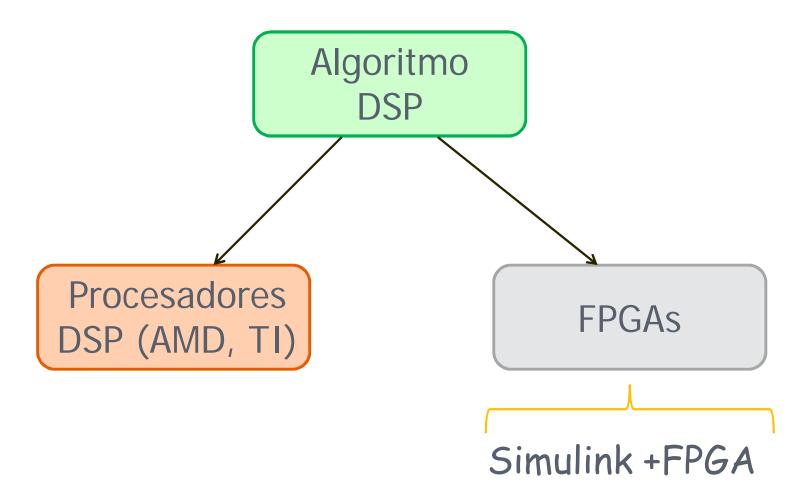

#### **ALGORITMOS DSPS**

#### ALGORITMOS DSPS-DÓNDE IMPLEMENTARLOS?

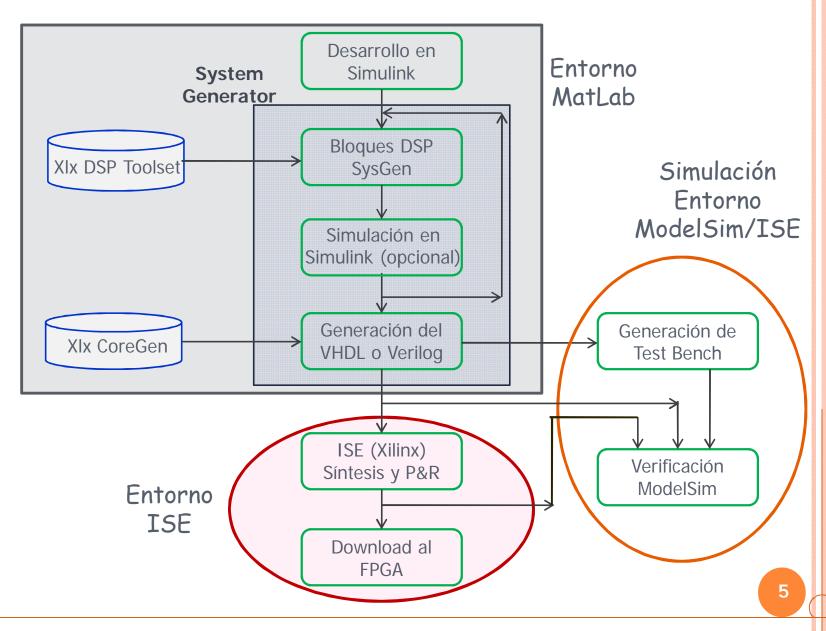

#### FLUJO DE DISEÑO SIMULINK-FPGA

# **DSP BLOCKS**

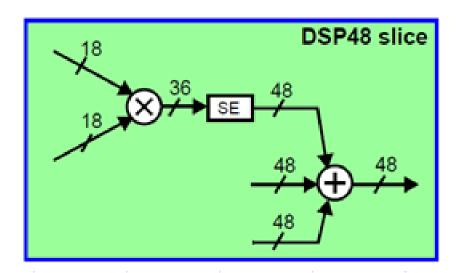

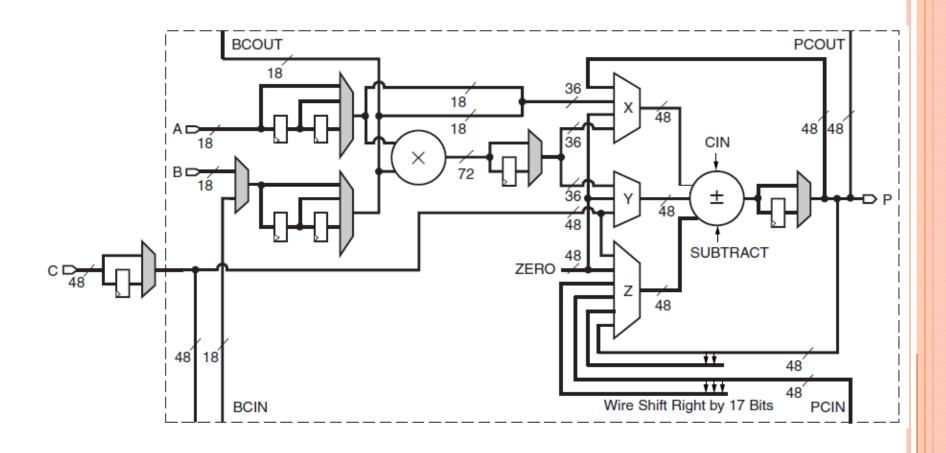

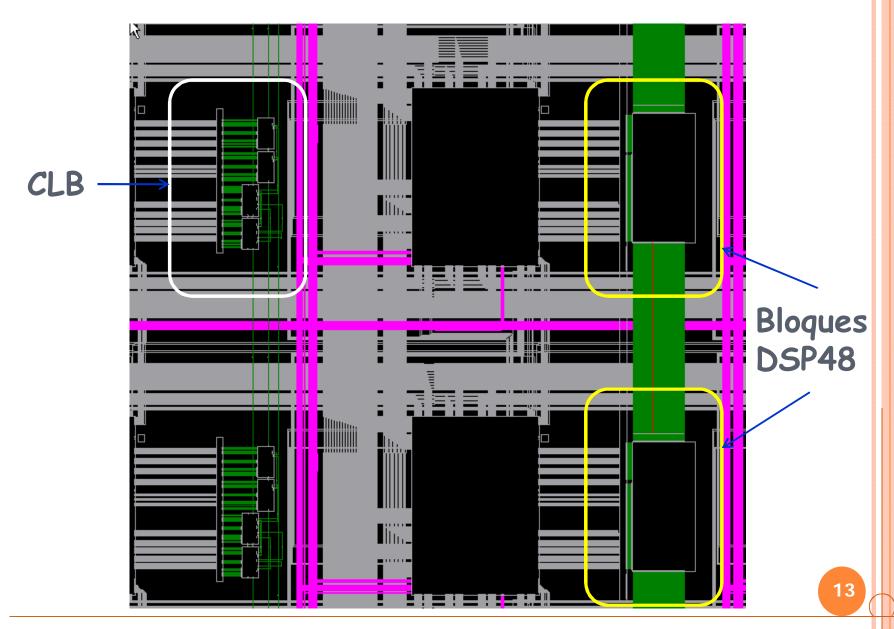

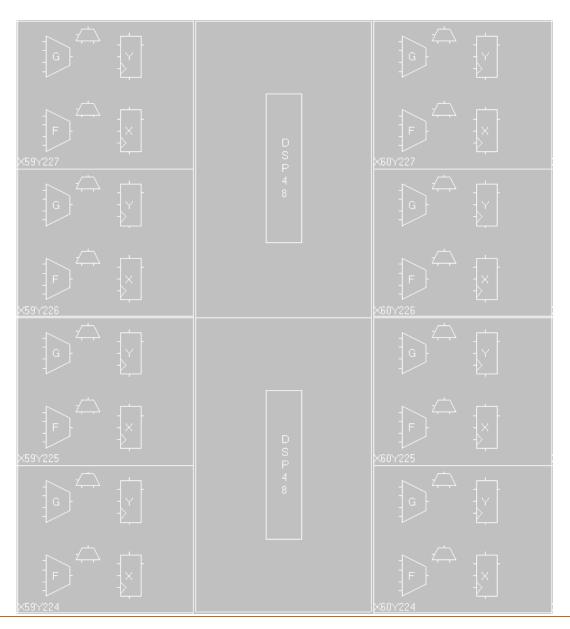

#### XILINX FPGA - BLOQUE DSP48

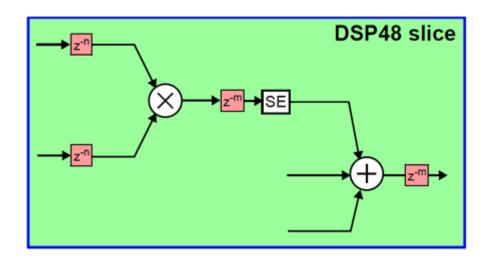

Desde un punto de vista simple el DSP48 puede multiplicar dos números de 18 bits (18x18) y acumular el resultado en un ACC de 48 bits. Todo expresado en complemento a dos.

SE - Sign Extension

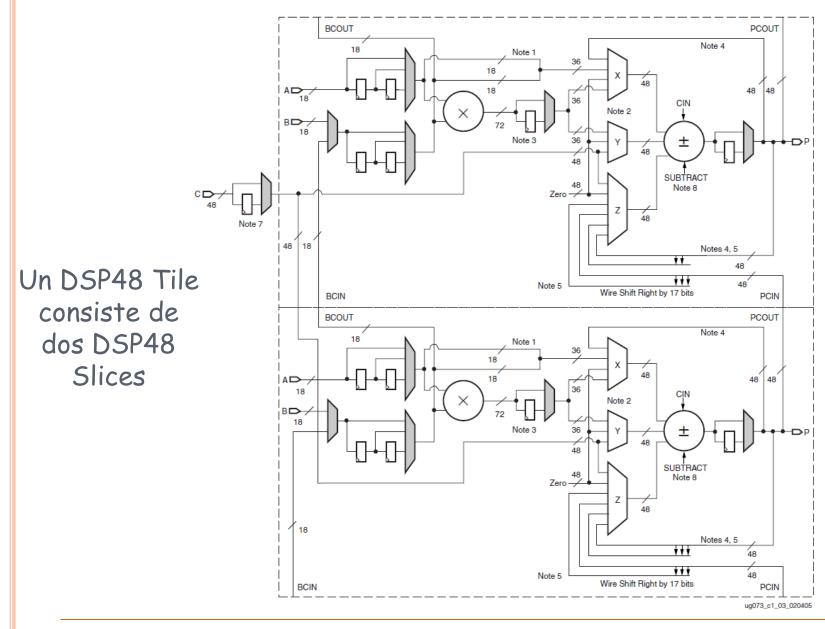

Nota: Dos DSP48 slices componen lo que se llama un Xtreme DSP Tile

### XILINX DSP48 SLICE

#### XILINX DSP48 TILE

9

#### BLOQUE DSP48 - REGISTROS

Existen diferentes opciones del uso de los registros disponibles en el DSP48

Los registros  $\square$  pueden tener n = 0, 1 o 2 para las entradas del multiplicador.

Los registros  $\overline{m}$  pueden tener m = 0 o 1.

10

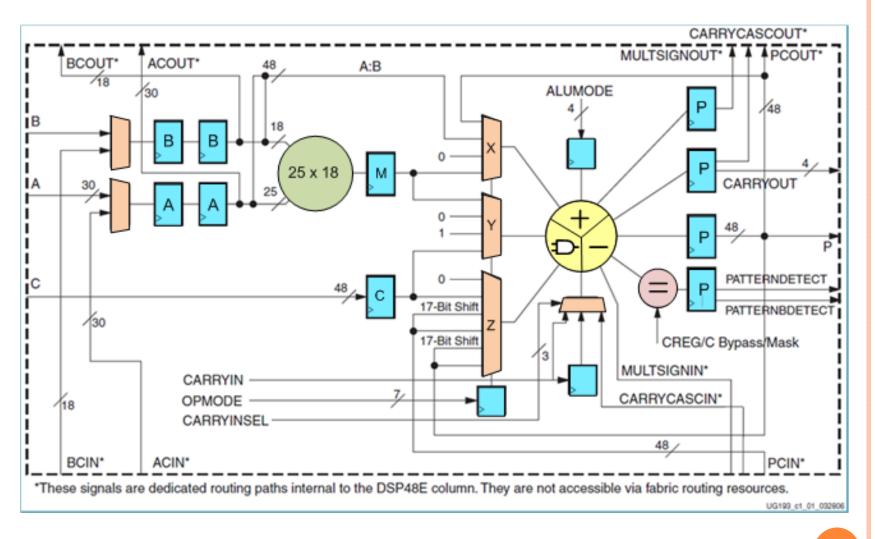

#### XILINX FPGA – BLOQUE DSP48

- El bloque DSP48 es parte del los bloques prediseñados ASMBLs (Application Specific Modular Blocks).

- El bloque DSP48 casi no usa el ruteo del FPGA, solo entrada y salidas. Ello implica: bajo consumo de potencia, muy alta frecuencia de trabajo y una implementación en silicio muy eficiente.

- Bloques DSP48E pueden fácilmente conectarse con sus bloques DSP48 vecinos. Pudiendo formar una cascada de bloques DSP48.

#### DSP48E - VIRTEX 5/6

#### DSP48 - FPGA VISTA INTERNA 1

### DSP48 – FPGA VISTA INTERNA 2

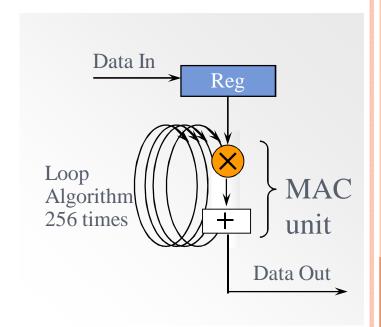

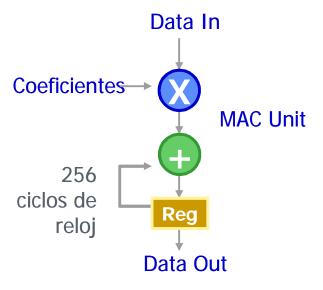

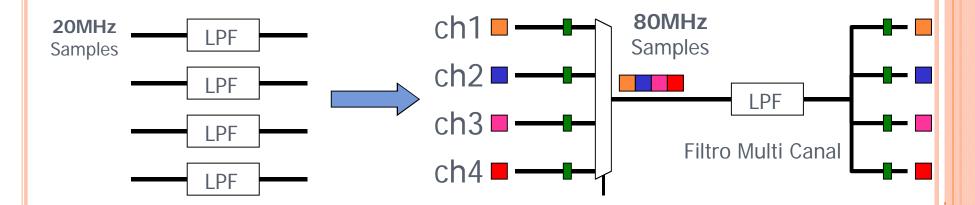

#### **DSP MAC LIMITES**

- Procesamiento sequencial processing limita max. frec. dato salida

- MAC tiempo compartida

- Reloj de alta frecuencia complica la performance

- Filtro FIR de 256 Tap

- 256 multiplica y acumula (MAC) operaciones por dato muestreado

- Una salida cada 256 ciclos de reloj

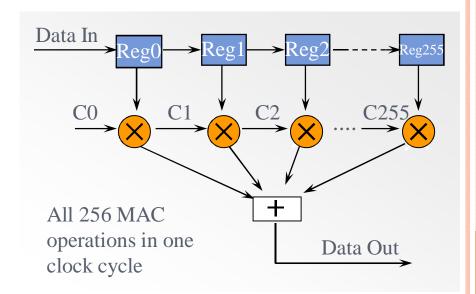

#### **FPGA MACs**

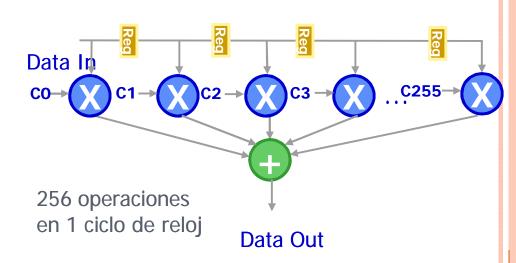

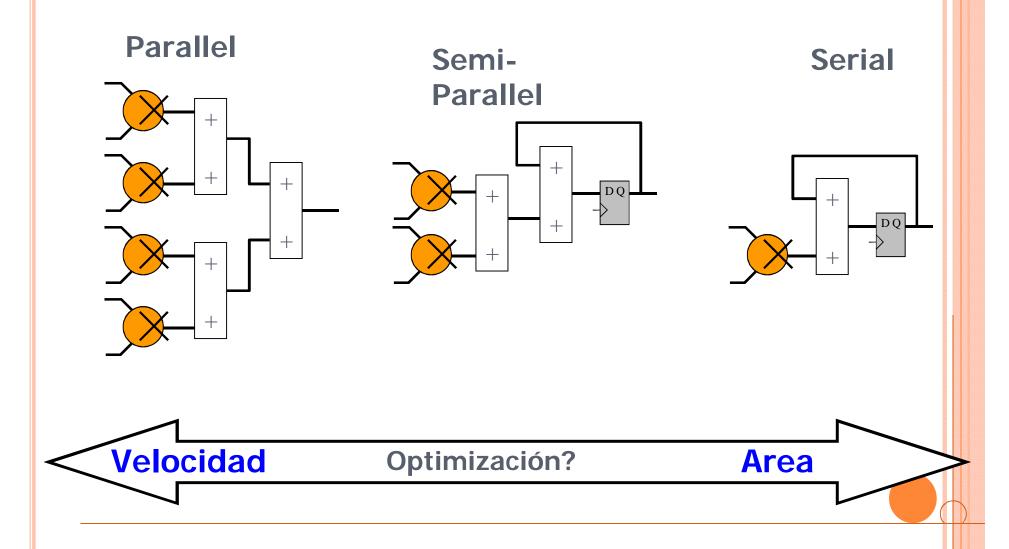

- Procesamiento paralelo maximiza frecuencia dato de salida

- Soporta cualquier nivel de paralelismo

- Filtro FIR de 256 Taps

- 256 multiplica y acumula (MAC) operaciones por dato muestreado

- One output every clock cycle

- Flexible architecture

- Bloques DSP, Bloques de Memoria, Registros, Controladores de Reloj, etc.

#### Razón 1

# Procesador DSP - Secuencial

$$\frac{1 \text{ GHz}}{256 \text{ clock cycles}} = 4 \text{ MSPS}$$

# FPGA – Implementación en Paralelo

$$\frac{500 \text{ MHz}}{1 \text{ clock cycle}} = 500 \text{ MSPS}$$

# RAZÓN 2

# Razón 3

#### IMPORTANCIA BLOQUE DSP EN FPGA

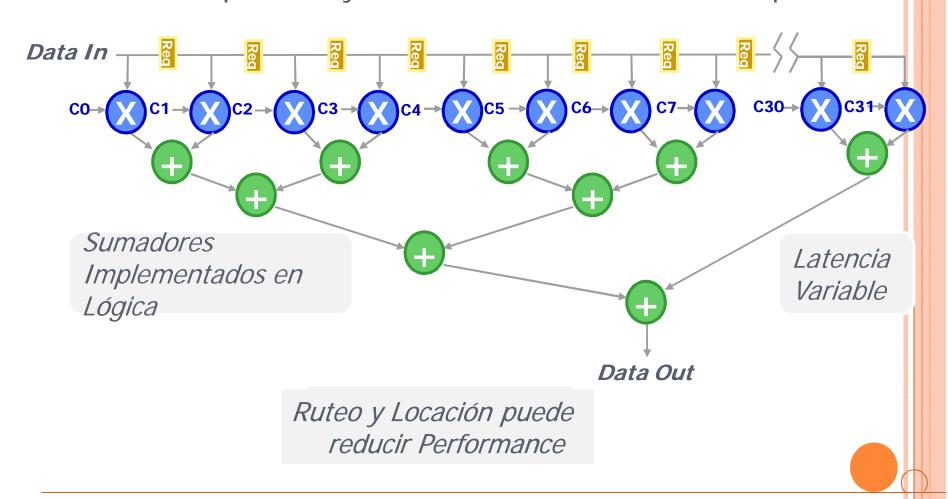

Multiplicación y Suma Paralela en FPGA sin Bloque DSP

#### IMPORTANCIA BLOQUE DSP EN FPGA

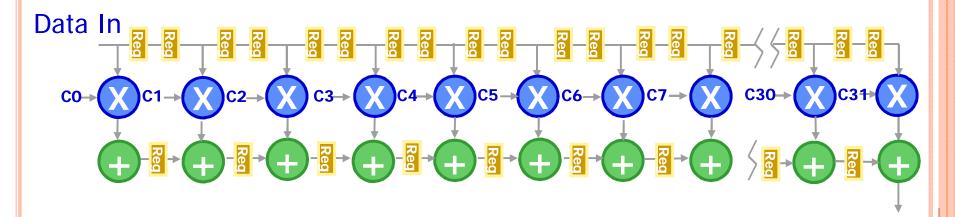

Multiplicación y Suma Paralela en FPGA con Bloque DSP

**Data Out**

# MATLAB - SIMULINK

◆ The MathWorks

Introducción

#### MATLAB - SIMULINK

El entorno MatLab/Simulik es un entorno gráfico para la modelación y simulación de sistemas dinámicos.

#### Soporta:

Sistemas lineales y no lineales, modelados en tiempo continuo, tiempo discreto (muestras) o un híbrido de los dos.

## MATLAB - SIMULINK (CONT.)

- Editor gráfico de bloques

- Simulador controlado por evento(s) (event driven)

- Puede modelar/simular paralelismo

- Una extensa librería de funciones con parámetros variables:

- Bloques matemáticos de Simulink

- Bloques de fuentes de señal y absorción de señal

- Bloques:

- DSPs

- Comunicaciones

# SYSTEM GENERATOR

Xilinx DSP Toolkit

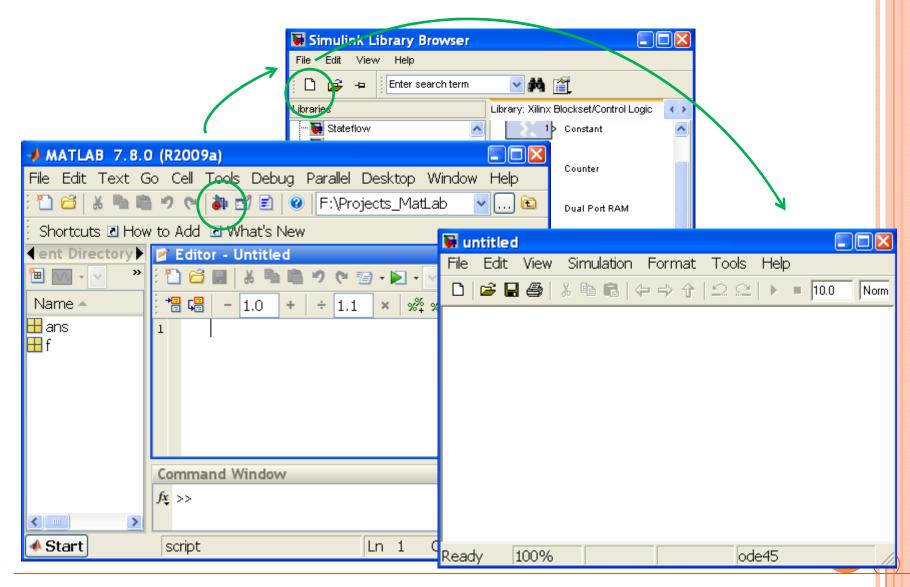

#### SYSTEM GENERATOR - SIMULINK

- Flujo de diseño integrado a Simulink, generando directamente el archivo de programación .bit

- o Integra:

- MatLab, Simulink

- HDL Síntesis

- Librerías de DSP

- Herramientas de implementación del FPGA

- Simulación en doble precisión y punto fijo

- Abstracción Aritmética

- Punto-fijo arbitrario, incluyendo cuantización y overflow

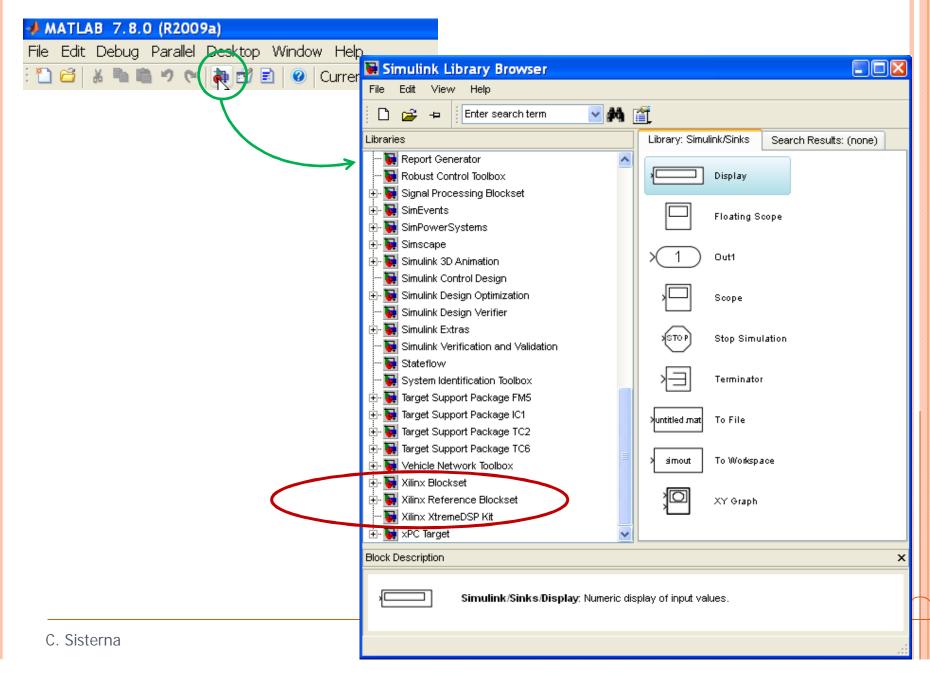

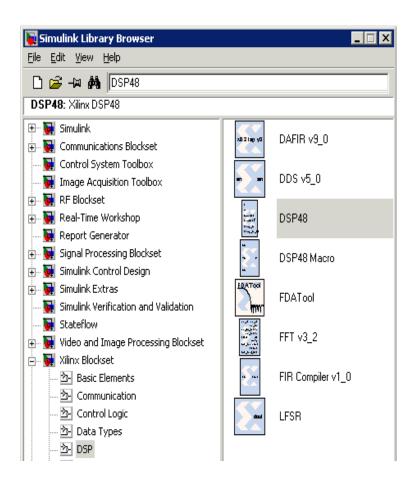

- System Generator es un 'Blockset' dentro del entorno Simulink

26

#### SYSTEM GENERATOR - SIMULINK

#### SYSTEM GENERATOR - SIMULINK

o Librería de funciones:

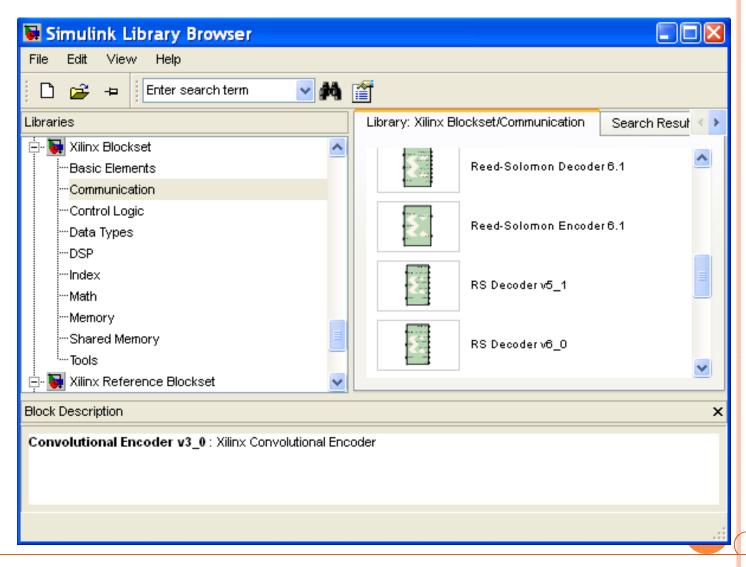

#### SYSGEN: PRINCIPALES BLOQUES

- Elementos básicos: contadores, retardos, lógica binaria, etc.

- Comunicaciones: ECC bloques, Viterbi, Reed Solomon, etc.

- Tipo de Datos: convertir, rotar, concatenar, etc.

- DSP: IIR, FIR, FFT, etc.

- Math: multiplicar, acumular, invertir, contadores, etc.

- Memoria, dual port RAM, single port RAM, ROM, FIFO.

- Tools: ModelSim, Estimador de Recursos, SysGen Token

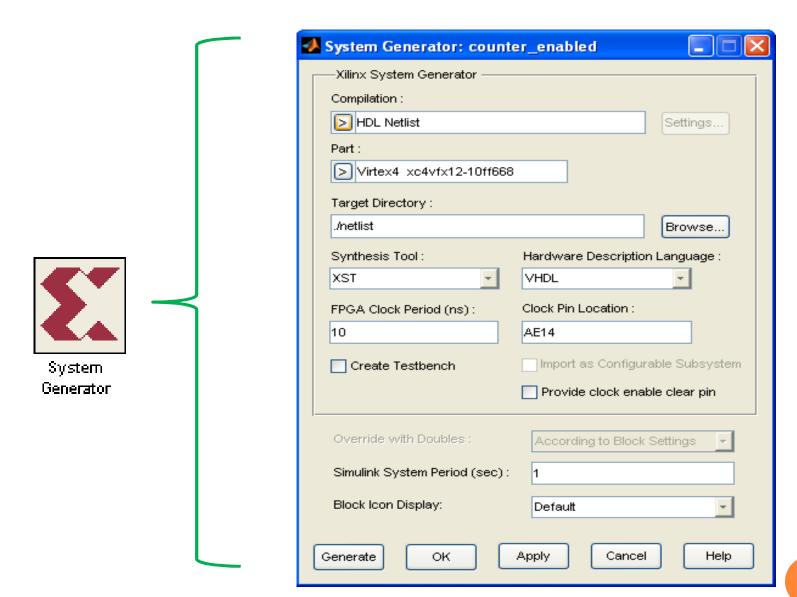

#### SYSGEN-SIMULINK: GENERACIÓN ARCHIVOS

- Generación del código VHDL y Verilog para:

- Virtex-7, Virtex-6, Virtex-5, Virtex-4, Spartan-7, Spartan-6,

Spartan-3E

- Mapeo y expansión del hardware respectivo a cada bloque

- Preservación de la jerarquía del modelo una vez generados los códigos VHDL y Verilog

- Utilización de IP cores de CoreGen

- Generación automática de:

- Un proyecto ISE

- Archivo de restricciones (constraint file \*.ucf)

- Archivo de simulación Test Bench y script \*.do (ModelSim)

30

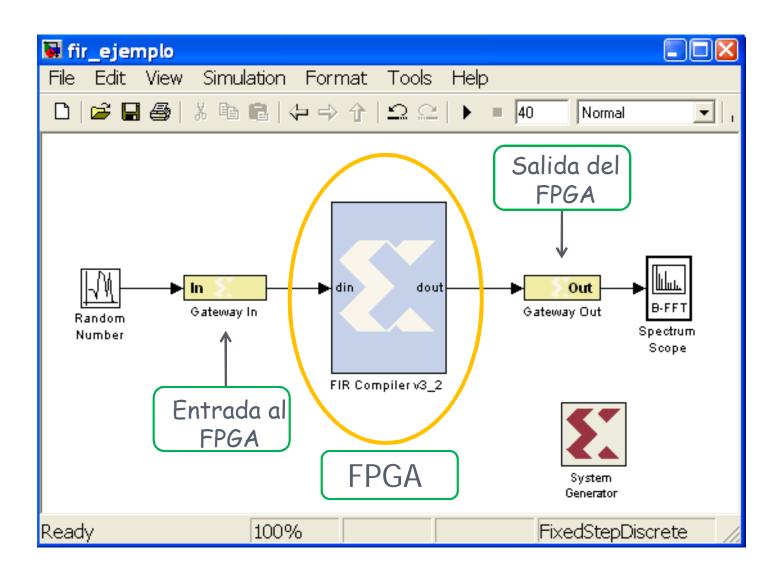

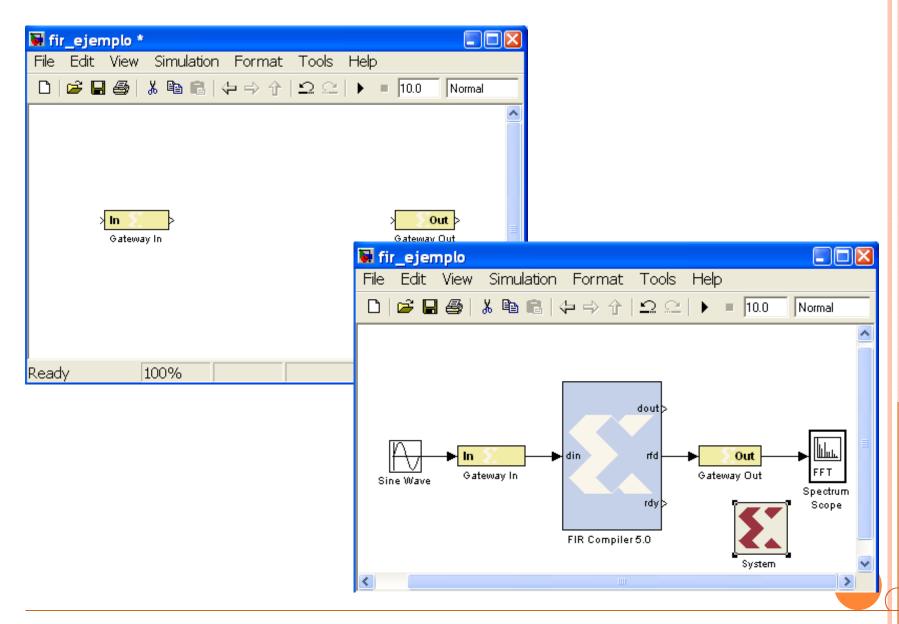

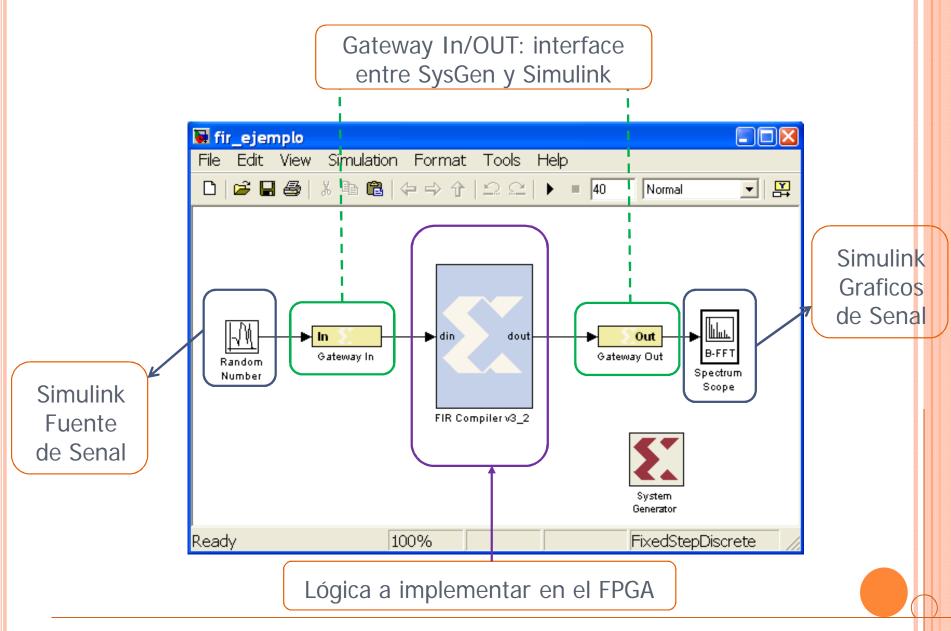

#### SYSGEN - SIMULINK - E/S DEL FPGA

#### SYSGEN IN/OUT

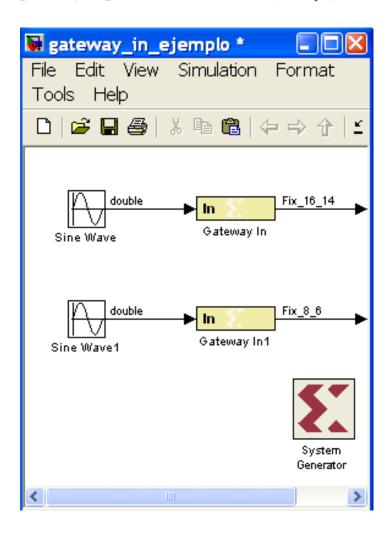

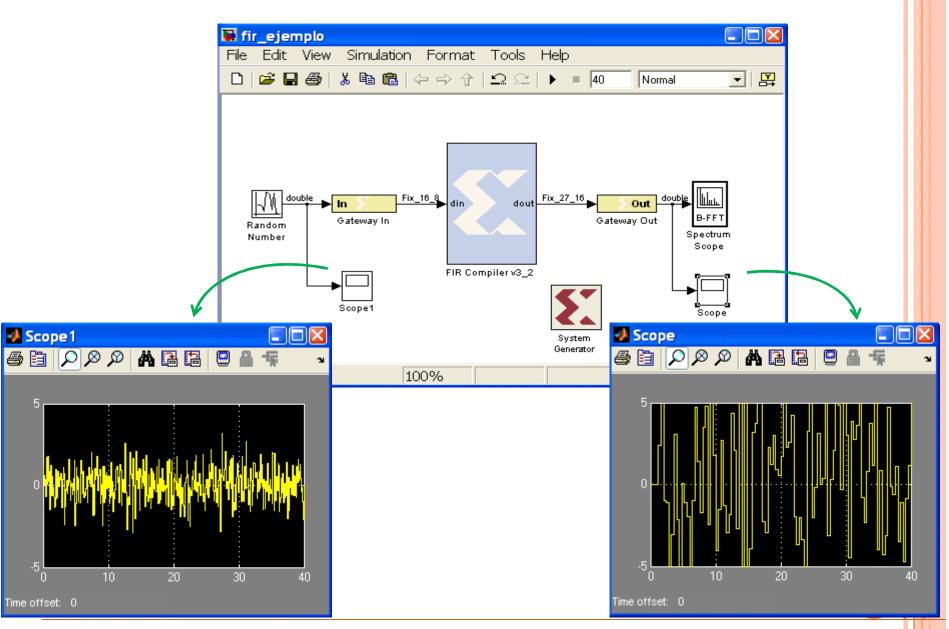

- Simulink usa 'double' para representar números en simulación. A double es un número en punto flotante en complemento a dos de 64 bits.

- TODOS los bloques de Xilinx usan representación en n-bits en punto fijo (complemento a dos es opcional).

- Por ello se usa un bloque para la conversión de datos desde Simulink a un bloque de Xilinx, llamado Gateway In. Y otro bloque para la conversión desde un bloque de Xilinx a Simulink, llamado *Gateway Out*.

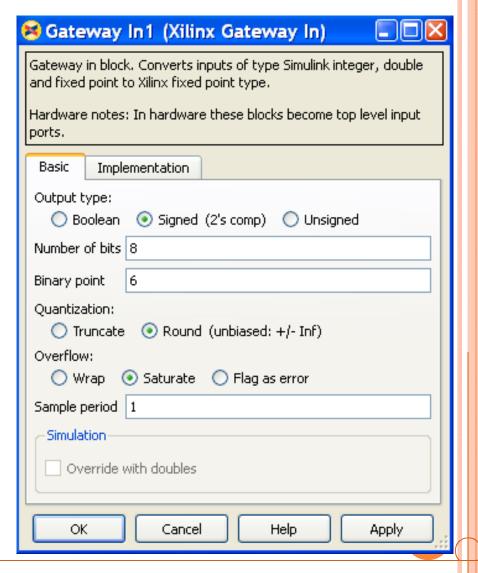

#### SYSGEN: BLOQUE GATEWAY IN

- Controla la conversión desde un número representado en double, entero o punto fijo a un número booleano de N-bits, que puede ser con signo (complemento a dos) o sin signo punto fijo (unsigned fixed-point)

- Presenta la opción de manejar los extra bits durante la conversión

- Este bloque define cuales van a ser las entradas del diseño codificado en HDL por SysGen

- Define los estímulos en caso de que la opción de 'Create Testbench' haya sido seleccionada

33

#### SYSGEN: BLOQUE GATEWAY IN

#### SYSGEN: BLOQUE GATEWAY OUT

- Convierte los datos de punto fijo de System Generator a dato doble de Simulink

- Define cuales van a ser los puertos de salida del sistema codificado en HDL por System Generator

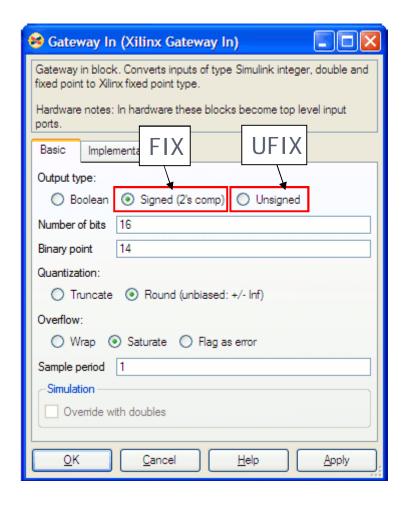

#### SYSGEN: TIPOS DE DATOS

- FIX: tipo de dato fijo, es un número representado en complemento a dos

- UFIX: es un número representado sin signo

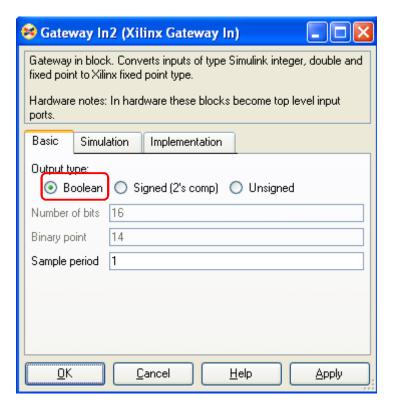

#### SYSGEN: TIPOS DE DATOS

Boolean: pueda tomar valores '1' o '0'. Se usa para controlar señales como LOAD, CS, RESET, etc.

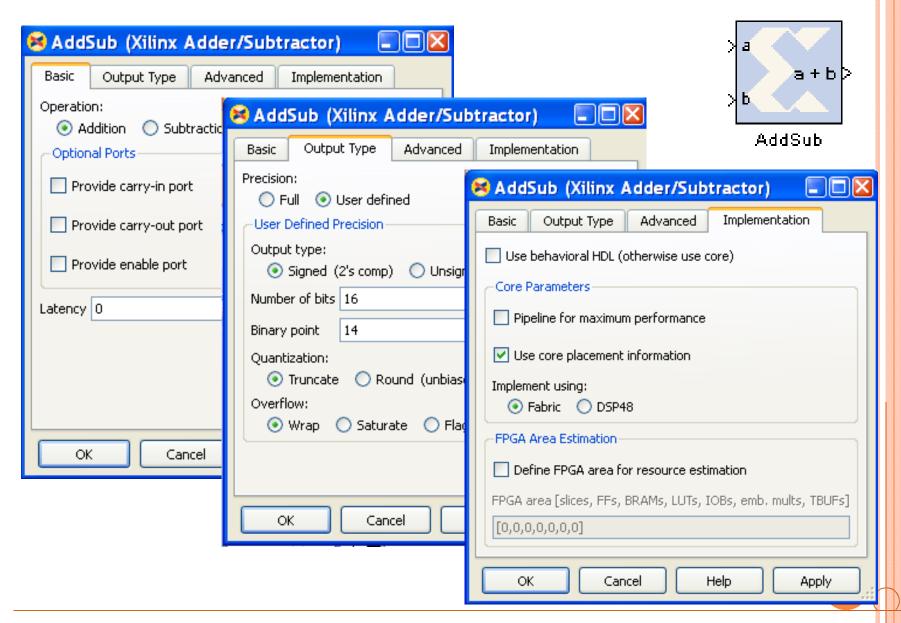

### SysGen - Ejemplo Configuracion

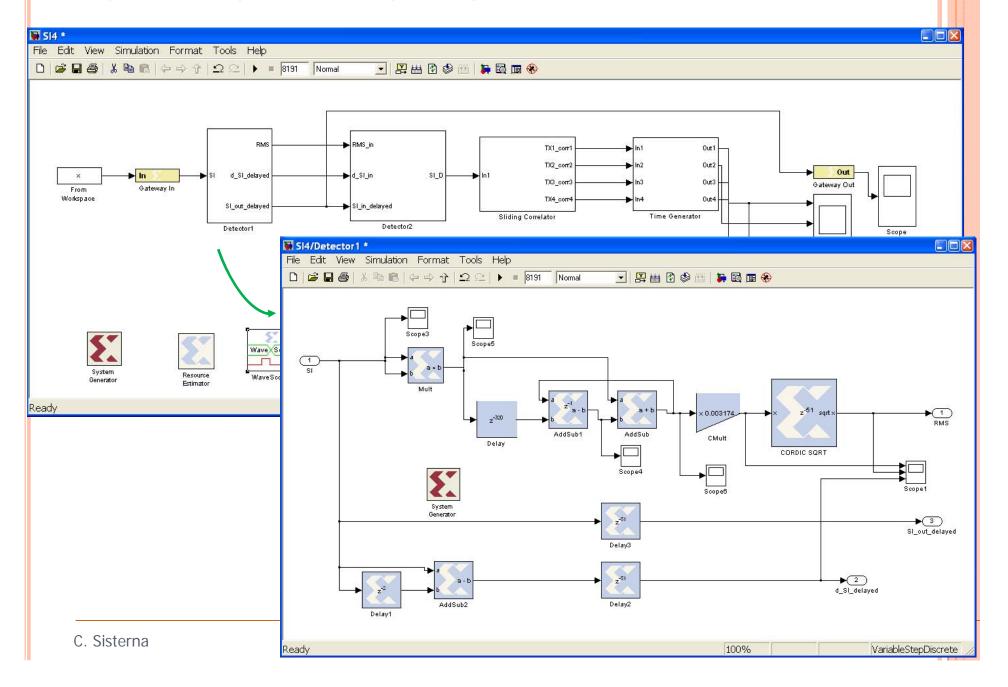

# EJEMPLO DE DISEÑO

Flujo de Diseño Simulink/SysGen/ISE/ModelSim

#### CREANDO UN DISEÑO CON SYSGEN

#### CREANDO UN DISEÑO CON SYSGEN

#### EJEMPLO DE DISEÑO: FIR

## SIMULACIÓN EN SIMULINK

### BLOQUE SYSTEM GENERATOR

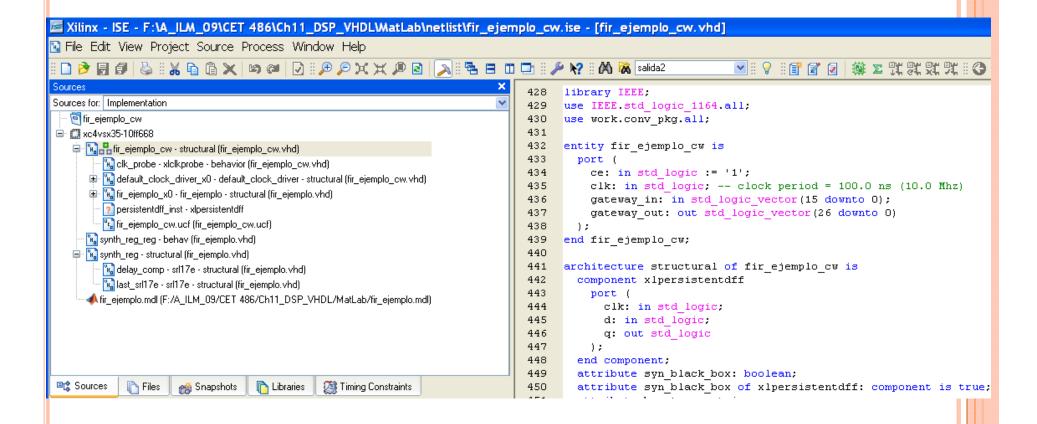

#### SYSGEN - ARCHIVOS GENERADOS

Archivos de Diseño

```

.vhd o .v

.edn o .ngc

.xcf

```

.ise .tcl – Archivos de Proyecto

```

Archivos de Simulación _ .dat

_tb.vhd o _tb.v

```

#### PROYECTO FPGA CREADO POR SYSGEN

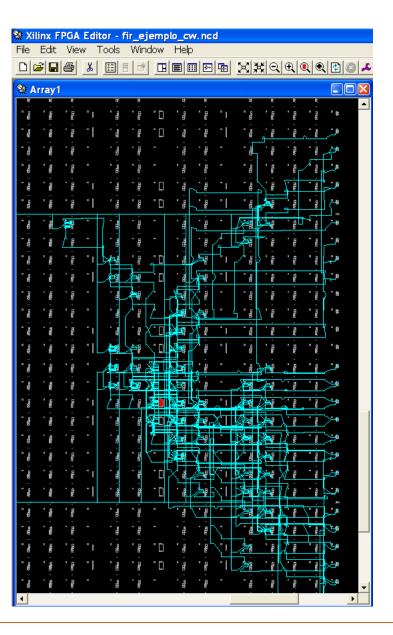

#### VISTA DEL FIR IMPLEMENTADO EN EL FPGA

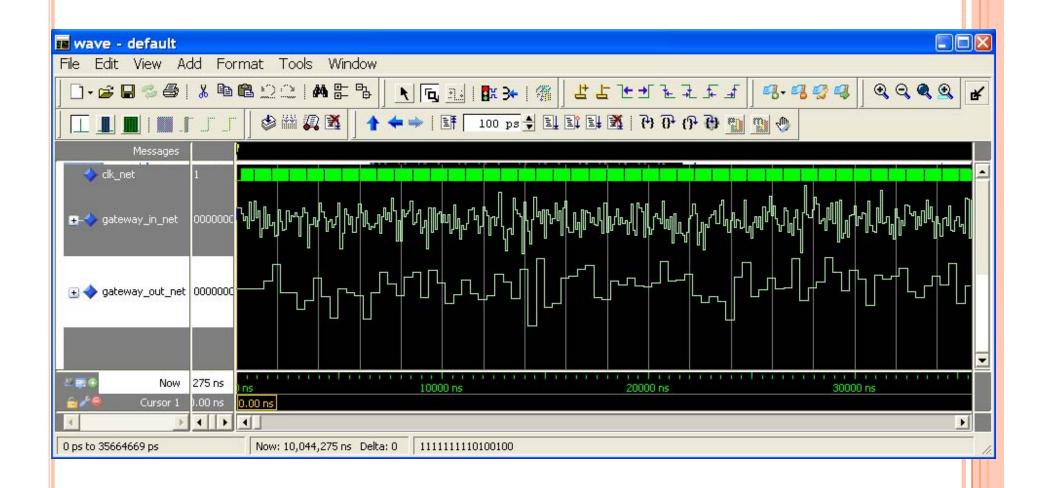

#### FIR-SIMULACIÓN EN MODELSIM

#### EJEMPLO DE DISEÑO

#### Contacto:

cristian@unsj.edu.ar

cristian@c7t-hdl.com

Mas información (notas de aplicación, notas técnicas, etc):

http://www.c7t-hdl.com

Blog

http://hdl-fpga.blogspot.com.ar/